International Journal of Electronics

ISSN: 0020-7217 (Print) 1362-3060 (Online) Journal homepage: https://www.tandfonline.com/loi/tetn20

# Wide range fully integrated VCO with new cellsbased varactor

Margarita Marrero-Martin , Benito Gonzalez , Javier Garcia , Sunil L. Khemchandani , Antonio Hernandez & Javier del Pino

To cite this article: Margarita Marrero-Martin , Benito Gonzalez , Javier Garcia , Sunil L. Khemchandani, Antonio Hernandez & Javier del Pino (2012) Wide range fully integrated VCO with new cells-based varactor, International Journal of Electronics, 99:8, 1165-1178, DOI: 10.1080/00207217.2011.651699

To link to this article: https://doi.org/10.1080/00207217.2011.651699

Published online: 09 Mar 2012.

Submit your article to this journal

Article views: 160

View related articles

Citing articles: 2 View citing articles 🕑

# Wide range fully integrated VCO with new cells-based varactor

Margarita Marrero-Martin<sup>\*</sup>, Benito Gonzalez, Javier Garcia, Sunil L. Khemchandani, Antonio Hernandez and Javier del Pino

ULPGC, IUMA, Campus Universitario de Tafira, Pab A – Dcho 203, Las Palmas de Gran Canaria 35019, Spain

(Received 5 December 2010; final version received 23 November 2011)

This article presents a wide range inductance–capacitance voltage controlled oscillator (VCO) with a unit cells-based varactor. The unit cell represents the minimum possible integrated varactor based on p–n junction diodes, where N<sup>+</sup> diffusions are central rectangles, surrounded by doughnut shaped P<sup>+</sup> diffusions, with their respective contacts. The varactors are designed using the AMS 0.35  $\mu$ m BiCMOS process. A physical model has been derived from the measurement of a set of eight fabricated varactors. Measurements indicate that the VCO, which is intended to be used in DVB-H, oscillates from 1.087 to 2.032 GHz, with a 61% tuning range. The phase noises of –124 dBc/Hz at 1 MHz offset and –108 dBc/Hz at 100 kHz offset are obtained.

Keywords: VCO; capacitance model; PN varactor; BiCMOS

## 1. Introduction

Radio frequency (RF) communication systems demand better and cheaper devices (Tiemeijer et al. 2004) with lower power consumption and higher data transfer rates. There are modules, for example voltage controlled oscillator (VCOs), which are important in many RF applications as transceivers for wireless communication (Gu 2005).

VCOs are oscillators in which the output frequency depends on an applied external voltage. Electronic systems, which require a source of variable frequency used for clock and data recovery, frequency synthesis, and other applications, utilise these subsystems. These circuits are particularly important in phase locked loops, used for clock generation and synchronisation (Craninckx and Steayert 1995). For the implementation of these circuits silicon-based technologies are used, like SiGe or BiCMOS (Larson, Case, Rosenbaum, and Rensh 1996).

One of the most widely used architectures for high frequency is the inductancecapacitance (LC) oscillator (Hegazy, Sharaf, and Ragai 2002). LC oscillators are based on the parallel resonance of an inductor and a capacitor. Usually, a negative resistance configuration is used to compensate tank losses, and consequently maintain the oscillation. To convert the oscillator in a VCO, the most common technique is to replace the capacitor with a varactor. The phase noise of LC-tuned oscillators is much better than other configurations, because they use the band pass characteristic of the LC-tank to reduce it. Other types of oscillators, like ring oscillators, suffer from switching effects

<sup>\*</sup>Corresponding author. Email: margarita@iuma.ulpgc.es

and can introduce noise in the power supply, causing a worse phase noise than LC-tuned oscillators (Kral 1998).

Integrated varactors can be made in several ways (Pedersen 2001; Gau et al. 2005). Those implemented by metal-oxide-silicon (MOS) capacitors (MOSVAR) or p-n junction diodes (JVAR) are usually by-product devices from a standard fabrication process, which is originally for CMOS transistors (Chan, Huang, Wu, Chen, and Chao 2007). The choice of one of them will depend on the application. The keys to this choice are the *Q*-factor and the tuning range. Thus, the *Q*-factor in p-n junction diodes (JVARs) is significantly superior to that in MOS capacitors (MOSVARs), primarily due to a lower resistance, whereas the tuning range,  $C_{\rm max}/C_{\rm min}$ , is lower (Chan et al. 2007).

In order to design a fully integrated VCO, where the LC-tank is on chip, cells-based varactors have been designed according to the tank requirements. The Q of the tank will determine the VCO's phase noise and power consumption (Maget et al. 2003). Therefore, they will be dominated by the Q of the inductor for low frequency range, and the Q of the varactor at higher range, such as mm-wave. In our case, the cells-based varactors have been designed and modelled to operate in the gigahertz-range.

The organisation of this article is as follows. In 'Designed varactors' section, we describe the cell-based varactors, and their model is presented in next section. A fully integrated VCO using  $0.35 \,\mu m$  SiGe technology is described in 'Designed VCO' section. The next section is devoted to the VCO 'measurement and results'. Finally, the 'conclusions' are given.

#### 2. Designed varactors

PN-junction in JVARs is created by implanting  $P^+$  diffusions into N-wells. As they use electrons as majority carriers, *Q*-factors higher than those in  $N^+$  to P-well junctions are expected. The JVARs' capacitance is associated with the depletion area between  $P^+$  diffusions and the well. The  $P^+$  substrate is usually connected to ground.

Varactor capacitance is strongly dependent on layout geometry, having a great impact on large size varactors. An efficient silicon area, to decrease the device cost, is obtained by reducing the size of the varactor (Aparicio and Hajimiri 2002). Thus, layout geometry has been modified to develop some novel varactors which are different to those supplied by the foundry (García et al. 2007).

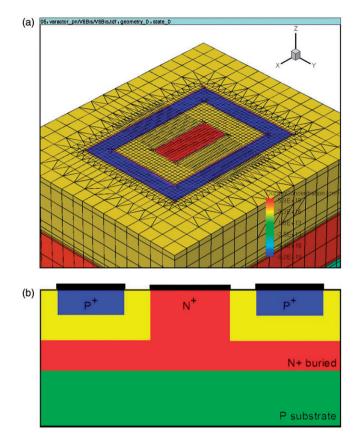

In order to obtain the required capacitance, the first step of our methodology is designing a unit cell. This unit cell represents the minimum possible integrated varactor. Its layout, whose area is  $12.9 \times 11.1 \,\mu\text{m}^2$ , is shown in Figure 1(a): N<sup>+</sup> diffusions are central rectangles, surrounded by doughnut shaped P<sup>+</sup> diffusions, with their respective contacts. In our case, N<sup>+</sup> diffusions are deep enough to reach an N<sup>+</sup> buried layer, according to Figure 1(b), diminishing the resistance of the device.

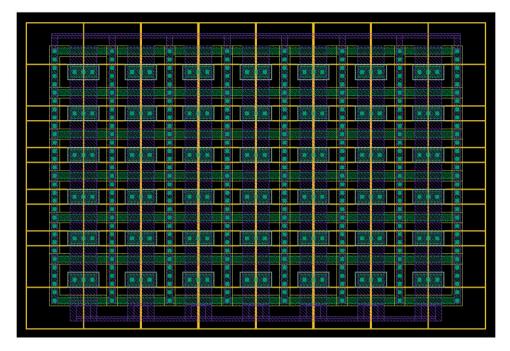

Then, the varactors are made up of horizontal and vertically overlapping unit cells on  $P^+$  diffusions. As an example, Figure 2 illustrates a varactor with 42 unit cells.

#### 3. Varactor model

Eight varactors based on cells have been designed and fabricated. They have been measured on-wafer by means of a Cascade Probe Station and Vector Network Analyzer

Figure 1. (a) Unit cell layout and (b) unit cell layer structure.

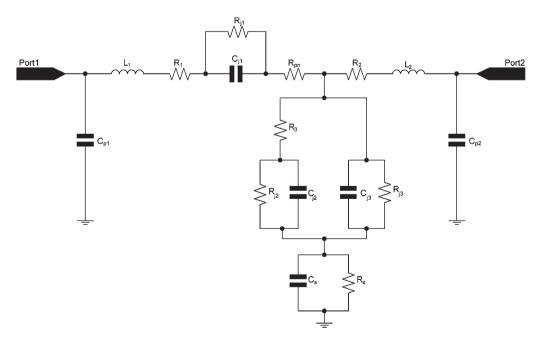

(Agilent 8720ES). Then, a capacitive model has been generated. Figure 3 shows the resulting equivalent circuit of varactors.

The varactor used in our VCO has 90 unit cells. All the values for the modelled components are given in Table 1.

Junctions capacitances,  $C_{j_1}$ ,  $C_{j_2}$  and  $C_{j_3}$ , between P<sup>+</sup> diffusions and Nwell, substrate and N<sup>+</sup> buried layer, and Nwell and substrate, respectively, are modelled in the study of Marrero-Martín, García, González, and Hernández (2010) and given by

$$C_{j_k} = \frac{C_{A_k} \cdot A_k + C_{P_k} \cdot P_k}{\sqrt{1 - \frac{V}{V_{b_{i_k}}}}} \quad k = 1, 2, 3$$

(1)

where  $C_{A_k}$  and  $C_{P_k}$  are the capacitances per unit area and perimeter length of the different junctions, with area  $A_k$  and perimeter  $P_k$ , and  $V_{bi_k}$  the corresponding built-in voltage; V the applied voltage from anode to cathode.

The ground proximity effect from ports 1 and 2,  $C_{p_1}$  and  $C_{p_2}$ , and the substrate capacitance,  $C_s$ , depends on the number of cells.

With respect to resistors,  $R_s$  models the parasitic effects due to the substrate,  $R_{pn}$  the Nwell resistance, associated to the neutral region,  $R_{j1}$ ,  $R_{j2}$  and  $R_{j3}$ , the resistances of every

Figure 2. Varactor layout.

Figure 3. Inductors, resistors and capacitors of varactor equivalent circuit.

| Model component      | Value $(\Omega)$ | Model component | Value      |  |

|----------------------|------------------|-----------------|------------|--|

| $R_1$                | 0.42             | $C_{i_1}$       | 1608.01 fF |  |

| $R_2$                | 0.97             | $C_{j_2}$       | 702.41 fF  |  |

| $R_3$                | 8e2              | $C_{j_3}$       | 100.86 fF  |  |

| $R_{i1}$             | 2.87e16          | $C_{p_1}$       | 30 fF      |  |

| $R_{j1}$<br>$R_{j2}$ | 1.21e14          | $C_{p_2}$       | 25 fF      |  |

| $\vec{R_{i3}}$       | 8.46e14          | $\hat{C}_s$     | 275.11 fF  |  |

| $R_{j3}$<br>$R_s$    | 15.84            | $L_1$           | 55 pH      |  |

| $R_{pn}$             | 0.2589           | $L_2$           | 30 pH      |  |

Table 1. Values of model components.

depletion region in junctions,  $P^+$  diffusions – Nwell, substrate –  $N^+$  buried layer, and Nwell – substrate, respectively,  $R_1$  and  $R_2$  correspond to the resistances of interconnections on ports 1 and 2, and  $R_3$ , the resistance between Nwell and N<sup>+</sup> buried layer.

The inductances are associated with metal interconnections on ports 1 and 2; and exponentially depend on the number of cells.

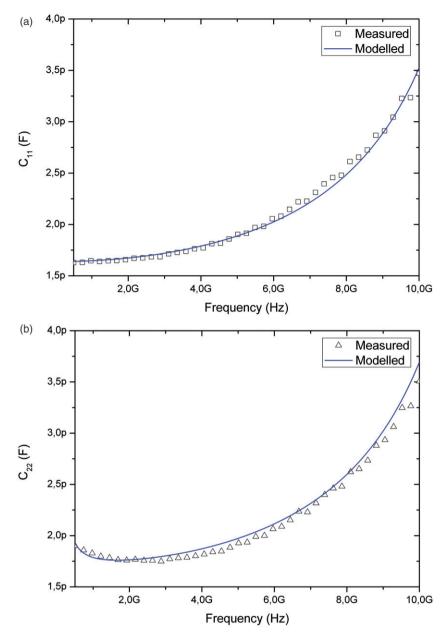

Figure 4 represents the measured (with symbols) and modelled (with lines) capacitances of the varactor selected, from port 1 (a) and port 2 (b) in all the frequency range and an applied voltage at 0 V.

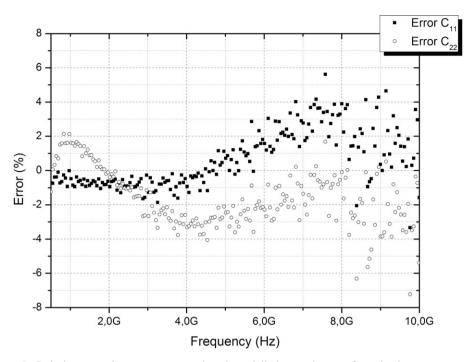

The corresponding relative error between modelled and measured capacitances from both ports is less than 8% in any case, as Figure 5 shows, where  $C_{11}$  and  $C_{22}$  errors are plotted with solid and open marks, respectively.

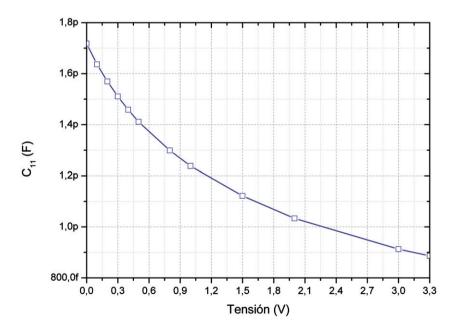

From Figure 6, which represents the varactor capacitance dependence on the applied voltage (from 0 to 3.3 V), at 0.88 GHz, a tuning characteristic of 33.48% is derived. *Q*-factor varies from 40.17 to 75.57 at the same frequency.

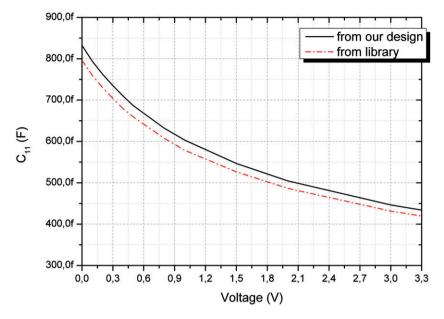

In order to point out the benefits of our design methodology, a varactor from AMS  $0.35 \,\mu\text{m}$  BiCMOS library has been manufactured and measured, and compared with one of our varactors with similar capacitance. Their capacitive characteristic curves are represented in Figure 7, and Table 2 compares the relevant parameters. The tuning range is similar, around 31%. However, our varactor shows a higher quality factor and a significative lower area.

## 4. Designed VCO

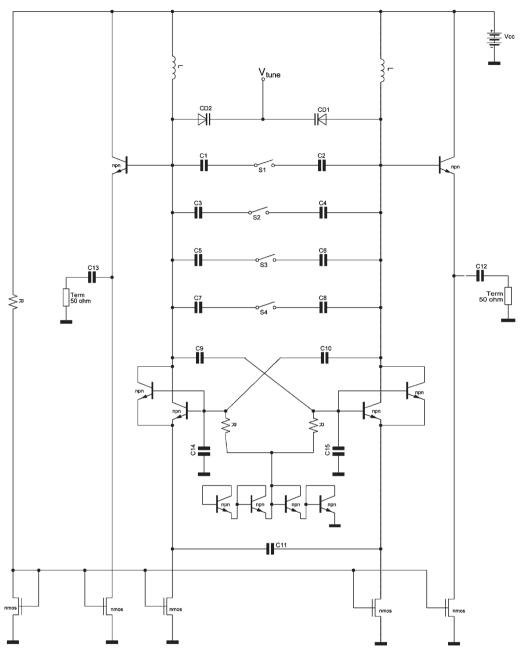

To demonstrate the feasibility of the designed varactors, a VCO has been fabricated. The best inductor for the VCO tank is chosen with an automatic generation tool called IMODEL (Iturri, del Pino Suárez, Khemchandani, and Hernández 2008). The simplified schematic of the VCO is shown in Figure 8. This oscillator uses an LC oscillator topology, integrating all components of the tank on chip. The VCO core uses a cross-coupled transistor pair to build up the negative resistance. A differential topology provides a more stable frequency versus supply voltage characteristic, and improves the immunity to load variations. A buffer amplifier was also added to provide additional isolation from load variations and to boost the output power.

The inductors are designed so that the quality factor is the optimal one for the frequency of interest (Goñi Iturri et al. 2005), and the varactors have been selected

Figure 4. Capacitances versus frequency of the varactor selected from: (a) port 1 and (b) port 2.

according to our model. A voltage applied to the  $V_{TUNE}$  pin, which is connected to varactors, controls the VCO frequency.

Additionally, an array of switched capacitors is employed to increase the frequency range. It uses techniques like emitter degeneration, capacitor divider and optimum bias for minimum noise to improve phase noise requirements and oscillation amplitude (Khemchandani, del Pino, Diaz, and Hernandez 2009).

Figure 5. Relative error between measured and modelled capacitances from both ports.

Figure 6. Capacitances from port 1 versus voltage.

Figure 7. Capacitances from port 1 versus the applied voltage for the designed varactor and a varactor from the AMS BiCMOS library.

|                                                                      | Own varactor | Library varactor |  |  |

|----------------------------------------------------------------------|--------------|------------------|--|--|

| TR (%)                                                               | 30.55        | 31.03            |  |  |

| $Q_{ m min~(at~0.88GHz)}$                                            | 97.84        | 58.14            |  |  |

| $Q_{\text{max} (\text{at } 0.88 \text{ GHz})}$<br>Area ( $\mu m^2$ ) | 183.89       | 110.46           |  |  |

| Area (µm <sup>2</sup> )                                              | 1661.52      | 2120.4           |  |  |

Table 2. Parameters of designed varactors.

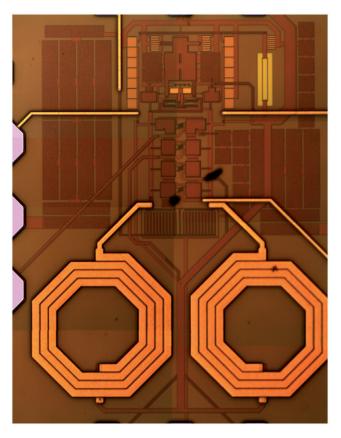

The layout of the VCO, which is shown in Figure 9, is designed with the greatest possible symmetry between the two branches of the differential circuit. In order to reduce the influence of gradients of dispersion in the performance of the VCO, the elements are placed matched with a common centroid technique (Baker, Li, and Boyce 1998).

The layouts are designed to reduce the circuit area as much as possible and to introduce the minimum degradation with connecting tracks.

#### 5. Measurement results

Measurement of the VCO was carried out on-wafer with 35 GHz signal-ground-signal (SGS) probes, using a Cascade SUMMIT 9000 probe station with an optical microscope Olympus SZ-CTV, and the 26.5 GHz Agilent E4440A spectrum analyser with phase noise measurement personality.

Figure 8. VCO schematic.

Figure 9. VCO layout.

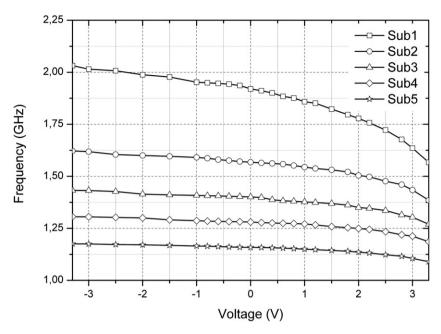

Figure 10 shows the VCO tuning range and overlapping regions of the five subbands. VCO oscillates from 1087 to 2032 MHz, using only one core. The measured tuning range is 61% around 1.56 GHz, and the total chip area is 0.841 mm<sup>2</sup>.

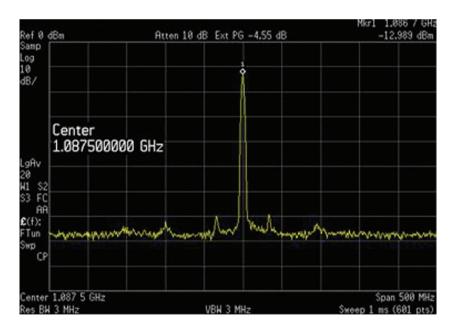

The VCO spectrum, when  $V_{TUNE}$  is set to 3.3 V and all switched capacitors (S1, S2, S3 and S4) are connected (Figure 8), was also measured and represented in Figure 11. Notice that a central frequency of 1087 MHz is derived.

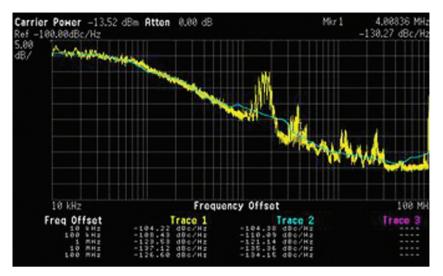

As Figure 12 shows, the phase noises of  $-124 \, \text{dBc/Hz}$  at 1 MHz offset and  $-108 \, \text{dBc/Hz}$  at 100 kHz offset are obtained.

Finally, Table 3 compares the performance of our VCO with other published integrated VCOs (Herzel, Erzgraber, and Ilkov 2000; Tiebout 2002; Li and Kenneth 2003; Antoine et al. 2005; Berny, Niknejad, and Meyer 2005; Sung, Lee, Baek, Kim, and Park 2005). It oscillates in the same band by means of a figure of merit (FoM) according to the following formula

$$FoM = 10 \cdot \log \left(\frac{f_{max} - f_{min}}{\Delta f}\right)^2 - 10 \cdot \log L(\Delta f)$$

where  $f_{\text{max}}$  and  $f_{\text{min}}$  are the maximum and minimum frequencies,  $\Delta f$  the offset frequency and  $L(\Delta f)$  the phase noise at  $\Delta f$ . The combination of low phase noise and tuning range give

Figure 10. VCO tuning range.

Figure 11. VCO spectrum with a 500 MHz span.

Figure 12. VCO measured phase noise for a 1087 MHz oscillation frequency.

| Author                                                                             | L (1 MHz)<br>dBc/Hz             | Tuning<br>range (%)        | Band<br>(MHz)                                   | Technology<br>(µm)                                 | FoM<br>(dB)                          | Type of varactor  | Number<br>of cores                                       |

|------------------------------------------------------------------------------------|---------------------------------|----------------------------|-------------------------------------------------|----------------------------------------------------|--------------------------------------|-------------------|----------------------------------------------------------|

| This study<br>Berny et al. (2005)<br>Herzel et al. (2000)<br>Li and Kenneth (2003) | -124<br>-126.50<br>-116<br>-124 | 61<br>72.20<br>46<br>53.60 | 1087–2032<br>1150–2450<br>1340–2140<br>667–1156 | BiCMOS 0.35<br>CMOS 0.18<br>CMOS 0.35<br>CMOS 0.18 | 183.03<br>188.78<br>174.01<br>177.78 | PN<br>MOS<br>MOS  | Single core<br>Single core<br>Single core<br>Single core |

| Sung et al. (2005)<br>Antoine et al. (2005)<br>Tiebout (2002)                      | -131<br>-135<br>-127            | 63.11<br>82.10<br>69       | 900–1730<br>420–1005<br>978–2010                | CMOS 0.18<br>BiCMOS 0.35<br>CMOS 0.25              | 189.38<br>176.88<br>175.97           | MOS<br>MOS<br>MOS | Single core<br>Three cores<br>Single core                |

Table 3. Comparison with published wide-band VCOs.

to our design a good classification, even better than (Antoine et al. 2005), which uses a three-core VCO. The VCO with the best FoM (Sung et al. 2005) uses an external high Q inductor (it is not fully integrated).

### 6. Conclusions

In this article, we have modelled new cell-based varactors. The varactors are p–n junction diodes, designed using the AMS 0.35  $\mu$ m BiCMOS process. A set of eight varactors has been fabricated and measured to test the varactors and validate the proposed physical model. One LC VCO was also fabricated and measured. The frequency range is from 1.087 to 2.032 GHz, with a 61% tuning range, and the phase noise is –124 dBc/Hz at 1 MHz offset. The proposed VCO exhibits a good FoM compared to other fully integrated VCOs operating in the same band.

### References

Antoine, P., Bauser, P., Beaulaton, H., Buchholz, M., Carey, D., Cassagnes, T., Chan, T.K., Colomines, S., Hurley, F., Jobling, D.T., Kearney, N., Murphy, A.C., Rock, J., Salle, D., and

Tu, C.-T. (2005), 'A Direct-conversion Receiver for DVB-H', *IEEE Journal of Solid-State Circuits*, 40, 2536–2546.

- Aparicio, R., and Hajimiri, A. (2002), 'Capacity Limits and Matching Properties of Integrated Capacitors', *IEEE Journal of Solid State Circuits*, 37, 384–393.

- Baker, R.J., Li, H.W., and Boyce, D.E. (1998), CMOS Circuit Design, Layout, and Simulation, Piscataway, NJ: IEEE Press.

- Berny, A.D., Niknejad, A.M., and Meyer, R.G. (2005), 'A 1.8-GHz LC VCO with 1.3-GHz Tuning Range and Digital Amplitude Calibration', *IEEE Journal of Solid-State Circuits*, 40, 909–917.

- Chan, Y.-J., Huang, C.-F., Wu, C.-C., Chen, C.-H., and Chao, C.-P. (2007), 'Performance Consideration of MOS and Junction Diodes for Varactor Application', *IEEE Transactions on Electron Devices*, 54, 2570–2573.

- Craninckx, J., and Steayert, M. (1995), 'Low-noise Voltage-controlled Oscillators using Enhanced LC-tanks', *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, 42, 794–804.

- García, J., González, B., Marrero-Martín, M., Aldea, I., del Pino, J., and Hernández, A. (2007), 'Analysis of PN Integrated Varactors with N<sup>+</sup> Buried Layer Varying P<sup>+</sup> Diffusions Contour for RF Applications', in *Proceedings of the XXII DCIS Conference*, Sevilla, España, 21–23 November.

- Gau, J.H., Wu, R.T., Sang, S., Kuo, C.H., Chang, T.L., Chen, H.H., Chen, A., and Ko, J. (2005), 'Gate Assisted High-Q-factor Junction Varactor', *IEEE Electron Device Letters*, 26, 682–683.

- Goñi Iturri, A., Khemchandani, S.L., del Pino, J., García, J., González Pérez, B., and Hernández Ballester, A. (2005), 'Design and Modeling of an On-silicon Spiral Inductor Library using Improved EM Simulations', in *Proceedings of the Microtechnologies for the New Millennium* 2005, SPIE, Europe, 9–11 May.

- Gu, Q. (2005), RF System Design of Transceivers for Wireless Communications, New York, NY: Springer.

- Hegazy, H., Sharaf, K., and Ragai, H.F. (2002), 'A Comparative Study of CMOS-based Quadrature Integrated LC VCO Topologies', in *Proceedings of the 45th IEEE International Midwest* Symposium on Circuits and Systems, Tulsa, OK, 4–7 August, Vol. 1, pp. 336–339.

- Herzel, F., Erzgraber, H., and Ilkov, N. (2000), 'A New Approach to Fully Integrated CMOS LC-oscillators with a Very Large Tuning Range', in *Proceedings of the IEEE Custom Integrated Circuits Conference, 2000, CICC*, Orlando, FL, 21–24 May, pp. 573–576.

- Iturri, A.G., del Pino Suárez, J., Khemchandani, S.L., and Hernández, A. (2008), 'IMODEL: A Novel Tool for High-performance Inductor Selection', *Microwave Journal*, 51: 90–100. Horizon House Publications Inc.

- Khemchandani, S.L., del Pino, J., Diaz, R., and Hernandez, A. (2009), 'A Fully Integrated Single Core VCO with a Wide Tuning Range for DVB-H', *Microwave and Optical Technology Letters*, 50: 1338–1343. John Wiley & Sons Inc.

- Kral, A. (1998), 'A 2.4 GHz CMOS Frequency Synthesizer', Master Thesis, Integrated Circuits and Systems Laboratory, UCLA, pp. 109–141.

- Larson, L.E., Case, M., Rosenbaum, S., and Rensh, D., (1996), 'Si/SiGe HBT Technology for Low Cost Monolithic Microwave Integrated Circuits', in *Proceedings of the 1996 International Solid State Circuits Conference*, San Francisco, CA, 8–10 February, pp. 80–81.

- Li, Z., and Kenneth, O. (2003), 'A 900-MHz 1.5-V CMOS Voltage-controlled Oscillator using Switched Resonators with a Wide Tuning Range', *IEEE Microwave and Wireless Components Letters*, 13, 137–139.

- Maget, J., Tiebout, M., and Kraus, R. (2003), 'MOS Varactors with n- and p-type Gates and Their Influence on an LC-VCO in Digital CMOS', *IEEE Journal of Solid-State Circuits*, 38, 1139–1147.

- Marrero-Martín, M., García, J., González, B., and Hernández, A. (2010), 'Capacitive Model for Integrated PN Varactors of Cells with N<sup>+</sup> Buried Layer', *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, 23, 364–378.

- Pedersen, E. (2001), 'RF CMOS Varactors for 2 GHz Applications', *Analog Integrated Circuits and Signal Processing*, 26, 27–36.

- Sung, E.Y., Lee, K.S., Baek, D.H., Kim, Y.J., and Park, B.H. (2005), 'A Wideband 0.18-µm CMOS ΔΣ Fractional-N Frequency Synthesizer with a single VCO for DVB-T', in *Proceedings of the* 2005 Asian Solid-State Circuits Conference, Hsinchu, 1–3 November, pp. 193–196.

- Tiebout, M. (2002), 'A CMOS Fully Integrated 1 GHz and 2 GHz Dual Band VCO with a Voltage Controlled Inductor', in *Proceedings of the 28th European Solid-State Circuits Conference*, Florence, Italy, 24–26 September, pp. 799–802.

- Tiemeijer, L., Havens, R., de Kort, R., Scholten, A., van Langevelde, R., Klaassen, D., Sasse, G., Bouttement, Y., Petot, C., Bardy, S., Gloria, D., Scheer, P., Boret, S., Van Haaren, B., Clement, C., Larchanche, J.-F., Lim, I.-S., Duvallet, A., and Zlotnicka, A. (2004), 'Record RF Performance of Standard 90 nm CMOS Technology', in *Proceedings of the IEEE Electron Devices Meeting*, 2004, *IEDM Technical Digest*, San Francisco, CA, 13–15 December 2004, pp. 441–444.