### ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### PROYECTO FIN DE CARRERA

# DISEÑO DE UN FILTRO ASINCRONO DIGITAL DE ALTA FRECUENCIA PARA RECEPTORES DIGITALES

**Autor: D. Carlos Manuel Fernández Reyes Tutor: Dr. Francisco Javier del Pino Suárez**

Fecha: Junio 2018

## ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### PROYECTO FIN DE CARRERA

### DISEÑO DE UN FILTRO ASINCRONO DIGITAL DE ALTA FRECUENCIA PARA RECEPTORES DIGITALES

#### **HOJA DE FIRMAS**

#### **Alumno**

Fdo.: D. Carlos Manuel Fernández Reyes

**Tutor**

Fdo.: Dr. Francisco Javier del Pino Suárez

Fecha: Junio 2018

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### PROYECTO FIN DE CARRERA

### DISEÑO DE UN FILTRO ASINCRONO DIGITAL DE ALTA FRECUENCIA PARA RECEPTORES DIGITALES

#### **HOJA DE EVALUACIÓN**

| Calificación: |              |

|---------------|--------------|

| Presidente    |              |

| Fdo.:         |              |

| Vocal         | Secretario/a |

| Fdo.:         | Fdo.:        |

|               |              |

Fecha: Junio 2018

#### **Agradecimientos**

En principio quería dar un agradecimiento en general, compañero, profesores y todos los miembros que componen la comunidad educativa a la que estuve ligado tanto tiempo.

Aunque me ha costado entregar parece que ha llegado a su fin, seguramente no hubiese sido posible sin mi compañera y amiga Enara, siempre está para ayudarme y darme ánimos

Tampoco puede faltar el agradecimiento a mi Bea que no se ha aburrido de este PFC ni de mi aún, y especialmente por preocuparse en que pudiera entregar.

Un especial agradecimiento a mi tutor Javier que me ha aguantado mis inesperadas visitas y siempre con una actitud positiva.

Y finalmente a la persona más especial y que más me ha dado, mi Madre.

### ÍNDICE

| 1. Introducción                                       | 1  |

|-------------------------------------------------------|----|

| Motivación                                            | 1  |

| Objetivos y organización de la memoria                | 3  |

| 2. Introducción a los convertidores A/D Sigma-Delta   | 5  |

| Introducción                                          | 5  |

| Convertidor A/D Sigma-Delta                           | 6  |

| Conclusiones                                          | 11 |

| 3. Filtros digitales                                  | 13 |

| Introducción                                          | 13 |

| Filtros digitales                                     | 14 |

| Respuesta finita al impulso (FIR)                     | 14 |

| Respuesta infinita al impulso (IIR)                   | 18 |

| Características de los filtros digitales              | 20 |

| Filtro FIR asíncrono                                  | 22 |

| Diezmado                                              | 24 |

| Implementación del filtro digital en Matlab           | 29 |

| Conclusiones                                          | 34 |

| 4. Efectos de Cuantificación y no linealidades        | 37 |

| Introducción                                          | 37 |

| Cuantificación del filtro digital                     | 38 |

| Formato de datos y representación numérica            | 39 |

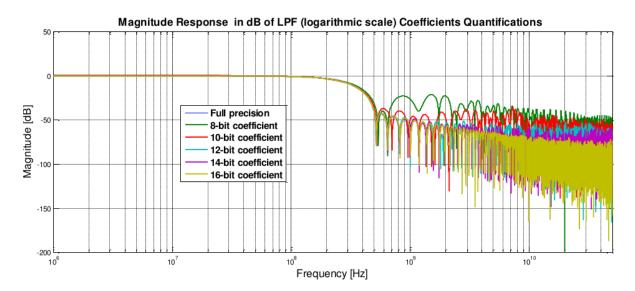

| Cuantificación de los coeficientes                    | 40 |

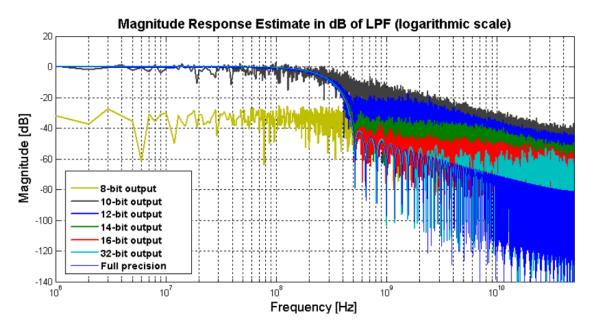

| Cuantificación de salida y operaciones aritméticas    | 44 |

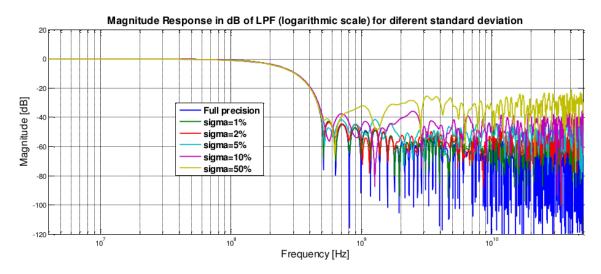

| No-linealidad en los elementos de retardo             | 49 |

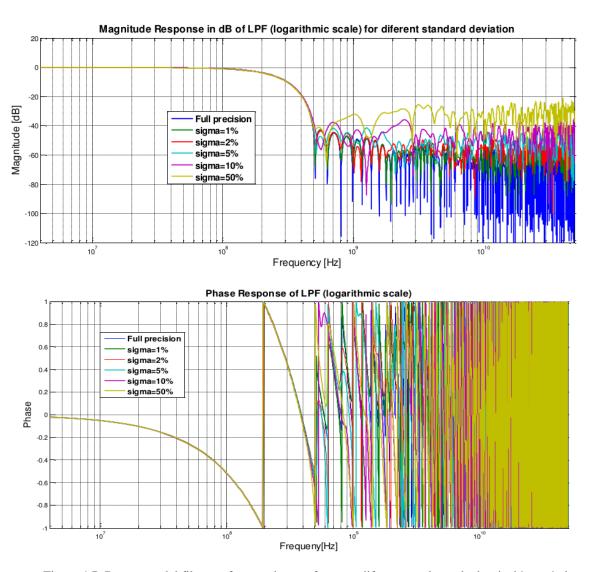

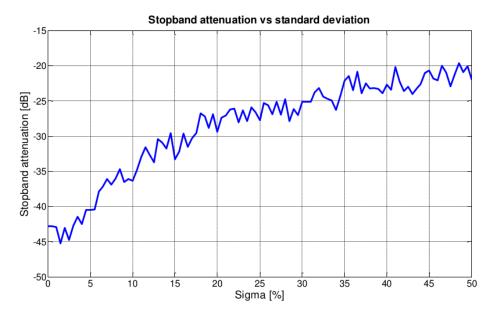

| Desviación estándar                                   | 50 |

| Implementación en Matlab                              | 51 |

| Resultados de las simulaciones                        | 53 |

| Conclusiones                                          | 56 |

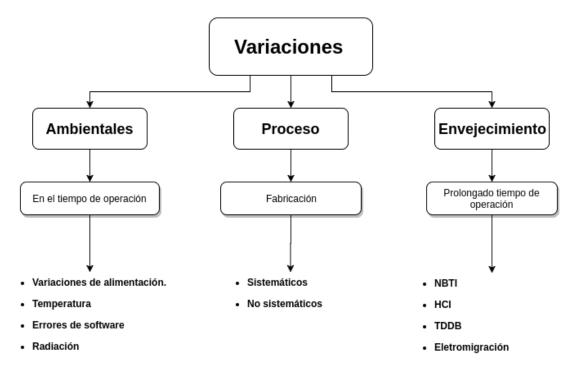

| 5. Estudio de la implementación a nivel de transistor | 59 |

| Introducción                                          | 59 |

| Variaciones en circuitos digitales                    | 60 |

| Impacto de las variaciones en el retardo de los sistemas digitales | 62  |

|--------------------------------------------------------------------|-----|

| Optimización del retardo por las variaciones                       | 62  |

| Análisis estadístico de tiempos                                    | 63  |

| Elementos de retardo asíncrono                                     | 63  |

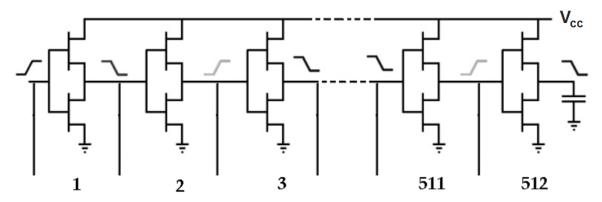

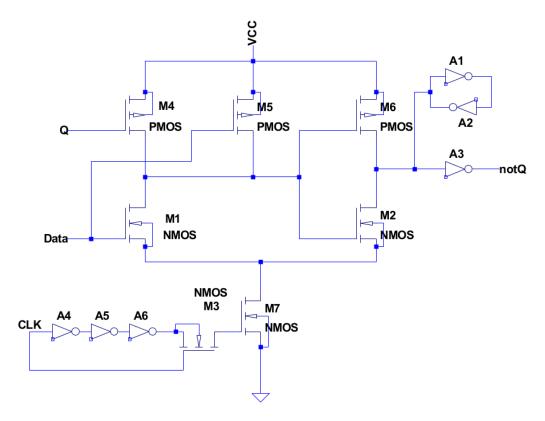

| Implementación                                                     | 64  |

| Simulaciones                                                       | 71  |

| Diezmado y bloque multiplicador                                    | 74  |

| Implementación                                                     | 75  |

| Simulaciones                                                       | 78  |

| Conclusiones                                                       | 80  |

| 6. Conclusiones                                                    | 83  |

| Orden y coeficientes del filtro                                    | 84  |

| Cuantificación del filtro                                          | 85  |

| No linealidades en lo elementos de retardo                         | 86  |

| Estudio de la implementación a nivel de transistor                 | 87  |

| Conclusiones                                                       | 89  |

| Presupuesto                                                        | 93  |

| Costes debidos a los Recursos Humanos                              | 93  |

| Costes de Ingeniería                                               | 93  |

| Costes de amortización                                             | 94  |

| Otros costes                                                       | 95  |

| Coste Total                                                        | 95  |

| BIBLIOGRAFIA                                                       | 97  |

| ANEXO: MATLAB                                                      | 101 |

| ANEXO: HSPICE                                                      | 105 |

#### 1. Introducción

#### Motivación

En los últimos años, la continua evolución de la tecnología *deep-submicron* en los circuitos VLSI (*Very Large Scale of Integration*) ha sido evidente, logrando un impacto significativo en el rendimiento de los mismos [1]. De esta forma, se han alcanzado grandes avances en la familia CMOS (*Complementary Metal Oxide Semiconductor*), especialmente en los transistores MOS de canal corto que han logrado mejorar su transconductancia permitiendo reducir consumos e incrementar velocidades de conmutación, siendo así muy atractivas para aplicaciones de alta velocidad y bajo consumo [2].

Hoy en día, las tecnologías inalámbricas están en constante evolución. Como consecuencia, cada vez aparecen nuevos estándares inalámbricos con mayores exigencias y, por lo tanto, es necesario contar con sistemas electrónicos avanzados de altas prestaciones, tales como ancho de banda, resolución o tasas de transmisión de datos. Entre estos sistemas se encuentran los modernos receptores de radiofrecuencia (RF).

En este sentido, los actuales receptores de RF deben tener unos convertidores analógicos digitales (A/D) con altas resoluciones e inmunidad al ruido. A diferencia de los convertidores A/D convencionales, los convertidores sigma-delta (convertidores de sobremuestreo) ofrecen la posibilidad de utilizar circuitos analógicos más simples a expensas de unos circuitos digitales más sofisticados y de mayor velocidad. Esta reducción

de la complejidad en los circuitos analógicos los hace más insensibles a las no idealidades, las cuales se acentúan en las tecnologías nanométricas.

Por lo tanto, los convertidores Sigma-Delta son capaces de conseguir altas resoluciones gracias al empleo de sobremuestreo y técnicas de *noise shaping*. En algunos casos, para poder conseguir una resolución dada es necesario emplear un sobremuestreo muy elevado, esto hace necesario el diseño de un filtro digital a la salida del modulador con una tasa de muestreo muy alta.

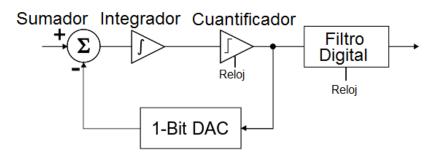

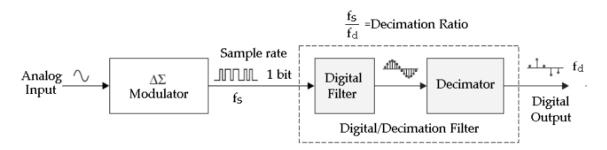

El filtro digital a la salida del modulador sigma-delta es empleado para eliminar todas las componentes de alta frecuencia que están fuera de la banda de la señal y reducir la frecuencia de salida, es decir, diezmar. En la Figura 1.1 se muestra el diagrama de bloques modulador Sigma-Delta básico.

Figura 1.1. Diagrama de bloques de un modulador Sigma-Delta

Por otro lado, la creciente complejidad en los sistemas electrónicos integrados está amplificando un conjunto de fenómenos que degradan su funcionamiento. Estos fenómenos en los sistemas de lógica síncrona pueden ocasionar diferente, inconvenientes en aspectos de energía, distribución de reloj, emisiones electromagnéticas, etc. Con todo esto la lógica síncrona parece alcanzar ciertas limitaciones tecnológicas para resolver estos problemas. En muchos casos, la lógica asíncrona ha demostrado ser una mejor alternativa, proporcionando características interesantes como la inmunidad a los estados metaestables [3], la baja emisión de ruido electromagnético [4], bajo consumo de energía [5] [6], elevadas velocidades de operación y robustez a variaciones de tensión tanto por temperatura como por parámetros en los procesos de fabricación [7] [8] [9].

#### Objetivos y organización de la memoria

Dentro del contexto considerado en el apartado anterior, este proyecto fin de carrera propone la implementación un filtro FIR con alta frecuencia de muestreo combinado con un diezmador, cuyos elementos de retardo se basan en una línea de retardo asíncrona. La línea de retardo asíncrona se realiza a través de una cadena de inversores implementada con tecnología CMOS de 45nm [10].

El principal objetivo del proyecto fin de carrera es estudiar y analizar los efectos de emplear los filtros FIR, teniendo en cuenta las no idealidades asociadas a este tipo de arquitectura, y la viabilidad de emplearlos en conversores Sigma-Delta por sus altas frecuencias de muestreo.

Inicialmente para el desarrollo del proyecto fin de carrera se han establecido unas condiciones de diseño. Estas condiciones de diseño son las especificaciones que debe cumplir el filtro, las cuales están basadas en estudios y diseños previos de filtros para convertidores A/D Sigma-Delta. Por otro lado, también se ha tenido en consideración diseños de subsistemas que han empleado líneas de retardo síncronas. De este modo, durante el transcurso del proyecto fin de carrera se hemos adoptado diferentes decisiones de diseño que permitan cumplir con las especificaciones indicadas para el filtro. En la tabla 1.1 se pueden observar las especificaciones iniciales para el diseño del filtro.

Tabla 1.1 Especificaciones del filtro.

| Tipo de respuesta                 | Paso baja             |

|-----------------------------------|-----------------------|

| Método de diseño                  | Ventana               |

| Tipo de Ventana                   | Kaiser                |

| Beta Kaiser                       | 4                     |

| Frecuencia de Corte               | 250 MHz               |

| Frecuencia de muestreo            | 100 GHz               |

| Reloj local (síncrono)            | 1 GHz                 |

| Atenuación en la banda de rechazo | > 40dB                |

| Banda de transición               | < Frecuencia de corte |

| Rizado                            | < 0.5dB               |

A continuación, se expone la organización de la memoria, indicando los diferentes capítulos realizados.

En el capítulo 2 realizamos una introducción y exponemos los conceptos básicos que consideramos adecuados para obtener una visión general de los convertidores Sigma-Delta y permitan comprender decisiones de diseño relacionadas.

Durante el capítulo 3 se proporciona una descripción general de los filtros digitales y una explicación más detallada del filtro FIR para alta tasa de muestreo con diezmador propuesto.

En el capítulo 4 se analizan los efectos de cuantificación y diezmado en el filtro. También se realiza la implementación del filtro en Matlab para poder estudiarlo más en detalle con las especificaciones seleccionadas, comparando así, el empleo de diferentes números de bits en el filtro y sus respuestas en frecuencia. Además, se estudia los efectos de las no-idealidades en la línea de retardo asíncrona del diseño, empleando simulaciones en Matlab.

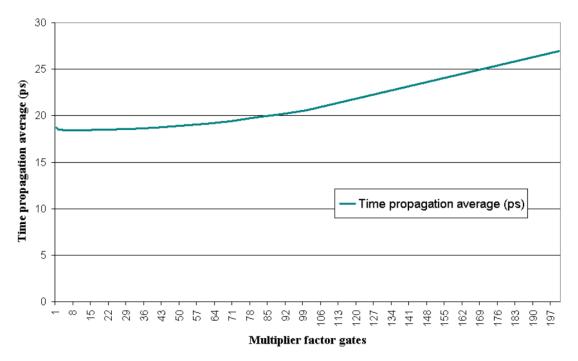

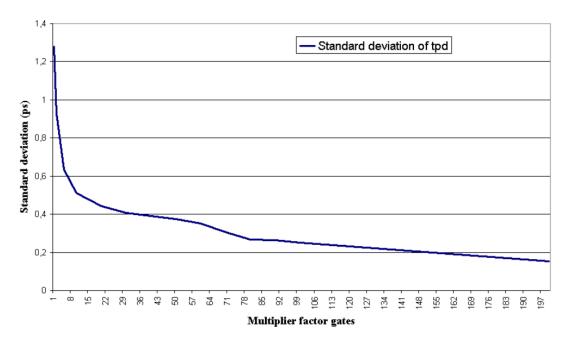

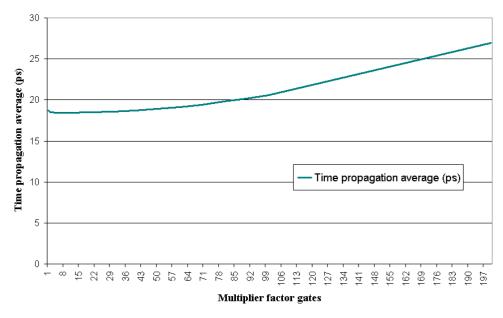

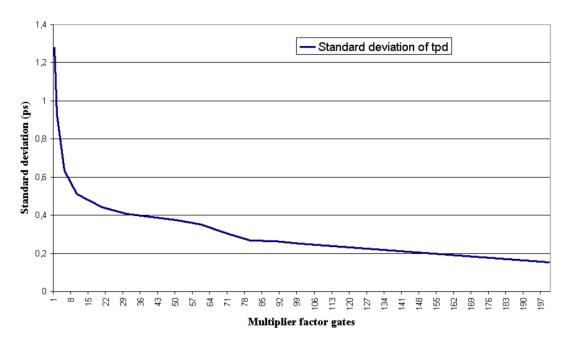

El capítulo 5 estudiamos a nivel de transistor las desviaciones en los tiempos de propagación de la cadena de inversores usada como elemento de retardo del filtro. Además, hacemos diferentes simulaciones que nos van a permitir ajusta la desviación estándar de los elementos de retardo.

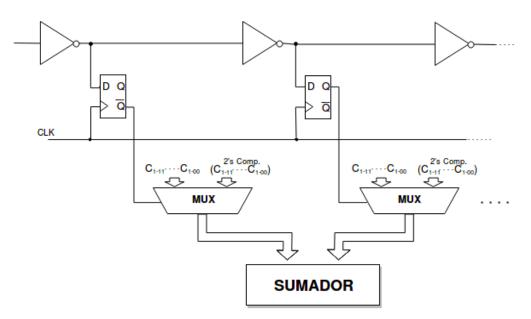

Por otro lado, en el capítulo 5 también diseñamos el bloque diezmador a nivel de transistor para estudiar sus restricciones temporales, muy importantes en la viabilidad del diseño. Para los diseño y simulaciones del capítulo 5 empleamos el programa Hspice.

Finalmente, en el capítulo 6 se exponen las conclusiones y posibles trabajos futuros relacionados con este proyecto fin de carrera.

Para concluir la memoria incluye dos anexos donde se detalla el código empleado en el proyecto. El primer anexo se puede encontrar los scripts de Matlab desarrollados y en el segundo anexo los *netlists* empleados en Hspice.

# 2. Introducción a los convertidores A/D Sigma-Delta

#### Introducción

Durante el capítulo anterior indicamos que el diseño del filtro FIR de alta tasa de muestreo emplea líneas de retardo asíncronas, en lugar de las clásicas líneas de retardo síncronas que suelen usar los filtros digitales.

Mediante las líneas de retardos asíncronas se logra alcanzar altas tasas de muestreo y se evita el uso de elevadas frecuencias de reloj. En capítulos siguiente exponemos otras ventajas del empleo de las líneas de retardo asíncronas y los beneficios en el rendimiento del filtro en el caso del diseño propuesto.

Para entender de manera más clara la necesidad de altas tasas de muestreo en los filtros digitales con el enfoque propuesto en el proyecto fin de carrera, así como la idoneidad de emplear las líneas de retardo asíncronas en los Sigma-Delta con alta relación de sobremuestreo (OSR). Debemos situarnos dentro del ámbito de los convertidores A/D, siendo fundamental explicar el funcionamiento de los convertidores A/D Sigma-Delta.

Con la información expuesta en este capítulo, se puede interpretar de manera más clara las especificaciones de diseño propuestas en el primer capítulo. Debido

principalmente a que ciertas decisiones de diseño están muy relacionadas con los convertidores Sigma-Delta.

#### Convertidor A/D Sigma-Delta

El procesamiento de señales en el dominio digital frente al analógico ofrece importantes ventajas, entre las que se encuentran reducción de área, reducción de consumo, mejor inmunidad al ruido y a la distorsión, o facilidad y flexibilidad a la hora de implementar los diseños [11]. Estas ventajas junto al empleo de DSPs (*Digital Signal Processor*) para su procesamiento, han logrado que los sistemas digitales sean ampliamente usados en muchos y diferentes ámbitos. Para poder realizar el procesamiento en los sistemas digitales se requiere convertir las señales analógicas a digitales mediante convertidores analógicos digitales (ADC).

Aunque existen diferentes tipos de convertidores A/D, entre las arquitecturas más comunes para alta velocidad se pueden destacar el convertidor A/D de pipeline, convertidor A/D *flash*, convertidor A/D de aproximaciones sucesivas y el convertidor A/D de sobremuestreo [12]. En la actualidad la opción más popular empleada en sistemas de audio digital y medición industrial de precisión, es el convertidor A/D de sobremuestreo, también conocido como convertidor A/D Sigma-Delta [13].

Las técnicas de modulación empleadas en los convertidores Sigma-Delta existen desde hace varias décadas atrás [14], pero ha sido en los últimos años cuando han ganado gran popularidad, siendo usadas en sistemas de comunicación como parte de la topología de los convertidores A/D para receptores de RF [15], atribuyéndole algunos de los principales avances tecnológicos recientes en materia de bajo consumo de energía, bajo costo de fabricación y menor exigencia en sus filtros *anti-aliasing* [16].

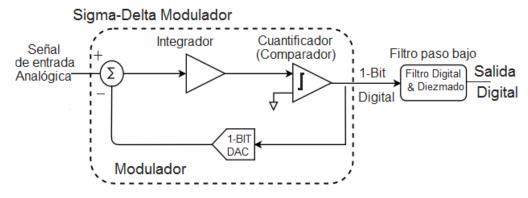

En la Figura 2.1 se muestra un diagrama de bloques de un convertidor A/D Sigma-Delta. En el diagrama se puede observar dos bloques, el modulador Sigma-Delta y un filtro paso bajo con diezmado. Las técnicas empleadas en el modulador sigma-delta permite alcanzar altas resoluciones de conversión usando baja resolución de cuantificación operando a altas velocidades [17], proporcionando así un flujo de bits que es filtrado y diezmado por un filtro paso bajo con diezmador.

Figura 2.1. Diagrama de bloques de un convertidor A/D Sigma-Delta [15]

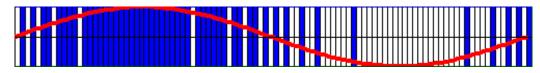

El modulador Sigma-Delta es el núcleo del convertidor. Es el encargado de digitalizar las señales analógicas de entrada y reducir el ruido en las frecuencias más bajas [18]. Como se puede observar en la Figura 2.1, el modulador Sigma-Delta consiste en un integrador seguido de un comparador y un convertidor digital analógico (DAC) en bucle que realimenta el bloque. En el dominio del tiempo, el integrador se encarga de integrar la diferencia entre la señal de entrada y la señal de salida que llega mediante la realimentación del modulador, distribuyendo así el error de cuantificación o ruido en espectro, reduciéndolo en la banda de interés y elevándolo en las frecuencias más elevada [19]. La salida del integrador pasa al comparador actuando como un cuantificador de un bit. Finalmente, a través de la retroalimentación negativa se intenta minimizar la diferencia entre la señal de entrada y la señal de salida del modulador Delta-Sigma, obteniendo así en la salida del modulador, el promedio del seguimiento de la señal de entrada [20] como se puede observar en la Figura 2.2.

Figura 2.2 Señal de entrada y salida en el dominio del tiempo en un modulador Sigma-Delta. [21]

Debido a la técnica que emplea los convertidores Sigma-Delta de sobremuestreo, normalmente deben usar filtros con altas frecuencias de muestreo, aunque la banda de las señales analógicas de entrada se encuentre en frecuencias mucho más bajas. Esta técnica realiza el muestreo a frecuencias mucho más elevadas que la *frecuencia* de *Nyquist*, la cual

es la mínima frecuencia de muestreo necesaria para evitar que se produzca *aliasing*. Mediante el sobremuestreo se reduce el ruido de cuantificación en la banda de la señal de entrada [22].

La relación entre la frecuencia de muestreo empleada en la modulación y la frecuencia de Nyquist se le denomina relación de sobremuestreo ( $Over\ Sampling\ Ratio,\ OSR$ ), definido como la relación entre la frecuencia de muestreo y la frecuencia de Nyquist, como se muestra en la ecuación 2.1. Donde  $f_S$  es la frecuencia de muestreo,  $f_N$  es la frecuencia de Nyquist y  $f_B$  es la banda de frecuencia máxima de la señal de entrada.

$$OSR = \frac{f_s}{f_N} = \frac{f_s}{2 \cdot f_B} \tag{2.1}$$

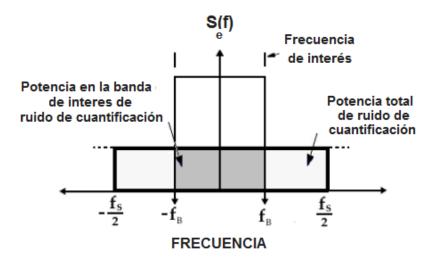

Si analizamos los efectos en potencia que produce la técnica de sobremuestreo empleada en los Sigma-Delta se puede observar la reducción de la potencia de cuantificación en el ancho de banda de la señal de entrada. Esta reducción de potencia es debida a que la potencia del error de cuantificación es distribuida de manera uniforme, extendiéndose sobre el ancho de banda de la frecuencia de muestreo ( $-f_S/2$  a  $+f_S/2$ ). De esta manera la potencia de cuantificación que se encuentra acotada en el rango del ancho de banda de la señal ( $-f_B$  a  $f_B$ ) es menor que el error de cuantificación producido por el ancho de banda total.

Como se muestra en la Figura 2.2 y definido en la ecuación 2.2, podemos calcular la densidad espectral de potencia con el ruido reducido que proporciona el convertidor, denominada como  $P_e$ , donde OSR es la relación de sobremuestreo,  $\Delta$  es el intervalo de cuantificación que a su vez es definido como  $\Delta$  = Vref / 2N,  $S_e(f)$  es la densidad espectral de potencia del ruido total y se define como  $S_e = \Delta^2$  / 12. Finalmente, H(f) es el filtro con diezmado ya realizado y que elimina el ruido de cuantificación en la frecuencia fuera de la banda de la señal  $f_B$  [21] [20].

$$P_{e} = \int_{\frac{f_{s}}{2}}^{\frac{-f_{s}}{2}} S_{e}(f) |H(f)|^{2} df = \left(\frac{\Delta^{2}}{12}\right) \cdot \frac{1}{OSR}$$

(2.2)

Figura 2.2. PSD del error de cuantificación en un convertidor sobremuestreado [15].

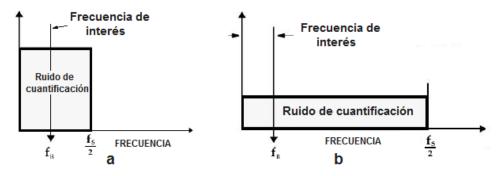

En la figura 2.3 se muestra la diferencia entre el espectro de ruido de cuantificación en un convertidor A/D Sigma-Delta con la frecuencia de muestreo de Nyquist y el espectro de ruido de cuantificación con un convertidor que emplea la técnica de sobremuestreo expuesta.

Figura 2.3. Densidad espectral del ruido de cuantificación del convertidor con Nyquist (a) y con sobremuestreo (b).

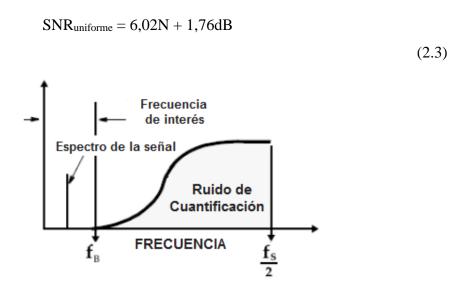

Además del sobremuestreo, los convertidores A/D Sigma-Delta hacen uso de *noise* shaping, técnica encargada de distribuir el error de cuantificación (o también denominado ruido del convertidor). Mediante esta técnica se realiza una reducción de la potencia de error de cuantificación en las frecuencias de la banda de interés, incrementándose en frecuencias más elevadas.

En la figura 2.4 se puede observar el efecto que produce la técnica *noise shaping* en el espectro, donde se puede apreciar que el ruido de cuantificación total se mantiene, aunque concentrado en las frecuencias más elevadas. De este modo es posible obtener altas resoluciones en un ancho de banda relativamente reducido [23], entendiendo como la resolución de un modulador Sigma-Delta a la relación máxima de señal a ruido (SNR) que puede obtenerse en su señal de salida, estimada de forma aproximada en los convertidores Sigma-Delta para una SNR máxima con un cuantificador uniforme con la ecuación 2.3, donde N es el número de bits de cuantificador [24].

Figura 2.4. Espectro de ruido de cuantificación del convertidor Sigma-Delta con noise shaping [14].

Como se puede observar en la figura 2.4, el ruido de cuantificación está concentrado en las frecuencias altas debido a la técnica *noise shaping* que se ha indicado en el párrafo anterior.

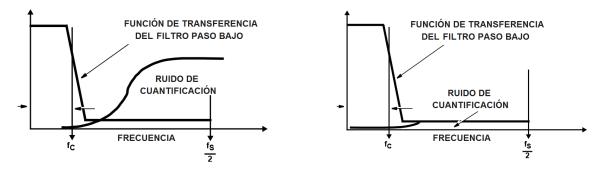

Para eliminar o atenuar el ruido de cuantificación es necesario emplear un filtro capaz de atenuar las frecuencias altas de la señal de salida del modulador. Como se ha mencionado al inicio del capítulo, la señal de entrada después de ser procesada por el modulador Sigma Delta, (donde es sobremuestreada y se le aplica la técnica *noise shaping*), pasa a través del filtro digital con diezmado como se muestra en la Figura 2.1. La función del filtro digital es proporcionar una corte lo más brusco posible en las frecuencias superiores, con el objetivo principal de eliminar el ruido de cuantificación que se encuentra fuera de la banda de interés [25]. En la Figura 2.5 se muestra el espectro de la señal y el

filtro digital, antes y después eliminar el ruido de cuantificación que el modulador desplazó hacia las frecuencias más altas.

Figura 2.5. Espectro del ruido de cuantificación y filtro, antes (derecha) y después de ser filtrado (izquierda) [15].

#### **Conclusiones**

En este capítulo se han estudiado los aspectos más relevantes de los convertidores analógico/digital Sigma-Delta, centrándose en las técnicas que emplea y la relación de las altas tasas de muestreo y la caracterización del ruido, lo que nos permite entender mejor las especificaciones de diseño, como pueden ser el uso de un filtro paso bajo, la alta tasa de muestreo del filtro o la frecuencia de corte muy distancia de la frecuencia máxima de muestreo. Por otro lado, también ayudará a comprender algunas decisiones de diseño adoptadas durante los siguientes capítulos del proyecto fin de carrera para la implementación del filtro digital.

#### 3. Filtros digitales

#### Introducción

En los últimos años los procesadores digitales de señales (DSPs) han incrementado notablemente su presencia en productos de telecomunicaciones y electrónica, debido en gran parte a la mejora de la tecnología VLSI. Estos dispositivos se emplean en numerosos ámbitos, como pueden ser las comunicaciones inalámbricas, el procesamiento de imagen o audio, etc.

Los filtros digitales son una parte muy significativa de los DSPs [26]. Estos permiten la separación de alguna señal que ha sido mezclada o la recuperación de una señal que ha sufrido distorsión [27] [28].

Figura 3.1. Diagrama de bloques de un convertidor A/D Sigma-Delta con filtro diezmador digital (bloques sombreados) [29].

Aunque existen diferentes formas de implementar un filtro digital, en este proyecto se ha propuesto la implementación de un filtro FIR con líneas de retardo asíncronas. Este será empleado como filtro diezmador en un convertidor A/D sigma-delta con altos requerimientos en la tasa de muestreo, como se puede observar en la Figura 3.1

Como introducción, en este capítulo se realiza una descripción general de los filtros digitales, indicando sus propiedades y características principales. Además, se expone el proceso de diseño de los filtros con respuesta al impulso de longitud finita (FIR).

Posteriormente, se desarrolla la arquitectura del filtro FIR propuesto indicando todos los requisitos que debe presentar. Para ello, se calcula el orden necesario del mismo y sus coeficientes. Esto se hará considerando un filtro ideal, sin valorar otras consideraciones como la cuantificación o no linealidades las cuales se estudiarán en el siguiente capítulo.

#### Filtros digitales

El filtro digital es un tipo de filtro que opera con señales discretas y cuantificadas, puede implementarse mediante software en ordenadores con datos almacenados en memoria o con circuitos digitales específicos, estos reciben una secuencia discreta de números (señal de entrada) que es transformada mediante un algoritmo en otra secuencia discreta de números (señal de salida), que tendrá un espectro en el dominio de frecuencia modificado [30]. Normalmente se encuentran en los procesadores digitales de señales (DSPs) de propósito general para aplicaciones de audio o circuitos integrados de aplicación específica (ASIC) en aplicaciones con altas tasas de muestreo [31].

El filtrado de una señal se puede realizar mediante dos tipos de filtros digitales, denominados filtro FIR (*Finite Impulse Response* o Respuesta Finita al Impulso) o filtro IIR (*Infinite Impulse Response* o Respuesta Infinita al Impulso). Aunque en el presente proyecto fin de carrera el tipo escogido en las especificaciones iniciales es de tipo FIR, dedicaremos un apartado a los filtros IIR a modo de introducción y con el fin de conocer las diferencias con los filtros FIR.

#### Respuesta finita al impulso (FIR)

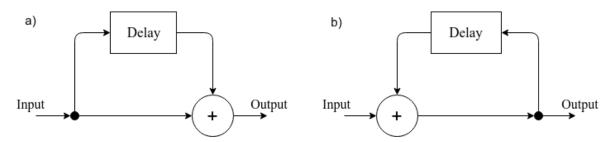

En los filtros digitales se pueden distinguir dos tipos de funcionamiento, filtro norecursivo y filtro recursivo. En el caso de los filtros con respuesta finita al impulso, el tipo de funcionamiento es no-recursivo y este viene definido cuando la salida está exclusivamente calculada a partir de los valores de entrada (Y[n]=X[n]+X[n-1]+ X[n-2]...), como se puede apreciar en la Figura 3.2a.

Por otro lado, los filtros digitales recursivos, como veremos en el apartado de los filtros digitales IIR, además de los valores de entrada para calcular la salida, se necesitan emplear valores previos de salida (Y[n-1], Y[n-2]...), como se puede observar en la Figura 3.2 b.

Figura 3.2. Diagrama de bloques de los dos tipos de filtros digitales: (a) no-recursivo (FIR) y (b) recursivo (IIR).

Los filtros con respuesta finita al impulso son filtros digitales caracterizados por la respuesta obtenida al aplicar una señal impulso a la entrada, la cual será de duración finita. Además, como se comentó en el párrafo anterior la salida depende exclusivamente de las entradas actuales y anteriores. Así, un filtro de longitud N puede ser definido como muestra la ecuación 3.1:

$$y(n) = b_0 x(n) + b_1 x(n-1) + \dots + b_{N-1} x(n-N+1) = \sum_{k=0}^{N-1} b_k x(n-k)$$

(3.1)

donde b<sub>k</sub> son los coeficientes del filtro y el orden del filtro viene dado el número de coeficientes N.

Además, se puede obtener la expresión en el dominio temporal mediante la ecuación 3.3. En la misma, la salida del filtro y(n) es obtenida mediante la convolución de la entrada x(n) con la respuesta al impulso h(n) (ecuación 3.2).

$$y(n) = \sum_{k=-\infty}^{+\infty} h(k) \cdot x(n-k) \quad con \begin{cases} 0 & k < 0 \\ h(k) & 0 \le k < N \\ 0 & k \ge 0 \end{cases}$$

$$y(n) = \sum_{k=0}^{N-1} h(k) \cdot x(n-k)$$

(3.2)

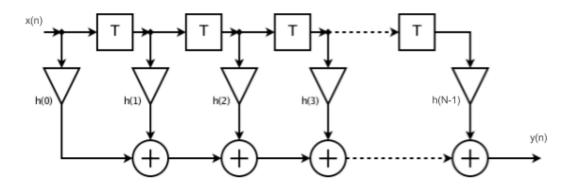

Siguiendo la ecuación 3.3 se puede representar la estructura básica de un filtro FIR como se aprecia en la Figura 3.2.

Figura 3.2. Estructura básica de un filtro FIR, forma directa I.

Teniendo en cuenta la ecuación 3.1 y empleando como entrada la señal impulso se puede deducir la respuesta al impulso con la ecuación 3.4.

$$h(n) = \sum_{i=0}^{N} b_i \cdot \delta(n-i) = b_n$$

(3.4)

Por otro lado, la transformada de Fourier de una respuesta impulsional de un filtro corresponde a su función de transferencia y permite caracterizar a los filtros en el dominio frecuencial. En el caso de un filtro FIR se puede observar su función de transferencia en la ecuación 3.5, la cual también puede ser expresada en términos de los coeficientes b<sub>n</sub> si consideramos la ecuación 3.4.

$$h(n) = \sum_{n=-\infty}^{\infty} h[n] \cdot z^{-n} = \sum_{n=0}^{N} b_n \cdot z^{-n}$$

(3.5)

Dadas las ecuaciones expuestas para los filtros FIR, se puede deducir que todos los polos se encuentran localizados en el origen, indicando así que son estables. Otra ventaja a considerar es que nos permite diseñar el filtro con fase lineal [32].

Entre las desventajas de los filtros FIR se encuentra la necesidad de orden elevado para cumplir ciertas especificaciones de diseño y lograr que la respuesta del filtro sea la deseada, ocasionando un mayor tiempo de cómputo, así como un aumento de componentes en el caso de implementaciones electrónicas específicas.

Para el diseño de un filtro FIR se debe seleccionar los coeficientes (b<sub>n</sub>) adecuados que cumplan con las especificaciones de diseño dadas. Existen diferentes métodos para el cálculo de los coeficientes de entre los cuales los más empleados son el método de diseño de ventanas, el método *equiripple*, el método de muestreo de frecuencia y el método de mínimos cuadrados [26]. A continuación, se realiza una breve descripción de cada uno de los métodos comentados:

- El método de diseño de ventanas implementa la respuesta en frecuencia ideal deseada, definida con la respuesta al impulso correspondiente, la cual se calcula con la multiplicación de la respuesta al impulso deseada en el tiempo por la función ventana. Las funciones ventanas se basan simplemente en truncar la respuesta del impulso para obtener una aproximación al filtro FIR causal. Dependiendo del tipo de ventana usado para el truncamiento se pueden modificar ciertos parámetros (ancho de transición, rizado pasabanda, atenuación máxima en la banda de rechazo, relación lóbulo principal y lóbulos laterales) en la respuesta en frecuencia del filtro [26].

- El método *equiripple* (rizado uniforme) emplea una técnica indirecta para encontrar los coeficientes del filtro óptimos, donde los valores son ajustados para conseguir un rizado que se mantenga uniforme en toda la banda. Este método utiliza un procedimiento de optimización más eficiente para minimizar el ancho de transición en relación con el rizado de la banda de paso y la de rechazo [33].

- El método de muestreo en frecuencia consiste simplemente en muestrear uniformemente la respuesta de frecuencia deseada y realizar la inversa de la transformada de fourier discreta (DFT) para obtener la correspondiente respuesta al impulso del filtro [34]. Generalmente, el método de muestreo proporciona buen rendimiento con un número suficiente de frecuencias muestreadas, pero el rendimiento es limitado cuando la banda de transición deseada es muy estrecha [35].

- El método de aproximación por mínimos cuadrados (también denominado como minimización del error por mínimos cuadrados) es similar al de muestreo en frecuencia, pero en este caso se controla la respuesta mediante la integral del error al cuadrado respecto a la respuesta deseada entre los puntos muestreados, considerando un número de puntos muestreados mayor que el orden del filtro. Como la energía de la señal está relacionada con el cuadrado de la misma, este método es apropiado para optimizar el diseño del filtro [36].

#### Respuesta infinita al impulso (IIR)

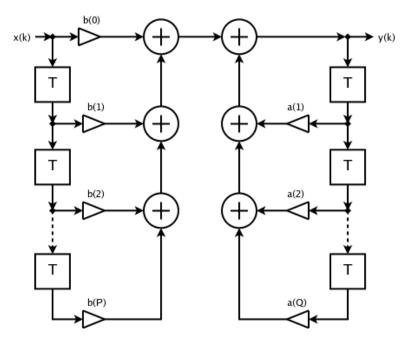

A diferencia de los filtros FIR, los filtros IIR son filtros digitales de tipo recursivo los cuales presentan una respuesta al impulso infinita o, dicho de otra manera, si la entrada del filtro IIR es una señal impulso, en la salida se tendrá un número infinito de términos no nulos, impidiendo así su retorno al estado de reposo.

La expresión matemática de los filtros IIR está indicada en la ecuación 3.6, y se puede observar que la salida del filtro  $(y_n)$  depende de las entradas actuales  $(x_n)$ , pasadas  $(x_{n-k})$  y las salidas de instantes anteriores  $(y_{n-k})$ .

$$y_n = b_0 \cdot x_n + b_1 \cdot x_{n-1} + \dots + b_N \cdot x_{n-N} - a_1 \cdot y_{n-1} - a_2 \cdot y_{n-2} - \dots - a_M \cdot y_{n-M}$$

(3.6)

donde  $a_k$  y  $b_k$  son los coeficientes del filtro y el orden viene determinado por el máximo entre los valores de M y N, que a su vez indica el número de polos y ceros en la función de transferencia.

Aunque existen numerosas implementaciones posibles para los filtros IIR, en la Figura 3.3 se muestra una estructura básica, la cual cumple la ecuación 3.6 y permite comprender de manera más adecuada su funcionamiento.

Figura 3.3. Estructura básica para filtros IIR.

Se puede observar que la estructura de la Figura 3.3 cumple con la ecuación 3.6. Además, si se aplica la transformada Z a la ecuación es posible caracterizar la función de transferencia como se puede observar en la ecuación 3.7.

$$H(z) = \frac{\sum_{N}^{K=0} b_k \cdot z^{-k}}{1 + \sum_{M}^{k=1} a_k \cdot z^{-k}}$$

(3.7)

Al contrario que los filtros digitales FIR, en la función de transferencia de los filtros IIR existe denominador, lo que introduce ceros que pueden causar inestabilidades, comprometiendo así la estabilidad y causalidad del sistema. Otro de los inconvenientes de los filtros IIR es la dificultad de tener fase lineal, solo posible con técnicas más complejas que acaban añadiendo más coeficientes. Por otro lado, los filtro IIR pueden lograr las mismas exigencias que los filtro FIR, pero con un número de coeficientes menor, reduciendo la carga computacional.

#### Características de los filtros digitales

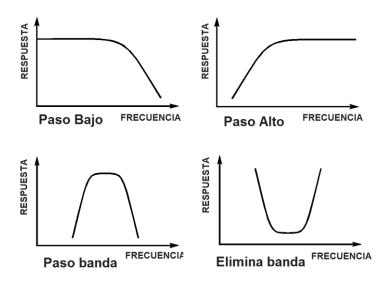

Los filtros digitales pueden ser clasificados en base a la respuesta en el dominio de la frecuencia. Esta clasificación comprende cuatro tipos básicos según sea la posición relativa de las bandas de paso y las bandas atenuadas. Los cuatro tipos existentes son filtro paso bajo, filtro paso alto, filtro paso banda y filtro elimina banda [37].

- El filtro paso bajo permite el paso de señal a baja frecuencia (banda de paso) mientras atenúa las frecuencias superiores a la frecuencia de corte del filtro.

- El filtro paso alto presenta un comportamiento complementario al paso bajo, siendo las frecuencias bajas las atenuadas y las frecuencias altas las paso banda.

- Los filtros paso banda tienen un rango de frecuencias definido por las frecuencias de corte superior e inferior, permitiendo pasar las frecuencias que se encuentran dentro del rango indicado.

- El filtro elimina banda presentan un comportamiento complementario a los paso banda, siendo así las frecuencias del rango definido las atenuadas.

En la Figura 3.4 podemos ver los cuatro tipos de filtro comentados, según el módulo de su respuesta frecuencial.

Figura 3.4. Tipos de filtros.

Idealmente la respuesta en frecuencia de los filtros viene caracterizada por una ganancia máxima para las frecuencias de interés (denominada también banda de paso), la cual en los filtro FIR es plana y sin atenuación (0 dB), y una mínima para las frecuencias

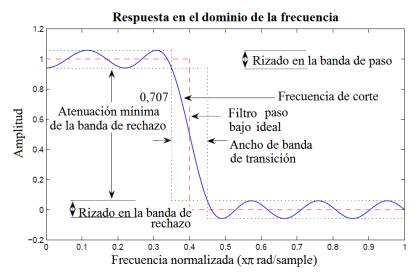

no deseadas (denominadas también banda de rechazo), las cuales presentan una atenuación. Además de esta característica, existen varios parámetros que nos permiten caracterizar la respuesta frecuencial del filtro de una manera más específica, entre los que se pueden destacar:

- Frecuencia de corte. Frecuencia a la cual la amplitud de la señal sufre una atenuación de 3 dB (la señal se reduce a 0.707). En el caso de filtros paso banda o filtros elimina banda, existen dos frecuencias de corte, frecuencia de corte inferior y frecuencia de corte superior. Como su denominación indica la inferior será la frecuencia de corte con frecuencia más baja que la superior.

- Ancho de la banda de transición. Conjunto de frecuencias comprendidas entre la banda de paso y la banda de rechazo.

- Rizado. Indica la presencia de una ondulación no deseada en la banda de paso/rechazo o en ambas.

- Atenuación mínima en banda de rechazo. Valor de la atenuación mínima que el filtro es capaz de proporcionar en la banda de rechazo.

En la Figura 3.5 se puede observar los parámetros comentados de los filtros sobre una respuesta frecuencial común de un filtro paso bajo.

Figura 3.5. Respuesta en frecuencia de un filtro paso bajo (indicando los parámetros)

#### Filtro FIR asíncrono

En las estructuras básicas de filtros FIR como la mostrada en la Figura 3.2, se pueden apreciar los elementos de retardos clásicos que actúan como registros síncronos, encargados de introducir un retardo a la señal de entrada. La mayoría de los diseños lógicos actuales emplean este tipo de registros síncronos coordinados por una señal de reloj y para su funcionamiento se basan principalmente en dos suposiciones: todas las señales son binarias y el tiempo es discreto. Esto facilita el diseño lógico y permite simplificarlo [38].

Aunque actualmente el desarrollo de circuitos síncronos domina los diseños en la industria de semiconductores, existen importantes limitaciones en la sincronización cuando son necesarias altas frecuencia de muestreo, lo cual dificulta de manera notable el rendimiento y el diseño [39]. Por otro lado, la lógica asíncrona tiene propiedades inherentes que pueden ser utilizadas para mejorar aspectos del diseño, como reducción de consumo, alta velocidad de operación, robustez ante variaciones de alimentación, temperatura y parámetros de proceso de fabricación [40].

De esta forma, para cumplir con las especificaciones descritas en el capítulo 1 de este proyecto fin de carrera, principalmente con la alta tasa de muestreo indicada para el filtro digital, se propone una implementación asíncrona de bajo consumo para los elementos de retardos del mismo. Los bloques restantes se mantienen síncronos, como los empleados en los filtros digitales convencionales, de esta manera se tendrá una combinación de bloques síncronos y asíncronos en la implementación, intentando conseguir las ventajas del diseño síncrono con la velocidad de muestreo que se puede lograr con el bloque asíncrono.

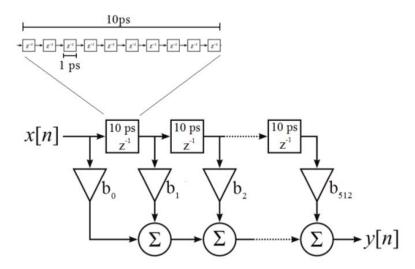

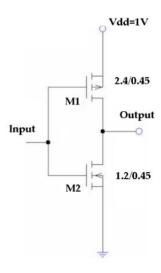

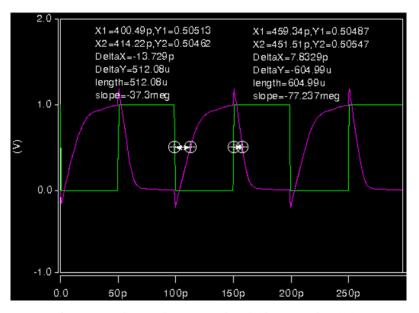

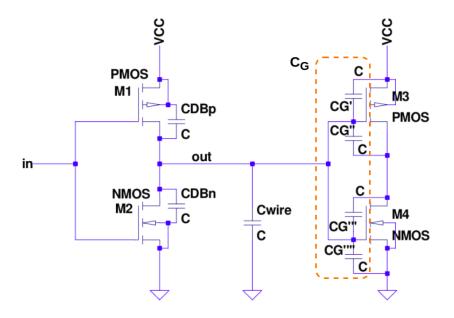

Para el bloque compuesto por los elementos de retardo del filtro FIR, hemos empleado líneas de retardo asíncronas mediante una cadena de inversores. Según las especificaciones iniciales de diseño, la tecnología CMOS empleada, PTM de 45nm [10], permite retardos de propagación alrededor de los 10 ps. como se estudiará en más profundidad en el capítulo 5, permitiendo operar alrededor de los 100 GHz. Los bloques síncronos del filtro FIR propuesto emplean flip-flops y multiplexores, siendo su frecuencia de trabajo menor, 1

GHz. El cambio de frecuencia será realizado por el diezmador como se explica en el apartado 3.3.4 del presente capítulo.

Como se ha comentado, el filtro con alta tasa de muestreo y diezmado propuesto está implementado mediante un filtro tipo FIR, siendo esta una condición inicial del diseño. Esto se debe principalmente a que el diseño está basado en el uso de líneas de retardo asíncronas y las arquitecturas de los filtros IIR dificultan notablemente el empleo de dichas líneas de retardo.

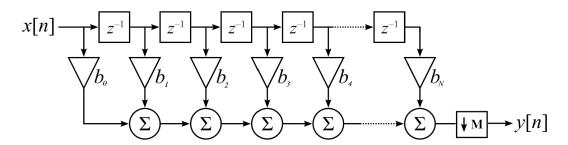

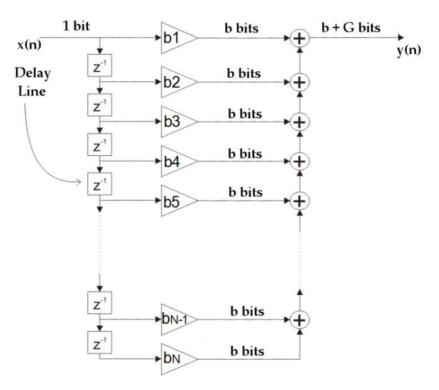

El diseño del filtro FIR está basado en la arquitectura de forma directa, la cual comprende tres tipos de elementos básicos: sumador, multiplicador y unidad/bloque de retardo.

En la Figura 3.6 se puede observar la estructura del filtro FIR de forma directa y los elementos básicos que la componen, donde los valores b<sub>k</sub> son los coeficientes del filtro usados por el multiplicador. De esta manera la salida y[n] será la suma de las muestras retardadas multiplicadas por el coeficiente correspondiente. Además, se puede observar en la Figura 3.6 que presenta un bloque diezmador justamente antes de la salida del filtro FIR, el cual realiza el diezmado, reduciendo así la frecuencia de muestreo original a una menor para evitar sobremuestreo en la salida.

Figura 3.6. Estructura básica de forma directa en un filtro FIR.

El diseño propuesto en el presente proyecto ha modificado la clásica estructura de la forma directa de la figura anterior reemplazando los elementos de retardo por líneas de retardo asíncrono y, modificando la posición del bloque diezmador que ahora se ubica en las entradas de los bloques multiplicadores en lugar de la salida del filtro, como se puede apreciar en la Figura 3.7.

Figura 3.7. Estructura de filtro FIR propuesta, con diezmado más eficiente y los elementos de retardos con una línea de retardo asíncrona (empleando inversores).

Por otro lado, como se indicó en las especificaciones del capítulo 1, el filtro debe usar el método de ventana para su diseño. Sin llegar a ser el método más óptimo, es un método rápido, fácil de usar y robusto [41], facilitando de esta manera el estudio de los efectos de emplear líneas de retardo asíncronos en el diseño del filtro FIR. El tipo de ventana empleado es el Kaiser, el cual proporciona el parámetro, que permite mejorar el rizado o la banda de transición, de forma que la mejora de una de ellas significa la degradación de la otra. Por ello, es necesario llegar a un compromiso entre las dos propiedades, de tal forma que se cumplan los requisitos propuestos al inicio, sobre todo en materia de banda de transición, evitando el posible *aliasing* durante el diezmado de la señal, como se verá más en profundidad en las siguientes secciones del capítulo.

El cálculo de los coeficientes y el ajuste de las especificaciones del filtro se han realizado mediante la herramienta *toolbox Signal Processing* de Matlab, el cual proporciona un conjunto de funciones y *apps* para generar, medir, transformar, filtrar y visualizar señales. En el apartado 3.3.2 se explica más en profundidad el uso del *toolbox* para el diseño del filtro. Recalcar que durante este capítulo los cálculos y simulaciones de diseño son basadas en la implementación ideal del filtro, sin considerar factores no-lineares o la cuantificación del mismo, que será estudiada en el siguiente capítulo.

#### Diezmado

En el capítulo 2 se pudo apreciar la importancia del proceso de sobremuestreo en los actuales convertidores analógicos/digitales Sigma-Delta [41], lo cual implica que la señal

de salida de los mismos tenga una frecuencia de muestreo muy superior a la necesaria. Por lo tanto, para reducir este sobremuestreo es necesario un diezmador, encargado reducir el número de muestras de la señal en tiempo discreto, equivalente a una reducción en la frecuencia de muestreo.

Sin embargo, antes de diezmar la señal de salida del convertidor será necesario filtrar la misma para evitar el fenómeno de *aliasing* (filtro *anti-aliasing*), debido a que dos señales separadas por un múltiplo de la frecuencia de muestreo son indistinguibles.

Por tanto, al usar el diezmador y modificar la frecuencia de muestreo existe el riesgo de alterar las frecuencias de la banda de interés, distorsionando así la señal original e impidiendo una futura reconstrucción exacta de la misma [42]. Así, en aplicaciones con convertidores A/D sigma-delta, el filtro diseñado cumplirá con la función de filtro *antialiasing*, requerido para este tipo de convertidores A/D.

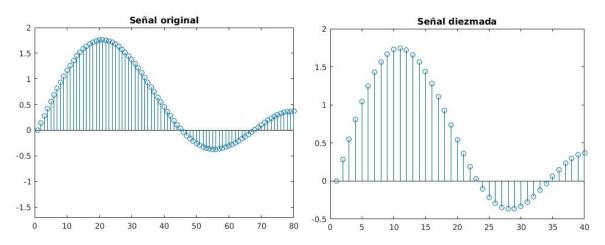

Esta disminución de la frecuencia de muestreo se lleva a cabo tomando una de cada M muestras y desechando las M-1 muestras intermedias. En la Figura 3.8 se puede observar la relación entre la entrada y la salida en tiempo discreto del bloque diezmador el efecto del diezmado en las muestras de una señal discreta de entrada con frecuencia  $f_s$  y su señal de salida discreta con la nueva frecuencia de muestreo  $f_s$  =  $f_s$  /2.

$$x[n]$$

$\longrightarrow$   $y[n] = x[nM]$

Free. muestreo entrada :  $f_z$  Free. muestreo salida  $f_z = \frac{f_z}{M}$

Figura 3.8. Entrada y salida del bloque diezmador y conversión de frecuencias de muestreo.

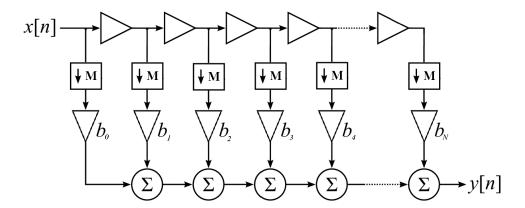

En la Figura 3.9 se puede observar de manera más clara el efecto que produce en las señales discretas el diezmado, en este caso un diezmado con factor de M=2.

Figura 3.9. Ejemplo de diezmado en una señal discreta con un factor de M=2.

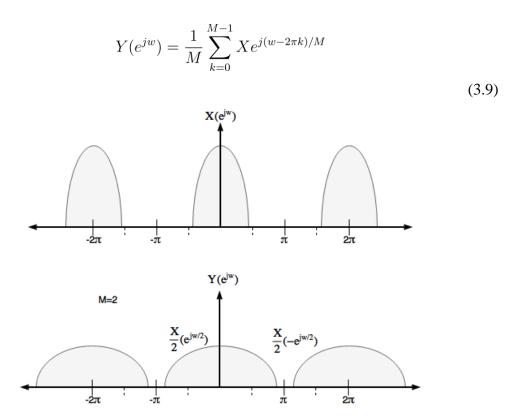

La caracterización en el dominio de la frecuencia es algo más compleja. Aplicando la transformada Z obtenemos la ecuación 3.8 y, evaluando la misma sobre la frecuencia unidad, obtenemos la ecuación 3.9 [35], siendo esta una sumatoria de espectros de la señal de entrada desplazados uniformemente y escalados un factor 1/M como se puede observar en la Figura 3.10, en este caso con un factor M=2.

Figura 3.10. Espectros de la señal original (superior) y la señal diezmada (inferior) con un factor M=2.

Con el fin de evitar el efecto del *aliasing* comentado, el diseño debe cumplir el Teorema de Nyquist, el cual determina que la frecuencia de muestreo debe ser superior al doble de la máxima frecuencia a muestrear [43]. De este modo y en un filtro paso bajo con las especificaciones descritas en el capítulo 1 y con bandas de transición tan elevadas, el filtro debe mantener en la banda de atenuación las frecuencias que sobrepasen el doble del valor de la frecuencia de muestreo que resulta una vez la señal diezmada, o dicho de otra manera, la frecuencia de muestreo mínima, una vez diezmada, debe ser superior al doble de la suma de la frecuencia de corte más la banda de transición, pudiendo ser comprobado con la ecuación 3.10.

$$\frac{F_z}{M} \ge 2 \cdot (Frecuencia\ de\ corte\ + banda\ de\ transición)$$

(3.10)

donde F<sub>s</sub> es la frecuencia de muestreo del filtro y M es el factor de sobremuestreo del filtro, el cual está definido por la división entre la frecuencia de muestreo del filtro asíncrono (F<sub>s</sub>) y la frecuencia de muestreo síncrona encargada del diezmado (F'<sub>s</sub>), calculado con la ecuación 3.11.

$$M = \frac{F_s}{F'_s} = \frac{100 \, GHz}{1 \, GHz} = 100$$

(3.11)

Así, con el factor de sobremuestreo calculado en la ecuación 3.11 y obteniendo los valores de las especificaciones de diseño indicadas en el capítulo 1 (frecuencia de corte, banda de transición y frecuencia de muestreo) es posible sustituir los valores de la ecuación 3.10 y comprobar que se cumple con las exigencias del teorema del muestreo de Nyquist, como se puede observar en la ecuación 3.12. Finalmente, en el apartado 3.3.2 se tendrá en cuenta que se cumple la especificación de banda de transición y frecuencia de corte, para el cálculo de los coeficientes y evitar que se produzca el *aliasing* en el diezmado.

$$\frac{100 \text{ GHz}}{100} \ge 2 \cdot (250 \text{ MHz} + 250 \text{ MHz})$$

(3.12)

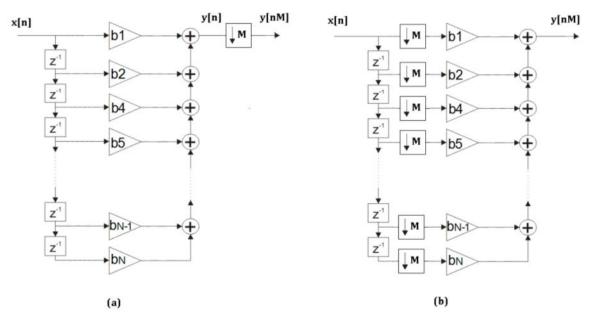

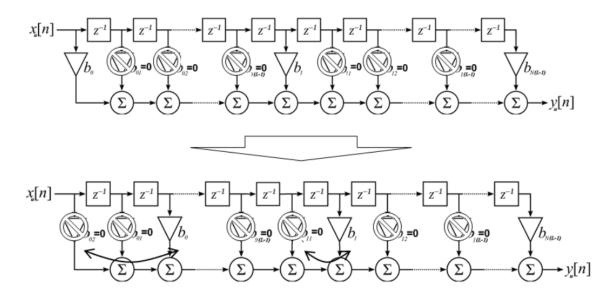

Como se adelantó en el apartado 3.3 del presente capítulo, la implementación del bloque diezmador ha sido modificada respecto a la estructura de filtro FIR de forma directa tal como se aprecia en la Figura 3.11a. La decisión de emplear una estructura diferente a la clásica es debido a que los bloques sumadores y multiplicadores del diseño propuesto operan de forma síncrona, al contrario de los bloques retardo del filtro que operan de forma asíncrona, siendo necesario una señal de reloj sólo para los bloques síncronos.

Con la estructura clásica, la señal de reloj tendría que operar a una frecuencia cercana a los 100 GHz (la frecuencia de muestreo del filtro) puesto que también es empleada en los bloques de retardo. Esta frecuencia es demasiado elevada y, por lo tanto, emplear bloques de retardo asíncronos nos permitirá lograr un filtro digital con una frecuencia de muestreo alta sin necesidad de usar una señal de reloj a esas frecuencias.

Para evitar esta limitación, la estructura propuesta implementa el bloque de retardo del filtro, previo a los bloques multiplicador y sumador, reduciendo la frecuencia de muestreo en un factor de 100 como se calculó en la ecuación 3.11 y, consecuentemente, la frecuencia de operación de estos bloques. Aunque esta nueva estructura requiere más bloques (lo cual implica más lógica/transistores), el consumo es reducido al operar a una frecuencia menor, logrando así ser realizable y mejorando la eficiencia del filtro digital. En la Figura 3.11b se puede observar la estructura del filtro FIR propuesta, donde se puede apreciar la nueva ubicación de los bloques diezmadores.

Figura 3.11. a) Filtro FIR con estructura forma directa I con diezmador. b) Filtro FIR con estructura forma directa I con diezmador ubicado de forma eficiente.

### Implementación del filtro digital en Matlab

Para realizar el filtro digital con las especificaciones que se indican el capítulo 1, el filtro ha sido implementado mediante la herramienta software Matlab. Matlab puede ampliar sus capacidades mediante cajas de herramientas, también conocidos como *toolbox*. En el caso de nuestro diseño se ha empleado el *toolbox Signal Processing*, que proporciona técnicas para diseñar, simular y analizar filtros digitales tanto en punto fijo como en punto flotante, lo que permite generar, medir, transformar, filtrar, visualizar señales o comparar señales en los dominios de tiempo, frecuencia y tiempo-frecuencia.

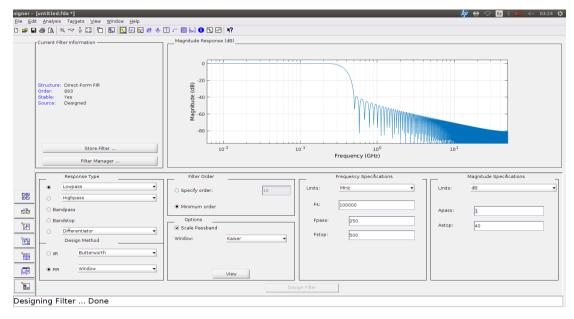

En este capítulo del proyecto, tanto los coeficientes como el orden del filtro se ha calculado mediante varias funciones (fir1, freqz) y herramientas (fvtool), así como la aplicación *Filter Designer*, todos componentes de la *toolbox Signal Processing*. La aplicación *Filter Designer* permite diseñar y analizar filtros digitales mediante un interfaz gráfico muy amigable, donde se deben insertar los parámetros que se desea que cumpla el filtro digital a diseñar. En la Figura 3.12 se puede observar el interfaz gráfico que proporciona la aplicación *Filter Designer* de Matlab.

3.12. Aplicación Filter Designer de Matlab.

Además de obtener las diferentes respuestas del filtro y sus coeficientes con los valores introducidos, la aplicación permite emplear varios tipos de análisis o ajustar la cuantificación para estudiar su respuesta al impulso, como se explicará con profundidad en el siguiente capítulo. En nuestro caso para tener una primera aproximación al diseño del filtro se realizaron varios tests con la aplicación *Filter Designer*, rellenando los campos necesarios con los valores de las especificaciones inicialmente dadas, obteniendo una respuesta en frecuencia al impulso como se muestra en la figura 3.12.

Por otro lado, con el fin de facilitar el manejo del filtro y representarlo gráficamente de manera más precisa, se ha empleado la función fir1, la cual nos permite obtener coeficientes del filtro, la función freqz que devuelve la respuesta en frecuencia del filtro y con la ayuda de la herramienta fvtool (*Filter Visualization Tool*) se podrá visualizar gráficamente las respuestas del filtro obtenidas. En la Tabla 3.1 se indican las funciones con los parámetros necesarios para su uso.

Tabla 3.1. Conjunto de funciones y herramientas empleadas en Matlab.

| Función                         | Sintaxis                                   | Argumentos                                                                     |

|---------------------------------|--------------------------------------------|--------------------------------------------------------------------------------|

| Obtener coeficientes del filtro | fir1(Orden,Wn,Ventana(Orden+ 1,Parámetro)) | Orden: Orden del<br>filtro.bWn:Restricciones en<br>frecuencia. Ventana:Tipo de |

|                                                 |                           | ventana. Parámetro: Forma enventanado.                                                  |

|-------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------|

| Obtener respuesta en frecuencia del filtro      | freqz(B <sub>2</sub> A,N) | <ul><li>B, A: Coeficientes del filtro.</li><li>N: Número de puntos evaluados.</li></ul> |

| Representar gráficamente la respuesta de filtro | fvtool(Hd)                | Hd:Respuesta del filtro (obj)                                                           |

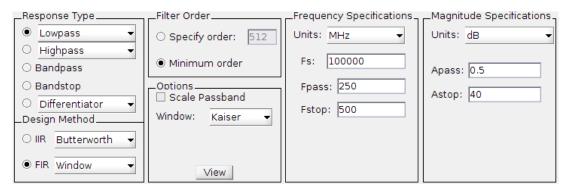

Inicialmente, mediante la aplicación *Filter Designer* y empleando la opción '*Minimum order*' se ha realizado una estimación del posible orden del filtro. Para ello se ha introducido los parámetros necesarios, como son el tipo de respuesta del filtro (*Response Type*), método de diseño del filtro FIR (*Design Method*), tipo de ventana (*Options*), frecuencia de muestreo (Fs), frecuencia final de la banda de paso (*Fpass*), frecuencia inicial de la banda de rechazo (*Fstop*), atenuación mínima en la banda de rechazo (*Astop*) y rizado máximo en la banda de paso (*Apass*).

En la figura 3.13 se puede observar todos los valores introducidos, que coinciden con los indicados en las especificaciones de diseño del capítulo 1, excepto la frecuencia final de la banda de paso (Fpass) y la frecuencia inicial de la banda de rechazo (Fstop), las cuales no están indicadas en las especificaciones del proyecto, pero mediante la frecuencia de corte y la banda de transición permitida, se han estimado empleando las siguientes expresiones mostradas en la ecuación 3.13.

Frecuencia final de la banda de paso = Frecuencia de corte = 250 Mhz

Frecuencia inicial de la banda de rechazo = Frec. de corte + Banda de transición = 500 Mhz

(3.13)

Figura 3.13. Valores rellenados en la aplicación Filter Designer de Matlab.

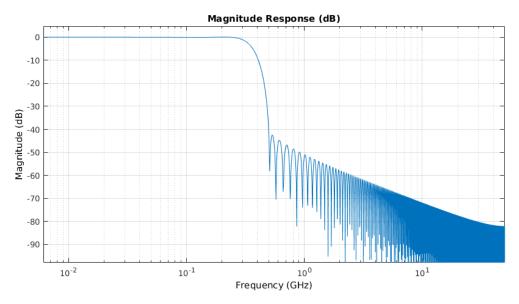

El orden del filtro proporcionado mediante la aplicación *Filter Designer* de Matlab es 893 y la respuesta en el dominio de la frecuencia se puede observar en la Figura 3.14.

Figura 3.14. Respuesta en frecuencia del filtro obtenida de la aplicación Filter Designer.

En este primer diseño se ha logrado cumplir las especificaciones impuestas inicialmente, pero el orden del filtro obtenido, 893, se considera bastante elevado si se desea una implementación del filtro a nivel de transistor, necesario para implementar las líneas de retardo asíncrono del filtro. Además, mediante la aplicación *Filter Designer* con la opción 'minimum order' no se ha podido ajustar la beta Kaiser a 4, como veremos a continuación este ajuste logra reducir el orden manteniendo las especificaciones.

Para intentar reducir este orden tan elevado se ha decido emplear la función 'fir1' para calcular los coeficientes. Mediante esta función se puede indicar la frecuencia de corte en lugar de la frecuencia final de la banda de paso y la frecuencia inicial de la banda de

rechazo. Por otro lado, permite introducir la *beta Kaiser*, que en el caso de nuestro diseño es 4, tal y como indican las especificaciones iniciales del filtro.

Una vez obtenido los coeficientes se ha empleado la función 'freqz' para generar la respuesta en frecuencia y finalmente se ha usado la herramienta 'fvtool' para representarla gráficamente. Este procedimiento se ha repetido modificando el orden del filtro, con el fin de encontrar un orden que permita cumplir con las especificaciones iniciales.

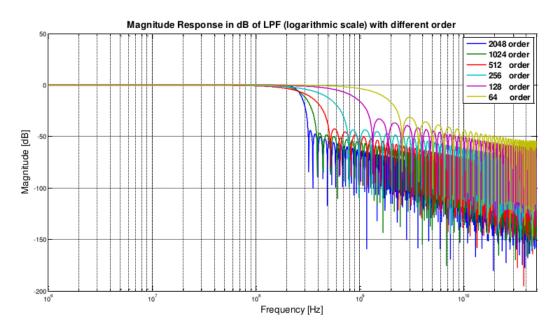

En la figura 3.15 se puede observar las diferentes respuestas en el dominio de la frecuencia de los filtros diseñados con diferente orden.

Figura 3.15. Respuesta en frecuencia de los filtros con diferente orden diseñados.

Además de representar gráficamente la respuesta en el dominio de la frecuencia del filtro, se deben determinar los parámetros de los filtros diseñados con los diferentes órdenes y conocer si cumplen con las especificaciones de diseño iniciales. Para ello, se ha creado una rutina en el lenguaje de Matlab (almacenado en un fichero .m) que permite obtener a partir de la respuesta del filtro en frecuencia los valores de frecuencia de corte, banda de transición, atenuación mínima en la banda de rechazo, rizado en la banda de paso e integral del error al cuadrado (ISE - Integral Square Error), este último parámetro será explicado en el siguiente capítulo. En el Anexo se pueden consultar las rutinas en Matlab

empleadas para el diseño de los filtros de este capítulo, así como el *script* generado para obtener los parámetros de los filtros digitales FIR.

Después de procesar las respuestas en el dominio de la frecuencia de los filtros digitales que se muestran en la Figura 3.15 con la rutina creada, se comprueba que cumplen en todos los casos con las especificaciones de frecuencia de corte y máximo rizado en la banda de paso, no así para la atenuación mínima en la banda de rechazo y la banda de transición tal como se aprecia en la Tabla 3.3.

Tabla 3.3. Relación entre el orden con la banda de transición y su banda de rechazo.

| Orden | Banda de Transición | Atenuación en la<br>Banda de Paso |

|-------|---------------------|-----------------------------------|

| 2048  | 117 MHz             | -44                               |

| 1024  | 146 MHz             | -46                               |

| 512   | 249 MHz             | -42                               |

| 256   | 520 MHz             | -43                               |

| 128   | 1271 MHz            | -33                               |

| 64    | 2698 MHz            | -31                               |

La Tabla 3.3 permite seleccionar el orden mínimo de los filtros evaluados el cual permite cumplir con las especificaciones inicialmente establecidas para el filtro digital propuesto en el proyecto. El orden mínimo resultante funcional es 512.

#### **Conclusiones**

En este capítulo hemos visto una introducción al funcionamiento de los filtros digitales, dando a conocer los tipos que existen y las principales características de éstos.

Además, hemos hecho una introducción a los filtros digitales asíncronos y se ha explicado las propiedades de este tipo de filtros, indicando la arquitectura elegida y los bloques funcionales necesarios, centrándonos en el diezmador.

Una vez conocida la arquitectura y el tipo de filtro, se ha diseñado el filtro con las especificaciones de diseño indicadas en el capítulo 1. Para ello se ha empleado Matlab, software que nos ha permitido calcular los coeficientes y el orden del filtro.

Los cálculos y el diseño del filtro realizados en este capítulo corresponden a una primera aproximación ideal al diseño final ya que suponen que la cadena de retardos asíncronos es lineal y que los cálculos de los sumadores, multiplicadores y los coeficientes del filtro tienen una resolución infinita. En el siguiente capítulo se va a estudiar los efectos de la cuantificación del filtro, así como la no linealidad de los elementos de retardo.

# 4. Efectos de Cuantificación y no linealidades

#### Introducción

En el diseño del filtro FIR propuesto nos encontramos con dos importantes fuentes de no-linealidad, una primera fuente debida a la cuantificación del filtro, presente en todos los filtros digitales, y una segunda debida al uso de elementos de retardo asíncrono como son la cadena de inversores que se ha decidido emplear en nuestro diseño. Este último requiere especial estudio debido a lo característico que es y la reducida literatura que existe al respecto.

Las no-linealidades debido a la cuantificación comprende la cuantificación a la entrada del filtro, la de los coeficientes y la de la salida del filtro. En algunas ocasiones la cuantificación del filtro es trivial debido a que el filtro digital está implementado en ordenadores o equipos con alta prestaciones de cómputo, permitiendo el uso de una gran cantidad de bits y evitando así posibles errores de cuantificación. Sin embargo, en nuestro caso es un diseño *full-custom* implementado con elementos de retardo mediante líneas de retardo asíncronas.

De esta forma es indispensable minimizar el número de bits para reducir la complejidad en el diseño a nivel de transistor al mínimo posible, sin olvidar que el rendimiento del filtro debe continuar cumpliendo con las especificaciones de diseño iniciales.

Por otro lado, la no-linealidad causada por los elementos de retardo, requiere de un análisis previo que nos ayude a determinar los posibles efectos en el filtro digital diseñado, más concretamente en las especificaciones de diseño deseadas. Para ello se va a estudiar las variaciones de tiempo de retardo que pueden sufrir los elementos de retardo por el empleo de una cadena de inversores. En el capítulo siguiente se explicarán de manera más concreta las variaciones que sufren los elementos de retardo por emplear puertas lógicas.

## Cuantificación del filtro digital

Los diseños de filtros digitales normalmente se realizan suponiendo una anchura de palabra infinita o muy grande. En la práctica, los sistemas están restringidos a un conjunto finito de valores discretos limitado por la longitud de los registros (precisión finita). De esta manera es necesario seleccionar un número finito de bits en la entrada del filtro, en los coeficientes y en la salida del filtro. Los efectos de la cuantificación son muy significativos debido a que dicho proceso transforma el filtro en un sistema no lineal, pudiendo tener consecuencias nefastas en el rendimiento del filtro digital, llegando incluso a que un filtro estable se convierta en inestable [44] [45].

Generalmente los efectos de la cuantificación son complejos de analizar y cuantificar, pero existen técnicas sin una elevada complejidad y mediante simulaciones con software específico que permiten minimizar las perturbaciones que ocasionan, siempre y cuando la contribución de los efectos de cuantificación no sea significativa respecto a la señal. Los errores de cuantificación en un filtro pueden ser divididos según su origen en cuantificación en la entrada, cuantificación de los coeficientes y la precisión finita en las operaciones aritméticas del filtro [46]. El caso del primero origen indicado, cuantificación en la entrada, no será estudiada en el presente proyecto fin de carrera, teniendo en cuenta que lo consideramos dentro del ámbito del convertidor Sigma-Delta previo al filtro, ya descrito en el capítulo 2, y suponemos una señal ya cuantificada correctamente a la entrada del filtro, considerando las especificaciones de diseño indicadas en el capítulo 1.

Con el fin de limitar los efectos de cuantificación y favorecer un diseño adecuado, inicialmente se va a analizar el formato de los datos y su representación numérica. A continuación, se estudiará la cuantificación de los coeficientes y finalmente se realiza la

elección del número de bits de salida para evaluar el error de cuantificación por precisión finita en las operaciones aritméticas del filtro.

#### Formato de datos y representación numérica

En el diseño de sistemas de procesamiento digital de señales existen dos tipos de representación numérica:

Aritmética en coma flotante: En general la representación en coma flotante está basada en la notación exponencial. En la notación exponencial cualquier número real diferente de cero puede ser expresado en sistema decimal como muestra la siguiente ecuación, 4.1.

$$r = c \cdot b^e \tag{4.1}$$

donde 'b' es la base, en el sistema lineal 10, 'e' es un número entero y se denomina exponente y 'c' es un número real con un solo dígito entero seguido de una coma y varios dígitos fraccionarios (noción científica estandarizada), denominado coeficiente o mantisa.

Las características más destacables en la implementación de filtros digitales son:

- o Después de operaciones aritméticas requiere normalización de los números.

- o Se emplean donde la precisión y el rango dinámico son determinantes.

- Es necesario más algoritmos para su implementación que en la aritmética de punto fijo.

- o Facilidad en la codificación.

- Mayor necesidad de área, frecuencia y potencia.

- Aritmética de punto fijo: La aritmética de punto fijo proporciona una alternativa a la aritmética en coma flotante. Los números en coma flotante almacenan dos valores, el exponente y la mantisa, la multiplicación de la mantisa por el exponente define su valor numérico. Los números de punto fijo solo emplean una parte de sus dígitos disponibles exclusivamente para representar la parte entera y el resto de

dígitos para la parte fraccionaria. En la ecuación 4.2 se puede observar la forma de representar un número real.

$$R = e_{n-1}e_{n-2}...e_2e_0, f_{-1}f_{-2}f_{-p}$$

(4.2)

donde 'e' son los valores binarios de la parte entera, 'f' los valores binarios de la parte fraccionaria y 'n' y 'p' son el número de bits de la parte entera y fraccionaria respectivamente.

En el caso de la aritmética de punto fijo las características a tener en consideración para la implementación de filtros digitales son:

- o La parte decimal es fija.

- o Mayor simplicidad en hardware, baja potencia y menor área necesaria.

- Las Multiplicaciones doblan en número de bits empleado (NxN bits produce 2N bits).

- o Código menos entendible, necesario control de desbordamiento y escalado.

Considerando las características de cada tipo de representación numérica, para el presente proyecto se ha decidido que la aritmética de punto fijo es la más adecuada, principalmente por su menos compleja implementación a nivel de transistores, menor consumo y menor área, en comparación con la aritmética en coma flotante.

#### Cuantificación de los coeficientes

La decisión de emplear aritmética de punto fijo en el diseño propuesto obliga a realizar una cuantificación de los coeficientes con un número finito de bits, debido a que los coeficientes calculados en el capítulo anterior emplean números en punto flotante de precisión doble. A continuación, analizaremos la cuantificación de los coeficientes para minimizar los errores por cuantificación en el rendimiento de la respuesta en frecuencia del filtro que permita mantener las especificaciones de diseño indicadas en el capítulo 1.

Como se pudo observar en la Figura 3.15 del capítulo anterior, la atenuación mínima en la banda de rechazo alcanzada con los coeficientes calculados es de 42dB. Teniendo en cuenta esta atenuación mínima en la banda de rechazo y considerando la ecuación 4.3 [47],

podemos realizar una primera estimación inicial de cuantos son los bits mínimos necesarios en la cuantificación de los coeficientes para proporcionar al filtro un adecuado rango dinámico. Según esta regla se asume que es necesario un bit por cada 5dB de atenuación. Así el valor calculado es:

$$Bitsmin. = \frac{AtenuacinMin.BandaRechazo}{5dB/bit} = \frac{42dB}{5dB/bit} = 8, 4 \approx 9$$

$$(4.3)$$

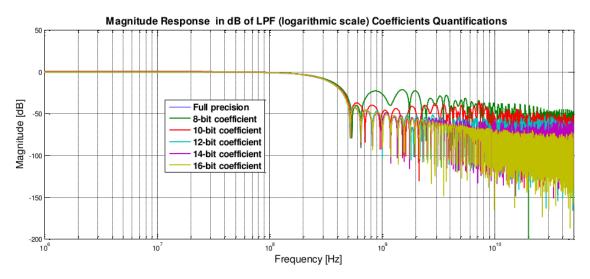

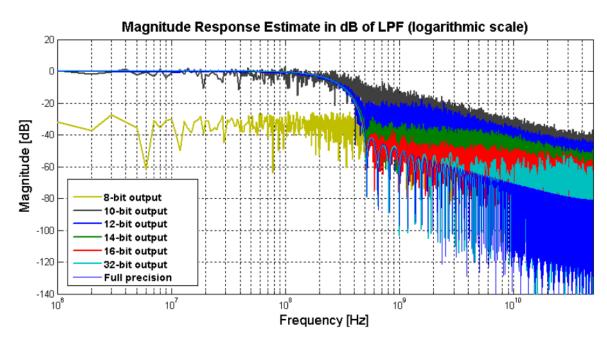

Como se puede observar en la ecuación 4.3 el mínimo exigible según esta regla es 9 bits, para comprobarlo y mostrarlo gráficamente de forma más clara, en la Figura 4.1 se muestra una serie de simulaciones con diferente cuantificación de coeficientes, 8, 10, 12, 14 y 16 bits realizadas con la función 'qfilt' que proporciona el toolbox Filter Design de Matlab. En la tabla 4.1 se indica la sintaxis y parámetros que emplea la función 'qfilt'. Aunque la norma establece 9 bits para lograr un adecuado margen dinámico, la cuantificación con ese número de bits puede deteriorar ciertas especificaciones del filtro, pudiendo incumplir algunas de las especificaciones de diseño del filtro o no logrando una respuesta en frecuencia del filtro lo suficientemente fina para algunas aplicaciones.

Tabla 4.1. Funciones qfilt de Matlab.

| Función                                                    | Sintaxis                               | Argumentos                                                                                                         |  |  |

|------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Generar filtro<br>cuantificado                             | qfilt('Struce',{Coef},'prop1',value1,) | Struc: Estructura del filtro.<br>Coef: Coeficientes del filtro.<br>prop1: Propiedades.<br>value1: Valor propiedad1 |  |  |

| Configura el tamaño de palabra y tamaño parte fraccionaria | qfilt('quantizer',[f_length length]    | length: Tamaño de la palabra (n+ bits) f_length: Tamaño parate fraccionaria.                                       |  |  |

Figura 4.1. Respuesta en frecuencia del filtro para diferente cuantificación de coeficientes.

Analizando más en detalle la Figura 4.1 se puede apreciar, que la respuesta en frecuencia del filtro sufre una distorsión evidente con una cuantificación en los coeficientes de 8 bits.

Esta distorsión se produce principalmente en la atenuación en la banda de rechazo. Por otro lado, la cuantificación de los coeficientes con 10 bits mejora la atenuación en la banda de rechazo, pero no es posible identificar visualmente si cumple con las especificaciones indicadas en el capítulo 1.

Para ser capaces de evaluar mejor si cumple las especificaciones deseadas, la respuesta en frecuencia de los filtros con los coeficientes cuantificados ha sido procesada por la rutina generada en el proyecto, la cual ya fue empleada en el capítulo anterior para caracterizar mejor el filtro y, como se indicó, permite obtener a partir de la respuesta en frecuencia del filtro los valores de frecuencia de corte, banda de transición, atenuación mínima en la banda de rechazo y rizado. Además, para determinar mejor la distorsión que se produce en el filtro, se ha añadido la integral del error al cuadrado (ISE, *integrated squared* error) en módulo y en fase, que vendrá dada por la ecuación 4.4, donde H es la respuesta del filtro después de ser cuantificado y H<sub>1</sub> es la respuesta del filtro ideal, sin cuantificar.

$$ISE = \frac{2}{f_s} \sum |H_i - H|^2 \tag{4.4}$$

Los valores obtenidos para las diferentes cuantificaciones de los coeficientes del filtro propuesto se muestran en la Tabla 4.2.

Tabla 4.2. Parámetros del filtro para diferente cuantificación de coeficientes.

| Filtro                                     | Coefi.<br>Bits | Frec.<br>Corte<br>[MHz] | Banda<br>Trans.<br>[MHz] | Atenu.<br>[dB] | Rizado<br>[dB] | ISE Magnit. | ISE<br>Fase |

|--------------------------------------------|----------------|-------------------------|--------------------------|----------------|----------------|-------------|-------------|

| Filtro Precisión<br>doble                  | -              | 256                     | 249                      | -42,46         | 0              | 0           | 0           |

| Filtro cuantificado coeficientes - 8 bits  | 8              | 266                     | 228                      | -21,33         | 0,05           | 3,40E-10    | 2,00E-38    |

| Filtro cuantificado coeficientes - 10 bits | 10             | 254                     | 256                      | -36,3          | 0,088          | 6,10E-11    | 9,80E-39    |

| Filtro cuantificado coeficientes - 12 bits | 12             | 256                     | 257                      | -42,11         | 0,012          | 9,50E-13    | 1,40E-38    |

| Filtro cuantificado coeficientes - 14 bits | 14             | 256                     | 255                      | -42,26         | 0,006          | 4,60E-13    | 1,60E-38    |

| Filtro cuantificado coeficientes - 16 bit  | 16             | 256                     | 255                      | -42,46         | 0,001          | 0           | 2,00E-38    |

Con los valores de los parámetros de la tabla 4.2 ya somos capaces de seleccionar un número de bits adecuado para la cuantificación de los coeficientes del filtro.

Como muestra la columna de la banda de atenuación para 8 y 10 bits, los resultados no son óptimos. Aunque la ecuación 4.3 indica que con 10 bits se cumple con la especificación del margen dinámico, la tabla muestra que la banda de atenuación se ve reducida a -36.30 dB, incumpliendo así una de las especificaciones de diseño proporcionada en el capítulo 1. Sin embargo, si elegimos usar 12 bits para cuantificar los coeficientes del filtro, además de cumplir con la atenuación mínima en la banda de rechazo, tendremos un margen para los efectos de las no-linealidades que aún no se han cuantificado.

Por otro lado, las integrales del error al cuadrado tienen un valor muy reducido, y el rizado y la banda de transición, aunque no se mantiene estrictamente dentro de las

especificaciones de diseño, son tan pequeños los errores que se ha dado por satisfactorio para continuar.

#### Cuantificación de salida y operaciones aritméticas

Para finalizar la cuantificación en el filtro digital se debe realizar la cuantificación de las operaciones aritméticas, las cuales nos van a permitir seleccionar el número de bits de salida y el número de bits necesarios en las operaciones aritméticas internas (en nuestro diseño nos referimos a los sumadores). Aunque la estructura del diseño propuesto es singular, por la modificación puntual de la ubicación del diezmador, está basado en la estructura de forma directa. Dada esta estructura y continuando con la decisión de emplear aritmética de punto fijo, en la Figura 4.2 se puede observar la estructura de cuantificación con el número de bits que deben tenerse en consideración durante la cuantificación de las operaciones aritméticas.

Figura 4.2. Estructura de forma directa cuantificada para el filtro FIR diseñado [48].

Debido a que la entrada del filtro digital es de un bit, no es necesario realizar cuantificación por la multiplicación ya que el número de bits de salida de la multiplicación siempre va a ser el mismo número de bits de los coeficientes cuantificados, evitando en estos bloques posibles errores de redondeo. Descartados los errores de cuantificación en

los bloques multiplicadores, los efectos negativos de la cuantificación se van a concentrar en los bloques sumadores.

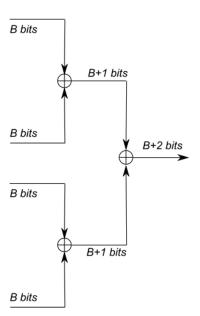

En general, para evitar los errores por redondeo cuando se realiza una suma entre dos números en punto fijo con el mismo número de bits se añade un bit extra, lo que permite contemplar el bit de acarreo que puede producir la suma. Así para un filtro de orden N, se deberían de emplear el número de bits de los valores de los sumandos más N-1 bits adicionales. Sin embargo, en la práctica no es necesario incrementar un bit por cada suma para evitar errores de redondeo. El incremento se puede calcular a partir de la ecuación 4.5:

$$G = log_2(N) + 1 = log_2(512) + 1 = 10$$

(4.5)

Esta ecuación con crecimiento logarítmico en base 2 se puede entender mejor si se aplica para las sumas una arquitectura de árbol de sumadores En la Figura 4.3 se puede observar este efecto con la suma de 4 números representados con B bits. Para lograr el resultado final de la suma de esos 4 números será necesario tres sumas e inicialmente se podría pensar que es necesario 3 bits adicionales. Sin embargo, en la Figura 4.3 se puede apreciar que con 2 bits adicionales es suficiente.

Figura 4.3. Árbol de sumadores, para 4 sumandos indicando el número de bits necesarios [48].

Teniendo en cuenta esto y aplicando la ecuación 4.5, el valor obtenido de G es de 10. Si a continuación realizamos la suma de G + b como indica la salida del filtro en la Figura, se obtiene una salida de 22 bits. Una cuantificación con sumadores y a la salida del filtro a 22 bits no parece adecuada, debido al notable aumento de tamaño del circuito y su consumo asociado.

Existen métodos que permiten reducir la G de la Figura 4.2 y, por consiguiente, la salida del filtro. En nuestro caso para obtener precisión infinita obtuvimos una cuantificación en los bloques sumadores de 22 bits, pero antes de seleccionar esta cuantificación se va a intentar reducir basándonos en la ecuación 4.5, la cual indica una convolución para un filtro FIR con un orden de N + 1:

$$y[n] = \sum_{m=0}^{N} h[m]x[n-m]$$

(4.5)

Mediante la ecuación 4.5, si somos capaces de determinar los valores de entrada, es posible calcular la máxima salida que se va a obtener y, de esta manera, conocer el número de bits necesarios para una cuantificación correcta. Para ello, inicialmente se debe pasar a valor absoluto cada uno de los miembros de la ecuación y, a continuación, se aplica la desigualdad del triángulo para la norma 1, quedando como se muestra en la ecuación 4.6.

$$|y[n]| \le \left| \sum_{m=0}^{N} h[m] \cdot x[n-m] \right| = \sum_{m=0}^{N} |h[m] \cdot x[n-m]| = \sum_{m=0}^{N} |h[m]| \cdot |x[n-m]|$$

(4.6)

Finalmente, y partir de la ecuación 4.6, se debe aplicar en para x el rango máximo que se tiene para las entradas normalmente viene expresado por [-R/2, R/2), donde R es el rango que puede cubrir la entrada (en nuestro caso hace referencia a los coeficientes). Al aplicar obtenemos la ecuación 4.7, donde solo queda calcular la salida máxima del filtro. Esto se realiza mediante la suma todos los valores absolutos de los coeficientes (norma 1) y, finalmente se multiplica por el rango de entrada.

$$|y[n]| = \frac{R}{2} \sum_{m=0}^{N} |h[m]| = \frac{R}{2} \cdot ||h[n]||_1 = 1 \cdot 4,096 = 4,096$$

(4.7)

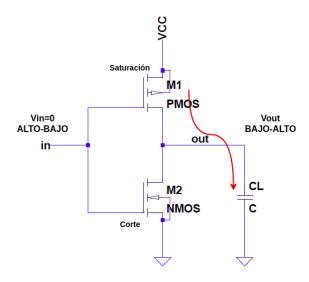

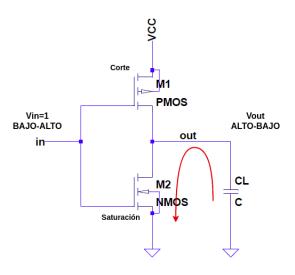

Con el intervalo de salida calculado y conociendo el intervalo de entrada, simplemente es necesario obtener el factor de ganancia de la salida respecto a la entrada y sumárselo al número de bits ya cuantificado de los coeficientes. En el caso del filtro digital propuesto R/2 es igual a 1, debido a que la entrada es de 1 bit y la norma 1 de los coeficientes del filtro es igual a 4,096. Teniendo en cuenta estos valores, con un incremento de 2 bits es posible cubrir el rango de [-4,4), valor muy cercano al 4,096 calculado. De esta manera el número de bits sería 14: 12 bits de los coeficientes más los 2 calculados.