# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

## TRABAJO FIN DE MÁSTER

Entorno UVM para la verificación funcional de un IP multi-interfaz orientado a la compresión de imágenes

Titulación: Máster Universitario en Ingeniería de

**Telecomunicación**

Autor: D. Samuel Rodríguez Rodríguez Tutores: Dr. D. Valentín De Armas Sosa

Dr. D. Félix B. Tobajas Guerrero

Fecha: Febrero de 2018

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE MÁSTER

# Entorno UVM para la verificación funcional de un IP multi-interfaz orientado a la compresión de imágenes

#### **HOJA DE FIRMAS**

Alumno

Fdo.: D. Samuel Rodríguez Rodríguez

Tutor/a Tutor/a

Fdo.: Dr. D. Valentín De Armas Sosa Fdo.: Dr. D. Félix B. Tobajas Guerrero

Fecha: Febrero de 2018

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

# TRABAJO FIN DE MÁSTER

Entorno UVM para la verificación funcional de un IP multi-interfaz orientado a la compresión de imágenes

## **HOJA DE EVALUACIÓN**

| Calificación: |              |

|---------------|--------------|

| Presidente    |              |

|               |              |

| Fdo.:         |              |

| Vocal         | Secretario/a |

|               |              |

| Fdo.:         | Fdo.:        |

|               |              |

Fecha: Febrero de 2018

#### **RESUMEN**

Actualmente, los procesos de validación y verificación son extremadamente importantes en el diseño de sistemas hardware digitales y abarcan la mayor parte del tiempo de desarrollo de un producto. Es por ello que en este Trabajo Fin de Máster (TFM) se hace uso de la metodología UVM (*Universal Verification Methodology*) con el fin de reducir el impacto de la verificación funcional en el flujo de diseño de sistemas hardware. Se trata de una metodología de verificación reciente soportada por los principales desarrolladores de herramientas EDA (*Electronic Design Automation*). El objetivo fundamental de este TFM consiste en desarrollar un entorno de verificación basado en UVM para un módulo IP (*Intellectual Property*) específico, partiendo de un *test bench ad-hoc* de referencia ya existente. El entorno UVM será, no solamente reusable, sino que también estará mejor estructurado y resultará más sencillo de modificar que el *test bench* original. En primer lugar, se estudia la metodología UVM a partir de la implementación de un entorno de verificación UVM genérico, para a continuación analizar en detalle el módulo IP a verificar y su *test bench* original, con el fin de desarrollar el entorno de verificación basado en UVM y validar su funcionamiento. Además, se evidencian las mejores prestaciones en la arquitectura del entorno de verificación desarrollado en comparación con el *test bench* de referencia.

#### **A**BSTRACT

Validation and verification processes are extremely important in current designs of digital hardware systems and cover most of the development time of a final product. Therefore, in this project it is used UVM (Universal Verification Methodology), which is the most recent verification methodology and is supported by the main EDA (Electronic Design Automation) tools developers. In this case, the main objective consists of rebuilding a traditional test bench focused on a complex IP (Intellectual Property) module by using this methodology. In addition, that environment will be not only reusable, but also better structured and easier to modify (for instance, adding functionalities) than the traditional test bench. Firstly, the methodology was studied (creating generic UVM environment), as well as the specific IP the project deals with and its original test bench. Finally, the final UVM environment was developed and its validity proved. Moreover, it has been verified the more flexible and powerful architecture of the new verification environment in comparison with the original test bench.

# ÍNDICE DE CONTENIDOS

| Índic | e de  | e Figuras                                                  | V       |

|-------|-------|------------------------------------------------------------|---------|

| Índic | e de  | Códigos                                                    | VII     |

| Índic | e de  | Tablas                                                     | IX      |

| Acró  | nimo  | os                                                         | XI      |

|       |       |                                                            | MEMORIA |

| Capí  | tulo  | 1. Introducción                                            | 1       |

| 1.3   | 1     | Antecedentes                                               | 1       |

| 1.2   | 2     | Objetivos                                                  | 3       |

| 1.3   | 3     | Peticionario                                               | 4       |

| 1.4   | 4     | Estructura del documento                                   | 4       |

| Capí  | tulo  | 2. Universal Verification Methodology                      | 5       |

| 2.3   | 1     | Introducción a la verificación                             | 5       |

| 2.2   | 2     | Verificación funcional de sistemas hardware digitales      | 6       |

| 2.3   | 3     | SystemVerilog                                              | 8       |

| 2.4   | 4     | Introducción a UVM                                         | 10      |

| 2.5   | 5     | Fundamentos de UVM                                         | 12      |

|       | 2.5.  | 1 Biblioteca de clases                                     | 12      |

|       | 2.5.2 | 2 Factory                                                  | 14      |

|       | 2.5.3 | 3 Fases de UVM                                             | 15      |

|       | 2.5.4 | 4 Mecanismo de configuración                               | 17      |

|       | 2.5.  | 5 Mecanismo de mensajes                                    | 18      |

|       | 2.5.6 | 6 TLM                                                      | 20      |

| 2.0   | 6     | Estructura de un entorno de verificación UVM               | 23      |

|       | 2.6.2 | 1 Secuencias                                               | 24      |

|       | 2.6.2 | 2 Componente Agent                                         | 26      |

|       | 2.6.3 | 3 Componente Scoreboard                                    | 29      |

|       | 2.6.4 | 4 Componente Environment                                   | 30      |

|       | 2.6.  | 5 Componente Test                                          | 30      |

|       | 2.6.  | 6 Módulo Top                                               | 31      |

| Capí  | tulo  | 3. Módulo IP multi-interfaz para la compresión de imágenes | 33      |

| 3.3   | 1     | Módulo IP                                                  | 33      |

| 3.2   | 2     | Entorno de verificación (test bench) original              | 37      |

| 3      | .2.1    | Generación de los estímulos y los archivos de simulación                | 37         |

|--------|---------|-------------------------------------------------------------------------|------------|

| 3      | .2.2    | Generación de las señales principales                                   | 42         |

| 3      | .2.3    | Referencia de los componentes del test bench                            | 43         |

| 3      | .2.4    | Proceso de configuración del IP                                         | 46         |

| 3      | .2.5    | Proceso de transferencia del flujo de datos de entrada                  | 50         |

| 3      | .2.6    | Proceso de recepción del flujo de datos de salida y comparación con los | valores de |

| re     | eferen  | ıcia                                                                    | 58         |

| 3      | .2.7    | Ejecución de los test                                                   | 62         |

| Capítu | lo 4. I | Desarrollo del entorno de verificación basado en UVM                    | 65         |

| 4.1    | Ge      | eneración de un IP usando HDL Coder                                     | 65         |

| 4.2    | In      | tegración de un DUV descrito en VHDL                                    | 73         |

| 4.3    | Cr      | eación de un wrapper como nuevo DUV                                     | 74         |

| 4.4    | Pa      | quetes con definición de constantes                                     | 75         |

| 4.5    | Es      | tructura del entorno de verificación del IP121 basado en UVM            | 78         |

| 4      | .5.1    | Interfaces virtuales                                                    | 80         |

| 4      | .5.2    | Módulo Top                                                              | 81         |

| 4      | .5.3    | Transacciones                                                           | 84         |

| 4      | .5.4    | Secuencias                                                              | 86         |

| 4      | .5.5    | Componente Test                                                         | 89         |

| 4      | .5.6    | Componente Environment                                                  | 93         |

| 4      | .5.7    | Componente Agent de configuración                                       | 94         |

| 4.     | .5.8    | Componente Agent de datos                                               | 103        |

| 4.     | .5.9    | Componente Scoreboard                                                   | 114        |

| 4.     | .5.10   | Makefile                                                                | 118        |

| 4.6    | Es      | tructura de directorios                                                 | 120        |

| 4.7    | Flu     | ujo de ejecución                                                        | 121        |

| Capítu |         | Resultados                                                              |            |

| 5.1    |         | lida de texto por consola                                               |            |

|        | .1.1    | Test normal                                                             |            |

|        | .1.2    | Test de Error                                                           |            |

|        | .1.3    | Test de ForceStop                                                       |            |

|        | .1.4    | Test de reconfiguración                                                 |            |

| 5.2    |         | rmas de onda                                                            |            |

| 5.3    |         | empo de ejecución                                                       |            |

|        |         | Conclusiones                                                            |            |

| •      |         | onclusiones generales                                                   |            |

|        |         |                                                                         |            |

| 6.2       | Líneas futuras       | 137                   |

|-----------|----------------------|-----------------------|

| Referen   | cias                 | 139                   |

|           |                      | PLIEGO DE CONDICIONES |

| Pliego de | e condiciones        | 143                   |

|           |                      | PRESUPUESTO           |

| Presupu   | esto                 | 147                   |

| Recur     | sos humanos          | 147                   |

| Recur     | sos hardware         | 147                   |

| Recur     | sos software         | 148                   |

| Mater     | ial fungible         | 148                   |

| Coste     | total del proyecto   | 149                   |

|           |                      | ANEXOS                |

| Anexo –   | Contenido del CD-ROM | 153                   |

# ÍNDICE DE FIGURAS

| Figura 1.1. Evolución de las metodologías previas en las que se basa UVM                 | 2   |

|------------------------------------------------------------------------------------------|-----|

| Figura 2.1. Diagrama de técnicas de verificación                                         | 6   |

| Figura 2.2. Proceso genérico de diseño y verificación funcional                          | 7   |

| Figura 2.3. Tendencias en lenguajes de verificación ASIC/IC                              | 8   |

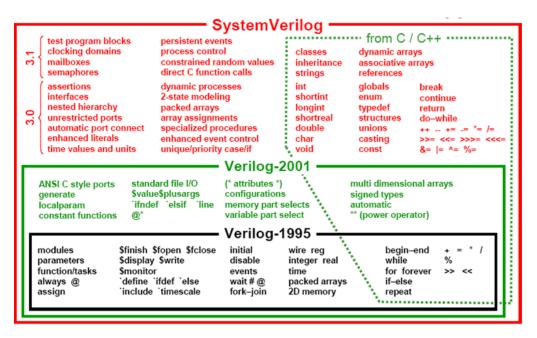

| Figura 2.4. Funcionalidades de SystemVerilog                                             | 9   |

| Figura 2.5. Tendencias en metodologías de verificación ASIC/IC                           | 12  |

| Figura 2.6. Jerarquía parcial de la biblioteca de clases de UVM                          | 13  |

| Figura 2.7. Fases de UVM y orden de ejecución                                            | 15  |

| Figura 2.8. Clases para la mensajería                                                    | 19  |

| Figura 2.9. Comunicación TLM port – TLM export                                           | 22  |

| Figura 2.10. Comunicación TLM analysis port – TLM analysis exports                       | 22  |

| Figura 2.11. Modelo básico de entorno de verificación UVM                                | 23  |

| Figura 2.12. Tareas en la ejecución de una secuencia                                     | 25  |

| Figura 2.13. Agente UVM                                                                  | 26  |

| Figura 2.14. Protocolo de handshake Sequencer-Driver                                     | 27  |

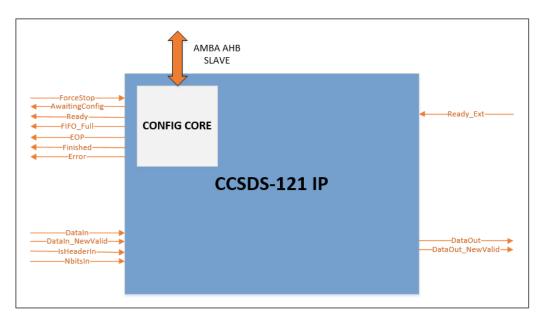

| Figura 3.1. Diagrama de entradas/salidas del IP                                          | 34  |

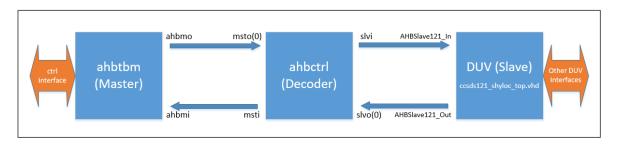

| Figura 3.2. Diagrama de bloques de la estructura del test bench                          | 45  |

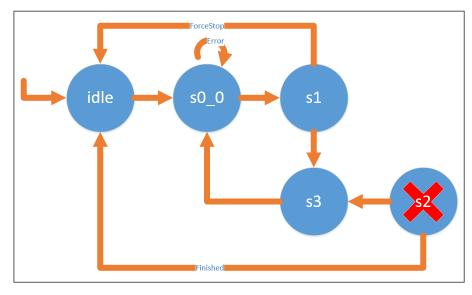

| Figura 3.3. Diagrama de la máquina de estados original para el flujo de datos de entrada | 57  |

| Figura 3.4. Bibliotecas de GRLIB IP correctamente enlazadas a QuestaSim                  | 63  |

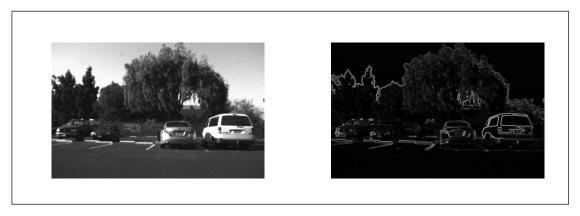

| Figura 4.1. Resultado de la ejecución del test bench mlhdlc_sobelfilter_tb.m             | 68  |

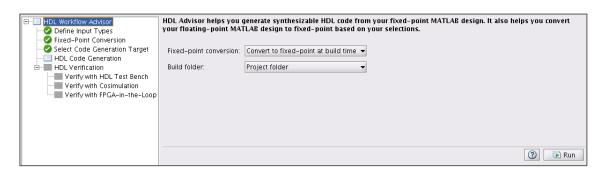

| Figura 4.2. Ventana de un proyecto en HDL Coder                                          | 70  |

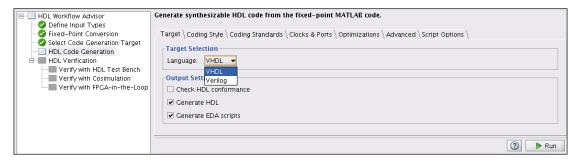

| Figura 4.3. Ventana del Workflow Advisor de HDL Coder                                    | 71  |

| Figura 4.4. Selección del lenguaje para la generación del código HDL                     | 71  |

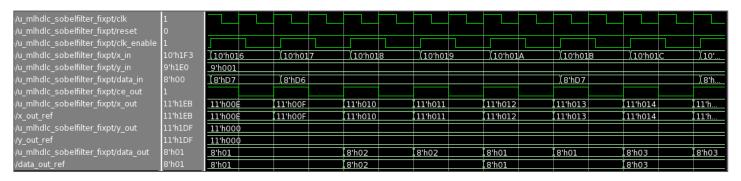

| Figura 4.5. Formas de onda de la simulación en QuestaSim del IP generado en HDL Coder    | 73  |

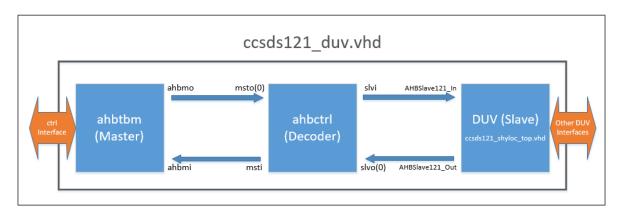

| Figura 4.6. Diagrama de bloques de la entidad VHDL ccsds121_duv                          | 74  |

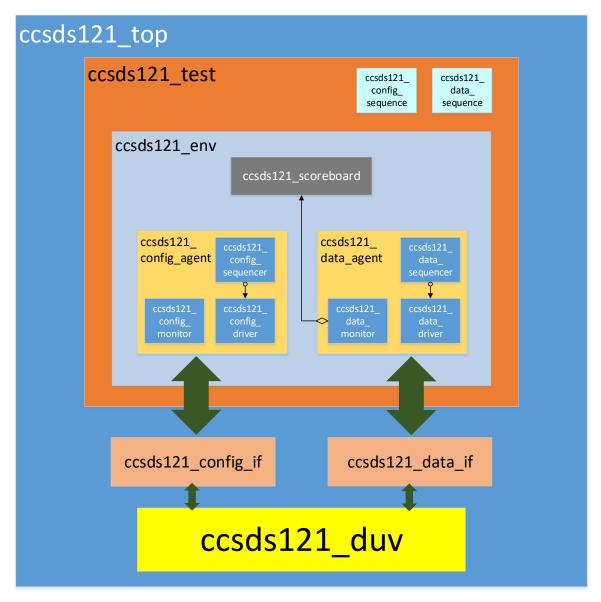

| Figura 4.7. Estructura del entorno UVM específico creado                                 | 79  |

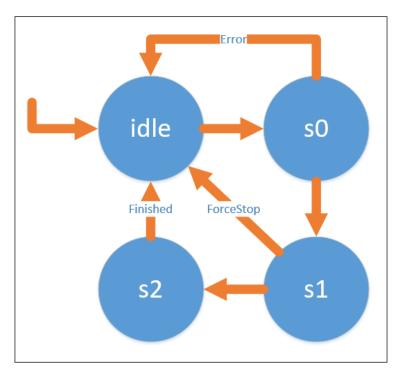

| Figura 4.8. Diagrama de la nueva máquina de estados para el flujo de datos de entrada    | 106 |

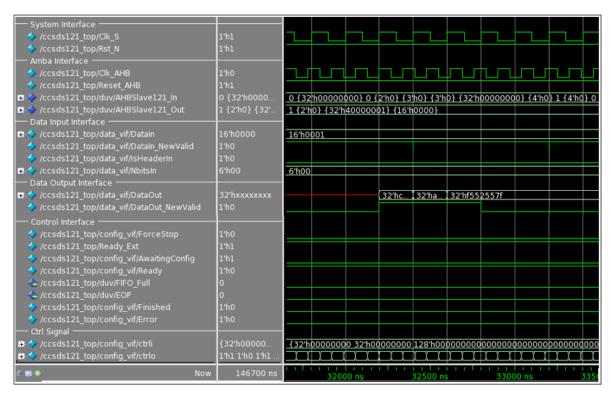

| Figura 5.1. Formas de onda en el comienzo de la recepción del flujo de datos de salida   | 134 |

# ÍNDICE DE CÓDIGOS

| Código 3.1. Entidad VHDL del IP                                                                | 35         |

|------------------------------------------------------------------------------------------------|------------|

| Código 3.2. Ayuda de ejecución del script run_vhdl_tests_121.py                                | 38         |

| Código 3.3. Paquete ccsds121_parameters para el Test 25                                        | 39         |

| Código 3.4. Paquete ccsds121_tb_parameters para el Test 25                                     | 41         |

| Código 3.5. Generación de las señales principales del test bench                               | 43         |

| Código 3.6. Referencia, en el test bench, del IP y los componentes para la comunicación AHB    | 45         |

| Código 3.7. Proceso general de configuración del IP                                            | 47         |

| Código 3.8. Procedimiento de ejecución del test0 (dos compresiones consecutivas)               | 49         |

| Código 3.9. Proceso síncrono de la máquina de estados para el flujo de datos de entrada        | 51         |

| Código 3.10. Proceso asíncrono de la máquina de estados para el flujo de datos de entrada      | 57         |

| Código 3.11. Proceso de recepción del flujo de datos de salida                                 | 60         |

| Código 3.12. Procedimiento de comparación de los datos de salida con sus valores de referencio | ı 62       |

| Código 3.13. Comando de ejecución de los test en QuestaSim                                     | 63         |

| Código 4.1. Función MATLAB mlhdlc_sobelfilter                                                  | 67         |

| Código 4.2. Archivo mlhdlc_sobelfilter_tb.m                                                    | 68         |

| Código 4.3. Almacenamiento de la imagen <code>mlhdlc_img_yuv.tif</code> como matriz de datos   | 69         |

| Código 4.4. Modificación del modo de lectura de la imagen en el test bench                     | 69         |

| Código 4.5. Código a eliminar del test bench                                                   | 70         |

| Código 4.6. Simulación en QuestaSim del código VHDL generado en HDL Coder                      | 72         |

| Código 4.7. Comando para la supresión de warnings en la simulación con un DUV VHDL             | 73         |

| Código 4.8. Entidad VHDL del nuevo DUV ccsds121_duv                                            | <i>7</i> 5 |

| Código 4.9. Ayuda de ejecución del script gen_config_tests_121.py                              | 76         |

| Código 4.10. Paquete SystemVerilog ccsds121_tb_parameters para el Test 25                      | 78         |

| Código 4.11. Interfaz ccsds121_config_if                                                       | 80         |

| Código 4.12. Interfaz ccsds121_data_if                                                         | 81         |

| Código 4.13. Archivo ccsds121_top.sv                                                           | 83         |

| Código 4.14. Archivo ccsds121_pkg.sv                                                           | 84         |

| Código 4.15. Transacción ccsds121_config_packet                                                | 85         |

| Código 4.16. Transacción ccsds121_data_packet                                                  | 86         |

| Código 4.17. Secuencia ccsds121_config_sequence                                                | 87         |

| Código 4.18. Secuencia ccsds121 data sequence                                                  |            |

| Código 4.19. Componente ccsds121_base_test                                        | 91             |

|-----------------------------------------------------------------------------------|----------------|

| Código 4.20. Componentes UVM Test asociados a la funcionalidad de cada test       | 93             |

| Código 4.21. Componente ccsds121_env                                              | 94             |

| Código 4.22. Componente ccsds121_config_agent                                     | 95             |

| Código 4.23. Componente ccsds121_config_sequencer                                 | 95             |

| Código 4.24. Funciones principales del componente ccsds121_config_driver          | 97             |

| Código 4.25. Tarea test                                                           | 99             |

| Código 4.26. Componente ccsds121_config_monitor                                   | 102            |

| Código 4.27. Componente ccsds121_data_agent                                       | 103            |

| Código 4.28. Componente ccsds121_data_sequencer                                   | 104            |

| Código 4.29. Funciones principales del componente ccsds121_data_driver            | 105            |

| Código 4.30. Tarea reset                                                          | 105            |

| Código 4.31. Tarea drive_inputs                                                   | 111            |

| Código 4.32. Componente ccsds121_data_monitor                                     | 113            |

| Código 4.33. Componente ccsds121_scoreboard                                       | 117            |

| Código 4.34. Contenido principal del archivo Makefile                             | 119            |

| Código 4.35. Generación de los archivos con los parámetros de configuración       | 121            |

| Código 4.36. Ejecución de dos test sobre el entorno de verificación creado        | 121            |

| Código 5.1. Mensajes durante la ejecución de la simulación del test ccsds121_norm | al_test        |

|                                                                                   | 126            |

| Código 5.2. Mensajes recibidos en la fase run_phase del test ccsds121_error_t     | est <b>129</b> |

| Código 5.3. Mensajes recibidos en la fase run_phase del test ccsds121_forcest     | op_test        |

|                                                                                   | 130            |

| Código 5.4. Mensajes recibidos en la fase run_phase del test ccsds121_reconfi     | g_test         |

|                                                                                   | 133            |

# ÍNDICE DE TABLAS

| Tabla 2.1. Acciones por defecto en las macros del mecanismo de mensajes | 19  |

|-------------------------------------------------------------------------|-----|

| Tabla 2.2. Valores de verbosity                                         | 20  |

| Tabla PL.1. Condiciones hardware                                        | 143 |

| Tabla PL.2. Condiciones software                                        | 143 |

| Tabla P.1. Coste de recursos hardware                                   | 148 |

| Tabla P.2. Coste de recursos software                                   | 148 |

| Tabla P.3. Coste de material fungible                                   | 148 |

| Tabla P.4. Coste total                                                  | 149 |

#### **ACRÓNIMOS**

ABV Assertion-Based Verification

AHB Advanced High-performance Bus

AMBA Advanced Microcontroller Bus Architecture

API Application Programming Interface

ASIC Application-Specific Integrated Circuit

AVM Advanced Verification Methodology

CCSDS Consultative Committee for Space Data Systems

CD-ROM Compact Disc Read-Only Memory

CPU Central Processing Unit

CSV Comma-Separated Values

DPI Direct Programming Interface

DUT Device Under Test

DUV Device Under Verification

ECTS European Credit Transfer and Accumulation System

EDA Electronic Design Automation

EITE Escuela de Ingeniería de Telecomunicación y Electrónica

eRM e Reuse Methodology

ESA European Space Agency

FIFO First In, First Out

FPGA Field-Programmable Gate Array

HDL Hardware Description Language

HVL Hardware Verification Language

IC Integrated Circuit

IGIC Impuesto General Indirecto Canario

IP Intellectual Property

IUMA Instituto Universitario de Microelectrónica Aplicada

MDV Metric-Driven Verification

MUIT Máster Universitario en Ingeniería de Telecomunicación

OOP Object-Oriented Programming

OVM Open Verification Methodology

PDF Portable Document Format

RAL Register Abstraction Layer

RRHH Recursos Humanos

RTL Register-Transfer Level

TFM Trabajo Fin de Máster

TLM Transaction-Level Modeling

ULPGC Universidad de Las Palmas de Gran Canaria

UVC UVM Verification Component

UVM Universal Verification Methodology

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VMM Verification Methodology Manual

VMM-RAL VMM - Register Abstraction Layer

VP Verification Plan

V&V Verification and Validation

# **M**EMORIA

#### Capítulo 1. Introducción

En este capítulo se detallarán los antecedentes y las necesidades que dan lugar a la realización de este Trabajo Fin de Máster (TFM), así como los objetivos inicialmente planteados y la estructura del presente documento.

#### 1.1 ANTECEDENTES

En la actualidad, la verificación funcional de un sistema hardware digital es un proceso de gran relevancia. Muchos de los sistemas desarrollados hoy en día no son entregados al cliente con evidencias reales de que cumplen con lo dispuesto en el documento de especificaciones funcionales, debido a la dificultad que puede conllevar la realización de un entorno de validación y verificación [1].

Este procedimiento de verificación y validación (V&V, *Verification and Validation*) se utiliza, de modo genérico, para asegurar que un sistema hardware digital satisface las necesidades y especificaciones de diseño, además de no poseer defectos. Por lo general, los sistemas de verificación funcional se dividen en estáticos y dinámicos, siendo estos últimos los más utilizados. Entre las técnicas de verificación dinámica, destaca la simulación, utilizada desde los comienzos del diseño electrónico, y que consiste en la ejecución de diferentes *test* o vectores de estímulos, los cuales pueden seguir patrones totalmente aleatorios o dirigidos [2].

Dada la complejidad de los actuales módulos o bloques funcionales IP (*Intellectual Property*), dicho proceso debe estar presente desde las primeras fases de diseño de un sistema para alcanzar su eficacia óptima, y no relegarse a las últimas etapas de desarrollo [2]. De hecho, la verificación funcional consume más del 60% del tiempo y el esfuerzo en un proyecto de diseño de un sistema hardware digital, por lo que existe una búsqueda constante de nuevas metodologías que proporcionen un mejor rendimiento sobre la verificación funcional [3].

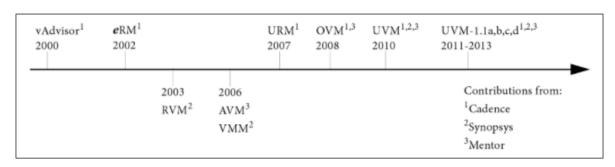

Así, de entre las metodologías existentes para afrontar el proceso de verificación funcional de un componente hardware digital, una de las más recientes es UVM (*Universal Verification Methodology*). El estándar UVM fue publicado en 2011 por *Accellera Systems Initiative* como la primera metodología de verificación promovida por los tres principales desarrolladores de hardware digital en el mercado: *Cadence, Synopsys y Mentor* (Figura 1.1) [3].

Figura 1.1. Evolución de las metodologías previas en las que se basa UVM

A pesar de su relativa juventud, se trata de una metodología madura, ya que su código está basado en modificaciones efectuadas sobre la biblioteca OVM (*Open Verification Methodology*). Además, UVM es de código abierto, así como compatible y portable a los simuladores comerciales más destacados. Esta metodología se basa en el desarrollo y la integración de componentes independientes de verificación o UVC (*UVM Verification Component*), los cuales son diseñados mediante el lenguaje *SystemVerilog*, y se interconectan entre sí a través del uso de la API TLM (*Transaction-Level Modeling*) con el fin de facilitar su reusabilidad [3].

Las principales ventajas de UVM se fundamentan en la adopción de un flujo de trabajo común y en la reusabilidad, de modo que se incrementa la productividad y la eficiencia. Por otra parte, el entorno de verificación se desarrolla de forma aislada al sistema hardware digital a verificar o DUV (Device Under Verification), que en ocasiones también se denominará como DUT (Device Under Test). Así, se consigue que los componentes de un entorno de verificación puedan ser reutilizados para validar la funcionalidad de diferentes DUV, o bien que un único entorno permita verificar dos implementaciones de un mismo sistema descrito en diferentes lenguajes HDL (Hardware Description Language), únicamente adaptando la interfaz con el DUV [3], [4].

Esto choca con el proceso de verificación funcional tradicional, en el que se sigue una metodología *ad-hoc* basada en un Plan de Verificación (VP, *Verification Plan*) rígido elaborado a partir de las especificaciones funcionales del DUV [5]. Este Plan de Verificación se traduce en entornos de *test* específicos implementados en lenguajes HDL, donde para cada nuevo diseño es necesario implementar un *test bench* o entorno de verificación, prácticamente desde el principio. Por tanto, UVM pretende reducir este esfuerzo a partir de la reutilización de los entornos de verificación desarrollados, permitiendo que sean dinámicos y configurables [6].

Para el caso de bloques IP multi-interfaz, se debe prestar especial atención a la integración y adaptación del DUV al entorno UVM, así como al modo de gestionar las distintas interfaces. Este último aspecto determinará la complejidad del diseño, debido a las dependencias entre las

informaciones transferidas, los diferentes protocolos de comunicaciones, etc. En este TFM en particular se trabajará en esta línea, debido a que se utilizará como DUV un IP específico que integra una interfaz de configuración y otra de datos.

#### 1.2 OBJETIVOS

El objetivo principal que se pretende alcanzar con la realización de este Trabajo Fin de Máster es el de elaborar un entorno basado en UVM para la verificación funcional de un IP multi-interfaz (consta de interfaces independientes de configuración y de datos) cuya funcionalidad consiste en la compresión sin pérdidas de imágenes hiperespectrales y multiespectrales. Este IP fue desarrollado en un proyecto llevado a cabo por el Instituto Universitario de Microelectrónica Aplicada (IUMA), en colaboración con la Agencia Espacial Europea (ESA, *European Space Agency*). Se trata de un IP complejo y altamente configurable, por lo que en el entorno de verificación se requiere automatizar el proceso de ejecución de *test*.

El IP en cuestión está descrito en lenguaje VHDL y posee un entorno de verificación *ad-hoc* tradicional y complejo. El entorno UVM a desarrollar, por su parte, se definirá mediante el lenguaje *SystemVerilog*, por lo que se hace necesaria una adaptación multilenguaje que permita la integración del IP en el mismo. Se persigue que este nuevo entorno UVM sea más fácil de interpretar, además de reutilizable, características inexistentes en el *test bench* de referencia.

Una vez establecido el objetivo principal del TFM, se enumeran a continuación los objetivos operativos que se plantean para su desarrollo:

- Adquirir los conocimientos relativos a la metodología UVM: estructura de un entorno básico, diferentes elementos, componentes e interconexiones, etc.

- Implementar un entorno UVM básico y adaptarlo para comprobar su correcto funcionamiento mediante la verificación de un IP sencillo, independiente del IP específico sobre el que se centra el presente TFM (por ejemplo, un IP generado a partir de una funcionalidad desarrollada por un tercero en MATLAB).

- Estudiar y analizar el funcionamiento del IP multi-interfaz orientado a la compresión de archivos de imagen (a nivel del protocolo de comunicación utilizado en sus interfaces de configuración y de datos), así como de su test bench original, lo que servirá de referencia para la generación del entorno de verificación basado en UVM.

- Desarrollar un entorno UVM para la verificación del IP multi-interfaz específico. En este caso, se reutilizarán aspectos del entorno de verificación UVM básico previamente

implementado. Una vez finalizado el desarrollo del entorno basado en UVM, se generarán una serie de *test* de verificación de la funcionalidad básica del IP.

#### 1.3 PETICIONARIO

Actúa como peticionario del presente Trabajo Fin de Máster la Escuela de Ingeniería de Telecomunicación y Electrónica (EITE) de la Universidad de Las Palmas de Gran Canaria (ULPGC), con el fin de satisfacer los requisitos de la asignatura Trabajo Fin de Máster en el plan de estudios de la titulación Máster Universitario en Ingeniería de Telecomunicación (MUIT).

#### 1.4 ESTRUCTURA DEL DOCUMENTO

El presente documento se encuentra dividido en cuatro partes claramente diferenciadas: Memoria, Pliego de condiciones, Presupuesto y Anexos. La memoria, a su vez, se estructura en seis capítulos y la bibliografía empleada. El contenido de estos capítulos es el que se resume a continuación:

- Capítulo 1. Introducción. Este capítulo recoge los antecedentes que han dado lugar a la realización de este TFM, sus objetivos, el peticionario del mismo, y la estructura del documento.

- Capítulo 2. Universal Verification Methodology. Este capítulo presenta una introducción al

proceso de verificación funcional, así como los aspectos que han propiciado la creación de

la metodología UVM. Además, se introduce esta metodología, incluyendo sus principales

características, los fundamentos en los que se sustenta, y los componentes que integra.

- Capítulo 3. Módulo IP multi-interfaz para la compresión de imágenes. En este capítulo se realiza una descripción detallada del sistema hardware digital que se pretende verificar haciendo uso de la metodología UVM, así como de su test bench original.

- Capítulo 4. Desarrollo del entorno de verificación basado en UVM. En este capítulo se presenta el entorno UVM desarrollado para la verificación funcional del IP multi-interfaz descrito en el Capítulo 3, así como el procedimiento llevado a cabo para su implementación.

- Capítulo 5. Resultados. Este capítulo muestra los resultados obtenidos tras la ejecución de varios test sobre el DUV en el entorno de verificación UVM desarrollado.

- Capítulo 6. Conclusiones. Tras haber completado los objetivos establecidos en este TFM, en este capítulo se recogen las conclusiones obtenidas a partir de su realización, así como las posibles ampliaciones futuras que puedan surgir a raíz de la línea de trabajo iniciada.

#### Capítulo 2. Universal Verification Methodology

En este capítulo se presentan los principales aspectos de la metodología UVM (*Universal Verification Methodology*), utilizada durante el desarrollo del presente TFM. En primer lugar, se realizará una introducción al proceso de verificación y su importancia en el flujo de diseño de sistemas hardware, centrándose particularmente en la verificación funcional. En relación con UVM, se presentará su arquitectura basada en componentes, los fundamentos en los que se basa su propuesta, el lenguaje de verificación hardware que utiliza, etc. Con ello, se asentarán las bases de la metodología con el fin de comprender el porqué de su concepción y uso actual.

#### 2.1 Introducción a la verificación

La verificación es la actividad que determina el correcto funcionamiento de un sistema. En otras palabras, asegura que un diseño cumple perfectamente con las especificaciones funcionales establecidas. En el ámbito del diseño de sistemas hardware digitales, la verificación se centra, en la mayoría de los casos, en asegurar que las especificaciones de diseño están correctamente implementadas en su descripción a nivel RTL (*Register-Transfer Level*) [7].

Este procedimiento es crucial para determinar si un producto final puede ser utilizado, o no, de modo seguro por sus usuarios potenciales. Si se considerase un escenario en el que un producto fuese comercializado hacia los consumidores finales sin seguridad de que se comporta de forma acorde a sus especificaciones, existiría la posibilidad de que el mismo tuviese un comportamiento erróneo. Ello podría ocasionar pérdidas considerables a la compañía, tanto a nivel económico como a nivel de reputación ya que, como es lógico, un usuario no tiene intención de adquirir productos sin la seguridad de que estos operen correctamente [7].

Es una realidad que, hoy en día, la verificación ha adquirido una importancia muy significativa, hasta el punto de que un equipo de desarrollo típico posee el mismo número de ingenieros de verificación que de diseño. Ello es debido al tamaño y la complejidad de los sistemas hardware actuales, que hacen que el proceso de verificación pueda consumir, aproximadamente, el 70% del esfuerzo de un proyecto (tanto económico como temporal) [8]. Y es que un ingeniero de diseño, por lo general, se ciñe a los casos representativos de las especificaciones, y su trabajo finaliza cuando contempla dichos casos en la implementación. Sin embargo, un ingeniero de verificación debe verificar el diseño bajo todo tipo de casos, los cuales tienden a ser infinitos [7].

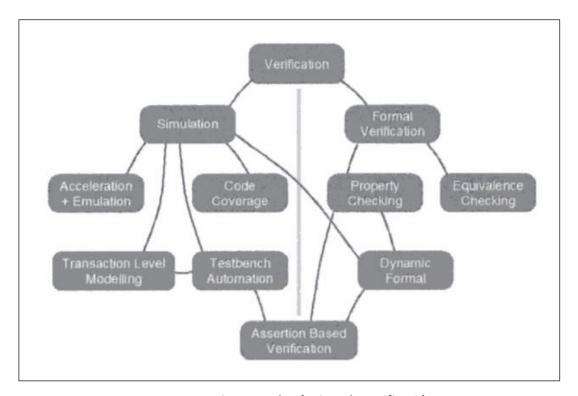

Debido a su trascendencia, existen numerosas técnicas de verificación (Figura 2.1) [8], las cuales se dividen en estáticas (verificación formal) y dinámicas (verificación funcional, basada en simulación y emulación).

Figura 2.1. Diagrama de técnicas de verificación

Por un lado, la verificación formal consiste en el uso de técnicas matemáticas (no requiere de simulación) para comprobar que un diseño cumple con sus especificaciones funcionales o, al menos, con una parte de ellas. Por otro, la verificación funcional tiene como objetivo asegurar que un diseño cumple con la funcionalidad para la que fue implementado [8], [9]. En el caso particular de este TFM, se hará uso de esta última como ámbito de trabajo.

#### 2.2 VERIFICACIÓN FUNCIONAL DE SISTEMAS HARDWARE DIGITALES

La verificación funcional es un tipo de verificación particular que puede probar la existencia de errores funcionales en un diseño, pero no su ausencia, pues ello depende del nivel de cobertura (el porcentaje de casos de funcionalidad comprobados) definido en el Plan de Verificación.

Aunque la verificación formal tiene hoy en día una tendencia creciente, la verificación funcional, especialmente basada en simulación, sigue siendo la más utilizada en la actualidad, debido a la facilidad que ofrece para situar al sistema en múltiples escenarios o casos de uso, sobre todo en los denominados *corner cases*, los cuales son difíciles de alcanzar en situaciones normales [6].

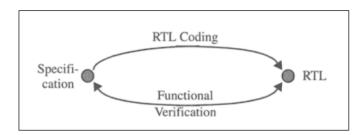

Para aplicar la verificación funcional, en primer lugar, en la etapa de diseño se genera el código RTL del sistema a partir de sus especificaciones funcionales, para posteriormente comprobar que la funcionalidad de este código cumple con las especificaciones inicialmente establecidas [7]. Una descripción gráfica de este procedimiento se muestra en la Figura 2.2.

Figura 2.2. Proceso genérico de diseño y verificación funcional

Así, esta verificación se aplica cuando, conociendo los datos de entrada al DUV, se realiza una comparación de las salidas esperadas con las realmente obtenidas desde el mismo. A la hora de implementar la verificación funcional existen tres métodos o enfoques fundamentales: *Black-Box*, *White-Box* y *Grey-Box*, cuyas diferencias principales consisten en el nivel de conocimiento o de abstracción que se tiene del DUV [7], [9].

- Verificación Black-Box: La verificación funcional se lleva a cabo sin ningún tipo de conocimiento acerca de la implementación del diseño del DUV. Todo el proceso de verificación se realiza a partir de las interfaces disponibles en el DUV, sin acceso directo a sus estados internos, su estructura o su implementación. La decisión de si el resultado de un determinado test es correcto, o no, viene dada por la respuesta en las salidas del DUV ante unos determinados estímulos de entrada. La principal ventaja de este modelo es que no depende de ninguna implementación específica del diseño. Sin embargo, en caso de no obtenerse los resultados esperados, es difícil conocer la fuente del problema.

- Verificación White-Box: En este caso, la verificación funcional permite el acceso y el control absoluto de la estructura interna y la implementación del diseño del DUV. Con ello, se consigue simplificar en gran medida la fase de depuración, permitiendo la posibilidad de localizar el origen de un error con mayor facilidad. Por otra parte, una desventaja de este modelo consiste en la fuerte dependencia con la implementación del diseño, de modo que cualquier modificación interna del DUV llevará asociada una modificación en el test bench.

- Verificación Grey-Box: Este tipo de verificación se encuentra a medio camino entre las dos anteriores, estableciendo un compromiso entre el nivel de abstracción del proceso de

verificación *Black-Box* y el nivel de dependencia con la implementación de la verificación *White-Box*. En otras palabras, la verificación *Grey-Box* únicamente permite el acceso a determinados puntos de la estructura interna y la implementación del diseño del DUV.

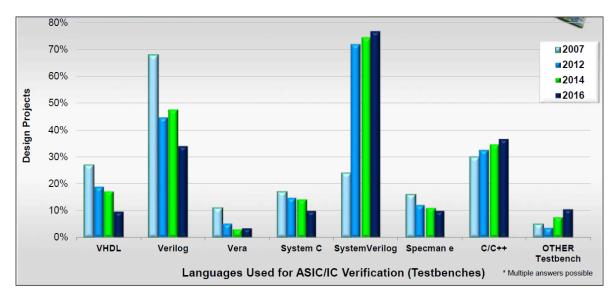

Otro aspecto fundamental a tener en cuenta en la verificación funcional es el lenguaje de verificación hardware a emplear (HVL, Hardware Verification Language). Según el estudio "ASIC/IC and FPGA Functional Verification Study" llevado a cabo por Wilson Research Group en el año 2016 [10], en los últimos 10 años el lenguaje SystemVerilog ha seguido una tendencia muy positiva, situándose en la actualidad como HVL por excelencia para la verificación ASIC/IC, tal y como se muestra en la Figura 2.3.

Figura 2.3. Tendencias en lenguajes de verificación ASIC/IC

En el caso particular de los lenguajes utilizados para la verificación FPGA, se observa una tendencia en la misma línea, con *SystemVerilog* imponiéndose a otros lenguajes como VHDL y *Verilog*, los cuales tienen un mayor mercado como lenguajes de diseño hardware. Debido a este hecho, resulta necesario realizar un breve análisis de las características básicas de este lenguaje, que lo han llevado a ser el más utilizado actualmente en el proceso de verificación funcional.

#### 2.3 SystemVerilog

SystemVerilog es un lenguaje de descripción hardware (HDL), así como un lenguaje de verificación hardware (HVL), que surge desde la necesidad de disponer de un único lenguaje a aplicar, tanto en la etapa de diseño como en la de verificación de un sistema hardware digital. Se trata de una extensión de Verilog-2001, pero que también incluye características propias de otros lenguajes

como VHDL, C y C++ [11]. En la Figura 2.4 se proporciona un desglose de las propiedades más representativas presentes en el lenguaje *SystemVerilog*.

Figura 2.4. Funcionalidades de SystemVerilog

Al haber evolucionado desde el lenguaje de descripción hardware *Verilog*, *SystemVerilog* mantiene las características básicas para la implementación de diseños electrónicos. Sin embargo, el verdadero propósito de este lenguaje se encuentra directamente ligado a la verificación [11], como ya pudo observarse en la Figura 2.3. Las principales razones que justifican este hecho son las siguientes [8]:

- El uso de clases, que permite aplicar las técnicas de la programación orientada a objetos (OOP, Object-Oriented Programming), una característica muy importante para el desarrollo de entornos de verificación complejos. Una clase es un conjunto de variables y rutinas que definen las características y el comportamiento del objeto a referenciar y, en SystemVerilog, son elementos dinámicos que permiten el modelo de herencia simple y que pueden ser parametrizadas (función básica de C++). La herencia de clases permite reutilizar código existente, de modo que una subclase solamente requiera implementar ciertas características adicionales.

- La posibilidad del uso de assertions y medidas de cobertura. Un assertion no es más que una propiedad que se describe dentro del mismo código del diseño y que se comprueba automáticamente durante toda la fase de simulación. SystemVerilog soporta la verificación ABV (Assertion-Based Verification), además de definir un mecanismo de cobertura y de adquisición de datos flexible. Esto puede utilizarse, por ejemplo, para comprobar que los

assertions se han cumplido durante la ejecución de test benches automáticos utilizando una generación de estímulos aleatoria con restricciones.

- La aleatorización de los datos. Como se ha dejado entrever en el punto anterior,

SystemVerilog permite la generación de estímulos de forma puramente aleatoria, o bien aleatoria con restricciones.

- La utilización de diferentes tipos de datos, tanto estáticos como dinámicos.

- La posibilidad de usar interfaces para encapsular las comunicaciones. Las interfaces, además de ser un conjunto ordenado de datos, pueden contener comportamientos y utilizarse para describir modelos funcionales de un bus. En este sentido, SystemVerilog soporta el uso de comunicaciones TLM, lo que también ofrece la posibilidad de reutilización de entornos de verificación en diferentes niveles de abstracción.

- La interfaz DPI (*Direct Programming Interface*), que permite referenciar funciones descritas en C de forma directa en el código *SystemVerilog*.

- El uso de paquetes (packages) para compartir código entre distintos módulos. Un paquete

incluye declaraciones y definiciones que se agrupan bajo un nombre común, el del propio

paquete. Estas declaraciones pueden incluir tipos, constantes, funciones, tareas, clases...

Es por todas estas características que *SystemVerilog* se ha consolidado hoy en día como lenguaje de verificación hardware por excelencia. De ahí que la metodología UVM haga uso del mismo como HVL para la implementación de entornos de verificación.

#### 2.4 Introducción a UVM

A lo largo de este capítulo se han ido indicando las diferentes necesidades que han surgido en la verificación funcional con la evolución de la complejidad de los sistemas hardware, hasta el punto del establecimiento de *SystemVerilog* como HVL de referencia. Todo ello invita a pensar en la necesidad de disponer de una metodología estándar que proporcione una guía para la aplicación de diversas técnicas de verificación, de modo que se consiga la máxima eficiencia y eficacia posible en el desarrollo de un diseño electrónico.

Es por ello que surge UVM (*Universal Verification Methodology*), un estándar de *Accellera Systems Initiative* que fue desarrollado mediante el trabajo cooperativo de los principales fabricantes y consumidores de herramientas EDA (*Electronic Design Automation*). Todo ello fue posible gracias a la sólida base ya existente en OVM (*Open Verification Methodology*) y a las contribuciones incluidas desde VMM (*Verification Methodology Manual*) [12].

Entrando más en detalle, UVM es un híbrido de tecnologías de diferentes desarrolladores, tomando de cada una de ellas sus características más destacadas [12]:

- AVM (Advanced Verification Methodology) de Mentor.

- OVM de *Mentor* y *Cadence*.

- eRM (e Reuse Methodology) de Verisity.

- VMM-RAL (Verification Methodology Manual Register Abstraction Layer) de Synopsys.

- Resources, TLM2 y Phasing, desarrolladas por Mentor específicamente para UVM.

En conjunto, se obtiene una metodología potente y flexible con la que es posible implementar entornos de verificación escalables, reusables e interoperables, cuyas características fundamentales son [3]:

- A través de la metodología y una biblioteca de código, ofrece la posibilidad de dividir de manera limpia el entorno de verificación en un conjunto de ítems de datos (estímulos y respuestas) y componentes de verificación (UVC). Con esto se consigue estructurar y organizar los objetos y las funcionalidades del entorno de verificación de forma más sencilla, así como incrementar su reusabilidad.

- Posee clases e infraestructuras para permitir el control minucioso de los flujos de datos secuenciales a enviar como estímulos al DUV. Además, ofrece un mecanismo de generación de estímulos que puede ser adaptado para incluir transacciones jerárquicas definidas por el usuario, o crear flujos de transacciones.

- Utiliza TLM para facilitar la comunicación entre componentes de verificación descritos en diferentes lenguajes como, por ejemplo, VHDL, *SystemVerilog* o *SystemC*, entre otros.

- Debido a su estructura de clases y su característica de herencia, un buen flujo de trabajo a

partir de clases base permite desarrollar entornos de verificación automatizados con una

topología jerárquica y reutilizable.

- Proporciona los mecanismos necesarios para llevar a cabo una verificación dirigida por métricas de cobertura (MDV, Metric-Driven Verification) sobre los UVC reusables.

- Ofrece capacidades de análisis y depuración a través de mecanismos como el informe de errores, el registro de transacciones, el rastreo de secuencias, etc.

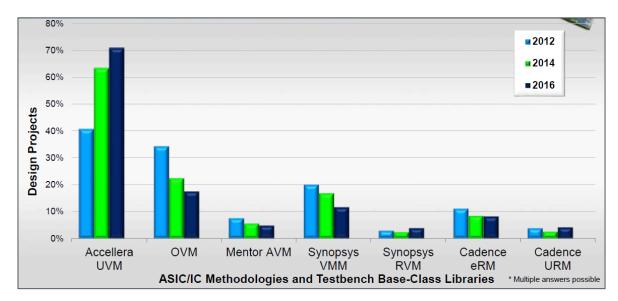

Todas estas características han hecho que, según el estudio [10], y tal y como puede verse en la Figura 2.5, UVM se haya consolidado como la metodología de verificación ASIC/IC más utilizada desde su creación. Al igual que en el caso del lenguaje *SystemVerilog* como HVL, los resultados del

estudio para la verificación FPGA muestran igualmente cómo UVM sigue destacando frente al resto de metodologías del mercado.

Figura 2.5. Tendencias en metodologías de verificación ASIC/IC

Una vez definidas las principales características que hacen que UVM sea la metodología de verificación más adoptada por los desarrolladores de hardware digital, se procede a continuación a estudiar en detalle los fundamentos en los que se basa la misma, así como los componentes y las funcionalidades que comprende un entorno de verificación UVM.

#### 2.5 FUNDAMENTOS DE UVM

#### 2.5.1 BIBLIOTECA DE CLASES

Desde un punto de vista general, UVM consiste en una biblioteca de clases base, utilidades y macros descritas en *SystemVerilog* que facilita la creación de entornos de verificación estructurados. Estos componentes pueden encapsularse e instanciarse jerárquicamente, dando lugar a un *test bench*, y son controlados a través de un conjunto de fases (*phases*) para inicializar, ejecutar y completar cada uno de los *test* [3]. Todas estas fases, que se definirán posteriormente, se encuentran integradas en la clase base de la biblioteca (uvm\_object), pero puede extenderse por herencia para ajustarse a los requisitos de cada entorno de verificación.

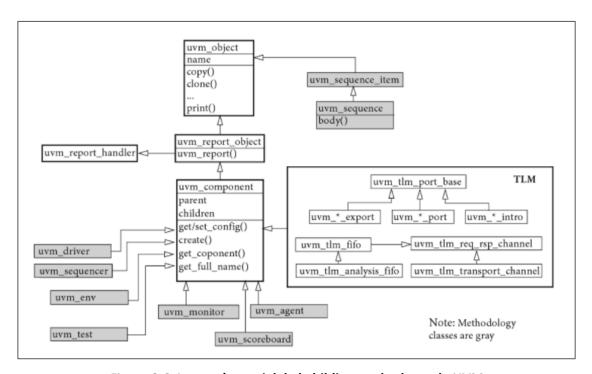

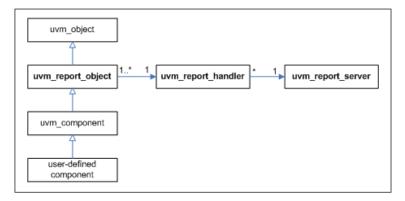

De entre las diferentes clases incluidas en el paquete UVM pueden distinguirse tres grupos fundamentales, los cuales se describen a continuación [13]. Seguidamente, en la Figura 2.6 se incluye un diagrama de bloques que recoge la jerarquía de los grupos de componentes a describir.

- uvm\_object. Se trata de la clase base o padre en la jerarquía de clases de UVM, de la cual hereda el resto de clases. Define y automatiza una serie de métodos para la implementación de funcionalidades comunes a todas las clases, así como atributos de identificación de un objeto.

- uvm\_component. Es la clase padre de todos los UVC a integrar en un entorno de verificación UVM. Es una clase bastante importante, pues incluye todas las funcionalidades de la metodología comunes a los UVC (Factory, fases, etc.).

- uvm\_sequence\_item y uvm\_sequence. Son las clases utilizadas para la generación de estímulos y para agrupar las respuestas del DUV que se desea verificar.

Figura 2.6. Jerarquía parcial de la biblioteca de clases de UVM

Los objetos pertenecientes a las subclases de uvm\_component son estáticos y forman parte de la jerarquía del *test bench* durante toda la simulación. Los objetos instanciados de las clases uvm\_sequence\_item y uvm\_sequence, por su parte, son dinámicos y están relacionados con los datos de entrada y de salida del DUV, por lo que se crean, se utilizan, y se descartan en tiempo de ejecución [12].

Tal y como se especifica en la Figura 2.6, las clases de la metodología a las que da acceso UVM son las que se destacan en gris (que serán estudiadas en detalle más adelante), de modo que cada una de ellas ya incluye las funcionalidades básicas propias de cada componente o elemento. De esta manera se aumenta la reusabilidad y se facilita la labor del ingeniero a la hora de crear un entorno

de verificación. Ello es debido a que se evita tener que crear los atributos y las funciones genéricas de cada uno de estos componentes.

Además, UVM también define un paquete para gestionar la comunicación TLM, en el cual se encuentran los diferentes puertos e interfaces para efectuar las comunicaciones entre componentes. Como ya se ha comentado, estas comunicaciones permiten separar el código en componentes, lo que aporta reusabilidad, interoperabilidad y modularidad al diseño del entorno de verificación [3].

La biblioteca de UVM se encuentra contenida en el paquete uvm\_pkg, que agrupa todas las clases ya citadas. Por tanto, para poder hacer uso de las mismas, este paquete debe ser importado en el módulo *Top* que, como se verá posteriormente, actúa de enlace entre el DUV y el entorno de verificación UVM [14].

#### 2.5.2 FACTORY

De cara a proporcionar una configuración dinámica y flexible, los diferentes componentes que integran un entorno de verificación UVM son registrados en la *Factory*. Este mecanismo se utiliza para crear dichos objetos y componentes, posibilitando jerarquías de componentes dinámicamente configurables, así como sustitución de objetos sin necesidad de modificar el código [14].

La operación de registrar objetos y componentes en la *Factory* de UVM puede efectuarse de diferentes maneras. Sin embargo, la más común consiste en hacer uso de dos macros parametrizables con el nombre del objeto o componente a registrar. Estas macros son `uvm\_object\_utils y `uvm\_component\_utils (en el caso de que el objeto o componente a registrar sea de un tipo parametrizable, se sustituyen por `uvm\_object\_param\_utils y `uvm component param utils, respectivamente) [15].

Estas macros proporcionan la implementación del método virtual create() como nuevo constructor, que reemplaza al tradicional método new(). Así, evita crear componentes o transacciones de tipo fijo, sino que los referencia en la *Factory* y devuelve un identificador (*handler*). Con ello, se posibilitan las sustituciones de tipo en tiempo de ejecución, sin tener que acceder internamente a la clase [15]. Otro método importante que proporcionan dichas macros es get\_type\_name(), que retorna el identificador de un objeto o componente y resulta bastante útil en tareas de depuración [14].

En cualquier caso, la definición del constructor new () en UVM es obligatoria, al contrario que el uso de la *Factory*. Aunque, como se ha comentado, el uso de la *Factory* y sus macros ofrece unas prestaciones únicas que aportan dinamismo al proceso de verificación.

#### 2.5.3 FASES DE UVM

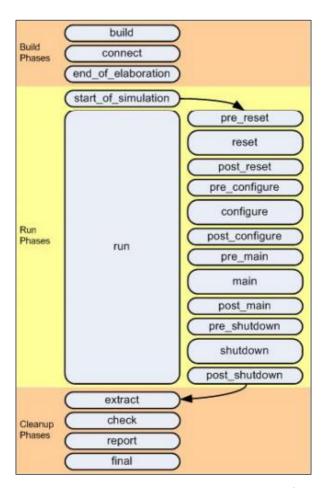

Una simulación en un entorno de verificación UVM consiste en la ejecución en secuencia de una serie de fases. En *SystemVerilog*, las clases se referencian durante la simulación, por lo que es necesario asegurarse de que el entorno haya sido creado en su totalidad previamente a comenzar con la ejecución de un *test*, o que los diferentes elementos hayan sido construidos antes de intentar conectarlos. Para ello, en UVM se definen las fases que se muestran en la Figura 2.7, las cuales se dividen en tres grandes grupos y se ejecutan de forma secuencial siguiendo el orden especificado.

La ejecución de estas fases comienza tras la llamada a la función run\_test(), que inicia la simulación de un determinado *test*, el cual se especifica, bien como parámetro de dicha función, o bien desde la línea de comandos a través de la variable global del entorno UVM TESTNAME [12].

Figura 2.7. Fases de UVM y orden de ejecución

Las fases de construcción o de creación (*build phases*) se ejecutan al comienzo de la simulación UVM y su propósito principal es el de construir, configurar y conectar la jerarquía de componentes del entorno de verificación. Todas estas fases son funciones que se ejecutan en tiempo cero de simulación, es decir, no consumen tiempo [12].

Durante las fases de ejecución (*run phases*) se generan los estímulos y se suceden las comunicaciones de transacciones entre los componentes del entorno, así como la interactuación con el DUV. Dentro de este conjunto se encuentra la única fase que está definida como tarea y que consume tiempo de ejecución, la fase run phase [12].

Finalmente, las fases de procesamiento (*clean up phases*) se encargan de extraer la información generada por ciertos componentes, de modo que determinan si la ejecución del *test* ha alcanzado o no los objetivos planteados. Estas fases también son funciones que no consumen tiempo de ejecución [12].

Cabe destacar que la clase uvm\_component hereda los métodos y atributos de la clase uvm\_report\_object, que define un método virtual para cada una de las fases de UVM. Por lo tanto, si alguna de estas fases no está incluida en la clase base de un componente determinado, este no participará durante la ejecución de la misma. De esta forma, se consigue reducir el tiempo y la carga de procesamiento en la CPU (*Central Processing Unit*).

En un entorno de verificación común, las fases más importantes y utilizadas son las siguientes [14]:

- build\_phase(). En esta fase se construye la jerarquía de componentes del entorno de verificación siguiendo una filosofía *top-down*, desde el nivel más alto de la jerarquía hasta los más bajos.

- connect\_phase(). En esta fase se realiza el conexionado de los componentes incluidos en el nivel de jerarquía actual. En este caso, se sigue una filosofía *bottom-up*, desde los componentes de los niveles más bajos de la jerarquía hasta el nivel más alto.

- run\_phase(). En esta fase se describe el comportamiento de cada uno de los componentes que constituyen el entorno de verificación. Todos los componentes implementan esta fase de forma paralela en el tiempo. Como puede verse en la Figura 2.7, esta fase está compuesta por múltiples sub-fases, si bien para un test de complejidad baja o media estas sub-fases no resultan de utilidad, por lo que el código correspondiente se escribe directamente bajo la denominación de run\_phase. Como se trata de la única fase que consume tiempo de ejecución, resulta necesario determinar cuándo ha finalizado, para lo que se utiliza el mecanismo de *objections*. Este mecanismo contabiliza el número de

componentes y secuencias que aún se encuentran participando en el *test bench*, para lo que define tres métodos:

- o raise\_objection(). Señaliza el momento en el que se inicia la ejecución de la fase run phase en un componente.

- o drop\_objection(). Señaliza el momento en el que finaliza la fase run\_phase en un componente. Una vez invocado este método en todos los componentes que hayan utilizado anteriormente el método raise\_objection, se da por finalizada la simulación y se prepara la ejecución de las fases de procesamiento.

- o set\_drain\_time(). Establece un intervalo de tiempo a esperar de cara a finalizar la simulación una vez todos los componentes hayan efectuado la llamada al método drop objection.

Otras fases de gran utilidad pueden ser las siguientes:

- end\_of\_elaboration\_phase() / start\_of\_simulation\_phase(). En estas fases

se puede mostrar en pantalla ciertos aspectos tras las fases de creación del test bench,

como puede ser información acerca de la topología final de la jerarquía del entorno o

información de configuración.

- report\_phase(). Esta fase es utilizada para mostrar en consola los resultados de la simulación, o bien escribirlos en un archivo externo.

#### 2.5.4 MECANISMO DE CONFIGURACIÓN

UVM proporciona un mecanismo de configuración flexible a través de una base de datos con el fin de permitir la configuración de ciertas características de un componente sin necesidad de hacerlo de forma estática, o bien utilizar la *Factory* como intermediario. Ello otorga reusabilidad a los componentes de verificación o UVC, ya que pueden configurarse componentes genéricos para un modo de operación específico en tiempo de ejecución.

Este mecanismo se basa en la clase uvm\_config\_db, que contiene una interfaz simplificada de acceso a los objetos de configuración que han sido creados en la base de datos. Haciendo uso de los métodos set() y get(), es posible leer o escribir los parámetros de configuración que se deseen para determinados objetos. Estas funciones son estáticas, por lo que deben invocarse mediante el operador "::" [15]. La definición de estos métodos es la siguiente [14]:

- uvm\_config\_db#(T)::set(context, inst\_name, field\_name, value).Permite incluir un nuevo elemento en la base de datos, o bien actualizar uno ya existente.

- uvm\_config\_db#(T)::get(context, inst\_name, field\_name, value).Permite recuperar un elemento de la base de datos, siempre y cuando dicho elemento se encuentre en ella.

En ambos casos, el argumento  $\mathbb{T}$  indica el tipo de dato a incluir o recuperar, pudiendo utilizar incluso tipos definidos por el usuario. En cuanto a los argumentos de ambos métodos [13], [14]:

- El contexto (context) indica el punto de entrada de la jerarquía desde el cual es accesible el objeto de la base de datos. En caso de utilizarse el valor this, hace referencia al componente actual en el que se ejecuta el método. Si el contexto es null o uvm rot::get(), es aplicable a todo el entorno.

- El nombre del componente (inst\_name) es un *String* que indica la ruta jerárquica desde el contexto hasta el nombre que se le dio al componente sobre el que se desea actuar.

- El nombre del campo (field\_name) es un String que actúa como identificador o etiqueta del objeto en la base de datos.

- El campo valor (value) hace referencia al valor que se desea aplicar en el caso del método set (), o a la variable en la que se desea recibir el valor, en el caso del método get ().

## 2.5.5 MECANISMO DE MENSAJES

Un aspecto básico de un entorno de verificación consiste en poder hacer uso de un mecanismo de mensajes de información o de errores. Como se observa en la Figura 2.8, todos los componentes heredan de la clase uvm\_report\_object, la cual ofrece una interfaz que posibilita el uso de este tipo de mensajería.

Esta interfaz se basa en delegar las tareas de comunicación en una clase interna, la clase uvm\_report\_handler. Dicha clase almacena la configuración del mecanismo de mensajes y, en base a ello, decide qué mensajes mostrar al usuario y cuáles no. En caso de que un mensaje deba ser mostrado, esa tarea se delega, a su vez, en la clase uvm\_report\_server, que se encarga de generar los mensajes conforme a un formato dado [14].

Figura 2.8. Clases para la mensajería

Este mecanismo de mensajes contiene cuatro macros, a partir de las cuales se puede controlar el entorno de verificación. Estas macros son las que se listan a continuación. Además, en la Tabla 2.1 se detallan las acciones que implica cada una de ellas [3], [14].

- `uvm info(string id, string message, int verbosity).

- `uvm warning(string id, string message).

- `uvm\_error(string id, string message).

- `uvm fatal(string id, string message).

Tabla 2.1. Acciones por defecto en las macros del mecanismo de mensajes

| TIPO        | ACCIÓN POR<br>DEFECTO | DESCRIPCIÓN                                                                                           |  |  |

|-------------|-----------------------|-------------------------------------------------------------------------------------------------------|--|--|

| UVM_INFO    | UVM_DISPLAY           | Envía un mensaje por la salida estándar (consola).                                                    |  |  |

| UVM_WARNING | UVM_DISPLAY           | Envía un mensaje por la salida estándar (consola).                                                    |  |  |

| UVM_ERROR   |                       | Envía un mensaje por la salida estándar (consola).                                                    |  |  |

|             | UVM_DISPLAY           | Finaliza la simulación si el número de mensajes de error supera un número especificado de errores (el |  |  |

|             | UVM_COUNT             |                                                                                                       |  |  |

|             |                       | valor por defecto es cero).                                                                           |  |  |

| UVM_FATAL   | UVM_DISPLAY           | Envía un mensaje por la salida estándar (consola).                                                    |  |  |

|             | UVM_EXIT              | Finaliza la simulación inmediatamente.                                                                |  |  |

En cuanto a la estructura de las macros, el primer argumento es una etiqueta que suele utilizarse como filtro, mientras que el segundo se corresponde con el mensaje de información que se desea imprimir por la salida estándar (consola). Finalmente, en el caso de la macro `uvm\_info, se debe indicar un valor de *verbosity* como último argumento.

El argumento verbosity indica el nivel de importancia del mensaje y, dependiendo del valor que se haya asignado a la variable global del entorno UVM\_VERBOSITY, el mensaje se mostrará o no.

Este nivel de importancia es de carácter inverso al valor de esta variable, es decir, que será mayor cuanto menor sea el valor de *verbosity*. UVM discretiza los valores de *verbosity* que se pueden tomar, los cuales se recogen en la Tabla 2.2 [3].

Tabla 2.2. Valores de verbosity

| VERBOSITY  | VALOR |  |

|------------|-------|--|

| UVM_NONE   | 0     |  |

| UVM_LOW    | 100   |  |

| UVM_MEDIUM | 200   |  |

| UVM_HIGH   | 300   |  |

| UVM_FULL   | 400   |  |

| UVM_DEBUG  | 500   |  |

De este modo, si la variable global UVM\_VERBOSITY toma el valor UVM\_DEBUG, se mostrarán todos los mensajes `uvm\_info introducidos en el entorno. Por otra parte, si a dicha variable se le asigna el valor UVM\_NONE, solamente se mostrarán los mensajes `uvm\_info cuyo argumento verbosity sea UVM\_NONE. Al igual que el *test* a ejecutar en el entorno de verificación UVM, el valor de esta variable puede especificarse, bien localmente, a través de la función set\_report\_verbosity\_level(), o bien desde línea de comandos.

## 2.5.6 TLM

Una de las claves para la productividad en la verificación es conseguir enfocar los problemas desde un nivel de abstracción apropiado. La interfaz con el DUV se representa a nivel de señales, pero en el caso de un entorno de verificación complejo, las transferencias de datos que requiere el diseño son muy diversas y complejas. Por lo tanto, el nivel de abstracción debe ser bastante elevado, a nivel de transacción. Para ello, UVM proporciona un conjunto de canales e interfaces de comunicación TLM (*Transaction-Level Modeling*), que permiten conectar los diferentes componentes del entorno de verificación a nivel de transacciones [15].

En UVM, TLM permite comunicar componentes descritos a diferentes niveles de abstracción y que implementen una misma interfaz. Como pudo verse en la Figura 2.6, la biblioteca de clases de UVM describe, en su jerarquía, un subconjunto para TLM en el que se incluyen una serie de interfaces y puertos con el objetivo de posibilitar dichas comunicaciones. Cada interfaz TLM consiste en uno o varios métodos que se utilizan para intercambiar datos, normalmente transacciones.

El uso de TLM proporciona un conjunto de beneficios con respecto a trabajar con comunicaciones a nivel de señales [3]:

- Los modelos TLM son más concisos y rápidos de simular que los modelos RTL.

- Los modelos TLM se sitúan en un mayor nivel de abstracción, que se acerca mucho más al nivel de abstracción deseado por los ingenieros de diseño o de verificación. De este modo, los modelos son más fáciles de escribir y de entender para desarrollos en equipo.

- Los modelos TLM tienden a ser más reusables ya que, además de ofrecer el uso de técnicas de la programación orientada a objetos, se extraen los detalles que dificultan la reusabilidad fuera de estos modelos.

## 2.5.6.1 TLM PORTS Y TLM EXPORTS

De cara a enviar y recibir transacciones de datos, UVM hace uso de *TLM ports* y *TLM exports*. Los primeros se encargan de especificar el conjunto de métodos que pueden ser utilizados y de iniciar las peticiones de transacción, mientras que los segundos proporcionan la implementación de dichos métodos. Estos puertos deben conectarse a un único puerto en la fase de construcción del entorno, normalmente en la fase connect\_phase, tras la creación de los componentes y previamente a la simulación. Dicha conexión se implementa a través del método connect (), que es invocado por los *TLM ports* [3].

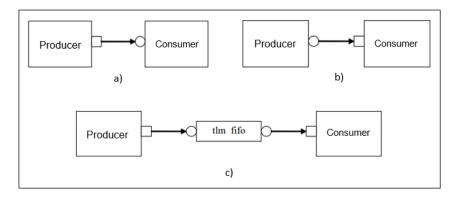

Atendiendo a su representación gráfica, TLM incluye una notación para diferenciar los tipos de comunicación. Así, los *TLM ports* se representan gráficamente con un cuadrado en la comunicación, mientras que los *TLM exports* se identifican mediante un círculo.

La Figura 2.9 muestra un ejemplo de comunicación de transacciones desde un componente de tipo *Producer*, a otro de tipo *Consumer*, mediante un *TLM port* y un *TLM export*. En el ejemplo a), el *Producer* inicia el envío de transacciones haciendo uso de un método put (), mientras que en el ejemplo b), el *Consumer* solicita la recepción de transacciones mediante un método get () [3], [15].

Además, también sería posible incluir una cola entre ambos componentes, por ejemplo, de tipo FIFO (*First In, First Out*). De este modo, la cola implementaría los *TLM exports* y tanto *Producer* como *Consumer* podrían hacer uso de los métodos put () y get (), desde sus *TLM ports*, sobre la FIFO, que es lo que sucede en el ejemplo c).

Figura 2.9. Comunicación TLM port – TLM export

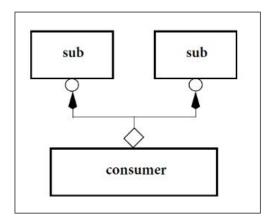

## 2.5.6.2 TLM ANALYSIS PORTS Y TLM ANALYSIS EXPORTS

En ocasiones, la complejidad del entorno de verificación hace que cierta información deba ser distribuida al resto de componentes. Por este motivo surgen los *TLM analysis ports* y los *TLM analysis exports*. A diferencia de los *TLM ports* y los *TLM exports*, en los que la comunicación se establece forzosamente entre dos componentes, este nuevo tipo de puertos permite que un *TLM analysis port* tenga varios *TLM analysis exports* conectados al mismo, o incluso ninguno. En este caso, únicamente se implementa un método write(), que consiste en efectuar una transmisión *broadcast* a todos los *TLM analysis exports* que hayan decidido conectarse (suscriptores) [3], [12], [15].

Como puede verse en la Figura 2.10, el modo de representar gráficamente un *TLM analysis port* es mediante un rombo. En dicha figura, se encuentra un componente de tipo *Consumer* que retransmite las transacciones recibidas a través de su *TLM analysis port*, al que se encuentran conectados dos componentes de tipo *Subscriber*.

Figura 2.10. Comunicación TLM analysis port – TLM analysis exports

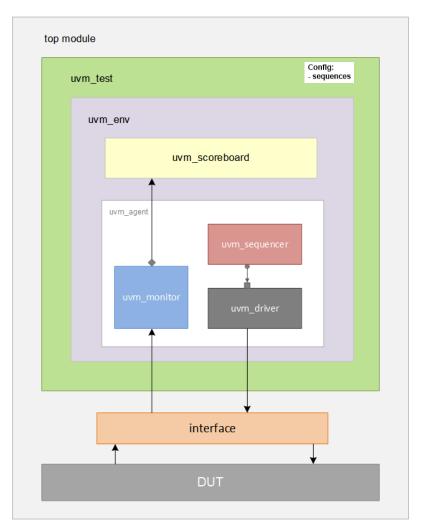

### 2.6 ESTRUCTURA DE UN ENTORNO DE VERIFICACIÓN UVM

Un *test bench* UVM sigue el planteamiento introducido acerca de la verificación funcional, pero ofrece la posibilidad de tener un mayor control sobre los siguientes procesos:

- La generación de los estímulos de entrada.

- La recepción de las salidas.

- La comparación de los datos de salida con los esperados.

Un entorno de verificación UVM se crea a partir de la instanciación de componentes de todas y cada una de las clases que heredan de uvm\_component, las cuales se presentaron en el apartado 2.5.1 Biblioteca de clases. La jerarquía se determina a partir de la relación entre estos componentes, de forma que unos son instanciados dentro de otros. Esta jerarquía puede observarse en la Figura 2.11, con un modelo de referencia básico de lo que sería un entorno de verificación de un IP mediante la metodología UVM.

Figura 2.11. Modelo básico de entorno de verificación UVM

En el diagrama representado en la Figura 2.11, la parte correspondiente al entorno UVM es la que engloba el módulo *test* (*uvm\_test*), que es el mayor nivel en la jerarquía. Este módulo puede incluir uno o varios componentes *Environment* (*uvm\_env*), que no es más que un contenedor para integrar los diferentes UVC, los cuales implementarán el desarrollo de las funcionalidades del *test bench*. El componente *test* también es el encargado de inicializar los estímulos.

Además, para comunicar el entorno de verificación con el DUV (o DUT), se hace uso de un módulo *top*, que instancia el DUV y conecta sus puertos a una interfaz virtual (*interface*) accesible desde el *test bench*. Desde este módulo también se lanza la ejecución del *test*.

Llegados a este punto, se va a proceder a describir con mayor detalle cada uno de los componentes que pueden formar parte de un entorno de verificación basado en UVM.

#### 2.6.1 SECUENCIAS

Una Secuencia UVM (*UVM Sequence*) es un objeto que hereda de uvm\_sequence y contiene el comportamiento para generar estímulos en forma de transacciones TLM durante el tiempo de simulación (run\_phase). Por lo tanto, cada secuencia estará parametrizada con el tipo de transacción que va a generar. Las secuencias no forman parte de la jerarquía de componentes, sino que se trata de objetos dinámicos. Estos objetos, además, pueden tener su propia jerarquía, incluyendo secuencias dentro de otras secuencias [15].

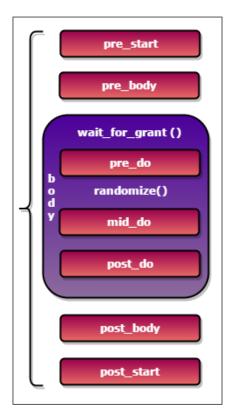

Al igual que para los componentes de la jerarquía en un entorno de verificación UVM, cuyas fases determinan la ejecución en la simulación, las secuencias UVM también siguen un patrón secuencial de tareas a ejecutase, las cuales son exclusivas de la clase uvm\_sequence. Este patrón se encuentra representado en la Figura 2.12.

La tarea principal es la tarea body(), que es la responsable de la generación de transacciones. Otras tareas que podrían utilizarse son  $pre_body()$  y  $post_body()$ , que permiten realizar acciones de inicialización o de sincronismo con otros eventos, antes o después de la ejecución de la tarea body(), respectivamente.

Figura 2.12. Tareas en la ejecución de una secuencia

UVM proporciona dos macros para crear, aleatorizar y enviar las transacciones de una secuencia, que son `uvm\_do y `uvm\_do\_with. La principal diferencia entre ambas consiste en que la segunda ofrece la posibilidad de incluir restricciones en la aleatorización de los campos de una transacción [14]. Sin embargo, se recomienda hacer uso directamente de las funciones start\_item() y finish\_item(), las cuales son invocadas implícitamente por las dos macros comentadas. Con la primera, se bloquea la ejecución hasta que el componente Sequencer (componente encargado de enviar la transacción) esté listo para enviar la transacción de estímulos, mientras que la segunda hace lo propio hasta que la transacción sea enviada [12]. Entre estas dos funciones, se aleatorizan los campos de la transacción mediante la ejecución del método randomize(), que también permite la opción with{} para la inclusión de restricciones.

## 2.6.1.1 TRANSACCIONES

Una transacción UVM o ítem de datos es un objeto que hereda de la clase uvm\_sequence\_item. Este tipo de objetos consiste en una serie de campos de datos requeridos para la generación de estímulos. Dichos campos de datos suelen ser aleatorios para luego incluir restricciones en los mismos y, por lo general, coinciden con las señales específicas a enviar o a leer desde los puertos del DUV [13].

Como ya se ha comentado, las transacciones en UVM se generan en las secuencias, que se encargan de darles valores a sus campos, bien de forma aleatoria, o bien con valores específicos indicando restricciones en el código. Además, las mismas se transmiten entre los diferentes componentes que las usan haciendo uso de los puertos TLM.

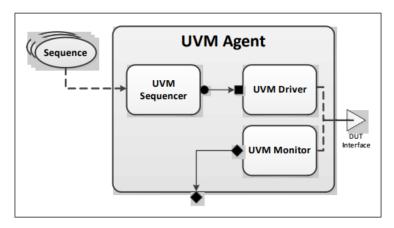

#### 2.6.2 COMPONENTE AGENT

Un *UVM Agent* es un componente de la jerarquía que se deriva de la clase uvm\_agent y que agrupa y estructura otros UVC, los cuales interactúan con una interfaz específica del DUV. Un componente *UVM Agent* genérico incluye, a fin de crear un nivel de abstracción mayor, un componente *UVM Sequencer*, un componente *UVM Driver* y un componente *UVM Monitor*. De este modo el componente *Sequencer* se encargará de controlar el flujo de estímulos (los cuales le llegan en forma de secuencia), el componente *Driver* de aplicar dichos estímulos sobre la interfaz con el DUV, y el componente *Monitor*, como su propio nombre indica, de monitorizar la interfaz con el DUV [15].

En la Figura 2.13 se muestra una representación gráfica de un componente *UVM Agent* genérico.

Figura 2.13. Agente UVM

Además, cabe comentar que los componentes *UVM Agent* pueden ser configurados bien como activos, o bien como pasivos. En el primer caso, su funcionalidad es la de captar estímulos y conducirlos hacia el DUV, mientras en el segundo, solamente se encarga de muestrear las señales en la interfaz con el DUV, sin controlarla. Por tanto, un componente *Agent* pasivo no necesita componentes *Sequencer* ni *Driver*, sino únicamente un componente *Monitor* para acceder a dicha interfaz [3], [13].

Además de los UVC ya citados que se integran en un componente *UVM Agent*, el mismo también puede incluir otros componentes. Estos componentes pueden ser: modelos TLM, colectores de

cobertura, comprobadores de protocolo, etc. [15]. Sin embargo, en el caso particular de este TFM, únicamente será necesario hacer uso de los tres componentes principales ya mencionados, los cuales se van a describir con mayor detalle a continuación.

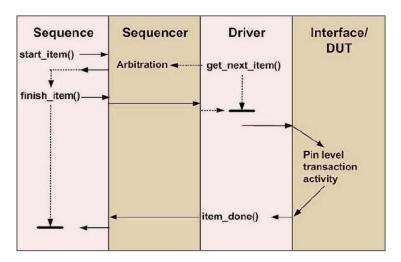

### 2.6.2.1 COMPONENTE SEQUENCER

Un *UVM Sequencer* es un componente que se deriva de la clase uvm\_sequencer y que actúa como un medio de arbitraje para controlar el flujo de transacciones con protocolo *request* y *response* entre las secuencias y el componente *Driver* (comunicación bidireccional). Esta comunicación entre el componente *Sequencer* y el componente *Driver* se efectúa a través de puertos TLM (cuyos puertos se heredan directamente de las clases uvm\_sequencer y uvm\_driver) y sigue un protocolo de *handshake* [13], [15].

Este protocolo de comunicación se muestra en la Figura 2.14, donde en primer lugar, la secuencia informa al componente *Sequencer* sobre una transacción disponible para el componente *Driver* (start\_item()). Una vez que el componente *Driver* haga una petición de recepción de una nueva transacción al componente *Sequencer* (función bloqueante get\_next\_item() sobre su puerto TLM), la secuencia es informada y se envía dicha transacción al componente *Driver* (finish\_item()). Finalmente, el componente *Driver* informa a la secuencia de que ya ha hecho uso de la transacción mediante la función item\_done() sobre su puerto TLM, con la que también puede enviarse información adicional a la secuencia.

Figura 2.14. Protocolo de handshake Sequencer-Driver