# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### PROYECTO FIN DE CARRERA

## GENERACIÓN DE VECTORES PARA LA VERIFICACIÓN DE CIRCUITOS BOOLEANOS MEDIANTE MILP

Titulación: Ingeniería en Electrónica

Autor: María de las Nieves Gloria Hernández González

Tutores: Dr. Carlos Javier Sosa González

Dr. Carlos Salvador Betancor Martín

Fecha: Junio 2017

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### PROYECTO FIN DE CARRERA

# GENERACIÓN DE VECTORES PARA LA VERIFICACIÓN DE CIRCUITOS BOOLEANOS MEDIANTE MILP

#### **HOJA DE FIRMAS**

#### **Alumna**

Fdo.: María de las Nieves Gloria Hernández González

Tutor Tutor

Fdo.: Dr. Carlos Javier Sosa González Fdo.: Dr. Carlos Salvador Betancor Martín

Fecha: Junio 2017

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### **PROYECTO FIN DE CARRERA**

## GENERACIÓN DE VECTORES PARA LA VERIFICACIÓN DE CIRCUITOS BOOLEANOS MEDIANTE MILP

## **HOJA DE EVALUACIÓN**

| Calificación: |              |

|---------------|--------------|

| Presidente    |              |

| Fdo.:         |              |

| Vocal         | Secretario/a |

| Fdo.:         | Fdo.:        |

Fecha: Junio 2017

# ÍNDICE

| indice de l     | riguras                                            | IV |

|-----------------|----------------------------------------------------|----|

| Índice de 🏾     | Гablas                                             | V  |

| MEMORI <i>A</i> | $\mathbf{A}$                                       | 1  |

| Resumen         |                                                    | 3  |

| Abstract        |                                                    | 5  |

| Acrónimos       | 5                                                  | 7  |

| CAPÍTULC        | ) <sub>1</sub>                                     | 9  |

| INTRODUC        | CIÓN Y ANTECEDENTES                                | 9  |

| 1.1 In          | troducción                                         | 9  |

| 1.2 A1          | ntecedentes                                        | 12 |

| 1.3             | bjetivos                                           | 13 |

| 1.4 P€          | eticionario                                        | 13 |

| 1.5 O           | rganización del documento                          | 13 |

| 1.5.1           | Memoria                                            | 14 |

| 1.5.2           | Presupuesto                                        | 14 |

| 1.5.3           | Pliego de condiciones                              | 14 |

| 1.5.4           | Anexo I: Códigos                                   | 15 |

| 1.5.5           | Anexo II: Banco de Pruebas                         | 15 |

| CAPÍTULC        | ) 2                                                | 17 |

| VERIFICAC       | TIÓN DE CIRCUITOS                                  | 17 |

| 2.1 In          | troducción                                         | 17 |

| 2.2 Ve          | erificación de Circuitos                           | 18 |

| 2.2.1           | Verificación formal                                | 19 |

| 2.3 Ge          | eneración de patrones de verificación y/o test     | 21 |

| 2.3.1           | Fundamentos para la Generación de Patrones de Test | 22 |

| 2.3.2           | Modelos de fallos                                  | 23 |

| 2.3.3           | Métodos algorítmicos                               | 24 |

| 2.4 Co          | obertura de fallos                                 | 25 |

| 2.5 Co          | onclusiones                                        | 26 |

| CAPÍTUL  | 03                                              | 29 |

|----------|-------------------------------------------------|----|

| SATISFAC | IBILIDAD (SAT)                                  | 29 |

| 3.1 I    | ntroducción                                     | 29 |

| 3.2 S    | atisfacibilidad Booleana (SAT)                  | 30 |

| 3.3 F    | ormato de descripción para SAT: CNF             | 32 |

| 3.3.1    | Ejemplo CNF                                     | 34 |

| 3.3.2    | Formato de archivo DIMACS para CNF              | 34 |

| 3.3.3    | Propiedades deseables de las codificaciones CNF | 36 |

| 3.4 P    | rogramación Lineal Entera Mixta (MILP)          | 37 |

| 3.4.1    | Reglas de sintaxis del formato de archivo LP    | 38 |

| 3.5 L    | P-solver CPLEX®                                 | 44 |

| 3.6 C    | Conclusiones                                    | 45 |

| CAPÍTUL  | O 4                                             | 47 |

| MÉTODO . | DESARROLLADO                                    | 47 |

| 4.1 I    | ntroducción                                     | 47 |

| 4.2 E    | Intorno de verificación                         | 48 |

| 4.3 F    | ormato de entrada de Circuitos de Referencia    | 57 |

| 4.4 N    | Modelado de Lógica Booleana mediante MILP       | 57 |

| 4.4.1    | Puerta OR                                       | 58 |

| 4.4.2    | Puerta AND                                      | 59 |

| 4.4.3    | Puerta NOT                                      | 61 |

| 4.4.4    | Puerta NOR                                      | 62 |

| 4.4.5    | Puerta NAND                                     | 63 |

| 4.5      | Conversión del problema SAT de CNF a MILP       | 65 |

| 4.5.1    | Cláusulas CNF                                   | 66 |

| 4.5.2    | AND lógico                                      | 66 |

| 4.5.3    | Codificador de CNF a MILP                       | 67 |

| 4.5.4    | Función para generar OR                         | 70 |

| 4.5.5    | Fijar entradas y/o salidas en CNF               | 71 |

| 4.6      | Conclusiones                                    | 72 |

| CAPÍTUL  | 05                                              | 73 |

| RESULTA  | DOS EXPERIMENTALES                              | 73 |

| 5.1 I    | ntroducción                                     | 73 |

| 5.2     | Descripción de los experimentos                | 74  |

|---------|------------------------------------------------|-----|

| 5.3     | Circuitos empleados                            | 77  |

| 5.4     | Resultados                                     | 77  |

| 5.5     | Conclusiones                                   | 86  |

| CAPÍT   | ULO 6                                          | 89  |

| CONCL   | USIONES Y LÍNEAS FUTURAS                       | 89  |

| 6.1     | Introducción                                   | 89  |

| 6.2     | Adecuación a los objetivos                     | 90  |

| 6.3     | Conclusiones                                   | 90  |

| 6.4     | Líneas futuras                                 | 93  |

| Bibliog | grafía                                         | 95  |

| PRESU   | JPUESTO                                        | 99  |

| P.1. I  | Introducción                                   | 101 |

| P.2.    | Costes de recursos humanos                     | 101 |

| P.3.    | Costes de recursos hardware                    | 103 |

| P.4.    | Costes de recursos software                    | 104 |

| P.5.    | Costes de material fungible y gastos generales | 104 |

| P.6.    | Costes de redacción                            | 105 |

| P.7.    | Coste del visado                               | 105 |

| P.8.    | Presupuesto total del proyecto                 | 106 |

| PLIEG   | O DE CONDICIONES                               | 107 |

| PC.1    | . Introducción                                 | 109 |

| PC.2    | . Recursos hardware                            | 109 |

| PC.3    | . Recursos software                            | 109 |

| PC.4    | . Circuitos de Referencia                      | 110 |

| ANEX    | O I:                                           | 111 |

| CÓDIO   | GOS                                            | 111 |

| AI.1.   | Código C cnf2lp.c                              | 113 |

| AI.2.   | . Código C Fix_IO_CNF.c                        | 119 |

| ANEX    | O II:                                          | 125 |

| BANC    | O DE PRUEBAS                                   | 125 |

| AII.1   | . Circuitos Benchmarks en formato BLIF         | 127 |

| ۸ ۱۱ ۵  | Circuitos Ronchmarks on formato CNE            |     |

# ÍNDICE DE FIGURAS

| FIGURA 1: FLUJO DE DISEÑO DE UN CIRCUITO INTEGRADO[6]                        | 11 |

|------------------------------------------------------------------------------|----|

| Figura 2: Chequeo de Equivalencia (EC)                                       | 20 |

| Figura 3: Expresión booleana                                                 | 33 |

| Figura 4: Codificación en formato CNF                                        | 34 |

| Figura 5: Línea de comentario en formato CNF                                 | 35 |

| Figura 6: Línea de problema en formato CNF                                   | 35 |

| Figura 7: Cláusula en formato CNF                                            | 35 |

| Figura 8: Problema de Programación Lineal                                    | 38 |

| Figura 9: Uso de espacios en LP                                              | 39 |

| FIGURA 10: USO DE FINAL DE LÍNEA EN LP                                       | 40 |

| FIGURA 11: RESTRICCIÓN CON NOMBRE EN LP                                      | 41 |

| Figura 12: Bounds en LP                                                      | 41 |

| Figura 13: Codificación LP                                                   | 43 |

| FIGURA 14: VARIABLES SEMI-CONTINUAS EN LP                                    | 43 |

| FIGURA 15: CONJUNTOS ESPECIALES ORDENADOS EN LP                              | 44 |

| Figura 16: Entorno de Verificación                                           | 48 |

| Figura 17: Circuito Booleano C17                                             | 49 |

| FIGURA 18: CODIFICACIÓN C17.BLIF                                             | 49 |

| Figura 19: Descripción C17 . cnf                                             | 50 |

| FIGURA 20: CIRCUITO DESCRITO EN C17. CNF                                     | 50 |

| Figura 21: Codificación MILP C17 . LP                                        | 52 |

| FIGURA 22: SOLUCIÓN DE C17. LP OBTENIDA CON CPLEX                            | 53 |

| FIGURA 23: CODIFICACIÓN MILP C17_0_100_1001 . LP                             | 55 |

| Figura 24: Solución de C17_0_100_1001. LP OBTENIDA CON CPLEX                 | 56 |

| FIGURA 25: ALGORITMO CNF2LP                                                  | 68 |

| Figura 26: Función genera_OR                                                 | 70 |

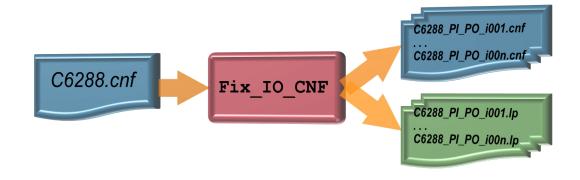

| FIGURA 27: ALGORITMO FIX_IO_CNF                                              | 71 |

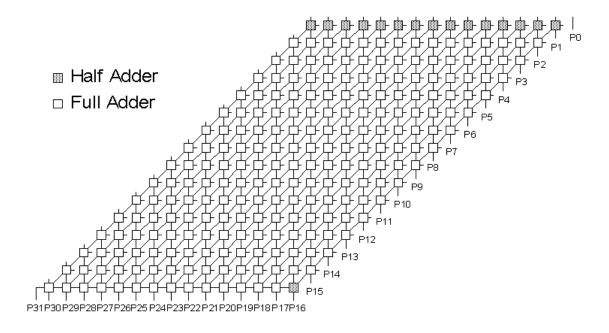

| FIGURA 28: MULTIPLICADOR 16x16 ISCAS-85 C6288                                | 74 |

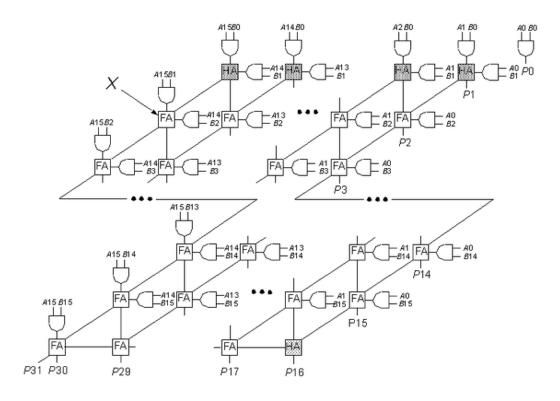

| FIGURA 29: CODIFICACIÓN DE C6288.BLIF A C6288.CNF                            | 74 |

| FIGURA 30: REPRESENTACIÓN ALTERNATIVA DEL MULTIPLICADOR 16x16 ISCAS-85 C6288 | 75 |

| FIGURA 31: CODIFICACIÓN DEL MULTIPLICADOR DE 16 BITS C6288. CNF              | 75 |

| FIGURA 32: CODIFICACIÓN DE C6288. CNF A C6288. LP                            | 76 |

| Figura 33: Resolución de C6288 . LP CON CPLEX                                | 76 |

| FIGURA 34: FIJAR ENTRADAS Y/O SALIDAS EN EL CIRCUITO C6288                   | 76 |

# ÍNDICE DE TABLAS

| Tabla 1: Generaciones de CIs                                               | 10  |

|----------------------------------------------------------------------------|-----|

| Tabla 2: Evolución temporal en el diseño de CIs [12]                       | 19  |

| Tabla 3: Combinaciones de entradas y salidas posibles para C17             | 54  |

| Tabla 4: Comprobación del modelado MILP de la puerta OR de dos entradas    | 58  |

| Tabla 5: Tabla de verdad de la puerta OR de dos entradas                   | 59  |

| Tabla 6: Comprobación del modelado MILP de la puerta AND de dos entradas   | 60  |

| Tabla 7: Tabla de verdad de la puerta AND de dos entradas                  | 61  |

| Tabla 8: Comprobación del modelado MILP de la puerta NOR de dos entradas   | 62  |

| Tabla 9: Tabla de verdad de la puerta NOR de dos entradas                  | 63  |

| Tabla 10: Comprobación del modelado MILP de la puerta NAND de dos entradas | 64  |

| Tabla 11: Tabla de verdad de la puerta NAND de dos entradas                | 65  |

| Tabla 12: Resolución de circuitos sin fijar entradas ni salidas            | 78  |

| Tabla 13: Resolución de circuitos con 10% de entradas fijadas              | 79  |

| Tabla 14: Resolución de circuitos con 30% de entradas fijadas              | 80  |

| Tabla 15: Resolución de circuitos con 50% de entradas fijadas              | 80  |

| Tabla 16: Resolución de circuitos con 70% de entradas fijadas              | 81  |

| Tabla 17: Resolución de circuitos con 90% de entradas fijadas              | 81  |

| Tabla 18: Resolución de circuitos con 100% de entradas fijadas             | 82  |

| Tabla 19: Resolución de circuitos con 10% de salidas fijadas               | 83  |

| Tabla 20: Resolución de circuitos con 30% de salidas fijadas               | 83  |

| Tabla 21: Resolución de circuitos con 50% de salidas fijadas               | 84  |

| Tabla 22: Resolución de circuitos con 70% de salidas fijadas               | 84  |

| Tabla 23: Resolución de circuitos con 90% de salidas fijadas               | 85  |

| Tabla 24: Resolución de circuitos con 100% de salidas fijadas              | 85  |

| Tabla 25: Factor de corrección según el número de horas trabajadas         | 102 |

| Tabla 26: Costes asociados a los recursos hardware                         | 103 |

| Tabla 27: Costes asociados a los recursos software                         | 104 |

| Tabla 28: Costes de material fungible y gastos generales                   | 104 |

| Tabla 29: Presupuesto total del proyecto                                   | 106 |

| Tabla 30: Relación de Benchmarks ISCAS'85                                  | 110 |

| Tabla 31: Relación de Benchmarks en formato BLIF                           | 127 |

| Tabla 32: Relación de Benchmarks en formato CNF                            | 129 |

# **MEMORIA**

### **RESUMEN**

Este Proyecto Fin de Carrera presenta una metodología para la generación de vectores de verificación basada en Programación Lineal Entera Mixta. La metodología propuesta da lugar a una herramienta que hace uso de diversos programas desarrollados, en lenguaje de programación C, a lo largo de este PFC y que se ejecutan a nivel de línea de comandos.

La herramienta desarrollada permite generar patrones para la verificación en la que se especifican, por ejemplo, el porcentaje de entradas y/o salidas que han de fijarse. Esta herramienta se ha evaluado mediante un banco de pruebas estándar ISCAS'85, empleado extensamente en la bibliografía.

Se han escogido de dicho banco de pruebas los circuitos combinacionales más representativos del estado del arte. La complejidad de los mismos va desde unas pocas puertas, C17 con 6 puertas, a circuitos de complejidad media con aproximadamente 3500 puertas como es el caso del C7552. En términos de entradas/salidas, la complejidad alcanza las 233 entradas para el C2670 ó 5 entradas para el C17 y desde las 2 salidas con que cuenta C17 hasta las 140 salidas para C2670.

Todas las pruebas realizadas demuestran la eficiencia de la metodología propuesta y la validez de la herramienta desarrollada. Los tiempos requeridos para obtener los vectores de verificación se encuentran siempre por debajo de 1,5 segundos en todas las pruebas realizadas en este PFC, salvo en contadas ocasiones que se corresponden con el circuito C7552 que requiere aproximadamente 33 segundos. Esa diferencia de tiempos es debida principalmente a la complejidad de interconexión de las puertas de dicho circuito de referencia.

Se puede concluir que el desarrollo de este PFC ha logrado satisfactoriamente los objetivos planteados inicialmente, sirviendo como punto de partida de una futura tesis doctoral en base a los resultados obtenidos.

#### **ABSTRACT**

This PFC presents a methodology for the generation of verification patterns using Mixed Integer Linear Programming. Based on proposed methodology, this PFC develops a verification tool made by several programs developed in C programming language. The verification tool is executed at the shell command line interface.

The developed tool allows to generate verification patterns which are specified for example with a percentage of inputs and/or outputs to be asserted. This verification tool has been evaluated using ISCAS'85 standard testbenches, widely used in the literature.

The most representative combinational circuits of the state of the art have been chosen from testbenches. Their complexity ranges from a few gates, C<sub>17</sub> with 6 gates, to medium complexity circuits with approximately 3500 gates as is the case of the C<sub>7552</sub>. In terms of inputs/outputs, the complexity reaches 233 inputs for the C<sub>2670</sub> or 5 inputs for the C<sub>17</sub> and from the 2 outputs with C<sub>17</sub> up to the 140 outputs for C<sub>2670</sub>.

All tests demonstrate the efficiency and usefulness of the proposed methodology and developed verification tool. The time required to obtain the verification patterns was always less than 1.5 seconds in all tests performed in this PFC. Only for circuit C7552, the required time to obtain the solution rises to approximately 33 seconds. This difference is mainly due to the complexity of its internal interconnection in this reference circuit.

It can be concluded that the development of this PFC has satisfactorily achieved the objectives set out initially, serving as a starting point for a future PhD. based on the obtained results.

### **A**CRÓNIMOS

Al Artificial Intelligence

ASCII American Standard Code for Information Interchange

BDD Binary Decision Diagram

BLIF Berkeley Logic Interchange Format

BMC Bounded Model Checking

CAD Computer-Aided Design

CI Circuito Integrado

CNF Conjunctive Normal Form

CTL Computational Tree Logic

DFT Design For Testability

DIMACS Center for Discrete Mathematics and Theoretical Computer Science

DUT Device Under Test

EC Equivalence Checking

EDA Electronic Design Automation

EITE Escuela de Ingeniería de Telecomunicación y Electrónica

IP Integer Programming

ISCAS International Symposium on Circuits And Systems

LP Linear Programming

LSI Large Scale integration

MBTG Model Based Test Generation

MC Model Checking

MCNC Microelectronics Center of North Carolina

MILP Mixed Integer Linear Programming

MIP Mixed Integer Programming

MIQP Mixed Integer Quadratic Programming

MSI Medium Scale integration

PC Property Checking

PFC Proyecto Fin de Carrera

PLA Programmable Logic Array

Prolog PROgrammation en LOGique

QCP Quadratically Constrained Programming

RTPG Random Test Pattern Generation

SAT Satisfiability

SoC System on Chip

SSI Small Scale integration

TPG Test Pattern Generation

ULPGC Universidad de Las Palmas de Gran Canaria

ULSI Ultra Large Scale Integration

Verilog VERIfication LOGic

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

# CAPÍTULO 1 INTRODUCCIÓN Y ANTECEDENTES

#### 1.1 Introducción

En el Diseño Electrónico, comprobar las funcionalidades implementadas es primordial [1]. Es bien conocido que un fallo de diseño a nivel de puerta, bloque, módulo, interfaz, subsistema o sistema puede ocasionar cuantiosas pérdidas económicas. En el mejor de los casos y en las etapas tempranas del diseño, la detección de un error implica un retraso de tiempo y una recodificación parcial del código bajo comprobación. En el peor de los casos, estos fallos pueden ocasionar un retraso considerable o incluso la cancelación del proyecto [2].

Por otro lado, se define el time-to-market como aquel periodo de tiempo que marca el momento idóneo para introducir un producto en el mercado. Si el producto se introduce con demasiada antelación a un time-to-market lo más probable es que dicho producto genere bajas ventas pues el mercado no está preparado. Cuando se da el caso contrario, es decir, el producto se introduce

posteriormente a su time-to-market, probablemente la competencia tenga acaparada gran parte de la cuota de mercado lo que implicaría nuevamente un bajo número de ventas.

Si se une la necesidad de cumplir el time-to-market al incremento de la complejidad de las funcionalidades incluidas en los circuitos integrados actuales [3][4], el desarrollo de un nuevo producto conlleva grandes riesgos que hay que minimizar. A modo de resumen, teniendo en cuenta las presiones temporales, pues los proyectos se acotan en el tiempo, y el volumen de funcionalidades más su complejidad, es necesario por lo general dedicar a verificación un 70% del esfuerzo total empleado en el desarrollo del producto.

Como puede verse en la Tabla 1, los sistemas digitales cada vez contienen un mayor número de elementos lógicos [5], por lo que resulta muy complejo probar todos y cada uno de los estados lógicos posibles y en algunos casos es prácticamente imposible, ya que los tiempos requeridos para realizar ese tipo de simulaciones y verificar el correcto funcionamiento del circuito se disparan exponencialmente. Por ello, se ha optado por aplicar la verificación funcional, que se basa en la cobertura de los puntos más significativos o de mayor interés en el diseño de un sistema digital, con los cuales se puede garantizar la correcta funcionalidad de todo el sistema.

| Escala de Integración | Año  | Nº Transistores    | Nº Puertas Lógicas |

|-----------------------|------|--------------------|--------------------|

| SSI                   | 1964 | 1 a 10             | 1 a 12             |

| MSI                   | 1968 | 10 a 500           | 13 a 99            |

| LSI                   | 1971 | 500 a 20.000       | 100 a 9.999        |

| VLSI                  | 1980 | 20.000 a 1.000.000 | 10.000 a 99.999    |

| ULSI                  | 1984 | 1.000.000 y más    | 100.000 y más      |

Tabla 1: Generaciones de CIs

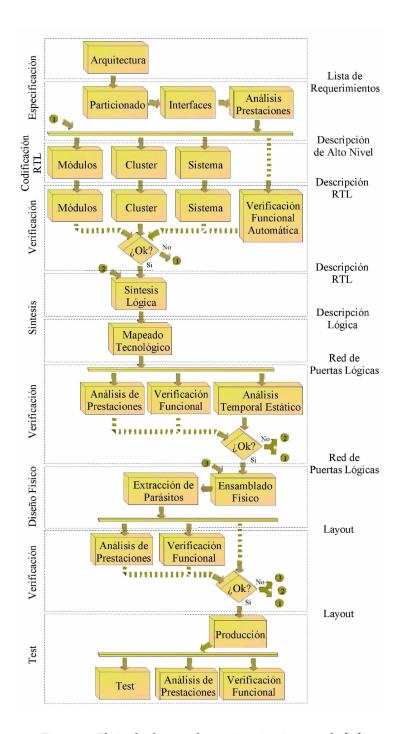

La verificación de un circuito integrado no se limita a un simple paso dentro del flujo de diseño. Puesto que en todos los pasos del flujo de diseño de un circuito integrado puede surgir un fallo, se ha de ejecutar un proceso de comprobación (verificación) tras cada paso en el que evolucione el diseño (Figura 1).

Figura 1: Flujo de diseño de un circuito integrado [6]

A partir de un conjunto de especificaciones en las que se detallan las características del circuito integrado a desarrollar, la verificación del mismo ha de plantear los distintos casos a comprobar en todos los niveles. Estos casos se denominan esquinas críticas (corner cases) [7]. A medida que el desarrollo avanza, su complejidad se ve incrementada. Del estudio de la literatura al respecto, se deduce que la complejidad de los casos críticos definidos en la verificación aumenta

en relación a la complejidad de la etapa del diseño. Además, esta complejidad es abordada introduciendo diversas capas de abstracción.

#### 1.2 ANTECEDENTES

Existen múltiples aportaciones en el estado del arte en el área de verificación en todos los niveles del flujo de diseño. Por ejemplo, destacan la generación de vectores, las métricas de cobertura y los modelos para acelerar el proceso de verificación.

En particular, un área muy estudiada es la generación de vectores. Conocida una funcionalidad, es muy sencillo generar estímulos de entrada a ese circuito y obtener su respuesta en las salidas. Lo complicado es el número mínimo de esos patrones de entrada/salida para asegurar un máximo de comprobación en el menor tiempo. Este problema es hoy día el paradigma de la verificación, es decir, la generación de vectores de máxima cobertura.

A nivel de módulo o incluso bloque, el incremento del número de puertas complica la generación de esos vectores de máxima cobertura. La literatura aborda este problema mediante la definición del llamado problema de satisfacibilidad (satisfiability) o comúnmente llamado SAT. Se define un SAT como el problema de determinar si el comportamiento implementado en un circuito conocido permite fijar unas entradas determinadas y que su respuesta en las salidas sean unos valores conocidos.

Por otro lado, los problemas SAT han sido ampliamente estudiados en el terreno matemático. La descripción del problema SAT se hace mediante ecuaciones algebraicas que modelan las puertas, la definición de las entradas fijadas y las salidas esperadas [8]. Los métodos matemáticos más recurridos en la literatura comprenden, por ejemplo, Programación Lineal Entera Mixta (MILP), Programación Cuadrática Entera Mixta (MIQP) [9] o Prolog [10].

#### 1.3 OBJETIVOS

Este Proyecto Fin de Carrera plantea la creación de herramientas que faciliten la generación de patrones de verificación de máxima cobertura para circuitos booleanos empleando MILP.

El objetivo principal es crear un entorno de desarrollo para la generación de patrones de verificación. Este entorno se ejecutará a nivel de línea de comandos y se desarrollará completamente en C. Su ejecución está prevista para máquinas Linux o Unix.

Como objetivos secundarios, pero no menos importantes, se plantea que se haga uso de un formato de entrada estándar. El empleo de un formato estándar permitirá utilizar esta herramienta con los diversos lenguajes de descripción hardware que se emplean en la literatura como, por ejemplo, VHDL, Verilog, BLIF y PLA, entre otros. Igualmente, en base a la literatura, se ha de establecer el banco de circuitos de prueba para comprobar las prestaciones del entorno.

También se han de desarrollar los modelos de puerta Booleana que permitan traducir el modelo circuital (netlist) a un modelo basado en MILP.

#### 1.4 Peticionario

Actúa como peticionario de este Proyecto de Fin de Carrera la Escuela de Ingeniería de Telecomunicación y Electrónica (EITE), de la Universidad de Las Palmas de Gran Canaria (ULPGC), siendo la realización de este proyecto requisito para la obtención del título de Ingeniero en Electrónica.

#### 1.5 ORGANIZACIÓN DEL DOCUMENTO

Este Proyecto Fin de Carrera está estructurado en cuatro bloques: Memoria, Presupuesto, Pliego de Condiciones y Anexos. Además, se adjunta un CD con la información contenida en el presente documento.

#### **1.5.1 MEMORIA**

La Memoria de este Proyecto Fin de Carrera está estructurada en 6 capítulos y la bibliografía.

- Capítulo 1: Introducción y antecedentes. En el capítulo introductorio de la memoria se detallan los antecedentes, así como los objetivos del proyecto, su peticionario y la estructura del documento.

- Capítulo 2: Verificación de circuitos. Se describen diferentes técnicas para la verificación de circuitos, centrándose en las relativas a la verificación de circuitos booleanos.

- Capítulo 3: Satisfacibilidad. Se explican los fundamentos de satisfacibilidad sobre los que se sustenta el trabajo, así como los formatos usados como entrada para los SAT-solvers.

- Capítulo 4: Método desarrollado. Se describe la organización del sistema diseñado, detallando las distintas partes desarrolladas.

- **Capítulo 5: Resultados experimentales**. Se expone la experimentación realizada con el banco de pruebas.

- Capítulo 6: Conclusiones y líneas futuras. Finalmente, se detallan las conclusiones obtenidas durante el desarrollo del proyecto y se presentan algunas líneas de trabajo que pueden derivarse de su realización.

- **Bibliografía.** En la bibliografía se detallan las referencias empleadas para la realización y la redacción del presente proyecto.

#### 1.5.2 Presupuesto

En el presupuesto se cuantifican los costes del desarrollo del presente Proyecto Fin de Carrera.

#### 1.5.3 PLIEGO DE CONDICIONES

En este apartado se detallan las condiciones bajo las cuales se han desarrollado las diferentes etapas del presente Proyecto Fin de Carrera.

#### 1.5.4 ANEXO I: CÓDIGOS

Se muestra el código en lenguaje C de los programas que han sido desarrollados en este proyecto.

#### 1.5.5 ANEXO II: BANCO DE PRUEBAS

Se hace una relación de los circuitos de referencia obtenidos con este PFC.

# CAPÍTULO 2 VERIFICACIÓN DE CIRCUITOS

#### 2.1 Introducción

Como se ha mencionado previamente, este PFC se centra en el desarrollo de herramientas para la generación de patrones de verificación y test de circuitos booleanos. Con el fin de abordar de forma confiable la temática de este PFC, antes de proseguir detallando en profundidad el desarrollo del mismo, se hace imprescindible la lectura de este capítulo que versa sobre el estudio del arte.

En primer lugar, y de forma simplificada, se exponen las diversas metodologías empleadas en la verificación/test de circuitos, aportando las razones por las que se deba emplear una u otra técnica y haciendo especial hincapié en aquellos métodos de verificación en que se encuadran los trabajos del presente PFC.

Por otro lado, se explican las principales técnicas de generación de vectores de verificación/test, detallando los conceptos de modelos de fallos, métodos algorítmicos y cobertura de fallos.

#### 2.2 VERIFICACIÓN DE CIRCUITOS

En la actualidad, dado que los circuitos pueden contener varios cientos de millones de transistores, la verificación de los diseños actuales se hace cada vez más difícil. Además, se ha observado que la verificación se convierte en el principal cuello de botella en los flujos de diseño, de forma que hasta el 80% de los costes globales de diseño se deben a la verificación (Tabla 2). Esta es una de las razones por las que en los últimos años se han propuesto infinidad de métodos/técnicas como alternativas y/o complementos a la simulación clásica [11].

Se define el concepto de cobertura de verificación/test de un diseño como el grado de seguridad sobre el correcto funcionamiento de un diseño. Si se tiene en cuenta el constante incremento de funcionalidades en las nuevas generaciones de circuitos integrados, el número de estas crece de forma exponencial. Por ello, asegurar el correcto funcionamiento de las mismas mediante simulación clásica se torna una tarea cuanto menos ardua, si no imposible, en términos de tiempos de ejecución razonables.

Entendiendo que es imposible alcanzar el cien por cien de confianza en la cobertura de verificación/test, es ahí donde entran en juego esas técnicas que permiten reducir el universo de simulaciones a un conjunto finito y bien definido que permita alcanzar un grado de confianza/cobertura aceptable.

Una primera metodología sencilla como aproximación aceptable consiste en la creación de un Testplan o el llamado Plan de Verificación/Test. Este es un documento en el que se detallan cada una de las funcionalidades a comprobar y el conjunto de pruebas que se han de realizar. Adicionalmente, este documento tendría que indicar el nivel de prioridad de dicha prueba. Las pruebas o casos críticos se han de priorizar en varios niveles (por ejemplo: críticos, medio y bajo) en los que se explicitaría qué casos han de comprobarse de forma ineludible, cuales son

opcionales y cuales prescindibles. Este documento ha de presentar una estimación del tiempo requerido para la ejecución de cada uno de los casos así como el grado de confianza alcanzado.

La comprobación de cada uno de esos casos conlleva la ineludible tarea de generación de los estímulos de entrada así como la obtención de las respuestas a obtener por parte del diseño. Si se realiza una comprobación basada en simulación, dichos estímulos de entrada y respuesta en las salidas se traducen en un conjunto de patrones de verificación (vectores de datos booleanos) en sus entradas y salidas, respectivamente.

La simulación de casos críticos, por sí sola no puede garantizar una cobertura suficiente del diseño, lo que conduce a errores que pueden permanecer sin ser detectados. La correcta generación de esos vectores de verificación/test son la clave de su correcta consecución.

Puesto que la simulación no puede garantizar el comportamiento correcto, y la simulación exhaustiva es a menudo imposible, como alternativa se han propuesto técnicas de verificación formal. En lugar de simular un diseño, la comprobación del mismo es probada por técnicas formales. Hay muchas áreas diferentes donde estos enfoques se pueden utilizar, como la comprobación de equivalencia, la comprobación de propiedades o la simulación simbólica. Estos métodos se han aplicado con éxito en muchos proyectos industriales y se han convertido en la técnica más avanzada en varios campos.

|                        | 1970 | 1975 | 1980  | 1985    | 1990   | 1995 | 2000  |

|------------------------|------|------|-------|---------|--------|------|-------|

| Complejidad            | SSI  | MSI  | LSI   | VLSI    | ULSI   |      | SoC   |

| Transistores           | 100  | 1K   | 10K   | 100K    | 1M     | 10M  | 100M  |

| Memorias               | 256  | 1K   | 4-16K | 64-256K | 1-16M  | 64M  | 1-16G |

| Velocidad              |      | 1MHz | 10MHz | 30MHz   | 100MHz | 1GHz | 10GHz |

| Terminales             |      | 32   | 64    | 128     | 256    | 512  | 1024  |

| Coste test/Coste total | 5%   | 10%  | 20%   | 40%     | 60%    | 70%  | 80%   |

Tabla 2: Evolución temporal en el diseño de CIs [12]

#### 2.2.1 VERIFICACIÓN FORMAL

La idea principal de la verificación formal de un diseño es probar su funcionalidad sin recurrir a simulación. Para el proceso de comprobación se han

propuesto diferentes técnicas. La mayoría de ellos trabajan en el dominio booleano, como diagramas binarios de decisión (BDDs) o solucionadores SAT (SAT-solvers). Los escenarios típicos de verificación de hardware, en los que se aplican técnicas de verificación formal, son el chequeo de equivalencia (EC) y la verificación de propiedades (PC), también llamada verificación de modelos (MC).

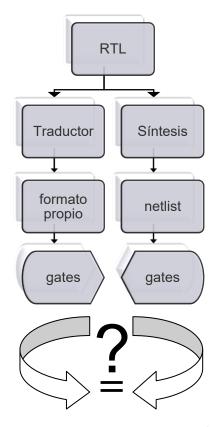

El objetivo de EC es asegurar la equivalencia de dos descripciones de circuitos. Estos circuitos pueden darse en diferentes niveles de abstracción, es decir, nivel de transferencia de registro o nivel de puerta. Las etapas principales de un chequeador de equivalencia son las siguientes (Figura 2) [13]:

- 1. Traducir ambos diseños a un formato propio.

- 2. Establecer la correspondencia entre los dos diseños en una fase de coincidencia.

- 3. Probar equivalencia o inequivalencia.

- 4. En caso de una inequivalencia se genera una incidencia y comienza la fase de depuración.

Figura 2: Chequeo de Equivalencia (EC)

El circuito se considera puramente combinacional al modelar los elementos de estado como entradas y salidas primarias adicionales. Este modelado puede dar lugar a casos que no son accesibles durante el funcionamiento normal del circuito.

A diferencia de EC, donde se consideran dos circuitos, para PC se da un solo circuito y las propiedades se formulan en un "lenguaje de verificación" específico. Se demuestra entonces formalmente si estas propiedades se mantienen en todas las circunstancias. Mientras que la verificación de modelos "clásicos" basada en CTL (Computational Tree Logic) sólo puede aplicarse a diseños de tamaño mediano, los enfoques basados en BMC (Bounded Model Checking), como se describe en [14], dan muy buenos resultados cuando se usan para bloques completos con hasta 100k puertas.

Sin embargo, todos estos enfoques pueden tener problemas causados por la complejidad, esto es, si el circuito se hace demasiado grande o si la función representada resulta ser compleja para los métodos formales. El segundo problema surge a menudo en casos de aritmética compleja, como multiplicadores.

Estos problemas han conducido a la propuesta de métodos híbridos, como por ejemplo, simulación simbólica y verificación de aserción. Estos métodos intentan salvar la brecha entre la simulación y las pruebas de corrección, pero también hacen uso de técnicas de verificación formal.

#### 2.3 GENERACIÓN DE PATRONES DE VERIFICACIÓN Y/O TEST

Aunque BDDs y SAT son las técnicas más populares en la verificación hardware, y se han aplicado a muchos dominios, todavía hay gran cantidad de investigación en curso. Además de los enfoques monolíticos clásicos, las herramientas modernas de EC utilizan enfoques múltiples que combinan diferentes técnicas, como: SAT, BDD, reescritura de términos, generación de patrones de test y simulación con patrones de test aleatorios.

La Generación de Patrones de Test (TPG) es un método de automatización de diseño electrónico utilizado para encontrar una secuencia de entrada (o test) que, cuando se aplica a un circuito digital, permita que el equipo de prueba distinga

entre el comportamiento correcto del circuito y el comportamiento defectuoso causado por defectos.

Los primeros patrones de test consistían en un archivo formado por vectores binarios escritos manualmente. Posteriormente, se desarrollaron generadores de vectores de test, como los generadores de pruebas aleatorias (RTPG), los generadores de test basados en modelos (MBTG), llegando a los actuales generadores de patrones de test aleatorios con restricciones mediante el uso de solucionadores de restricciones.

Los patrones generados se usan para probar dispositivos semiconductores después de la fabricación, o para ayudar a determinar la causa del fallo (análisis de fallos). La eficacia de la TPG se mide por el número de defectos modelados, o modelos de fallo, detectables y por el número de patrones generados. Estas métricas generalmente indican la calidad de la prueba (mayor con más detecciones de fallos) y el tiempo de aplicación del test (mayor con más patrones). La eficiencia de la TPG es otra consideración importante que está influenciada por el modelo de fallo considerado, el tipo de circuito bajo test, el nivel de abstracción utilizado para representar el circuito bajo prueba y la calidad requerida del test.

#### 2.3.1 FUNDAMENTOS PARA LA GENERACIÓN DE PATRONES DE TEST

Un defecto es un error causado en un dispositivo durante el proceso de fabricación. Un modelo de fallo es una descripción matemática de cómo un defecto altera el comportamiento del diseño. Los valores lógicos observados en las salidas primarias del dispositivo, al aplicar un patrón de prueba a algún dispositivo bajo prueba (DUT), se denominan salida de ese patrón de prueba. La salida de un patrón de test, cuando se prueba un dispositivo sin fallos que funcione exactamente como se diseñó, se denomina salida esperada de ese patrón de prueba. Un fallo se dice que es detectado por un patrón de prueba si la salida de ese patrón de test, cuando se prueba un dispositivo que tiene solo un fallo, es diferente de la salida esperada. El proceso TPG para un fallo selectivo consta de dos fases: activación de fallos y propagación de fallos. La activación de fallos establece un valor de señal en el sitio del modelo de fallos que es opuesto al valor producido por el modelo de fallo. La

propagación de fallos mueve el valor de señal resultante o el efecto del fallo hacia adelante, sensibilizando un camino desde el sitio del fallo a una salida primaria.

La TPG no puede encontrar una prueba para un fallo en al menos dos casos. En primer lugar, el fallo puede ser intrínsecamente indetectable, de tal manera que no existen patrones que puedan detectar ese fallo en particular. El ejemplo clásico de esto es un circuito redundante, diseñado de tal manera que ningún fallo único hace que la salida cambie. En tal circuito, cualquier fallo único será intrínsecamente indetectable.

En segundo lugar, es posible que exista un patrón de detección, pero el algoritmo no puede encontrar uno. Puesto que el problema de la TPG es NP-completo (por reducción del problema de satisfacibilidad booleano) habrá casos donde existen patrones, pero la TPG abandona, ya que tardaría demasiado tiempo en encontrarlos.

#### 2.3.2 MODELOS DE FALLOS

Un modelo de fallo es un modelo matemático de algo que podría ir mal en la construcción u operación del DUT. A partir del modelo, el diseñador o usuario puede predecir las consecuencias de este fallo en particular. Los modelos de fallo pueden usarse en casi todas las ramas de la ingeniería.

Puede hacerse la suposición de fallo único, es decir, que solo se produce un fallo en el circuito. Si se definen k posibles tipos de fallos en el modelo de fallos y el circuito tiene n líneas de señal, por suposición de fallo único, el número total de fallos únicos es  $k \times n$ . O puede hacerse la asunción de múltiples de fallos, esto es que se contempla la posibilidad de que puedan ocurrir varios fallos en el circuito.

La magnitud del problema de la verificación hace necesaria la utilización de modelos de fallos que permitan determinar con precisión los fallos posibles y contar su número, encontrar vectores de test para cada fallo, conocer qué fallos detecta cada vector de test y calcular la cobertura de fallos, es decir, el conjunto de fallos que pueden ser detectados por un conjunto dado de vectores de test.

#### 2.3.2.1 Colapso de fallos equivalentes

Los fallos equivalentes producen el mismo comportamiento defectuoso para todos los patrones de entrada. Cualquier fallo del conjunto de fallos equivalentes puede representar el conjunto completo. En este caso, se requieren pruebas de fallos mucho menores que  $k \times n$  para un circuito con n líneas de señal. Eliminar fallos equivalentes de un conjunto completo de fallos se denomina colapso de fallos.

#### 2.3.2.2 Modelo de fallos por bloqueo Stuck-at

Es el modelo de fallos más utilizado en las últimas décadas. En este modelo, se supone que una de las líneas de señal de un circuito está atascada a un valor lógico fijo, independientemente de las entradas que se suministran al circuito. Por lo tanto, si un circuito tiene n líneas de señal, existen potencialmente 2n atascos definidos en el circuito, algunos de los cuales pueden ser vistos como equivalentes a otros. El modelo de fallos stuck-at es un modelo de error lógico porque no hay información de retardo asociado con la definición del fallo. También se denomina modelo de fallo permanente, porque se supone que el defecto es permanente, en contraste con los fallos intermitentes, que pueden ocurrir esporádicamente de forma aleatoria y transitoria, dependiendo de las condiciones de funcionamiento (por ejemplo, temperatura, tensión de alimentación) o en los valores de datos (estados de alta o baja tensión) en las líneas de señal circundantes. El modelo stuckat es estructural porque se define a partir de un modelo de circuito estructural a nivel de puerta.

Un conjunto de patrones con 100% de cobertura del modelo de fallos stuck-at consiste en pruebas para detectar todos los fallos posibles en un circuito.

#### 2.3.3 MÉTODOS ALGORÍTMICOS

La prueba de circuitos integrados VLSI (Very Large Scale Integration) con una alta cobertura de fallos es una tarea difícil debido a la complejidad de los mismos. Por lo tanto, se han desarrollado muchos métodos TPG diferentes para abordar circuitos combinacionales y secuenciales.

Los primeros algoritmos de generación de test, tales como la diferencia booleana y la proposición literal, no eran prácticos para implementar en una computadora.

El Algoritmo D fue el primer algoritmo de generación de test práctico en términos de requerimientos de memoria. Fue propuesto por Roth en 1966 e introdujo la Notación D que sigue siendo utilizada en la mayoría de los algoritmos TPG. Este algoritmo intenta propagar el valor de fallo stuck-at a una salida primaria.

La toma de decisiones orientada por el camino (PODEM) es una mejora sobre el Algoritmo D. PODEM fue creado en 1981 por Prabhu Goel, cuando se evidenciaron las limitaciones del Algoritmo D que no podía con los circuitos que surgieron por las innovaciones del diseño.

El Algoritmo FAN, orientado por Fan-Out, es una mejora sobre PODEM. Limita el espacio de búsqueda TPG para reducir el tiempo de cálculo y acelera el proceso.

También se usan métodos basados en la satisfacibilidad booleana para generar vectores de prueba.

La generación de test Pseudoaleatorios es el método más simple de crear tests. Utiliza un generador de números pseudoaleatorios para generar vectores de test y se basa en la simulación lógica, para conseguir buenos resultados de funcionamiento, y simulación de fallos, para calcular la cobertura de fallos de los vectores generados.

#### 2.4 COBERTURA DE FALLOS

La cobertura de fallos se refiere al porcentaje de algún tipo de fallo que se puede detectar durante el test. Una alta cobertura de fallos es particularmente valiosa durante la prueba de fabricación, y técnicas tales como diseño para test (DFT) y la generación automática de patrones de test se utilizan para aumentarla.

En la electrónica se mide la cobertura de fallos stuck-at fijando cada pin del modelo hardware a '0' lógico y a '1' lógico, respectivamente, y ejecutando los

vectores de test. Si al menos una de las salidas difiere de lo que se espera, se dice que se detecta el fallo. Conceptualmente, el número total de ciclos de simulación es el doble del número de pines, ya que cada pin es fijado de las dos maneras, y ambos fallos deben ser detectados. Sin embargo, hay muchas optimizaciones que pueden reducir el cálculo necesario. En particular, a menudo muchos fallos que no interactúan pueden ser simulados en una ejecución y cada simulación puede ser terminada tan pronto como se detecta un fallo.

Un test con una determinada cobertura de fallos se alcanza cuando se puede detectar por lo menos un porcentaje especificado de todos los fallos posibles. Si no se consigue, existen al menos tres opciones. En primer lugar, el diseñador puede aumentar o mejorar el conjunto de vectores, tal vez utilizando una herramienta de generación de patrones de prueba automática más eficaz. En segundo lugar, el circuito puede ser redefinido para una mejor detección de fallos (mejor controlabilidad y observabilidad). En tercer lugar, el diseñador puede simplemente aceptar la menor cobertura.

#### 2.5 CONCLUSIONES

Uno de los principales desafíos en la línea de producción de circuitos integrados es el uso de procedimientos adecuados y prácticos para probar circuitos en diferentes etapas del proceso de fabricación para mejorar el rendimiento y la fiabilidad de los productos finales. Con los recientes avances en las tecnologías de semiconductores y el aumento continuo de la densidad de circuitos de los chips VLSI, el costo de las pruebas aumenta rápidamente. La prueba de circuitos digitales es el proceso de aplicar algunos vectores de prueba a las entradas del circuito y observar las salidas. El tamaño del conjunto de pruebas afecta el coste total de las pruebas del circuito.

Este análisis se utiliza con el objetivo de generar nuevos vectores de prueba altamente eficaces. La relación entre los fallos focalizados y el total de fallos posibles tiene efecto en la mejora de la cobertura de fallos.

Por último y a modo de reflexión, mientras la verificación de circuitos se refiere al conjunto de tareas encaminadas a comprobar un diseño desde un punto de vista puramente funcional y el test se centra en chequear defectos físicos, ambos procesos del ciclo de diseño se encuentran íntimamente interrelacionados. Por ejemplo, gran parte de las pruebas a las que se somete el diseño en su verificación son reutilizadas en el test. Esta dualidad de ciertas metodologías/técnicas de verificación/test hace que, por ejemplo, la inmensa mayoría de los generadores de patrones de verificación/test sean aplicados en ambos ámbitos.

En particular, los generadores de patrones propuestos en este PFC son aplicables tanto a la verificación como al test de circuitos digitales booleanos.

# CAPÍTULO 3 SATISFACIBILIDAD (SAT)

### 3.1 Introducción

La satisfacibilidad (SAT) es un problema clásico tanto en el área de las matemáticas como en la ingeniería. Hoy día se resuelven muchos problemas cotidianos mediante SAT-solvers. La complejidad de los nuevos problemas, que surgen a diario en este ámbito, requieren de mayores recursos computacionales que a su vez crea nuevos retos en la obtención de la solución a dichos problemas de forma eficiente y más veloz en términos de memoria requerida y esfuerzo computacional.

Su aplicabilidad se debe probablemente a que la SAT se encuentra en el cruce de la lógica, la teoría de grafos, la informática, la ingeniería informática y la investigación operativa. Por lo tanto, muchos problemas originados en uno de estos campos suelen tener múltiples traducciones a SAT y existen muchas herramientas

matemáticas disponibles para que el SAT-solver pueda conseguir soluciones con un rendimiento mejorado.

En este capítulo se introducen conceptos teóricos sobre la satisfacibilidad, resaltando los aspectos aplicables al modelado y posterior resolución de circuitos booleanos. También se describen los formatos que van a ser usados para el modelado, con la finalidad de emplear SAT-solvers para obtener los vectores de verificación de los circuitos. Para tener éxito en esto, deben ser introducidas las ideas que han surgido durante los numerosos intentos de razonar con la lógica, requiriendo una terminología y una perspectiva que se ha desarrollado en los últimos dos milenios.

Por último, también se describe la metodología y usos de la programación lineal entera mixta (MILP), así como el formato de descripción que utiliza.

# 3.2 SATISFACIBILIDAD BOOLEANA (SAT)

La lógica proposicional ha sido reconocida a lo largo de los siglos como una de las piedras angulares del razonamiento en filosofía y matemáticas. A lo largo de la historia, su formalización en álgebra booleana fue acompañada gradualmente por el reconocimiento de que una amplia gama de problemas combinatorios puede expresarse como problemas de satisfacibilidad proposicional (SAT). Debido a estas dos funciones, SAT se ha convertido en una disciplina científica madura con múltiples facetas. Iniciado por el trabajo de Cook [15], que estableció su estatus NP-completo en 1971, SAT se ha convertido en un problema de referencia para una enorme variedad de especificaciones de gran complejidad.

Simultáneamente, muchos problemas del mundo real se formalizaron como problemas de decisión SAT utilizando diferentes técnicas de codificación. Esto incluye problemas de verificación en software y hardware, planificación, programación y diseño combinatorio.

Debido a las implicaciones prácticas potenciales, desde los comienzos de la informática ha estado en marcha una búsqueda intensiva de cómo se podrían resolver los problemas SAT de manera automatizada. En 1957, Allen Newell y Herb

Simon introdujeron uno de los primeros programas de inteligencia artificial (AI), la Máquina de Lógica Teórica [16], para probar los teoremas proposicionales del "Principia Mathematica" de Whitehead y Russell. Poco después, en 1960, Martin Davis y Hillary Putnam introdujeron su ahora famoso procedimiento de decisión para problemas de satisfacibilidad proposicional [17]. En 1962 siguieron Martin Davis, George Logemann y Donald Loveland con una versión más eficiente del espacio [18].

El problema de satisfacibilidad booleana consiste en determinar si existe una asignación de variables satisfactoria para una función booleana, o determinar que no existe esta posibilidad. SAT tiene muchas aplicaciones directas en el campo de la automatización del diseño electrónico (EDA), incluyendo la generación de patrones de prueba, análisis de tiempos, verificación de lógica, pruebas funcionales, etc. SAT pertenece a la clase de problemas NP-completos, con soluciones algorítmicas que pueden tener una complejidad exponencial en el peor de los casos. Este problema ha sido y sigue siendo un área importante de investigación porque las técnicas eficientes de SAT pueden tener un gran impacto en el rendimiento de muchas herramientas EDA actuales.

Con respecto a las aplicaciones en VLSI CAD (Computer-Aided Design), la mayoría de las instancias de formulaciones SAT comienzan a partir de una descripción abstracta del circuito, para lo cual se necesita validar un valor de salida requerido. La formulación resultante se mapea a continuación sobre una instancia de SAT, típicamente usando formulación en formato de Forma Normal Conjuntiva (CNF).

Los SAT-solvers basados en CNF pueden aplicarse directamente a los circuitos booleanos transformando todo el circuito en fórmulas CNF.

La mayoría de los SAT-solvers operan sobre problemas especificados en formato CNF. Esta forma consiste en el AND lógico de una o más cláusulas, que son a su vez un OR lógico de uno o más literales. El literal comprende la unidad lógica fundamental en el problema, siendo simplemente una instancia de una variable o su complemento. Todas las funciones booleanas se pueden describir en el formato

CNF. La ventaja de CNF es que, en esta forma, para que el problema sea satisfecho, cada cláusula individual debe ser satisfecha.

#### 3.3 FORMATO DE DESCRIPCIÓN PARA SAT: CNF

Antes de que un problema combinatorio pueda ser resuelto por los métodos actuales de SAT, normalmente debe ser transformado (codificado) a formato CNF, que consiste en una conjunción de cláusulas Ci, donde cada cláusula Ci es una disyunción de literales Lj, y cada literal Lj es una variable booleana o su negación. CNF tiene la ventaja de ser un formato muy simple, que conduce a la fácil implementación de algoritmos de búsqueda. Además, es un formato de archivo común. Lamentablemente, hay varias maneras de codificar la mayoría de los problemas y pocas directrices sobre cómo elegir entre ellos, sin embargo, la elección de la codificación puede ser tan importante como la elección del algoritmo de búsqueda.

Este formato se utiliza para definir una expresión booleana, escrita en CNF, que se puede utilizar como entrada para el problema de satisfacibilidad (SAT). Este problema considera el caso en el que se usan N variables booleanas para formar una expresión booleana que implica negación (NOT), conjunción (AND) y disyunción (OR). El problema es determinar si hay alguna asignación de valores a las variables booleanas que hace que la fórmula sea verdadera. Es algo así como tratar de mover un montón de interruptores para encontrar la combinación que hace que una bombilla se encienda.

En resumen, para que un problema SAT sea resuelto es común requerir que la expresión booleana sea escrita en formato CNF, que consiste en:

- 1. *cláusulas* unidas por AND;

- 2. cada cláusula, a su vez, consiste en *literales* unidos por OR;

- 3. cada literal es el nombre de una variable (*un literal positivo*) o el nombre de una variable precedida por NOT (*un literal negativo*).

En la Figura 3 se muestra un ejemplo de una expresión booleana de 3 variables y 2 cláusulas.

```

( x(1) OR ( NOT x(3) ) )

AND

( x(2) OR x(3) OR ( NOT x(1) ) )

```

Figura 3: Expresión booleana

El formato de archivo CNF es un formato de archivo ASCII.

- El archivo puede comenzar con líneas de comentario. El primer carácter de cada línea de comentario debe ser una letra minúscula "c". Las líneas de comentario normalmente se sitúan en una sección al principio del archivo, pero se les permite aparecer en todo el archivo.

- 2. Las líneas de comentario son seguidas por la línea de "problema". Esto comienza con la letra minúscula "p" seguida por un espacio, seguido por el tipo de problema, que para los archivos CNF es "cnf", seguido por el número de variables seguido por el número de cláusulas.

- 3. El resto del archivo contiene líneas que definen las cláusulas, una por una.

- 4. Una cláusula se define enumerando el índice de cada literal positivo y el índice negativo de cada literal negativo. Los índices comienzan en 1 y, por razones obvias, el índice 0 no está permitido.

- 5. La definición de una cláusula puede extenderse más allá de una sola línea de texto.

- 6. La definición de una cláusula se termina por un valor final de "0".

- 7. El archivo finaliza después de que se define la última cláusula.

Algunas curiosidades a tener en cuenta incluyen:

- La definición de la siguiente cláusula comienza normalmente en una nueva línea, pero puede seguir, en la misma línea, al "0" que marca el final de la cláusula anterior.

- En algunos ejemplos de archivos CNF, la definición de la última cláusula no termina con un "0" final.

- En algunos ejemplos de archivos CNF, no se sigue la regla de numeración de las variables de 1 a N. El archivo puede declarar que hay 10 variables, por ejemplo, pero permitir que se numeren de 2 a 11.

#### 3.3.1 EJEMPLO CNF

En la Figura 4 se muestra el archivo CNF que corresponde a la expresión booleana simple mostrada en la Figura 3.

```

c simple_v3_c2.cnf

p cnf 3 2

1 -3 0

2 3 -1 0

```

Figura 4: Codificación en formato CNF

#### 3.3.2 FORMATO DE ARCHIVO DIMACS PARA CNF

En el DIMACS Challenge de 1993 [19] fue ideado un formato de archivo para problemas de SAT en CNF y ha sido seguido desde entonces. También se propuso un formato para el SAT general, pero no parece haber sido adoptado en general. Tener un formato de archivo común ha facilitado la recolección de problemas benchmark de SAT en el sitio web de SATLIB, los desafíos de Beijing y las competiciones regulares de SAT-solvers han estimulado una gran cantidad de investigación sobre algoritmos eficientes e implementaciones.

En este formato al principio hay un preámbulo que contiene información sobre el archivo, como pueden ser su nombre, procedencia, etc. Se trata de líneas de

comentario, que son opcionales y comienzan con la letra "c" como puede verse en el ejemplo mostrado en la Figura 5.

c Este es un ejemplo de una línea de comentario.

Figura 5: Línea de comentario en formato CNF

Por convenio, la siguiente línea debe describir la dimensión del problema, indicando la cantidad de variables y cláusulas que tiene el problema codificado en CNF. En la codificación CNF solo hay una línea de este tipo y comienza con la letra "p". El formato de esta línea es el que se muestra en la Figura 6.

p cnf variables cláusulas

Figura 6: Línea de problema en formato CNF

Como ya se ha dicho, esta línea indica el número de variables y cláusulas booleanas en el archivo, donde las variables y cláusulas son enteros positivos, siendo las variables numeradas desde 1 hasta variables.

El resto del archivo contiene las cláusulas. Cada cláusula está representada por una lista de enteros, seguida de un cero que representa el final de la cláusula. Los números enteros deben estar separados por espacios, tabuladores o salto de línea. Un número entero positivo  $\bf i$  representa un literal positivo con la variable número  $\bf i$ , mientras que un número entero negativo  $-\bf i$  representa un literal negativo con la variable número  $\bf i$ . Por ejemplo, la línea mostrada en la Figura  $\bf 7$  representa la cláusula  $\bf v(1)$  OR  $\bf v(3)$  OR ( NOT  $\bf v(7)$  ).

1 3 -7 0

Figura 7: Cláusula en formato CNF

Las cláusulas pueden extenderse por más de una línea; los espacios y tabuladores pueden insertarse libremente entre enteros, y tanto el orden de literales en una cláusula como el orden de cláusulas en el archivo son irrelevantes en cuanto a la descripción del problema, pero tienen cierta importancia en cuanto a que los SAT-solvers pueden tardar más o menos tiempo en resolver un problema dependiendo del orden de las cláusulas y sus literales.

#### 3.3.3 Propiedades deseables de las codificaciones CNF

Hay algunas características de una codificación CNF que la hacen mejor que otra. A continuación, se exponen características que se han propuesto como deseables.

#### 3.3.3.1 Tamaño de codificación

Por el tamaño de una codificación se puede estimar el número de sus cláusulas, literales o variables. En primer lugar, se considera el número de cláusulas. Existen diversas técnicas para reducir la cantidad de cláusulas en un archivo CNF, posiblemente convirtiendo una codificación grande intratable en una más manejable.

En segundo lugar, se tiene en cuenta el número total de literales en la codificación, que se calcula sumando las longitudes de la cláusula, lo cual también tiene un fuerte efecto sobre los *overheads* de tiempo de ejecución. Como medida de la memoria utilizada por una codificación es más preciso que el número de cláusulas.

En tercer lugar, se considera el número de variables en la codificación. Analizando el tiempo de ejecución de los algoritmos SAT, en términos de número de variables en la fórmula, parece útil minimizar el número de variables. Por otra parte, puede haber razones de modelado para no minimizar el número de variables, ya que puede ser más conveniente para expresar las limitaciones del problema.

En la práctica, reducir el tamaño de una codificación no es garantía de rendimiento, independientemente de cómo se mida. Sin embargo, las codificaciones pequeñas valen la pena porque los resultados computacionales pueden ser muy impredecibles y, si no hay más diferencias que el tamaño, es preferible una codificación más pequeña.

#### 3.3.3.2 Densidad de la solución

Otra propiedad interesante de una codificación es su densidad de solución, que puede definirse como el número de soluciones dividido por 2<sup>n</sup>, donde n es el número de variables SAT. La idea de que una mayor densidad de solución hace que un problema sea más fácil de resolver parece natural, y normalmente se supone que tiene al menos algún efecto en el rendimiento de la búsqueda. Podría esperarse que un algoritmo de búsqueda pueda resolver un problema (satisfactorio) más rápidamente si tiene mayor densidad de solución.

## 3.4 PROGRAMACIÓN LINEAL ENTERA MIXTA (MILP)

A lo largo de más de 50 años de existencia, la teoría de la programación lineal entera mixta (MILP) y la práctica se han desarrollado significativamente, y ahora es una herramienta indispensable en los negocios y la ingeniería. Dos razones para el éxito de MILP son los *solvers* basados en la programación lineal (LP) y la flexibilidad del modelado con MILP. Existen varios solucionadores extremadamente eficaces que incorporan muchas técnicas avanzadas y, desde sus primeras etapas, MILP se ha utilizado para modelar una amplia gama de aplicaciones

Un MILP es un LP más restringido por las restricciones de integralidad. Se dice que es un MILP cuando algunas, pero no todas, las variables están restringidas a ser enteros.

MILP maximiza o minimiza una función objetivo lineal sujeta a desigualdades lineales y restricciones de integridad en algunas de las variables.

La Programación Lineal (LP) se ocupa de maximizar o minimizar una ecuación sujeta a ciertos criterios o restricciones. Un ejemplo simple podría ser el dado en la Figura 8.

```

Max: z = 3x1 - x2 + 5x3

Tal que x1 + 2x2 - 4x3 \le 7

7x1 - 5x2 - x3 \le 2

-x1 + 3x2 + 9x3 \le 13

xi \ge 0, i = 1, \dots, 3

```

Figura 8: Problema de Programación Lineal

El problema de la Figura 8 puede resolverse usando el Método Simplex para encontrar una solución de: x = (x1, x2, x3) = (0.5, 0, 1.5).

En MILP algunas partes de la solución pueden estar restringidas a números enteros. Los MILP son LP que requieren que algunas o todas las variables sean enteros. Redondear simplemente la solución a menudo comprometerá la solución, ya que el redondeo puede no estar en la región factible.

Una forma de resolver MILP es enumerar todas las soluciones enteras en la región factible y verificar individualmente cada una de ellas para obtener la óptima. Sin embargo, a medida que las dimensiones del problema crezcan, la enumeración se revelará como un problema de complejidad computacional de clase NP complejo (NP-hard), lo que significa que el número de soluciones enteras factibles crecerá exponencialmente.

#### 3.4.1 REGLAS DE SINTAXIS DEL FORMATO DE ARCHIVO LP

Cualquier cosa que siga una barra invertida (\) es un comentario y se ignorará hasta que se encuentre un final de línea. Las líneas en blanco también se ignoran. Las líneas en blanco y de comentario pueden colocarse en cualquier lugar y con la frecuencia que se desee en el archivo.

En general, el espacio en blanco entre caracteres es irrelevante, ya que se omite cuando se lee un archivo. Sin embargo, no se permite el espacio en blanco en las palabras clave utilizadas para introducir una nueva sección, como MAX, MIN, ST o BOUNDS. También las palabras clave deben estar separadas por espacio en blanco

del resto del archivo y deben estar al principio de una línea. La longitud máxima de línea permitida es de 255 caracteres.

Saltar espacios puede hacer que se interprete mal (y acepte) una entrada no válida, como la de la Figura 9. Si el usuario pretendía entrar en este ejemplo una restricción no lineal en que el producto de x1 por x2 fuera 0, restricción que no es válida en formato LP, se interpretaría como una restricción lineal especificando que una variable denominada x1x2 debe ser igual a cero.

Figura 9: Uso de espacios en LP

La definición del problema debe comenzar con la palabra MINIMIZE o MAXIMIZE, MINIMUM o MAXIMUM, o las abreviaturas MIN o MAX, en cualquier combinación de mayúsculas y minúsculas. La palabra introduce la sección de función objetivo.

Las variables se pueden nombrar siempre que el nombre no exceda de 16 caracteres, todos los cuales deben ser alfanuméricos (a-z, A-Z, o-9) o uno de estos símbolos:  $! " \# \% \& () /, .; ? @ _`' {} | \sim$ . Los nombres más largos se truncarán a 16. El nombre de una variable no puede comenzar con un número o un punto.

La letra E o e, sola o seguida por otros símbolos válidos, o seguida por otra E o e, debe evitarse ya que esta notación está reservada para entradas exponenciales. Por lo tanto, las variables no pueden llamarse e9, E-24, E8cats u otros nombres que podrían interpretarse como un exponente. Incluso nombres de variables como "entradas" o "ejemplo" pueden causar un error de lectura, dependiendo de su ubicación en una línea de entrada.

Además, los siguientes caracteres no son válidos en los nombres de las variables: ^, \*, [ y ].

La definición de función objetivo debe seguir a MINIMIZE/MAXIMIZE. Se puede introducir en varias líneas siempre y cuando ni una variable, ni una constante,

ni un indicador de sentido sea dividido por un final de línea. Por ejemplo, la función objetivo 1x1 + 2x2 + 3x3 se puede introducir en la forma dada en la Figura 10(a), pero no de la forma de la Figura 10(b), porque este segundo modo divide el nombre de la variable x2 por un retorno.

Figura 10: Uso de final de línea en LP

La función objetivo puede ser nombrada escribiendo un nombre y dos puntos antes de la función objetivo. El nombre de la función objetivo y los dos puntos deben aparecer en la misma línea. Los nombres de las funciones objetivo deben ajustarse a las mismas directrices que los nombres de las variables.

La sección de restricciones es introducida por las palabras clave SUBJECT TO. Esta expresión también puede aparecer como such that, st, S.T. o ST. En cualquier combinación de mayúsculas y minúsculas. Una de estas expresiones debe preceder a la primera restricción y estar separada de ella al menos por un espacio.

Cada definición de restricción debe comenzar en una nueva línea. Una restricción puede ser nombrada escribiendo un nombre y dos puntos antes de la restricción. El nombre de la restricción y los dos puntos deben aparecer en la misma línea. Los nombres de restricciones deben cumplir con las mismas directrices que los nombres de variables. Si no se especifican nombres de restricciones, se asignarán los nombres R1, R2, R3, etc.

Las restricciones se introducen de la misma manera que la función objetivo; sin embargo, una restricción debe ser seguida por una indicación de su sentido y un coeficiente a su derecha. El coeficiente del lado derecho debe escribirse en la misma línea que el indicador de sentido. Los indicadores de sentido aceptables son <, <=, =<,>=, >=, >=, >=, >=, >=, >=, >=, >=, respectivamente.

Por ejemplo, en la Figura 11 hay una restricción con nombre:

Figura 11: Restricción con nombre en LP

La sección BOUNDS (límites) es opcional y sigue a la sección obligatoria de restricciones. Está precedida por la palabra bounds o bound en cualquier combinación de mayúsculas y minúsculas.

Cada definición de límites debe comenzar en una nueva línea. El formato para un límite es  $1_n \le x_n \le u_n$  excepto en los siguientes casos:

Los límites superior e inferior también se pueden introducir por separado como en la Figura 12.

$$\begin{array}{ccc}

1_n & <= & x_n \\

x_n & <= & u_n

\end{array}$$

Figura 12: Bounds en LP

- 2. Con el límite inferior predeterminado de 0 (cero) y el límite superior por defecto de +∞, permaneciendo en efecto hasta que el límite se cambia explícitamente.

- 3. Los límites que fijan una variable se pueden introducir como igualdades simples. Por ejemplo, x5 = 5.6 es equivalente a 5.6 <= x5 <= 5.6.

Los límites  $+\infty$  (infinito positivo) y  $-\infty$  (infinito negativo) deben introducirse como palabras: +infinity, -infinity, +inf, -inf.

Una variable con un límite inferior infinito negativo y un límite superior infinito positivo se puede introducir como free, en cualquier mezcla de mayúsculas

y minúsculas, con un espacio que separa el nombre de la variable y la palabra free. Por ejemplo, x7 free equivale a -infinity <= x7 <= +infinity.

El archivo debe terminar con la palabra end en cualquier combinación de mayúsculas y minúsculas, solo en una línea. Esta palabra no es estrictamente necesaria, pero se recomienda encarecidamente. Los archivos que se han dañado con frecuencia se pueden detectar por una última línea que falta.

Para especificar cualquiera de las variables como variables enteras generales, se agrega una sección GENERAL; para especificar cualquiera de las variables como variables binarias enteras, se añade una sección BINARY. Las secciones GENERAL y BINARY siguen la sección BOUNDS, si hay una; de lo contrario, siguen la sección de restricciones. Cualquiera de las secciones GENERAL o BINARY puede preceder a la otra. La sección GENERAL está precedida por la palabra GENERAL, GENERALS, o GEN que debe aparecer solo en una línea. La línea o líneas siguientes deben enumerar los nombres de todas las variables que deben restringirse a valores enteros generales, separados por al menos un espacio. La sección BINARY está precedida por la palabra BINARY, BINARIES o BIN que debe aparecer solo en una línea. La línea o líneas siguientes deben enumerar los nombres de todas las variables que deben restringirse a valores enteros binarios, separados por al menos un espacio. Las variables binarias reciben automáticamente los límites de 0 (cero) y 1 (uno), a menos que se especifiquen límites alternativos en la sección BOUNDS, en cuyo caso se emite un mensaje de advertencia.

En la Figura 13 se muestra un ejemplo de una formulación de problemas en formato LP donde x4 es un entero general.

Para especificar cualquiera de las variables como variables semi-continuas, es decir, como variables que pueden tomar el valor 0 o valores entre los límites inferiores y superiores especificados, se utiliza la sección SEMI-CONTINUOUS. Esta sección debe seguir las secciones BOUNDS, GENERALS y BINARIES. La sección SEMI-CONTINUOUS está precedida por la palabra clave SEMI-CONTINUOUS, SEMI o SEMIS. La línea o líneas siguientes deben enumerar los nombres de todas las

variables que se van a declarar semi-continuas, separadas por al menos un espacio como en la figura 14.

Figura 13: Codificación LP

Semi-continuous x1 x2 x3

Figura 14: Variables semi-continuas en LP

Para especificar conjuntos especiales ordenados, hay que utilizar una sección SOS, que está precedida por la palabra clave SOS. La sección SOS debe seguir a las secciones Bounds, General, Binaries y Semi-Continuous. Los conjuntos ordenados especiales de tipo 1 requieren que, de las variables en el conjunto, una como máximo pueda ser distinta de cero. Los conjuntos ordenados especiales del tipo 2 requieren que como máximo dos variables en el conjunto puedan ser distintas de cero y, si hay dos distintas de cero, deben ser adyacentes. La adyacencia se define por los pesos, que deben ser únicos dentro de un conjunto dado a las variables. Los

pesos ordenados definen el orden del conjunto ordenado especial. El conjunto se especifica mediante un nombre de conjunto opcional seguido de dos puntos y, a continuación, una de las palabras clave S1 o S2 (que especifica el tipo) seguido de dos puntos dobles. Los nombres de los miembros del conjunto se enumeran en esta línea o líneas, con sus pesos. Los nombres y pesos de las variables están separados por dos puntos como puede verse en la Figura 15.

SOS set1: S1:: x1:10 x2:13

Figura 15: Conjuntos especiales ordenados en LP

#### 3.5 LP-SOLVER CPLEX®

CPLEX® [20] es una herramienta para resolver problemas de optimización relacionados con LP. Específicamente, resuelve problemas de optimización con restricciones lineales o cuadráticas, donde el objetivo a optimizar puede expresarse como una función lineal o una función cuadrática convexa. Las variables en el problema pueden ser declaradas como continuas o restringidas para tomar solo valores enteros.

El Optimizador Interactivo de CPLEX® es un programa ejecutable que puede leer un problema interactivamente o de archivos en ciertos formatos estándar, resolver el problema y entregar la solución interactivamente o en archivos de texto. El programa consiste en el archivo cplex.exe en plataformas Windows o cplex en plataformas UNIX.

CPLEX® es, entre otras, una herramienta para resolver problemas de programación matemática en los cuales algunas o todas las variables deben asumir valores enteros en la solución. Tales problemas se conocen como programas enteros mixtos o MIP porque pueden combinar variables continuas y discretas (por ejemplo, enteras) en la función objetivo y en las restricciones. Los MIP con objetivos lineales se denominan programas lineales enteros mixtos o MILP, y los MIP con términos

objetivos cuadráticos se denominan programas cuadráticos enteros mixtos o MIQP. Del mismo modo, MIPs que también son cuadráticamente restringidos en el sentido de QCP se conocen como programas mixtos enteros cuadráticamente restringidos o MIQCPs.

Dentro de la categoría de programas enteros mixtos, hay dos tipos de variables enteras discretas: si los valores enteros de las variables discretas deben ser 0 (cero) o 1 (uno), entonces se les conoce como binarios; si los valores enteros no están restringidos de esa manera, se les conoce como variables enteras generales.

#### 3.6 CONCLUSIONES

La satisfacibilidad está estrechamente relacionada con los conceptos centrales de la lógica, en los cuales tiene sus orígenes. Es más, la presencia de la satisfacibilidad en la lógica surge para modelar el pensamiento humano y el razonamiento científico a través de su uso en el diseño de computadoras y ahora se utiliza como herramienta de modelado para resolver gran variedad de problemas prácticos. Por todo ello, se ha revelado como una potente herramienta que permite modelar y resolver multitud de problemas, principalmente aquellos que comparten sus raíces en la lógica como es el caso del diseño y prueba de circuitos.

El formato de Forma Normal Conjuntiva (CNF) es el más ampliamente usado para describir los problemas que deberán resolver los SAT-solvers, razón por la que en este trabajo se toma como formato de partida. Una instancia de SAT es una fórmula de CNF  $\Phi$ . El problema de satisfacibilidad es determinar si existe una asignación de valores a las variables de  $\Phi$  que hace que  $\Phi$  se evalúe a 1.

Los modelos de programación entera surgen en prácticamente todas las áreas de aplicación de la programación matemática. Una amplia gama de problemas se puede modelar como problemas de Programación Lineal Entera Mixta (MILP). Se debe desarrollar una apreciación preliminar de la importancia de estos modelos.

# CAPÍTULO 4 MÉTODO DESARROLLADO

#### 4.1 Introducción

En este Proyecto Fin de Carrera se propone un nuevo método para la generación de vectores para la verificación de circuitos booleanos haciendo uso de Programación Lineal Entera Mixta

Tras haber presentado los diferentes entornos en los que se enmarca este trabajo, se procede en este capítulo a exponer el método desarrollado. Para comenzar, se presenta el método de una forma genérica. Seguidamente, se explica cómo se ha hecho cada una de las partes que lo componen. A continuación, se muestran los modelos MILP desarrollados y los programas que han sido creados para describir los circuitos en MILP. Finalmente se explica el programa desarrollado para conseguir las soluciones de los circuitos y obtener vectores para la verificación de los mismos.

#### 4.2 ENTORNO DE VERIFICACIÓN

Tal como se prevé en los objetivos, este entorno se ejecuta a nivel de línea de comandos y se ha desarrollado completamente en C. Su ejecución está prevista para máquinas Linux o Unix.

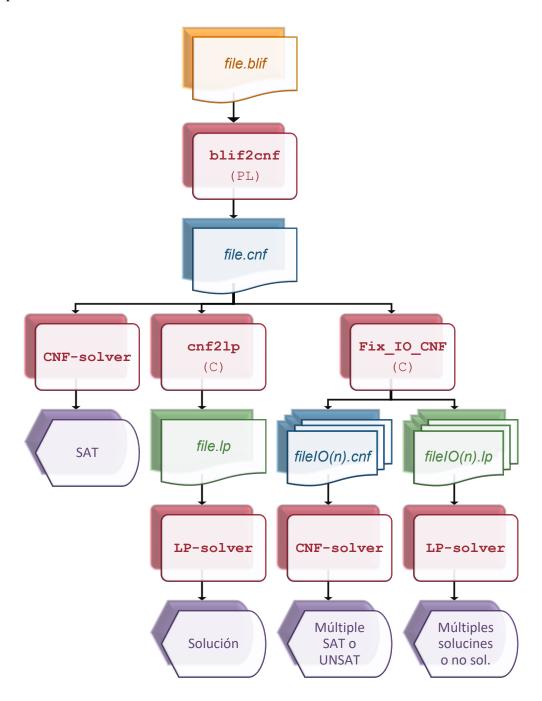

Figura 16: Entorno de Verificación

En la Figura 16 se muestra un diagrama de flujo en el que pueden observarse las potencialidades del entorno de verificación diseñado. Para explicar las

alternativas que ofrece, se muestra un ejemplo de circuito booleano al que se le aplica el método desarrollado.

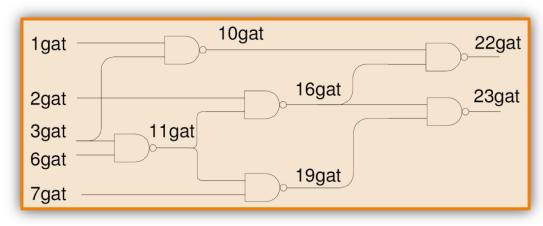

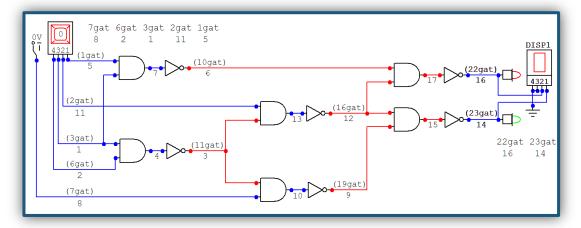

El circuito elegido es C17 (Figura 17), se trata de un circuito booleano compuesto por 6 puertas, y cuenta con 5 entradas y 2 salidas.

Figura 17: Circuito Booleano C17