## Máster en Tecnologías de Telecomunicación

## Trabajo Fin de Máster

Técnicas de compresión de imágenes hiperespectrales para aplicaciones espaciales

Autor: Aday García del Toro

Tutores: Dr. Roberto Sarmiento Rodríguez

Dr. José Fco. López Feliciano

Fecha: Diciembre 2012

## Máster en Tecnologías de Telecomunicación

## Trabajo Fin de Máster

# Técnicas de compresión de imágenes hiperespectrales para aplicaciones espaciales

### **HOJA DE FIRMAS**

**Alumno:** Aday García del Toro Fdo.:

**Tutor:** Dr. Roberto Sarmiento Rodríguez Fdo.:

**Tutor:** Dr. José Fco. López Feliciano Fdo.:

Fecha: Diciembre 2012

## Máster en Tecnologías de Telecomunicación

## Trabajo Fin de Máster

# Técnicas de compresión de imágenes hiperespectrales para aplicaciones espaciales

## **HOJA DE EVALUACIÓN**

| Calificación:         |       |

|-----------------------|-------|

| Presidente            | Fdo.: |

| Secretario            | Fdo.: |

| Vocal                 | Fdo.: |

| Eachar Diciombra 2012 |       |

Fecha: Diciembre 2012

### Índice de Contenidos

| 1. | INTRODU              | CCIÓN Y OBJETIVOS                                                        | 1          |

|----|----------------------|--------------------------------------------------------------------------|------------|

|    | 1.1. OBJE            | TIVOS                                                                    |            |

|    |                      | UCTURA DE LA MEMORIA                                                     |            |

| •  |                      |                                                                          |            |

| 2. |                      | DEL ARTE                                                                 |            |

|    |                      | CEPTO DE IMAGEN HIPERESPECTRAL                                           |            |

|    | 2.2. ALG             | DRITMOS DE COMPRESIÓN DE IMÁGENES HIPERESPECTRALES                       |            |

|    | 2.2.1.               | Algoritmos de compresión sin pérdidas (lossless compression)             |            |

|    | 2.2.1.1.             | 7,7 7,7 7,7 7,7 7,7 7,7 7,7 7,7 7,7 7,7                                  |            |

|    | 2.2.2.               | Algoritmos de compresión con pérdidas (lossy compression)                |            |

|    | 2.2.2.1.             | Lossy Compression for Exomars (LCE) Algorithm                            | 13         |

| 3. | DESARRO              | LLO DE LA ARQUITECTURA IMPLEMENTADA                                      | 17         |

|    | 3.1. IMPL            | EMENTACIÓN DEL ALGORITMO LCE EN EL SOFTWARE DE REFERENCIA                | 17         |

|    |                      | RACIÓN DEL CÓDIGO DE REFERENCIA EN MÓDULOS FUNCIONALMENTE INDEPENDIENTES |            |

|    | 3.2.1.               | Módulo adgolomb.cpp                                                      |            |

|    | 3.2.1.<br>3.2.2.     | Módulo calc perr.cpp                                                     |            |

|    | 3.2.2.<br>3.2.3.     | Módulo estimationIs.cpp                                                  |            |

|    |                      | • •                                                                      |            |

|    | 3.2.4.               | Módulo init_output.cpp                                                   |            |

|    | 3.2.5.               | Módulo mean.cpp                                                          |            |

|    | 3.2.6.               | Módulo pred_2D.cpp                                                       |            |

|    | 3.2.7.               | Módulo write_alphamu.cpp                                                 |            |

|    | 3.2.8.               | Módulo zero_block.cpp                                                    |            |

|    |                      | ERACIÓN DEL LENGUAJE DE DESCRIPCIÓN HARDWARE VHDL                        |            |

|    | 3.3.1.               | Metodología de diseño en la herramienta Catapult C                       |            |

|    | 3.3.1.1.             |                                                                          |            |

|    | 3.3.1.2.             |                                                                          |            |

|    | 3.3.1.3.             |                                                                          |            |

|    | 3.3.1.4.             |                                                                          |            |

|    | 3.3.1.5.<br>3.3.1.6. | Paso 5. Generación del RTLFlujo de verificación SCVerify                 |            |

|    | 3.3.1.6.<br>3.3.2.   | Implementación de los módulos mediante la herramienta Catapult C         |            |

|    | 3.3.2.1.             |                                                                          |            |

|    | 3.3.2.1.             | Implementación del módulo calc_perr.cpp                                  |            |

|    | 3.3.2.3.             | Implementación del módulo estimationls.cpp                               |            |

|    | 3.3.2.4.             | Implementación del módulo init output.cpp                                |            |

|    | 3.3.2.5.             | Implementación del módulo mean . cpp                                     |            |

|    | 3.3.2.6.             | Implementación del módulo pred_2D.cpp                                    |            |

|    | 3.3.2.7.             | Implementación del módulo write_alphamu.cppcpp                           |            |

|    | 3.3.2.8.             | Implementación del módulo zero_block.cpp                                 | 42         |

|    | 3.4. DISE            | ÑO, IMPLEMENTACIÓN Y VERIFICACIÓN DEL CONTROLADOR HARDWARE               | 43         |

|    | 3.4.1.               | Diseño del módulo hwctrl                                                 | 43         |

|    | 3.4.2.               | Implementación del módulo hwctrl                                         | 47         |

|    | 3.4.2.1.             | Módulo hwctrl                                                            | 47         |

|    | 3.4.3.               | Verificación del módulo hwctrl                                           |            |

|    | 3.4.3.1.             | Resultados de la verificación del módulo hwctrl                          | 56         |

| 4. | RESULTA              | DOS Y CONCLUSIONES                                                       | 57         |

|    |                      | ESIS SOBRE FPGA                                                          |            |

|    |                      | ATEGIAS DE OPTIMIZACIÓN                                                  |            |

|    |                      |                                                                          |            |

|    | 4.5. CON             | CLUSIONES                                                                | b <u>.</u> |

## Índice de Figuras

| FIGURA 1.1. SATÉLITE SPOT5 (IZQUIERDA) Y SU UNIDAD DE COMPRESIÓN (DERECHA)                        | 1  |

|---------------------------------------------------------------------------------------------------|----|

| FIGURA 1.2. SATÉLITE PLEIADES-HR (IZQUIERDA) Y SU UNIDAD DE COMPRESIÓN (DERECHA)                  | 2  |

| FIGURA 2.1. IMAGEN HIPERESPECTRAL (CUBO HIPERESPECTRAL)                                           | 6  |

| FIGURA 2.2. IMAGEN HIPERESPECTRAL – TIPOS DE PÍXELES                                              |    |

| FIGURA 2.3. ESQUEMA DEL COMPRESOR                                                                 |    |

| IGURA 2.4. VECINDAD, DISPOSICIÓN TÍPICA                                                           | 9  |

| FIGURA 2.5. MUESTRAS USADAS PARA EL CÁLCULO DE LAS SUMAS LOCALES                                  | 10 |

| FIGURA 2.6. CÓMPUTO DE LAS DIFERENCIAS LOCALES EN CADA BANDA ESPECTRAL                            | 11 |

| FIGURA 2.7. ESTRUCTURA DE LA IMAGEN COMPRIMIDA                                                    |    |

| Figura 2.8. Localización de la muestra actual y su vecindad                                       |    |

| FIGURA 2.9. FORMATO DEL FICHERO COMPRIMIDO GENERADO POR EL ALGORITMO LCE                          | 16 |

| FIGURA 3.1. PSEUDO-CÓDIGO DE LA FUNCIÓN PRED1BLOCK ( )                                            | 18 |

| FIGURA 3.2. CÓDIGO ANSI C DE LA FUNCIÓN PRED1BLOCK ( )                                            | 20 |

| FIGURA 3.3. FLUJOS DE DATOS                                                                       |    |

| FIGURA 3.4. ASPECTO DE LA INTERFAZ DE LA HERRAMIENTA CATAPULT C                                   | 27 |

| FIGURA 3.5. ASPECTO DE LA INTERFAZ DE LA HERRAMIENTA PRECISION RTL SYNTHESIS                      | 28 |

| FIGURA 3.6. ASPECTO DE LA INTERFAZ DE LA HERRAMIENTA MODELSIM TRAS SU LLAMADA MEDIANTE CATAPULT C | 31 |

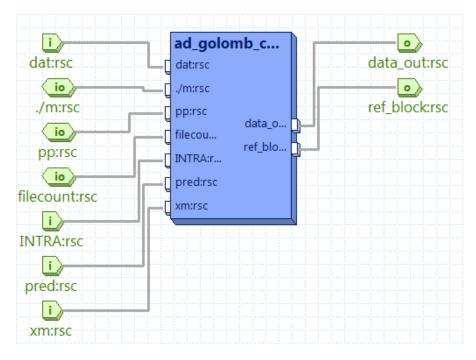

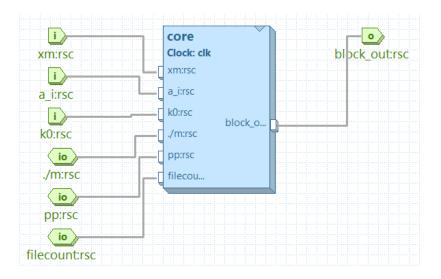

| FIGURA 3.7. INTERFAZ MÓDULO ADGOLOMB • CPP                                                        |    |

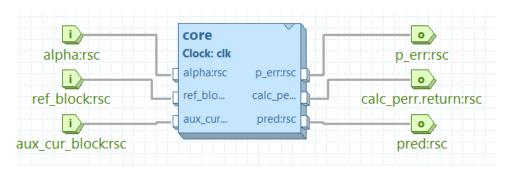

| GURA 3.8. INTERFAZ MÓDULO CALC_PERR • CPP                                                         | 34 |

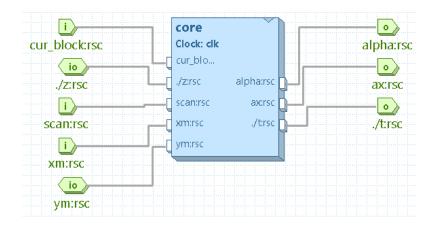

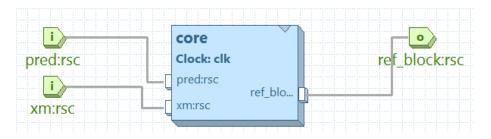

| FIGURA 3.9. INTERFAZ MÓDULO ESTIMATIONLS • CPP                                                    | 36 |

| FIGURA 3.10. INTERFAZ MÓDULO INIT_OUTPUT.CPP                                                      | 37 |

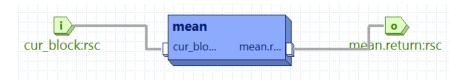

| FIGURA 3.11. INTERFAZ MÓDULO MEAN . CPP                                                           | 38 |

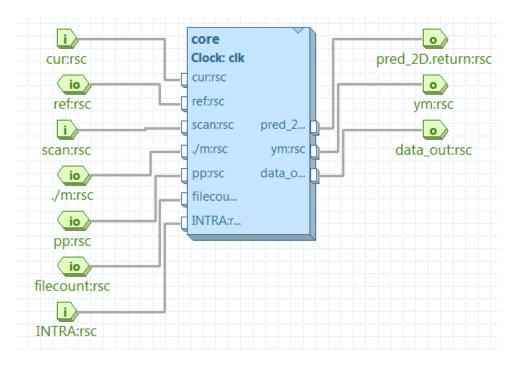

| FIGURA 3.12. INTERFAZ MÓDULO PRED_2D.CPP                                                          | 39 |

| FIGURA 3.13. INTERFAZ MÓDULO WRITE_ALPHAMU.CPP                                                    | 41 |

| FIGURA 3.14. INTERFAZ MÓDULO ZERO_BLOCK • CPP                                                     | 42 |

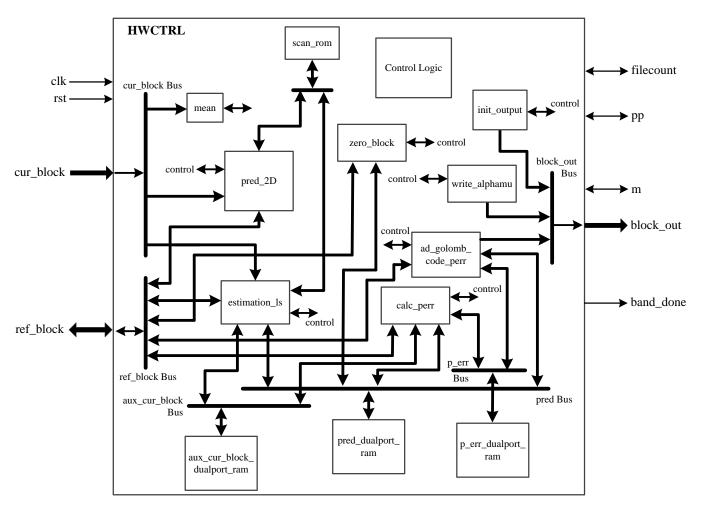

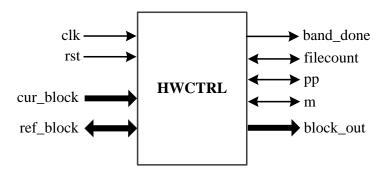

| FIGURA 3.15.CONTROLADOR HARDWARE (HWCTRL), ESQUEMA GENERAL                                        | 44 |

| FIGURA 3.16. INTERFACES DEL MÓDULO CONTROLADOR DE HARDWARE (HWCTRL)                               | 44 |

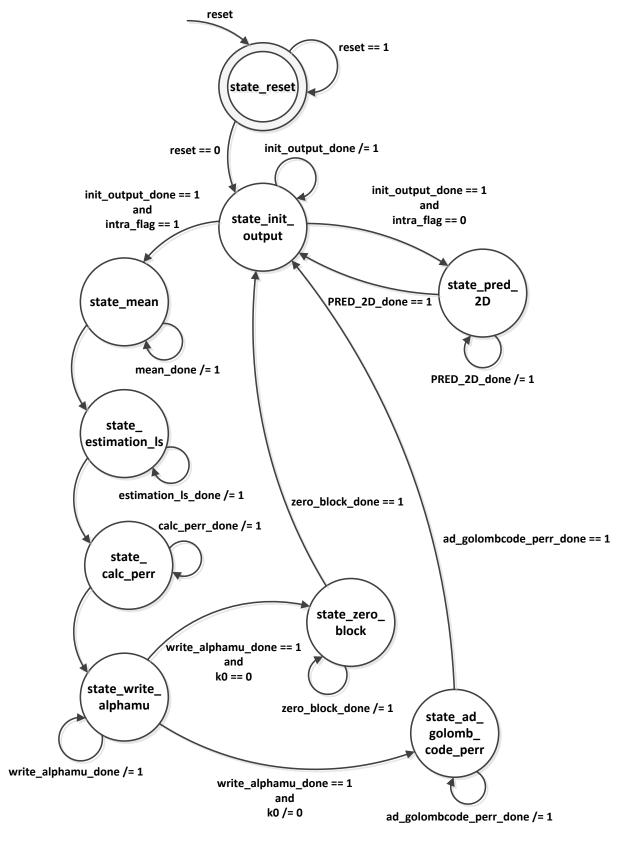

| FIGURA 3.17. DIAGRAMA DE ESTADOS DE LA FSM PERTENECIENTE AL BLOQUE FUNCIONAL HWCTRL               | 49 |

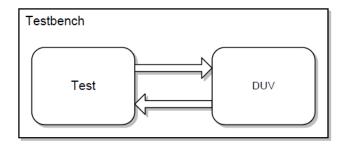

| FIGURA 3.18. ESTRUCTURA GENÉRICA DEL ENTORNO DE SIMULACIÓN                                        | 53 |

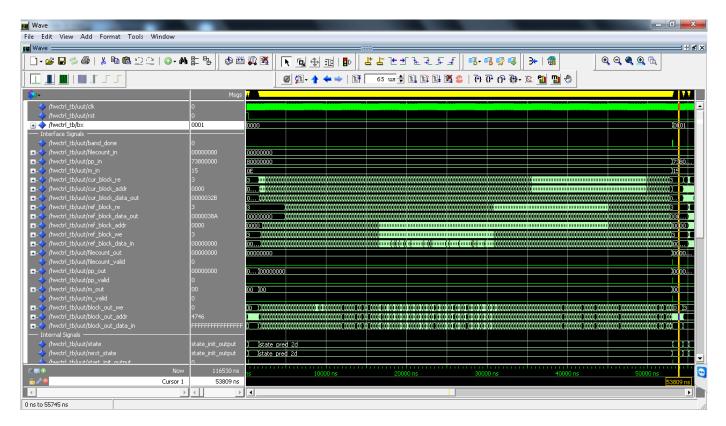

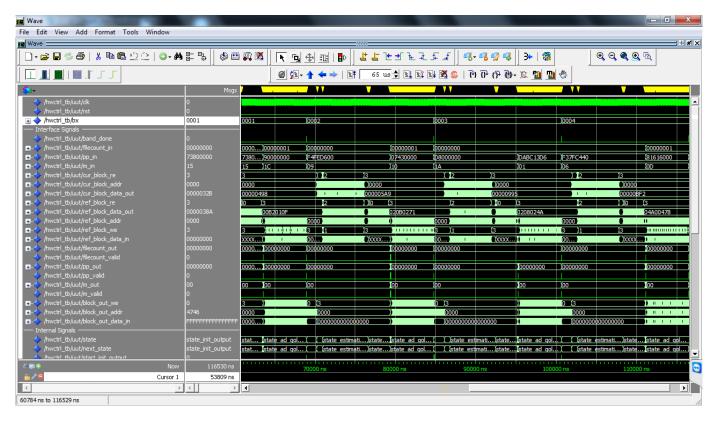

| Figura 3.19. Simulación hwctrl banda 0, $oldsymbol{i}=oldsymbol{0}$                               | 54 |

| Figura 3.20. Simulación hwctrl resto de bandas, $i  eq 0$                                         | 55 |

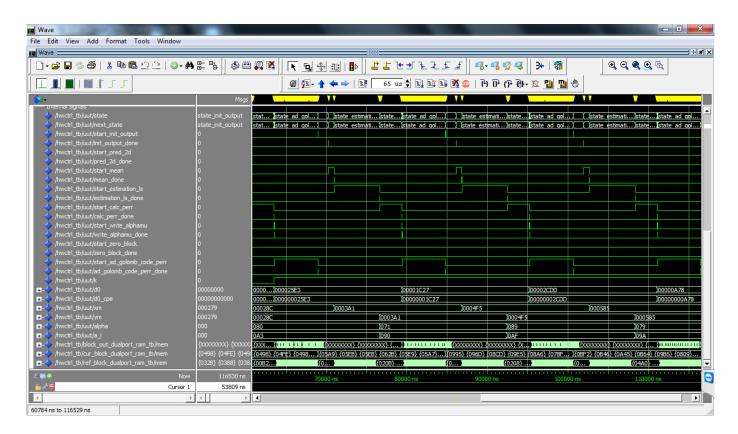

| IGURA 3.21. SIMULACIÓN HWCTRL SEÑALES INTERNAS REPRESENTATIVAS                                    | 55 |

## Índice de Tablas

| TABLA 3.1. INTERFAZ DEL MÓDULO ADGOLOMB . CPP                                               | 22 |

|---------------------------------------------------------------------------------------------|----|

| TABLA 3.2. INTERFAZ DEL MÓDULO CALC_PERR.CPP                                                | 23 |

| TABLA 3.3. INTERFAZ DEL MÓDULO ESTIMATIONLS.CPP                                             | 24 |

| TABLA 3.4. INTERFAZ DEL MÓDULO INIT_OUTPUT.CPP                                              | 24 |

| TABLA 3.5. INTERFAZ DEL MÓDULO MEAN CPP                                                     |    |

| TABLA 3.6. INTERFAZ DEL MÓDULO PRED_2D. CPP                                                 | 25 |

| TABLA 3.7. INTERFAZ DEL MÓDULO WRITE_ALPHAMU.CPP                                            | 26 |

| TABLA 3.8. INTERFAZ DEL MÓDULO ZERO_BLOCK.CPP                                               | 26 |

| Tabla 3.9. Estimaciones para el módulo adgolomb . CPP                                       |    |

| TABLA 3.10. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO ADGOLOMB. CPP     |    |

| TABLA 3.11. ESTIMACIONES PARA EL MÓDULO CALC_PERR.CPP                                       |    |

| TABLA 3.12. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO CALC_PERR.CPP     |    |

| TABLA 3.13. ESTIMACIONES PARA EL MÓDULO ESTIMATIONLS . CPP                                  |    |

| TABLA 3.14. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO ESTIMATIONLS.CPP  |    |

| TABLA 3.15. ESTIMACIONES PARA EL MÓDULO INIT_OUTPUT.CPP                                     | 37 |

| TABLA 3.16. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO INIT_OUTPUT.CPP   |    |

| TABLA 3.17. ESTIMACIONES PARA EL MÓDULO MEAN, CPP                                           |    |

| TABLA 3.18. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO MEAN. CPP         |    |

| TABLA 3.19. ESTIMACIONES PARA EL MÓDULO PRED_2D.CPP                                         |    |

| Tabla 3.20. Resultados obtenidos tras el emplazamiento y ruteo del módulo pred_2D.cpp       |    |

| TABLA 3.21. ESTIMACIONES PARA EL MÓDULO WRITE_ALPHAMU.CPP                                   | 41 |

| TABLA 3.22. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO WRITE_ALPHAMU.CPP |    |

| TABLA 3.23. ESTIMACIONES PARA EL MÓDULO ZERO_BLOCK • CPP                                    |    |

| TABLA 3.24. RESULTADOS OBTENIDOS TRAS EL EMPLAZAMIENTO Y RUTEO DEL MÓDULO ZERO_BLOCK . CPP  |    |

| Tabla 3.25. Interfaz del módulo hwcrtrl                                                     |    |

| Tabla 3.26. Estados de la FSM del módulo hwctrl                                             |    |

| Tabla 3.27. Especificación de características de las memorias internas en hwctrl            |    |

| Tabla 4.1. Resultados de la síntesis de los módulos de manera independiente                 |    |

| Tabla 4.2. Resultados de la síntesis sobre FPGA del bloque funcional hwctrl                 |    |

| TABLA 4.3. RESULTADOS DE LA SÍNTESIS SOBRE FPGA DEL MÓDULO PRED1BLOCK AL COMPLETO           |    |

| Tabla 4.4. Comparativa implementación algoritmo LCE frente a [32]                           |    |

| Tabla 4.5. Latencia y número de muestras por segundo obtenidas                              |    |

| TABLA 4.6. MUESTRAS POR CICLO MEDIA PARA IMÁGENES DE LOS SENSORES AIRS, AVIRIS Y MODIS      | 60 |

### Acrónimos

ASIC Application-Specific Integrated Circuit

CCSDS Consultative Committee for Space Data Systems

C-DPMC Clustered Differential Pulse Code Modulation

DSP Digital Signal Processor

DUV Design Under Verification

ESA European Space Agency

FPGA Field Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

HLS High Level Synthesis

LCE Lossy Compression for ExoMars

RTL Register Transfer Level

UTQ Uniform-threshold Quantizer

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# Memoria

### 1. Introducción y objetivos

La compresión de imágenes hiperespectrales se ha convertido en un foco de investigación a lo largo de los últimos años debido, principalmente, a la necesidad de adecuar la capacidad de adquisición de los sensores hiperespectrales con las capacidades de comunicación de los enlaces a tierra.

Todo tipo de imágenes espectrales, como multiespectrales, hiperespectrales y ultraespectrales, generan una gran cantidad de información que ha de ser comprimida con el fin de reducir el volumen de datos en la transmisión hacia el segmento terreno [1]. Los diferentes tipos de imágenes espectrales difieren en la cantidad de datos disponibles bien en la dimensión espacial o en la dimensión espectral, requiriendo potencialmente diferentes técnicas de compresión. Por ejemplo, típicamente las imágenes multiespectrales presentan una resolución espacial con alta granularidad mientras que la granularidad en resolución espectral no es tan alta. Por consiguiente, su compresión explota la correlación espacial. El caso opuesto ocurre con las imágenes de tipo hiper- y ultraespectrales, en las que la correlación espectral se presenta como factor dominante.

La compresión resulta de mayor utilidad para sensores espaciales ya que no es posible físicamente desmontar o leer la memoria de almacenamiento que almacena los datos adquiridos. Asimismo, si la resolución del sensor es muy alta o larga la duración de la misión, puede resultar necesaria la aplicación de técnicas de compresión para misiones embarcadas. Las técnicas de compresión de imágenes permiten la transmisión de un volumen mayor de datos en el mismo tiempo. La Figura 1.1 muestra el satélite de teledetección civil SPOT5 y su unidad de compresión. Asimismo, la Figura 1.2 muestra el satélite de observación terrestre PLEIADES-HR y su unidad de compresión.

Figura 1.1. Satélite SPOT5 (izquierda) y su unidad de compresión (derecha)

Figura 1.2. Satélite PLEIADES-HR (izquierda) y su unidad de compresión (derecha)

Existen diferentes tipos de técnicas compresión disponibles. En los algoritmos de compresión sin pérdidas (*loseless compression*), la imagen reconstruida es idéntica a la original [2] [3]. En compresión casi-sin pérdidas (*near-lossless compression*), la diferencia máxima absoluta entre la imagen reconstruida y la imagen original no exceden un valor máximo predefinido [4]. Finalmente, en compresión con pérdidas (*lossy compression*), la imagen reconstruida es similar a la imagen original, típicamente se emplea el error cuadrático medio dada una tasa de bits objeto.

Tradicionalmente, la compresión de imágenes hiperespectrales, ha sido realizada mediante algoritmos de compresión sin pérdidas. Estos algoritmos posibilitan que, tras la compresión, los datos sean reconstruidos sin pérdida alguna de información, es decir, la imagen reconstruida es idéntica a la original [2] [3]. La compresión sin pérdidas resulta la deseada ya que se preserva la integridad de toda la información contenida en la imagen. Sin embargo, los ratios de compresión que se obtienen mediante la aplicación de estos algoritmos son limitados. Los mejores algoritmos de compresión sin pérdidas proporcionan ratios de compresión típicamente del orden de 2:1 a 3:1 [5] [6] [7]. Tómese como ejemplo el algoritmo desarrollado en el estándar CCSDS para la compresión sin pérdidas de imágenes hiperespectrales [8].

Sin embargo, la compresión con pérdidas (*lossy compression*) de imágenes hiperespectrales se ha convertido en objeto de estudio dada la necesidad actual de mayores ratios de compresión. Varios algoritmos encaminados a la compresión con pérdidas de imágenes hiperespectrales han sido desarrollados en la actualidad. Incluso, estándares existentes de compresión en dos dimensiones (2D), tales como JPEG2000, han sido adaptados a la naturaleza tridimensional de las imágenes hiperespectrales [9]. Asimismo, el impacto de la

compresión con pérdidas sobre el procesado los datos ha sido evaluado para varios algoritmos de compresión mostrando que, la precisión en los resultados puede ser preservada alcanzado un ratio de compresión superior a los algoritmos de compresión sin pérdidas [1].

Los algoritmos de compresión suelen ser implementados en hardware el cual debe operar en un sistema embarcado, ya sea en una aeronave o en un satélite. A pesar de que la eficiencia en la codificación se presenta como un aspecto clave para la compresión que se realiza en sistemas embarcados, existen otra serie de importantes requisitos a tener en cuenta. La potencia computacional disponible en un satélite, por ejemplo, es limitada, mucho menor que la disponible en un procesador de gama media del sector comercial. Por lo tanto, se requiere de un algoritmo de baja complejidad. Normalmente, el algoritmo de compresión desplegado se implementa sobre una FPGA (Field Programmable Gate Array), un ASIC (Application-Specific Integrated Circuit) o un DSP (Digital Signal Processor). Muchos de los algoritmos de compresión existentes en la actualidad para imágenes en 2D alcanzan un buen ratio de compresión. Sin embargo, suelen ser demasiado complejos para ser implementados en los dispositivos hardware disponible en un satélite. Por este motivo, nuevos algoritmos de compresión de imágenes hiperespectrales han sido desarrollados completamente desde cero. Un ejemplo de esta aproximación, es el algoritmo desarrollado por Magli et. al. [10] denominado, Lossy Compression for Exomars (LCE) Algorithm.

### 1.1. Objetivos

El objetivo del presente Trabajo Fin de Máster (TFM) es la implementación, verificación y síntesis sobre una FPGA del algoritmo con pérdidas LCE. El resultado de este trabajo es por lo tanto un código RTL sintetizable en el lenguaje de descripción hardware VHDL (VHSIC Hardware Description Language). Para llevar a cabo este trabajo es necesario el uso de varias herramientas software.

Como entradas a este trabajo, ha sido necesario el estudio, en primer lugar, del estado del arte sobre algoritmos de compresión de imágenes hiperespectrales, en especial el algoritmo LCE. Asimismo, para esta implementación se ha partido del código de referencia proporcionado por la Universidad Politécnica de Torino escrito en el lenguaje de alto nivel C/C++. Este código de referencia ha sido previamente modificado con el fin de lograr una mayor aproximación al hardware empleando tipos de datos con resolución a nivel de bit (Algoritmic C data types), reduciendo el número de variables por constantes, evitando las operaciones matemáticas en punto flotante, eliminando accesos a memoria innecesarios y

optimizando bucles. Para mayor información de este trabajo previo sobre el código de referencia consultar [11].

Mediante las entradas descritas, se ha procedido a realizar una separación del código en ANSI C de las funciones que lo componen con el objetivo de obtener mediante la herramienta de síntesis de alto nivel, *High Level Synthesis* (HLS), Catapult C obtener el código RTL sintetizable escrito en VHDL de cada uno de los módulos [12].

En este punto se emplea la herramienta de diseño, simulación y depuración ModelSim con el fin de diseñar y verificar la unidad de control hardware que será la encargada de la conexión y gestión de los flujos de datos de cada uno de los módulos generados.

Finalmente, mediante el empleo de la herramienta Precision Synthesis, se realiza la síntesis de todo el algoritmo de compresión obtenido extrayendo los resultados de la misma. Estos resultados se comparan con los obtenidos en trabajos anteriores [11].

### 1.2. Estructura de la memoria

Esta memoria de trabajo fin de máster se estructura en este primer capítulo de introducción y objetivos en el que se han descrito una serie de conceptos en ideas básicos que sirven para central al lector en el objeto de este trabajo.

En el segundo capítulo se aborda el estado del arte definiendo, en primer lugar, el concepto de imagen hiperespectral y dentro de este amplio campo de estudio, abordando los algoritmos de compresión.

La primera etapa de trabajo realizado, es decir, el trabajo sobre el código de referencia para su separación en funciones y módulos independientes se describe en el tercer capítulo. En el cuarto capítulo se presenta el proceso de conversión desde ANSI C hacia VHDL de estos módulos independientes, haciendo especial hincapié en las decisiones tomadas en el uso de la herramienta Catapult C. El diseño y verificación de la unidad de control hardware se describe en el quinto capítulo.

En el sexto capítulo, se presentan los resultados obtenidos en este trabajo, su comparación con trabajos anteriores y posibles optimizaciones. Finalmente las conclusiones y bibliografía empleada en el trabajo se presentan en las secciones séptima y octava.

### 2. Estado del arte

El Estado del Arte en el presente Trabajo Fin de Máster resume y organiza los resultados recientes de investigación sobre lo concerniente a los algoritmos de compresión embarcados de imágenes hiperespectrales. Así, se presentará una mejor perspectiva de la materia y se evaluarán las principales tendencias en éste área. Para ello, se han analizado algoritmos más relevantes publicados en la literatura concerniente a la compresión de imágenes hiperespectrales como área específica.

No se entrará en excesivo detalle en sus respectivas descripciones salvo, que el algoritmo aporte algún concepto novedoso, pues la mayoría de algoritmos estudiados se basan en los mismos principios de funcionamiento.

Además, en este segundo capítulo, se realiza una presentación del concepto de imagen hiperespectral prestando especial atención en la necesidad de la existencia de algoritmos de compresión, especialmente en sistemas embarcados.

Como se describe en la sección anterior, los sistemas embarcados, ya sea en dispositivos tales como aeronaves o satélites, presentan una serie de requisitos exigentes en cuanto a consumo de potencia, cantidad de almacenamiento disponible o ancho de banda de transmisión hacia el segmento terreno. Es por ello que resulta crucial el empleo de algoritmos de compresión para minimizar el impacto que la adquisición de una imagen hiperespectral cause en el resto del sistema embarcado.

### 2.1. Concepto de imagen hiperespectral

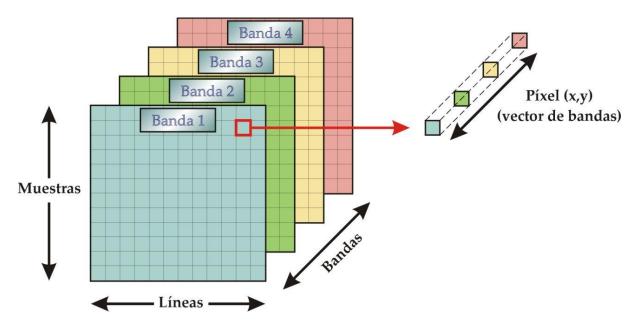

Una imagen hiperespectral es una imagen tomada a diferentes longitudes de onda en la que cada píxel representa la reflectancia de los materiales contenidos en ella. Por consiguiente, si se toman distintas imágenes a diferentes longitudes de onda, cada píxel se encontrará representado no por un único valor, como ocurre en una imagen en blanco y negro, sino por un vector de valores espectrales con la contribución de la luz detectada en ese punto para cada banda en el espectro. De esta forma, una imagen hiperespectral estará formada por un número finito de bandas que puede ir desde las decenas hasta los varios centenares de bandas dependiendo del sensor hiperespectral empleado.

A la hora de representar este tipo de imágenes se emplea, comúnmente, un cubo, denominado hipercubo o cubo hiperespectral, cuyas dos primeras dimensiones representarían la ubicación en el espacio de un píxel determinado de la imagen y una tercera dimensión que representaría la longitud de onda a la que ha sido tomada la

imagen. La Figura 2.1, muestra un ejemplo de representación del cubo hiperespectral para una imagen con 4 bandas.

Figura 2.1. Imagen hiperespectral (cubo hiperespectral)

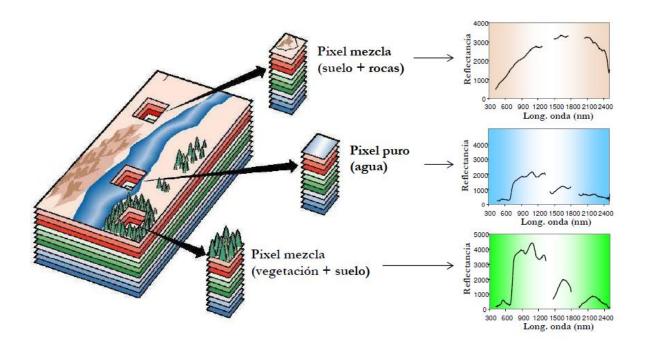

Por su naturaleza, un fenómeno característico de este tipo de imágenes es la presencia de varios tipos de píxeles según su composición en una misma banda a nivel sub-píxel. Existen píxeles llamados píxeles puros en los que únicamente existe la presencia de un único material y píxeles mezcla que contienen distintos materiales [13]. Este fenómeno es producido por la insuficiente resolución espacial de los sensores hiperespectrales para separar materiales espectralmente puros.

Generalmente, la mayoría de los píxeles presentes en una imagen son píxeles mezcla, ya que, independientemente de la escala que se considere, la mezcla se produce a nivel microscópico [14] [15]. En la Figura 2.2, se presenta una imagen hiperespectral en la que se puede observar píxeles puros y mezclas extraídos.

Figura 2.2. Imagen hiperespectral - Tipos de píxeles

### 2.2. Algoritmos de compresión de imágenes hiperespectrales

Las imágenes hiperespectrales son generalmente capturadas y almacenadas a bordo en un satélite o en una aeronave para, posteriormente, ser transmitidas hacia la estación terrena. Los instrumentos de alta resolución, presentes y futuros, embarcados en misiones espaciales para la adquisición de este tipo de imágenes, contribuyen a hacer necesario que las unidades de procesamiento de datos a bordo sean capaces de gestionar la inmensa cantidad de datos generados. Las limitaciones existentes a bordo en cuanto al ancho de banda disponible para el envío de las imágenes hiperespectrales y la capacidad para el almacenamiento de las mismas concluyen que, en líneas generales, se requiera de la aplicación de algoritmos de compresión de imágenes con el fin de reducir la cantidad de datos almacenados y transmitidos hacia el segmento terreno.

Tal y como se define en el capítulo 1, en cuanto a la clasificación de los algoritmos de compresión de imágenes hiperespectrales, típicamente, se establecen dos categorías, los algoritmos de compresión sin pérdidas y los algoritmos de compresión con pérdidas.

### 2.2.1. Algoritmos de compresión sin pérdidas (lossless compression)

La compresión de imágenes hiperespectrales sin pérdidas ha estado basada generalmente en el paradigma de la codificación predictiva, en donde cada pixel es predicho mediante datos anteriormente procesados y en donde el error de predicción se codifica entrópicamente [16] [17]. En [18] se introduce el concepto de predicción difusa, en donde se sustituye el predictor por un set predefinido empleando reglas de lógica difusa. En [19] se mejora la predicción mediante el uso del análisis de bordes. En [20] la predicción mediante el empleo de clasificadores proporciona un algoritmo de compresión casi sin pérdidas. La compresión mediante el empleo de clasificadores se desarrolla en mayor profundidad en [21] para compresiones tanto sin pérdidas como casi sin pérdidas. En [22] se emplea el concepto de cuantificación vectorial mientras que en [23] introduce clustering diferencial como base para la codificación proporcionando el concepto C-DPMC (Clustered Differential Pulse Code Modulation). En este algoritmo, el espectro de la imagen es agrupado (clustered), el predictor es formado para cada clúster y usado para decorrelar el espectro de la imagen. En [24] se introduce el concepto de emplear imágenes previamente procesadas, en el caso de este algoritmo dos, para formar el predictor espectral.

Una vez presentados los algoritmos más representativos de los estudiados en el Estado del Arte para la compresión de imágenes hiperespectrales sin pérdidas se desarrolla, en la siguiente sección, el estándar recomendado por el CCSDS (Consultative Committee for Space Data Systems). Este novedoso estándar, publicado en Mayo de 2012, representa el consenso técnico de las agencias participantes en el CCSDS. El CCSDS se postula como la agencia de referencia para organismos tales como la ESA (European Space Agency) a la hora de adoptar sus estándares en sus diseños y requerimientos.

## 2.2.1.1. CCSDS 123.0-B-1 Lossless Multispectral & Hyperspectral Image Compression [8]

El propósito de este estándar es establecer un algoritmo de compresión de datos aplicado al hipercubo tridimensional que forman las imágenes multiespectrales e hiperespectrales adquiridas por los instrumentos situados en la carga útil. Asimismo, especifica el formato de los datos comprimidos [8].

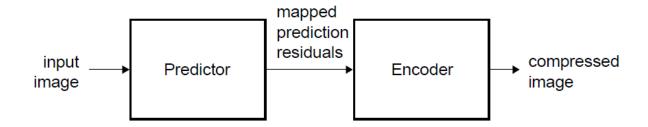

El compresor propuesto lo constituyen dos bloques funcionales representados en la Figura 2.3. Como se puede observar, han sido denominados como predictor y codificador.

Figura 2.3. Esquema del compresor

### Predictor

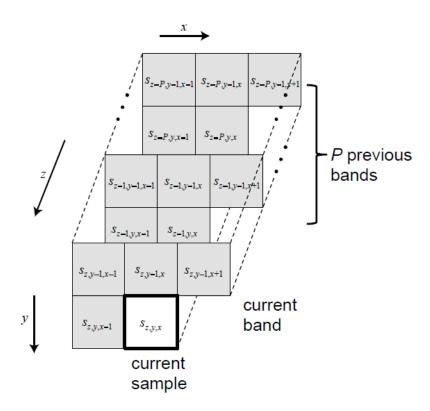

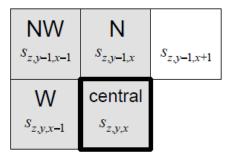

El predictor es el módulo encargado del cómputo del set de valores de muestras predichas,  $\hat{s}_{z,x,y}$ , y el mapeo de los residuos predichos,  $\delta_{z,x,y}$ , a partir de las muestras de la imagen de entrada,  $s_{z,x,y}$ . La etapa de predicción puede realizarse en un único pase a través de la imagen. La predicción de la muestra  $s_{z,x,y}$ , es decir, el cómputo de  $\hat{s}_{z,x,y}$  y  $\delta_{z,x,y}$ , depende, en general, de los valores de las muestras vecinas en la banda actual y en las P bandas anteriores, donde  $0 \le P \le 15$  es un valor a especificar por parte del usuario. La Figura 2.4, ilustra la disposición típica de la vecindad de las muestras usadas para la predicción. Nótese que para y = 0, x = 0, x =  $N_x$  - 1 o z < P la vecindad es consecuentemente truncada.

Figura 2.4. Vecindad, disposición típica

Dentro de cada banda espectral, el predictor computa una suma local,  $\sigma_{z,x,y}$ , de las muestras de valores vecinos. Cada suma local es empleada para calcular la diferencia local. El valor de la muestra predicha se calcula empleando la suma local de la banda espectral actual y una suma ponderada de la diferencia local de la banda actual y las P bandas espectrales anteriores. Los pesos empleados son adaptativamente actualizados. Cada residuo predicho, es decir, la diferencia entre una muestra  $s_{z,x,y}$  dada y su correspondiente valor predicho  $\hat{s}_{z,x,y}$ , se mapea en un entero sin signo denominado  $\delta_{z,x,y}$ .

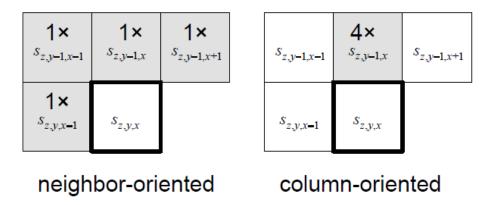

Existen varias técnicas, elegibles por parte de usuario, a la hora de seleccionar las muestras vecinas para el cómputo de la suma local. La Figura 2.5 muestra las predicciones denominadas *neighbor-oriented* y *column-oriented*.

Figura 2.5. Muestras usadas para el cálculo de las sumas locales

Se definen las siguientes ecuaciones para el cómputo de ambas técnicas para el cálculo de la suma local:

Neighbor-oriented

$$\sigma_{z,y,x} = \begin{cases} s_{z,y,x-1} + s_{z,y-1,x-1} + s_{z,y-1,x} + s_{z,y-1,x+1}, & y > 0, 0 < x < N_x - 1 \\ 4s_{z,y,x-1}, & y = 0, x > 0 \\ 2(s_{z,y-1,x} + s_{z,y-1,x+1}), & y > 0, x = 0 \\ s_{z,y,x-1} + s_{z,y-1,x-1} + 2s_{z,y-1,x}, & y > 0, x = N_x - 1 \end{cases}$$

Column-oriented

$$\sigma_{z,y,x} = \begin{cases} 4s_{z,y-1,x}, & y > 0\\ 4s_{z,y,x-1}, & y = 0, x > 0 \end{cases}$$

En cuanto al cómputo de la diferencia local, para cada banda espectral, el usuario puede escoger entre el modo reducido y el modo completo. La diferencia local central,  $d_{z,x,y}$ , es igual a la diferencia entre la suma local y cuatro veces el valor de la muestra  $s_{z,x,y}$ , en el

modo reducido. Bajo el modo completo, las tres diferencias locales direccionales,  $d_{z,x,y}^N$ ,  $d_{z,x,y}^N$ , son iguales a la diferencia entre  $\sigma_{z,x,y}$  y cuatro veces el valor de las muestras denominadas N, W, NW en la Figura 2.6.

Figura 2.6. Cómputo de las diferencias locales en cada banda espectral

Las siguientes ecuaciones definen el cálculo de la diferencia local en cada caso:

Diferencia local central

$$d_{z,y,x} = 4s_{z,y,x} - \sigma_{z,y,x}$$

Diferencias locales direccionales

$$\begin{split} d_{z,y,z}^{N} &= \begin{cases} 4s_{z,y-1,x} - \sigma_{z,y,x}, & y > 0 \\ 0, & y = 0 \end{cases} \\ d_{z,y,z}^{W} &= \begin{cases} 4s_{z,y,x-1} - \sigma_{z,y,x}, & x > 0, y > 0 \\ 4s_{z,y-1,x} - \sigma_{z,y,x}, & x = 0, y > 0 \\ 0, & y = 0 \end{cases} \\ d_{z,y,z}^{NW} &= \begin{cases} 4s_{z,y-1,x-1} - \sigma_{z,y,x}, & x > 0, y > 0 \\ 4s_{z,y-1,x} - \sigma_{z,y,x}, & x = 0, y > 0 \\ 0, & y = 0 \end{cases} \end{split}$$

### Codificador

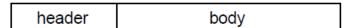

Este módulo es el encargado de componer el bit-stream de la salida. Éste se encuentra compuesto por una cabecera seguida por el cuerpo del mismo, tal y como se muestra en la Figura 2.7. La cabecera se encuentra compuesta por el metadato de la imagen, metadato del predictor y metadatos del codificador. El cuerpo consiste en la codificación sin pérdidas de los residuos predichos mapeados,  $\delta_{z,x,y}$ , del predictor.

Figura 2.7. Estructura de la imagen comprimida

El usuario puede escoger, para la codificación de los residuos mapeados, el uso de la codificación entrópica sample-adaptative o la aproximación block-adaptative. La aproximación sample-adaptative consigue tamaños de imágenes comprimidas menores que la aproximación block-adaptative [25].

Bajo la aproximación de codificación entrópica sample-adaptative, cada residuo mapeado predicho se codifica mediante el uso de una palabra de código binaria de longitud variable. Los códigos de longitud variable son seleccionados adaptativamente en base a estadísticas que son actualizadas tras la codificación de cada muestra. Se mantienen estadísticas separadas para cada banda.

Por otra parte, en la aproximación de codificación entrópica *block-adaptative*, la secuencia de residuos mapeados predichos se dividen en bloques de pequeño tamaño, y el método de codificación usado se selecciona independientemente y adaptativamente en cada bloque. Dependiendo del orden de codificación, los residuos mapeados predichos en un bloque pueden ser seleccionados de la misma banda espectral o de una banda diferente. Por consiguiente, si se escoge este método, el tamaño de la imagen comprimida depende del orden de codificación.

### 2.2.2. Algoritmos de compresión con pérdidas (lossy compression)

Los algoritmos de compresión con pérdidas alcanzan mayores ratios de compresión que aquellos sin pérdidas a expensas de una pérdida de información durante el proceso. A pesar de la pérdida de calidad en la imagen reconstruida, este tipo de algoritmos son de gran utilidad especialmente cuando se requieren grandes ratios de compresión. Asimismo, en [1] se evalúa el efecto de dichas pérdidas en imágenes hiperespectrales para aplicaciones específicas tales como, la detección o clasificación de objetivos, mostrando que se pueden alcanzar grandes tasas de compresión con impactos menores con respecto a la funcionalidad objeto.

La importancia del estudio de la compresión con pérdidas queda asimismo reforzada por el hecho de que el CCSDS ha desarrollado y aprobado estándares de relevancia internacional en esta material, en donde se incluye el estándar descrito en la sección anterior para la compresión sin pérdidas de imágenes hiperespectrales y encontrándose actualmente en

fase de definición de un estándar para la compresión de imágenes hiperespectrales con pérdidas.

Existen, en la literatura, numerosos algoritmos desarrollados para la compresión con pérdidas de imágenes hiperespectrales, muchos de ellos resultan generalizaciones de algoritmos existentes para la compresión de imágenes en 2D o algoritmos para la compresión de vídeo. En [26] se propone un algoritmo basado en el estándar JPEG2000 con un decorrelador espectral. En [1] [9] se introduce la transformada de Karhumen-Loève para la compresión del cubo hiperespectral. La transformada mediante wavelets y la descomposición de Tucker se aplican en [27]. Una visión diferente se propone en [28], donde se aplican las técnicas empleadas en el estándar de compresión de video H.264/AVC para la compresión del hipercubo espectral consiguiéndose resultados significativos en términos de tasa de bit - distorsión introducida. Estos algoritmos de compresión presentan unas necesidades en cuanto a memoria de almacenamiento y capacidad de cómputo disponible a bordo resultando demasiado complejos para una misión de larga duración.

Recientemente, se ha formado un nuevo paradigma basado en algoritmos de baja complejidad [10]. Esta técnica se basa en una primera etapa de predicción, una cuantificación, optimización tasa de bits-distorsión y codificación entrópica. Aprovecha la simplicidad y las altas prestaciones de los algoritmos de compresión basados en la predicción empleando pocos accesos a memoria. Asimismo, el empleo de la cuantificación y la optimización tasa de bits-distorsión asegura una tasa de compresión elevada. Así, en la siguiente sección se describe este algoritmo de compresión con pérdidas seleccionado para su implementación en este Trabajo de Fin de Máster.

### 2.2.2.1. Lossy Compression for Exomars (LCE) Algorithm

El algoritmo de compresión de imágenes hiperespectrales LCE [10], ha sido diseñado con el fin de poder ser desplegado a bordo de un satélite alcanzando altos ratios de compresión. Los objetivos principales en su desarrollo han sido, baja complejidad, resistencia a errores y fácilmente implementable a nivel hardware. A grandes rasgos, el algoritmo consiste en un predictor seguido por un codificador entrópico Golomb potencia de 2.

Con el fin de proporcionar al algoritmo de robustez frente a errores, el algoritmo codifica de manera independiente bloques de imagen de 16 x 16 píxeles. De esta forma, cada bloque es individualmente comprimido con lo que un error en un bloque dado no se propaga al resto de bloques. Asimismo, ha sido diseñado para que su implementación hardware sea fácilmente paralelizable permitiendo mayores prestaciones a sensores con altas tasas de datos.

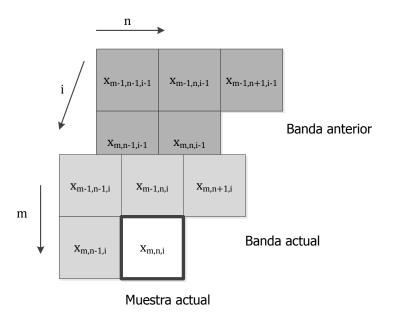

#### Predictor

El algoritmo comprime bloques espaciales independientes no solapados de tamaño 16 x 16 píxeles para todas las bandas del cubo hiperespectral. Sea  $x_{m,n,i}$  el píxel perteneciente a una imagen hiperespectral en la fila m, columna n y banda i. La Figura 2.8, muestra la ubicación del píxel a codificar y de la vecindad que lo rodea.

Figura 2.8. Localización de la muestra actual y su vecindad

En la primera banda (i=0), se aplica una compresión denominada 2D (modo INTRA) en la que no se emplea información de ninguna otra banda. Las muestras son procesadas de izquierda a derecha y de arriba hacia abajo, *raster scan order*. En general, el predictor empleado para esta banda es el presentado en la siguiente expresión.

$$\tilde{x}_{m,n,0} = (\hat{x}_{m-1,n,0} + \hat{x}_{m.n-1,0}) \gg 1$$

Donde  $\tilde{x}$  representa al predictor,  $\hat{x}$  el valor del píxel reconstruido y >> representa el desplazamiento de un bit hacia la derecha. Por lo tanto, el predictor para la primera banda se basa en la media de los píxeles vecinos (encima e izquierda) del pixel a predecir. Nótese que el primer píxel no es predicho, los píxeles en la primera fila, es decir, m=0, son predichos mediante la siguiente expresión  $\tilde{x}_{0,n,0}=\hat{x}_{0,n-1,0}$  y los píxeles en la primera columna, n=0, se predicen como  $\tilde{x}_{m,0,0}=\hat{x}_{m-1,0,0}$ .

Para el resto de bandas,  $i \neq 0$ , las muestras  $x_{m,n,i}$  se predicen mediante las muestras decodificadas,  $\hat{x}_{m,n,i-1}$ , es decir, mediante las muestras del mismo bloque en la banda

anterior. Se computa sobre el bloque un estimador LMS (*Least Mean Square*) definido como  $\alpha = \frac{\alpha_N}{\alpha_D}$ , siendo  $\alpha_N$  y  $\alpha_D$ :

$$\propto_N = \sum_{m,n} (\hat{x}_{m,n,i-1} - m_{i-1})(x_{m,n,i} - m_i)$$

$$\propto_D = \sum_{m,n} (\hat{x}_{m,n,i-1} - m_{i-1}) (x_{m,n,i-1} - m_{i-1})$$

Donde,  $m_i$  y  $m_{i-1}$  son las medias, dentro del conjunto de números enteros, computadas de los bloques anteriores decodificados en las bandas i e i-1.

$$m_{i/i-1} = round\left(\frac{1}{P}\sum_{m,n} x_{m,n,i/i-1}\right)$$

En la ecuación anterior P se define como el número de muestras computadas en el bloque actual.

Las versiones cuantificadas de  $\propto$  y  $m_i$ , denominadas  $\widehat{\propto}$  y  $\widehat{m}_i$ , se generan mediante el empleo de un cuantificador escalar. Finalmente, los valores de las muestras predichas se calculan para todas las muestras pertenecientes a un bloque como:

$$\widetilde{x}_{m,n,i} = \widehat{m}_i + \widehat{\propto} \left( \widehat{x}_{m,n,i-1} - m_{i-1} \right)$$

Por consiguiente, el error de predicción se calcula mediante la siguiente expresión:

$$e_{m,n,i} = x_{m,n,i} - \tilde{x}_{m,n,i}$$

#### Optimización tasa de bits-distorsión

Antes de proceder a la cuantificación del error de las muestras predichas, se verifica si el valor de la predicción se aproxima al valor real del pixel, permitiendo de esta forma evitar la codificación de las muestras de error. Si este es el caso, se fija al valor '1' lógico un flag que indica que el bloque actual de muestras de errores de predicción es cero. Esta condición se denomina, zero\_block condition. Para la toma de esta decisión, se computa la energía del error de predicción mediante la siguiente expresión:

$$D_0 = \frac{1}{256} \sum_{m,n} e_{m,n,i}^2$$

Si  $D_0$  es menor que el umbral definido  $D_T$ , es decir,  $D_0 < D_T$ , se aplica la condición  $zero\_block$ .

### Cuantificación y mapeo

Las muestras de los errores de predicción son cuantificadas en valores enteros,  $eq_{m,n,i}$ , para, posteriormente, ser decuantificadas a valores reconstruidos,  $er_{m,n,i}$ . Dentro de la primera banda, y=0, este proceso se realiza pixel a pixel empleando un cuantificador escalar uniforme. Para el resto de bandas,  $y\neq 0$ , es posible escoger entre el cuantificador escalar uniforme y el cuantificador de umbral uniforme, UTQ (*Uniform-threshold Quantizer*) presentado en [29]. Finalmente, los valores reconstruidos son mapeados a números enteros no negativos empleando la siguiente aproximación.

$$Sm, n, i = \begin{cases} 2|eq_{m,n,i}| - 1, si \ eq_{m,n,i} > 0 \\ 2|eq_{m,n,i}| &, si \ eq_{m,n,i} \le 0 \end{cases}$$

### Cuantificación y mapeo

El bloque de 16 x 16 residuos se codifican, en *raster scan order*, empleando la codificación Golomb potencia de 2, exceptuando la primera muestra de cada bloque. Éste, se codifica empleando un código Golomb exponencial potencia de 0. La primera muestra cuantificada de la primera banda no se codifica, por lo tanto, se almacena en la imagen comprimida usando 16 bits.

### Formato del fichero de salida

El bit-stream comprimido a la salida se encuentra compuesto por la concatenación de bloques codificados. Éstos han de ser leídos espacialmente en  $raster\ scan\ order$ . Cada bloque es codificado para todas las bandas. En cuanto a la información de salida escrita en el archivo comprimido para todos los bloques se tiene: a) para todas las bandas salvo la primera, los parámetros  $\propto$  y m; b) un bit correspondiente al indicador  $zero\_block\ condition$ ; c) para aquellos bloques en los que no se de la condición  $zero\_block\ nuestras\ de\ error\ de\ predicción\ cuantificadas\ de\ cada\ bloque\ escritas\ en\ raster\ scan\ order.$

```

block_0 [BAND0 \rightarrow encoded pred error;

BAND1\rightarrow \propto + \mu + zero_block flag + encoded pred error]

block_1 ... block_N

```

Figura 2.9. Formato del fichero comprimido generado por el algoritmo LCE

### 3. Desarrollo de la arquitectura implementada

Este tercer capítulo de la memoria se centra en la descripción del trabajo realizado en el presente Trabajo Fin de Máster. Se aborda en primer lugar el diseño a nivel de software del algoritmo *Lossy Compression for Exomars* (LCE) describiendo los módulos que lo componen, flujos de datos y consideraciones a la hora de separar en módulos independientes dicho código de referencia. Posteriormente, se presentan los trabajos realizados en la herramienta de síntesis Catapult C para la obtención del código VHDL a nivel RTL sintetizable. Finalmente, se presenta el módulo de control hardware diseñado en VHDL, implementado y verificado que permite la conexión de los módulos independientes del algoritmo.

### 3.1. Implementación del algoritmo LCE en el software de referencia

El software proporcionado [30] implementa el algoritmo en lenguaje ANSI C operando sobre cada bloque independiente de  $16 \times 16$  píxeles de la imagen hiperespectral de entrada de forma secuencial, es decir, bloque a bloque. Cada bloque se procesa conjuntamente con todas sus bandas espectrales, antes de que el siguiente bloque sea procesado.

La imagen hiperespectral de entrada es almacenada en un buffer de memoria denominado data de tipo entero. Durante el procesamiento de cada bloque, sus muestras son almacenadas en un buffer de menor tamaño, 256 posiciones de 16 bits, denominado curr\_block. El bloque usado como referencia a la hora de realizar la predicción se copia de igual forma en el buffer denominado ref\_block (256 x 16 bits) Las palabras código de salida del algoritmo se almacenan en el buffer de salida denominado block\_out (256 x 32 bits).

Asimismo, se incluyen tres variables que proporcionan información relevante a la hora realizar las escrituras en el buffer de salida. La variable pp almacena temporalmente los datos codificados y comprimidos. Cada vez que una nueva palabra de código es generada se almacena, temporalmente, en esta variable hasta que sus 32 bits sean escritos. Una vez se llene este buffer por la escritura de sus 32 bits, la palabra resultante se escribe en el buffer de salida block\_out. El número actual de bits escritos en la variable pp es controlado por la variable denominada m. Finalmente, la variable filecount indica el número de palabras de 32 bits escritas en el buffer de salida block\_out. Durante la codificación de cada banda este valor es actualizado, fijándose nuevamente a su valor inicial de '0' lógico al inicio de cada banda.

El estudio del software de referencia, ha permitido la extracción de los estímulos y así como la verificación de resultados en la etapa de verificación de la implementación del algoritmo. Los estímulos serán las entradas al banco de pruebas (*testbench*) diseñado y su salida será posteriormente comparada con los resultados proporcionados por el código de referencia.

En este punto cabe destacar que, el código de entrada en este Trabajo Fin de Máster contiene las siguientes modificaciones implementadas en [11] que facilitan su implementación a nivel hardware. Nótese que en [11] se evalúa el impacto de estas modificaciones sobre el código original no hallándose diferencias significativas entre el código inicial de referencia y el código a la salida de [11].

Como paso inicial en [11] se aisló en el código la parte del algoritmo que se implementaría a nivel hardware de lo que formaría parte del banco de pruebas. En este punto, se introdujeron tipos de datos con precisión a nivel de bit. Para ello, se emplearon datos de tipo Algorithmic C. De esta forma, la función denominada pred1block() contiene los módulos objeto de la implementación. La Figura 3.1, muestra en pseudo-código la estructura de la función pred1block().

Figura 3.1. Pseudo-código de la función pred1block()

Por otra parte, se redujo el número de operaciones matemáticas realizadas mediante el empleo de operadores lógicos tales como, el desplazador, funciones and/or, cuando resultó posible. Además la división entera propuesta para el cálculo del parámetro de ganancia del predictor  $\propto$ , fue sustituida por una búsqueda dicotómica. En la misma línea, se eliminaron y minimizaron las operaciones de lectura/escritura en los buffers de entrada/salida.

En cuanto a la llamada a funciones, se introdujeron en el código aquellas necesarias para la implementación hardware del algoritmo. Finalmente, se optimizaron con vistas a su implementación hardware los bucles empleados en el algoritmo.

## 3.2. Separación del código de referencia en módulos funcionalmente independientes

Como primer paso a la hora de abordar la implementación del algoritmo LCE, a partir del código de referencia proporcionado, se ha decidido dividir el mismo en módulos funcionalmente independientes. Para ello, se han identificado en el código de referencia aquellas funciones o sentencias de código asociadas a cada a cada una de las etapas del algoritmo LCE. Como salidas de esta tarea dispondremos de dos ficheros para cada módulo independiente, un fichero con extensión .cpp que contiene el cuerpo de cada función y un fichero con extensión .h que contiene las cabeceras de las funciones empleadas.

El objetivo de esta primera etapa es el de obtener módulos funcionalmente independientes que sirvan de entrada a la herramienta Catapult C. La idea principal que subyace bajo esta aproximación es la de conocer dentro de cada módulo su ruta crítica para así poder conocer los módulos con una mayor carga computacional asociada.

Los ficheros de salida correspondientes a módulos funcionalmente independientes son los que se citan a continuación:

- adgolomb.cpp y adgolomb.h

- calc\_perr.cpp y calc\_perr.h

- estimationls.cpp y estimationls.h

- init\_output.cpp y init\_output.h

- mean.cpp y mean.h

- pred\_2D.cpp y pred\_2D.h

- write\_alphamu.cpp y write\_alphamu.h

- zero\_block.cpp y zero\_block.h

Los siguientes apartados presentan cada uno de los módulos ANSI C independientes obtenidos describiendo su funcionalidad e interfaces de entrada/salida.

Dentro del desarrollo de esta tarea, se analizan cada una de las entradas/salidas resultantes de los módulos independientes con el fin de servir como entradas a las siguientes etapas del trabajo realizado. Resulta fundamental este análisis ya que las entradas o salidas que se definan se convertirán posteriormente en puertos de entrada, de salida o bidireccionales en el lenguaje de descripción hardware VHDL.

A nivel de código, la función pred1block() presenta, una vez finalizada esta tarea, la implementación mostrada en la Figura 3.2. Como puede observarse, sólo existen llamadas a funciones o decisiones a nivel de control. En ellas se decide la llamada o no de una función dada.

```

void pred1block(ac_int<16, true> cur_block[256], ac_int<16, true> ref_block[256],

int bx, ac_int<6, false> *m, ac_int<32, false> *pp,

ac_int<32, false> *filecount, ac_int<32, true> block_out[256],

ac_int<22, true> *ym){

ac_int<9, false> alpha, a_i = 0;

ac_int<9, false> j = 0;

ac_int<1, false> k0 = 1;

ac_int<1, false> INTRA =0;

ac_int<22, true> xm = 0;

ac_int<17, true> p_err[256];

ac_int<18, true> pred[256];

/*created to make cur block only input ++ parallelizing ++ memory*/

ac int<16, true> aux cur block[256];

ac int<32, false> D0 = 0;

if(bx == 0) INTRA = 1;

else INTRA = 0;

init_output (filecount, block_out);

if (INTRA){

// 2D Prediction of the block

xm = pred_2D(cur_block, ref_block, scan, m, pp, block_out, filecount,

INTRA, ym);

}

else{

//Calculate MEAN of current block

xm = mean (cur_block);

//Estimate, quantize and dequantize alpha

estimation_ls(cur_block, aux_cur_block, ref_block, &alpha, scan, &a_i,

xm, ym);

//Rate-distortion optimization & prediction error

D0 = calc_perr (p_err, pred, alpha, ref_block, aux_cur_block);

if(D0 > 0) k0 = 1; /*Zero-block option not selected-1 bit size*/

else k0 = 0; /*Zero-block option selected*/

// Output update with alpha and xm

write_alphamu (xm, a_i, k0, m, pp, block_out, filecount);

if(k0 == 0){

//If zero-block, decoded block is identical to the predictor

zero_block (ref_block, pred, xm);

else if (k0 == 1){

//Entropy coder

ad_golomb_code_perr(p_err, m, pp, block_out, filecount, INTRA,

ref_block, pred, xm);

} /* end of else for bands other than first */

} // end of pred1block

```

Figura 3.2. Código ANSI C de la función pred1block()

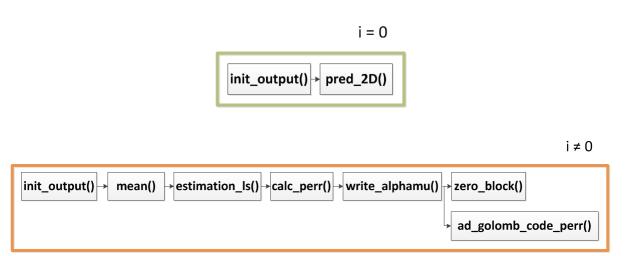

La Figura 3.3, presenta el flujo de datos y las dependencias entre los mismos resultado de la implementación de estas modificaciones en el código de referencia. Se observa que la primera banda, i=0, es procesada de forma distinta al resto de bandas, tal y como se define a nivel teórico en el algoritmo LCE.

Figura 3.3. Flujos de datos

Cabe destacar que, durante la realización de esta tarea se ha verificado en todo momento que las modificaciones introducidas en el código de referencia no afectan al funcionamiento del algoritmo LCE, esto es, el código ANSI C obtenido como salida de esta tarea es funcionalmente equivalente al código de referencia. Esta verificación se ha realizado mediante la comparación entre la imagen comprimida tras las modificaciones realizadas y una imagen comprimida con anterioridad mediante el uso del software de referencia con las modificaciones aportadas en [11].

### 3.2.1. Módulo adgolomb.cpp

En el interior de este módulo se han incluido las funcionalidades siguientes:

- Realizar la cuantificación del error de predicción

- Cómputo del bloque de referencia, es decir, los valores reconstruidos, que han de estar disponibles para la siguiente banda

- Implementar la codificación entrópica del error de predicción

- Realizar el empaquetado a nivel de bit de las palabras código resultantes de la compresión

Las conexiones de entrada y salida relacionadas con el módulo adgolomb.cpp extraídas del código resultante se pueden dividir en tres grupos: control y datos.

Los parámetros de control permiten identificar los elementos necesarios para la gestión del módulo, mientras que, el grupo de datos se refiere a valores de píxel. Ambos se encuentran referidos a un bloque y se pueden observar en la Tabla 3.1.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                     |

|---------|-----------|-----|---------------|-------------------------------------------------|

| CONTROL | m         | 1/0 | 6 bits        | Número de bits escritos en pp                   |

|         | рр        | I/O | 32 bits       | Buffer intermedio de valores codificados        |

|         | filecount | I/O | 32 bits       | Número de palabras escritas en<br>data_out      |

|         | INTRA     | I   | 1 bit         | Indicador de predicción 2D                      |

|         | xm        | I   | 22 bits       | Valor medio de los píxeles del<br>bloque actual |

| DATOS   | dat       | I   | 256 x 17 bits | Array de errores de predicción                  |

|         | data_out  | 0   | 256 x 32 bits | Array de palabras código                        |

|         | ref_block | 0   | 256 x 16 bits | Array de valores reconstruidos                  |

|         | pred      | ı   | 256 x 18 bits | Array de valores predichos                      |

Tabla 3.1. Interfaz del módulo adgolomb.cpp

### 3.2.2. Módulo calc\_perr.cpp

En este modulo, se computan tanto el predictor como el error de predicción teniendo en cuenta el valor del parámetro  $\propto$  decuantificado. Asimismo, retorna el estimador LMS (D0) con lo que a la salida de este módulo puede decidirse si la condición  $zero\_block$  es empleada.

En cuanto a entradas/salidas del módulo se agrupan de la misma forma que en la sección anterior, esto es, en control y datos. Así, la Tabla 3.2, presenta la interfaz de este módulo.

| Grupo   | Parámetro     | I/O | Tamaño        | Descripción                           |

|---------|---------------|-----|---------------|---------------------------------------|

| CONTROL | alpha         | I   | 9 bits        | Valor decuantificado de ∝             |

|         | DO            | 0   | 41 bits       | Valor energía del error de predicción |

| DATOS   | p_err         | 0   | 256 x 17 bits | Array de errores de predicción        |

|         | aux_cur_block | I   | 256 x 32 bits | Array auxiliar del bloque actual      |

|         | ref_block     | I   | 256 x 16 bits | Array de valores reconstruidos        |

|         | pred          | 0   | 256 x 18 bits | Array de valores predichos            |

Tabla 3.2. Interfaz del módulo calc\_perr.cpp

### 3.2.3. Módulo estimationls.cpp

El cálculo de los parámetros  $\alpha_N$  y  $\alpha_D$ , además del propio  $\alpha$ , se incluyen en este módulo. La resta del valor medio del bloque actual y el bloque de referencia también ha sido incluida en el módulo.

Por otra parte, el cómputo del valor cuantificado de  $\propto$  mediante una búsqueda dicotómica se añade como parte de este módulo. Finalmente, antes de retornar de la función, se calcula el valor decuantificado del parámetro  $\propto$ .

La interfaz de este módulo se presenta en la Tabla 3.3, en donde se observa la agrupación entre control y datos de los parámetros.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                       |

|---------|-----------|-----|---------------|---------------------------------------------------|

| CONTROL | xm        | I   | 22 bits       | Valor medio de los píxeles del<br>bloque actual   |

|         | ym        | 1/0 | 22 bits       | Valor medio de los píxeles del<br>bloque anterior |

|         | ax        | 0   | 9 bits        | Valor de cuantificado de ∝                        |

|         | alpha     | 0   | 9 bits        | Valor decuantificado de ∝                         |

| DATOS   | scan      | I   | 64 x 8 bits   | Índices a procesar en el bloque<br>actual         |

|         | cur_block | I   | 256 x 16 bits | Array de valores del bloque actual                |

|         | Z         | 1/0 | 256 x 16 bits | Array auxiliar del bloque actual                  |

|  | t | 0 | 256 x 16 bits | Array de valores reconstruidos |

|--|---|---|---------------|--------------------------------|

|--|---|---|---------------|--------------------------------|

Tabla 3.3. Interfaz del módulo estimation1s.cpp

### 3.2.4. Módulo init\_output.cpp

Este módulo es el encargado de la inicialización a 0xFFFFFFFF de las primeras 128 posiciones del buffer de palabras código de salida del algoritmo. En la Tabla 3.4 se representa la interfaz del módulo.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                 |

|---------|-----------|-----|---------------|---------------------------------------------|

| CONTROL | filecount | I   | 32 bits       | Número de palabras escritas en<br>block_out |

| DATOS   | block_out | 0   | 256 x 32 bits | Array de palabras código                    |

Tabla 3.4. Interfaz del módulo init\_output.cpp

### 3.2.5. Módulo mean.cpp

El valor medio de las muestras pertenecientes a una banda se computa en este módulo. Por lo tanto, la función retorna un valor entero de 22 bits con dicha media. La Tabla 3.5 presenta la interfaz perteneciente a este módulo.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                     |

|---------|-----------|-----|---------------|-------------------------------------------------|

| CONTROL | xm        | 0   | 22 bits       | Valor medio de los píxeles del<br>bloque actual |

| DATOS   | cur_block | I   | 256 x 16 bits | Array de valores del bloque actual              |

Tabla 3.5. Interfaz del módulo mean.cpp

### 3.2.6. Módulo pred\_2D.cpp

La predicción en dos dimensiones (2D), realizada para la primera banda, i=0, se implementa en este módulo. Asimismo, la codificación entrópica y el cómputo del valor medio de las muestras del bloque actual para ser utilizadas en la siguiente banda son implementados.

A nivel de interfaz, el módulo presenta los parámetros expuestos en la Tabla 3.6. En ella, pueden observase tanto los parámetros de control como de datos presentes en dicha interfaz.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                       |

|---------|-----------|-----|---------------|---------------------------------------------------|

| CONTROL | m         | 1/0 | 6 bits        | Número de bits escritos en pp                     |

|         | рр        | 1/0 | 32 bits       | Buffer intermedio de valores codificados          |

|         | filecount | I/O | 32 bits       | Número de palabras escritas en data_out           |

|         | INTRA     | I   | 1 bit         | Indicador de predicción 2D                        |

|         | xm        | 0   | 22 bits       | Valor medio de los píxeles del<br>bloque actual   |

|         | ym        | 0   | 22 bits       | Valor medio de los píxeles del<br>bloque anterior |

| DATOS   | cur       | I   | 256 x 17 bits | Array de errores de predicción                    |

|         | scan      | I   | 64 x 8 bits   | Índices a procesar en el bloque<br>actual         |

|         | ref       | 0   | 256 x 16 bits | Array de valores reconstruidos                    |

|         | data_out  | 0   | 256 x 32 bits | Array de palabras código                          |

Tabla 3.6. Interfaz del módulo pred\_2D.cpp

### 3.2.7. Módulo write\_alphamu.cpp

En este módulo se realiza la escritura en el buffer de palabras código del valor cuantificado de  $\propto$ , la media del bloque actual y el indicador de la condición zero\_block.

La Tabla 3.7, presenta la interfaz de este módulo, así como, la descripción de cada uno de estos parámetros.

| Grupo   | Parámetro | I/O | Tamaño  | Descripción                                     |

|---------|-----------|-----|---------|-------------------------------------------------|

| CONTROL | m         | 1/0 | 6 bits  | Número de bits escritos en pp                   |

|         | pp        | I/O | 32 bits | Buffer intermedio de valores codificados        |

|         | filecount | I/O | 32 bits | Número de palabras escritas en<br>data_out      |

|         | xm        | I   | 22 bits | Valor medio de los píxeles del<br>bloque actual |

|         | a_i       | I   | 9 bits  | Valor de cuantificado de ∝                      |

|       | k0       | I | 1 bits        | Indicador zero_block contidion |

|-------|----------|---|---------------|--------------------------------|

| DATOS | data_out | 0 | 256 x 32 bits | Array de palabras código       |

Tabla 3.7. Interfaz del módulo write\_alphamu.cpp

### 3.2.8. Módulo zero\_block.cpp

Si se activa la condición zero\_block, es decir, si el valor de la predicción se aproxima al valor real del pixel, se llama a esta función. Por lo tanto, se evitan tanto la cuantificación, la codificación entrópica y el empaquetado de las palabras código.

La interfaz del módulo se presenta en la Tabla 3.8.

| Grupo   | Parámetro | I/O | Tamaño        | Descripción                                     |

|---------|-----------|-----|---------------|-------------------------------------------------|

| CONTROL | xm        | 0   | 22 bits       | Valor medio de los píxeles del<br>bloque actual |

| DATOS   | pred      | I   | 256 x 18 bits | Array de valores predichos                      |

|         | ref_block | 0   | 256 x 16 bits | Array de valores reconstruidos                  |

Tabla 3.8. Interfaz del módulo zero\_block.cpp

### 3.3. Generación del lenguaje de descripción hardware VHDL

Catapult C [12] es una herramienta de sintetizado hardware de alto nivel. Se trata de un software comercial producido por Mentor Graphics, adquirido por la compañía Calypto Design Systems. Permite la utilización de código C/C++ y la generación de salidas RTL en código de descripción hardware VHDL y Verilog, entre otros, para la síntesis hardware de FPGAs y ASICs. Catapult C permite a los usuarios indicar las restricciones de tiempo y área indicando la frecuencia de reloj a utilizar y la tecnología de destino.

La utilización básica de Catapult no resulta complicada y sólo se requiere de la inserción de los archivos .cpp para iniciar el proceso. Posteriormente, Catapult C comprueba la corrección del código fuente. Una vez que el código es correcto, se continúa con la configuración del diseño, en donde se selecciona el dispositivo a sintetizar y la frecuencia de reloj que se quiere utilizar. El siguiente paso, Catapult genera las restricciones de la arquitectura seleccionada. Una vez finalizado este paso se pasa al organizador de la síntesis y para finalizar se realiza el paso de generación del lenguaje de descripción hardware RTL seleccionado.

Catapult C proporciona acceso a la herramienta Precision que permite realizar los pasos necesarios para la síntesis del código RTL generado. Gracias a que obtiene los datos necesarios del dispositivo seleccionado de Catapult C solo se ha de pulsar el botón de sintetizado para generara automáticamente todo el proceso.

Se debe destacar que, en determinados casos, los tiempos de generación del código RTL y de la síntesis posterior son muy prolongados pudiéndose necesitar días para la finalización de este proceso.

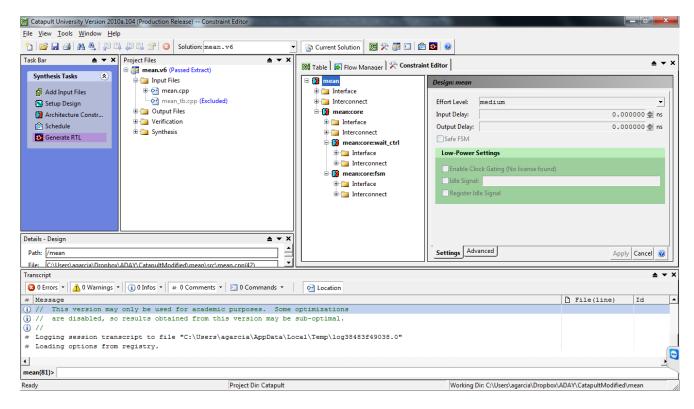

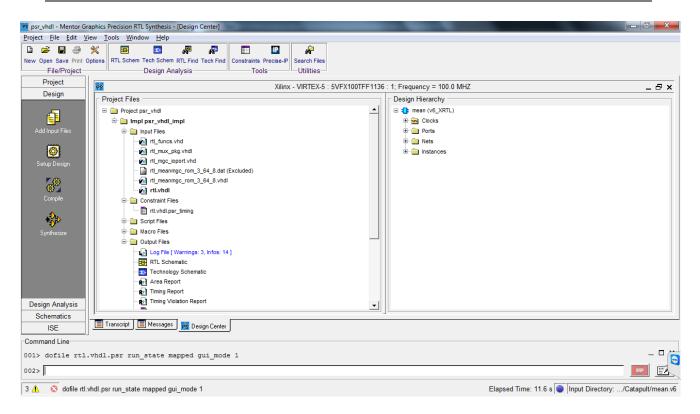

En la Figura 3.4 y Figura 3.5 se muestra el aspecto que presenta el programa Catapult C y Precision RTL Synthesis, empleada para el emplazamiento y ruteo.

Figura 3.4. Aspecto de la interfaz de la herramienta Catapult C

Figura 3.5. Aspecto de la interfaz de la herramienta Precision RTL Synthesis

# 3.3.1. Metodología de diseño en la herramienta Catapult C

En esta sección se presenta una breve descripción de la metodología de diseño que emplea la herramienta de síntesis Catapult C, para mayor información consultar [12]. Conocer esta metodología, así como en qué medida afecta un cambio en los parámetros escogidos en el hardware generado, resulta fundamental para poder realizar su integración en tareas posteriores.

### 3.3.1.1. Paso 1. Escritura y verificación del código C/C++

El algoritmo escrito, entrada a la herramienta, afecta al hardware resultante en mayor medida que cualquier otro paso en la metodología. Por lo tanto, la implementación de alto nivel del algoritmo debe hacerse cuidadosamente.

Es probable que, cualquier código escrito en C/C++ e introducido en la herramienta Catapult C genere un hardware en código VHDL o Verilog sintetizable. Sin embargo, los resultados que se obtendrán, en términos de latencia, área y transferencia de datos, probablemente, no cumplirán con los requisitos impuestos y, lo que es peor, será complicado cómo aumentar las prestaciones del sistema obtenido a partir de un código en C/C++ no escrito para ser usado en herramientas de síntesis de alto nivel.

En el caso de este Trabajo Fin de Máster, como ha quedado descrito, se parte de un código de referencia en ANSI C modificado para ser empleado en herramientas de síntesis de alto nivel. Asimismo, se han realizado las modificaciones necesarias con el fin de obtener módulos funcionalmente independientes.

### 3.3.1.2. Paso 2. Configuración de las restricciones hardware a nivel global

En este paso, se especifica, por parte del usuario, la frecuencia de reloj y la polaridad y presencia o ausencia de pines de control tales como *reset* y *enable*. Además, es en este paso donde se especifica la tecnología objeto de síntesis.

Por otra parte, se ha de especificar el módulo de más alto nivel (top module) de los comprendidos en la implementación. La herramienta, para el resto de funciones que sean llamadas desde el *top module*, creará su implementación hardware. Mientras que, aquellas que queden fuera se considerarán parte de banco de pruebas con lo que no formarán parte del diseño hardware generado.

## 3.3.1.3. Paso 3. Especificación de las restricciones arquitecturales

Catapult C proporciona abstracciones de alto nivel proporcionando grados de libertad al usuario con el fin de decidir la manera en que el diseño será implementado a bajo nivel. En este paso, las principales características disponibles son:

- Posibilidad de mapeo de arrays a recursos de memoria internos

- Decidir la forma en que se mapean las memorias en el diseño

- Parámetros para la optimización de bucles en el diseño. Los más relevantes son:

loop unrolling (U), permitiendo la eliminación del bucle expandiéndolo

completamente o dividiéndolo un número finito de veces, o loop pipelining,

permitiendo el comienzo de la segunda iteración antes de la finalización de la

anterior, esto se fija mediante la variable initialization interval (II)

- Identificación de entradas, salidas y recursos a nivel global (memorias ROMs, etc.)

- Gestión de las interfaces de entrada/salida

#### 3.3.1.4. Paso 4. Planificación del diseño

En este paso, Catapult C planifica el diseño hardware de acuerdo a las restricciones introducidas en los pasos 2 y 3. De forma gráfica proporciona un diagrama de Gantt en donde se representan las dependencias de datos existentes. De esta forma, el usuario obtiene una visión de cómo es planificado el diseño por la herramienta.

Asimismo, la herramienta proporciona información de utilidad con el fin de conocer cómo las restricciones impuestas en el paso 3 pueden ser optimizadas.

Por último, ya en este punto se obtienen estimaciones en cuanto a área, latencia y transferencia de datos.

### 3.3.1.5. Paso 5. Generación del RTL

Es en este paso donde la herramienta genera los ficheros RTL del diseño. Se generan, además del código RTL en VHDL o Verilog, esquemáticos por lo que es posible identificar la ruta crítica del diseño.

En cuanto a los ficheros generados cabe destacar que se disponen de dos tipos de descripciones de bajo nivel del diseño:

- cycle.vhdl, el cual contiene una descripción a nivel de comportamiento del diseño útil a la hora de realizar simulaciones

- rtl.vhdl, descripción de diseño sintetizable, es la que se debe usar en la síntesis del mismo

Tras la generación del código RTL, la herramienta proporciona un enlace directo a la herramienta Precision para realizar el emplazamiento y ruteo del diseño generado. Estimaciones con mayor detalle del área, latencia y transferencia de datos se proporciona a la salida de esta herramienta.

### 3.3.1.6. Flujo de verificación SCVerify

Complementariamente a la metodología de síntesis propuesta por Catapult C, existen una serie de flujos de verificación disponibles con el objetivo de garantizar el correcto comportamiento del código RTL generado.

De esta forma, el flujo de verificación SCVerify proporciona un entorno de trabajo para la validación de las salidas de Catapult C frente a la entrada original en C/C++ empleando un banco de pruebas proporcionado por el usuario en C/C++.

Estímulos idénticos se aplican tanto al diseño de alto nivel original y al código de bajo nivel generado mediante comparación se valida que las salidas de ambos diseños es idéntica.

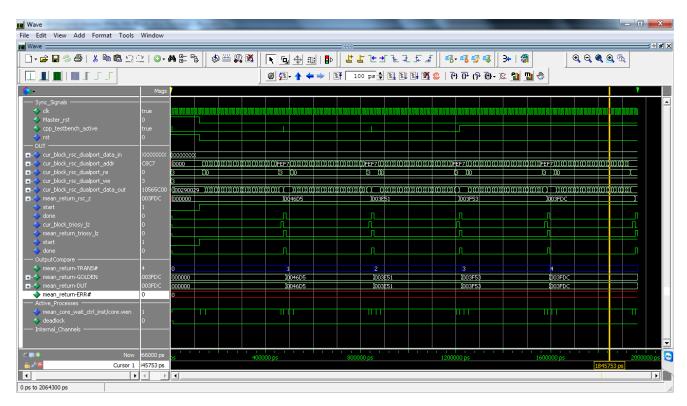

A lo largo de la realización de esta tarea se ha creado, para cada uno de los módulos funcionalmente independientes, un banco de pruebas con valores aleatorios con el fin de garantizar a nivel de simulación que los módulos generados por la herramienta proporcionan los mismos resultados a estímulos idénticos a la entrada. La Figura 3.6, representa el último paso ya en la herramienta de simulación y depuración ModelSim en donde se observa que el número de errores es nulo. Este proceso ha sido repetido para todos y cada uno de los módulos obtenidos.

Figura 3.6. Aspecto de la interfaz de la herramienta ModelSim tras su llamada mediante Catapult C

Esta verificación a nivel de bloque permite ir con una mayor seguridad a tareas posteriores en las que se verifica con estímulos extraídos del software de referencia el correcto funcionamiento de la implementación del algoritmo LCE.

## 3.3.2. Implementación de los módulos mediante la herramienta Catapult C

Una vez presentada, tanta la metodología de diseño empleada en la herramienta, como el flujo de verificación usado, se introduce, en esta sección, la implementación de los distintos módulos funcionalmente independientes obtenidos tras la ejecución de la tarea descrita con anterioridad.

La tecnología objeto de la implementación realizada con la herramienta es una FPGA de la familia Virtex-5 del fabricante XILINX. En concreto se ha empleado el modelo XC5FX100T con *speed grade* -1 y encapsulado FF1136.

Asimismo, se ha definido como objetivo, conseguir una frecuencia de funcionamiento por encima de los 75MHz para cada uno de los módulos.

La implementación de los módulos se ha realizado siguiendo la metodología descrita para la herramienta. A parte de las restricciones impuestas a nivel global, se han habilitado las siguientes señales a nivel de interfaz:

Señal start habilitada.

Señal activa a nivel alto. El módulo permanece a la espera de la activación de esta señal para comenzar su actividad.

Señal done habilitada.

Señal activa a nivel alto. Indica la finalización del procesado por parte del módulo. Éste permanece a la espera de una nueva señal de *start*.

Señal rst habilitada.

Señal activa a nivel alto. Inicializa las señales pertenecientes al módulo.

### 3.3.2.1. Implementación del módulo adgolomb.cpp

A nivel arquitectural, este módulo contiene un bucle principal denominado MAP. Asimismo, anidados dentro de éste, contiene tres bucles adicionales denominados abs\_adgolomb:for, find\_lead\_one:for y CALCK. Para el bucle principal se ha escogido para su pipeline II=1, mientras que los bucles adicionales han sido expandidos completamente, es decir U=1, con lo que su ejecución se ha paralelizado completamente. El bucle principal contiene 256 iteraciones mientras que el resto contiene 18 iteraciones para el bucle abs\_adgolomb:for, 18 iteraciones para el bucle find\_lead\_one:for y 22 iteraciones para el bucle CALCK. Notar que se han aplicado varias opciones de optimizaciones de bucles obteniéndose mejores resultados con las configuraciones que se comentan.

A nivel de interfaces, el bloque queda descrito en la Figura 3.7. En ella se observa que en cuanto a las entradas al módulo se han inferido dos memorias RAM, una de 256 x 17 bits para la variable de entrada dat y una de 256 x 18 bits para la variable pred, un registro de 22 bits para xm y uno de 1 bit para INTRA. Además, las variables bidireccionales, es decir, de entrada-salida, filecount, pp y m han sido inferidas en registros con anchos de 32 bits para las dos primeras y 6 bits para la última. Finalmente, para las variables de salida se han inferido dos memorias RAM, una de 256 x 32 bits para la variable data\_out y una de 256 x 16 bits para la variable ref\_block. Por lo tanto, se observa la trazabilidad entre las interfaces presentadas en la sección 3.2 a nivel software y las obtenidas a la salida de la herramienta.

Figura 3.7. Interfaz módulo adgolomb.cpp

Las estimaciones dadas por la herramienta a su salida son los presentados en la Tabla 3.9.

| Tecnología   | Ciclos en la      | Ciclos  | Transferencia de | Área      | Margen |

|--------------|-------------------|---------|------------------|-----------|--------|

|              | primera iteración | totales | datos            | (puertas) | (ns)   |

| 5VFX100 (-1) | 2                 | 266     | 1 muestra/ciclo  | 4146,73   | 1,42   |

Tabla 3.9. Estimaciones para el módulo adgolomb.cpp

Asimismo, los resultados tras el emplazamiento y ruteo son dados en la Tabla 3.10.

| Tecnología   | LUT<br>(Look-up table) | Slices<br>usadas | Bloques de<br>RAM   | DSP48        | Max.<br>Frecuencia | Ruta<br>crítica |

|--------------|------------------------|------------------|---------------------|--------------|--------------------|-----------------|

| 5VFX100 (-1) | 2502 (3,05%)           | 626 (3,06%)      | 1 RAMB18<br>(0,34%) | 5<br>(1,56%) | 85,020MHz          | 11,762ns        |

Tabla 3.10. Resultados obtenidos tras el emplazamiento y ruteo del módulo adgolomb.cpp

## 3.3.2.2. Implementación del módulo calc\_perr.cpp