Sistemas de información y Comunicaciones

## Máster en Tecnologías de Telecomunicación

## Trabajo Fin de Máster

Implementación Física y Verificación de un Cabezal de Recepción para el Estándar IEEE 802.15.4 en Tecnología CMOS 0.18 µm

Autor: Sergio Mateos Angulo

Tutor(es): Dr. Francisco Javier del Pino Suárez

Dr. Sunil Lalchand Khemchandani

Fecha: Junio 2016

Sistemas de información y Comunicaciones

# Máster en Tecnologías de Telecomunicación

## Trabajo Fin de Máster

# Implementación Física y Verificación de un Cabezal de Recepción para el Estándar IEEE 802.15.4 en Tecnología CMOS 0.18 µm

### **HOJA DE FIRMAS**

**Alumno/a:** Sergio Mateos Angulo Fdo.:

Tutor/a: Dr. Francisco Javier del Pino Suárez Fdo.:

Tutor/a: Dr. Sunil Lalchand Khemchandani Fdo.:

Fecha: Junio 2016

t +34 928 451 086 | iuma@iuma.ulpgc.es f +34 928 451 083 | www.iuma.ulpgc.es Campus Universitario de Tafira 35017 Las Palmas de Gran Canaria

## Máster en Tecnologías de Telecomunicación

Implementación Física y Verificación de un Cabezal de Recepción para el Estándar IEEE 802.15.4 en Tecnología CMOS 0.18 µm

## HOJA DE EVALUACIÓN

| Calificación:     |       |

|-------------------|-------|

| Presidente        | Fdo.: |

| Secretario        | Fdo.: |

| Vocal             | Fdo.: |

| Fecha: Junio 2016 |       |

# Índice

| 1. | Introducción                                                         | 15   |

|----|----------------------------------------------------------------------|------|

|    | 1.1. Objetivos                                                       | 19   |

|    | 1.2. Estructura de la memoria                                        | 19   |

| 2. | Estado del arte                                                      | 23   |

|    | 2.1. Redes de sensores inalámbricos                                  | 23   |

|    | 2.2. Estándar IEEE 802.15.4                                          | 25   |

|    | 2.2.1. Aplicaciones                                                  | 26   |

|    | 2.3. Tipos de arquitectura                                           | 28   |

|    | 2.3.1. Receptor heterodino simple                                    | 29   |

|    | 2.3.2. Receptor superheterodino                                      | 31   |

|    | 2.3.3. Receptor homodino                                             | 33   |

|    | 2.3.3.1. Receptor Cero-IF                                            | 33   |

|    | 2.3.3.2. Receptor Low-IF                                             | 36   |

|    | 2.4. Arquitectura del cabezal de recepción diseñado                  | 37   |

| 3. | Estudio de la tecnología                                             | 39   |

|    | 3.1. Resistencias                                                    | 39   |

|    | 3.1.1. Construcción                                                  | 39   |

|    | 3.1.2. Resistencias en la tecnología UMC 0.18 µm                     | 40   |

|    | 3.1.3. Resistencias optimizadas para RF en la tecnología UMC 0.18 µm | 41   |

|    | 3.2. Condensadores                                                   | 43   |

|    | 3.2.1. Construcción                                                  | 43   |

|    | 3.2.2. Condensadores en la tecnología UMC 0.18 µm                    | 43   |

|    | 3.2.3. Condensadores optimizados para RF en la tecnología UMC 0.18   | 3 μm |

|    | 44                                                                   |      |

|    | 3.3. Bobinas                                                         | 47   |

|    | 3.3.1. | Construcción                                                      | 47   |

|----|--------|-------------------------------------------------------------------|------|

|    | 3.3.2. | Funcionamiento                                                    | 47   |

|    | 3.3.3. | Modelo de la bobina                                               | 49   |

|    | 3.3.4. | Bobinas en la tecnología UMC 0.18 µm                              | 50   |

|    | 3.4.   | El Transistor MOSFET                                              | 51   |

|    | 3.4.1. | Construcción                                                      | 51   |

|    | 3.4.2. | Funcionamiento                                                    | 52   |

|    | 3.4.3. | Modelo de pequeña señal                                           | 54   |

|    | 3.4.4. | Transistores MOSFET en la tecnología UMC 0.18 μm                  | 57   |

|    |        | Transistores MOSFET optimizados para RF en tecnología UMC 0<br>58 | 0.18 |

|    | 3.5.   | Pads                                                              | 60   |

|    | 3.5.1. | Construcción                                                      | 60   |

|    | 3.5.2. | Pads en la tecnología UMC 0.18 μm                                 | 60   |

|    | 3.6.   | Lista de componentes                                              | 62   |

| 4. | Dis    | eño a nivel de esquemático                                        | 65   |

|    | 4.1.   | Arquitectura del cabezal de recepción diseñado                    | 65   |

|    | 4.2.   | Amplificador de bajo ruido (LNA)                                  | 66   |

|    | 4.2.1. | Estructura del amplificador de bajo ruido                         | 66   |

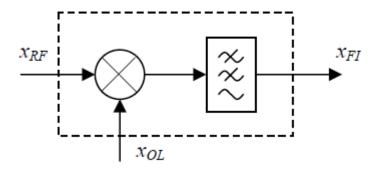

|    | 4.3.   | Mezclador                                                         | 71   |

|    | 4.3.1. | Conceptos teóricos de un mezclador                                | 71   |

|    | 4.3.2. | Estructura del mezclador                                          | 73   |

|    | 4.4.   | Amplificador de transimpedancia (TIA)                             | 75   |

|    | 4.4.1. | Estructura del amplificador de transimpedancia                    | 75   |

| 5. | Dis    | eño a nivel de <i>layout</i>                                      | 81   |

|    | 5.1.   | Proceso de diseño                                                 | 81   |

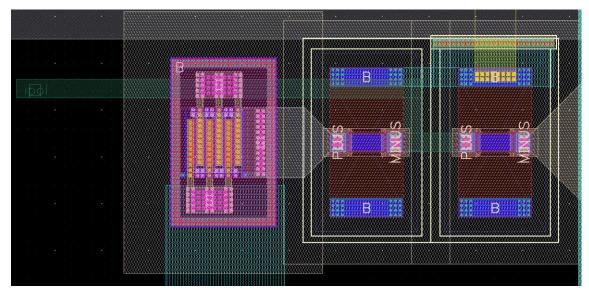

|    | 5.2.   | Layout del LNA                                                    | 83   |

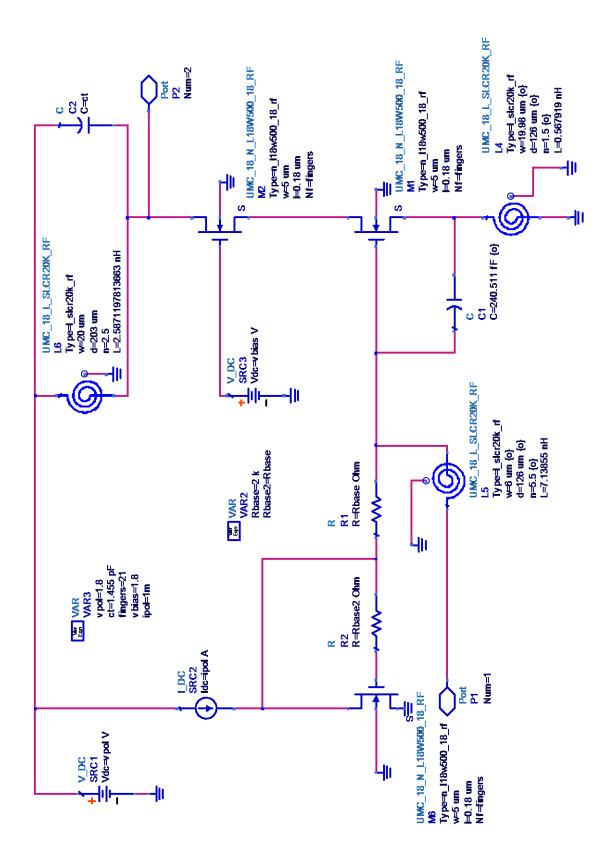

|    | 5.2.1. | Esquemático del LNA en Cadence                                    | 83   |

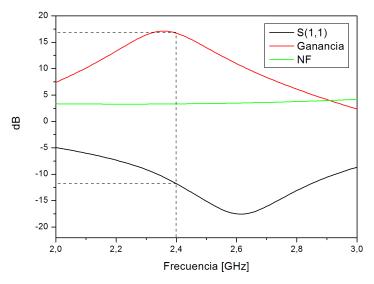

|    | 5.2.2. | Simulación del esquemático del LNA con <i>Dynamic Link</i> | 85  |

|----|--------|------------------------------------------------------------|-----|

|    | 5.2.3. | Diseño del layout del LNA                                  | 87  |

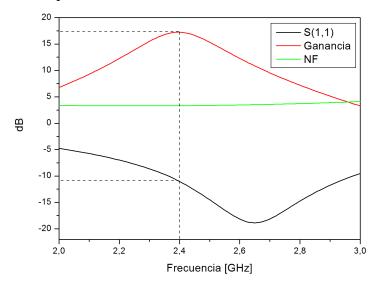

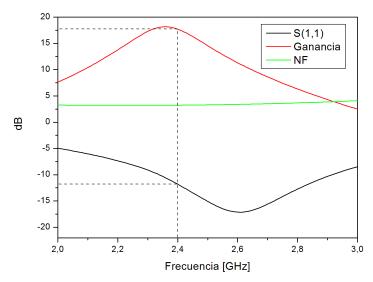

|    | 5.2.4. | Simulaciones post-layout del LNA                           | 89  |

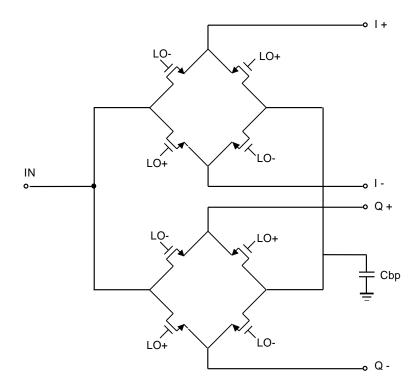

|    | 5.3.   | Layout del mezclador                                       | 93  |

|    | 5.3.1. | Esquemático del mezclador en Cadence                       | 93  |

|    | 5.3.2. | Simulación del esquemático del mezclador con Dynamic Link  | 94  |

|    | 5.3.3. | Diseño del <i>layout</i> del mezclador                     | 96  |

|    | 5.3.4. | Simulaciones post-layout del mezclador                     | 97  |

|    | 5.4.   | Layout del TIA                                             | 98  |

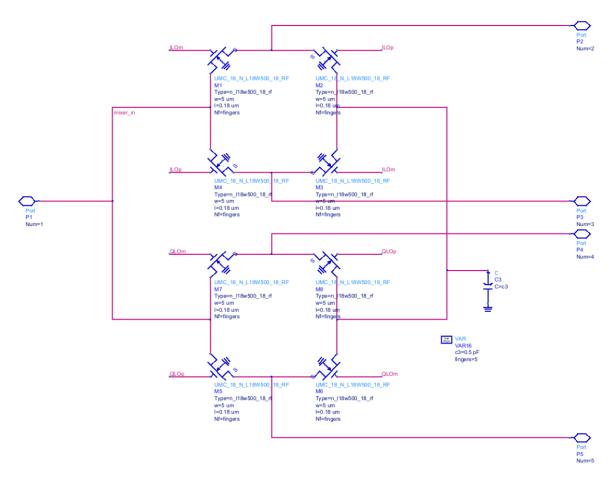

|    | 5.4.1. | Esquemático del TIA en Cadence                             | 98  |

|    | 5.4.2. | Simulación del esquemático del TIA con Dynamic Link        | 100 |

|    | 5.4.3. | Diseño del layout del TIA                                  | 102 |

|    | 5.4.4. | Simulaciones post-layout del TIA                           | 104 |

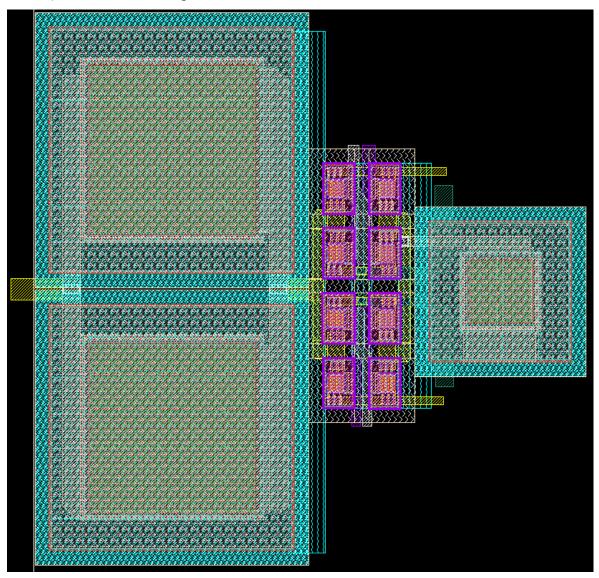

|    | 5.5.   | Layout del cabezal de recepción                            | 104 |

| 6. | Res    | sultados de simulaciones                                   | 109 |

|    | 6.1.   | Simulaciones post-layout del cabezal de recepción          | 109 |

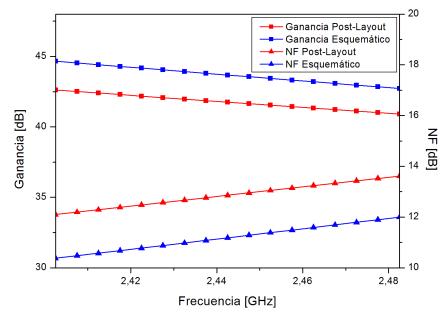

|    | 6.1.1. | Ganancia y figura de ruido                                 | 111 |

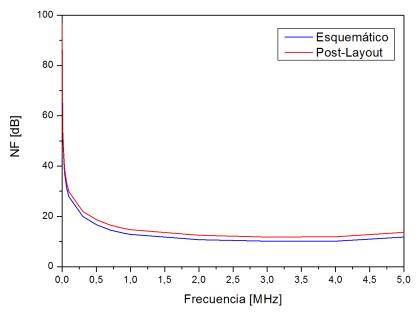

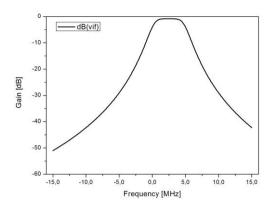

|    | 6.1.2. | Respuesta en frecuencia                                    | 114 |

|    | 6.1.3. | Adaptación de entrada                                      | 115 |

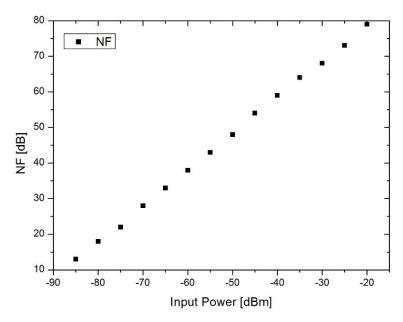

|    | 6.1.4. | Linealidad                                                 | 117 |

|    | 6.1.5. | Consumo de potencia                                        | 118 |

| 7. | Cor    | nclusiones                                                 | 121 |

| 8. | Bib    | liografía                                                  | 127 |

|    |        |                                                            |     |

# Índice de Figuras

| Figura 1-1. Diagrama de bloques de un transceptor.                                  | 16 |

|-------------------------------------------------------------------------------------|----|

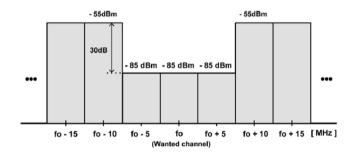

| <b>Figura 1-2.</b> Rechazo de señales en la banda de 2.4 GHz.                       | 17 |

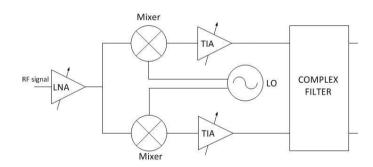

| Figura 1-3. Estructura del cabezal de recepción.                                    | 18 |

| Figura 2-1. Tecnologías inalámbricas.                                               | 24 |

| Figura 2-2. Arquitectura del protocolo.                                             | 25 |

| Figura 2-3. Bandas de frecuencia y canales del estándar 802.15.4.                   | 26 |

| Figura 2-4. Aplicaciones de ZigBee.                                                 | 27 |

| Figura 2-5. Diagrama de bloques de un receptor heterodino simple                    | 29 |

| Figura 2-6. Problema de la frecuencia imagen.                                       | 29 |

| Figura 2-7. Implementación de un filtro de rechazo de imagen.                       | 30 |

| Figura 2-8. Problema de mitad de IF.                                                | 31 |

| Figura 2-9. Diagrama de bloques de un receptor superheterodino.                     | 31 |

| Figura 2-10. Etapas de filtrado en un receptor superheterodino.                     | 32 |

| Figura 2-11. Receptor superheterodino para sistemas digitales.                      | 32 |

| Figura 2-12. Diagrama de bloques de un receptor homodino.                           | 33 |

| Figura 2-13. Receptor homodino para sistemas digitales.                             | 33 |

| Figura 2-14. Receptor cero-IF.                                                      | 34 |

| Figura 2-15. Problema de DC offset.                                                 | 34 |

| Figura 2-16. Ejemplo del efecto de la asimetría en una constelación QPSK            | 35 |

| Figura 2-17. Distorsión de segundo orden.                                           | 35 |

| Figura 2-18. Diagrama de bloques de un receptor Low-IF.                             | 36 |

| Figura 2-19. Filtro polifásico como solución al problema de la frecuencia imagen. 3 | 37 |

| Figura 2-20. Estructura del cabezal de recepción.                                   | 38 |

| Figura 3-1. Parámetros de una resistencia.                                          | 39 |

| Figura 3-2. Cuadro de diálogo de Cadence de ajuste de parámetros de resistencias.   | 40 |

| Figura 3-3. Circuito equivalente de una resistencia.                                | 11 |

| Figura 3-4. Layout de una resistencia del tipo RNHR_RF                              | 12 |

| Figura 3-5. Layout de una resistencia del tipo RNNPO_RF                             | 12 |

| Figure 3.6 Construcción de un condensador                                           | 12 |

| Figura 3-7. Cuadro de diálogo de Cadence de ajuste de parámetros de condensa           | ador. |

|----------------------------------------------------------------------------------------|-------|

|                                                                                        | 44    |

| Figura 3-8. Circuito equivalente del condensador MIMCAPM_RF                            | 45    |

| Figura 3-9. Layout de condensadores del tipo MICAPM_RF.                                | 46    |

| <b>Figura 3-10</b> . Sección transversal del <i>layout</i> de un condensador MICAPM_RF | 46    |

| Figura 3-11. Modelo de una bobina cuadrada simple.                                     | 47    |

| Figura 3-12. Campos eléctricos y magnéticos en un inductor integrado                   | 49    |

| Figura 3-13. Modelo clásico de un inductor espiral integrado.                          | 49    |

| Figura 3-14. Cuadro de diálogo de Cadence de ajuste de parámetros de bobinas.          | 50    |

| Figura 3-15. Layout de una bobina del tipo L_SLCR20K_RF                                | 51    |

| Figura 3-16. Sección transversal de transistores MOS.                                  | 52    |

| Figura 3-17. Transistor MOSFET tipo n en corte.                                        | 52    |

| Figura 3-18. Transistor MOSFET tipo n en zona óhmica                                   | 53    |

| Figura 3-19. Transistor MOSFET tipo n en zona de saturación.                           | 54    |

| Figura 3-20. Modelo simplificado de pequeña señal de un transistor MOSFET              | 55    |

| Figura 3-21. Modelo completo de pequeña señal de un transistor MOSFET                  | 56    |

| Figura 3-22. Cuadro de diálogo de Cadence de ajuste de parámetros de un trans          | istor |

| MOSFET                                                                                 | 57    |

| <b>Figura 3-23</b> . Circuito equivalente de los transistores optimizados para RF N/P  | 58    |

| Figura 3-24. Layout de un transistor MOSFET para RF                                    | 59    |

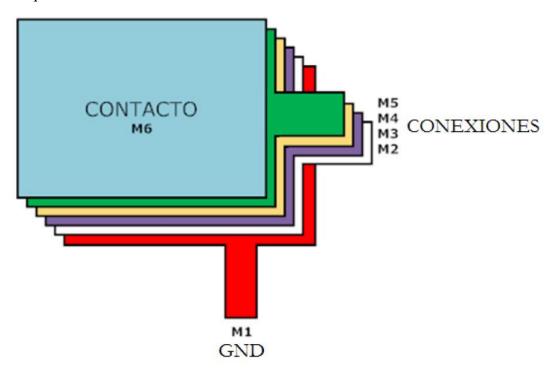

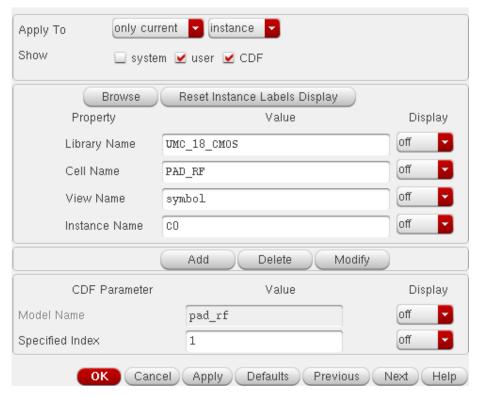

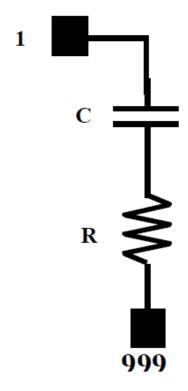

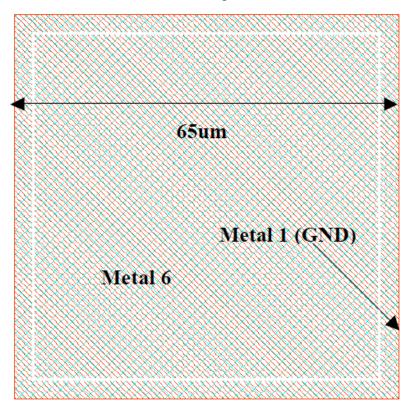

| Figura 3-25. Representación de un pad.                                                 | 60    |

| Figura 3-26. Cuadro de diálogo de Cadence de ajuste de parámetros de un PAD            | _RF.  |

|                                                                                        | 61    |

| Figura 3-27. Circuito equivalente de un PAD_RF                                         | 61    |

| Figura 3-28. Layout de un pad para RF.                                                 | 62    |

| Figura 4-1. Estructura del cabezal de recepción.                                       | 65    |

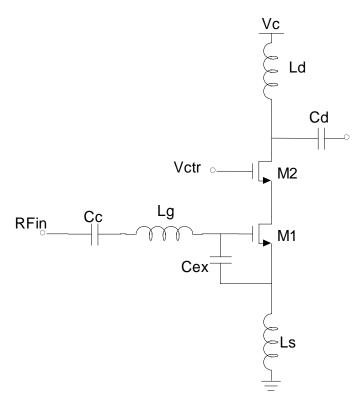

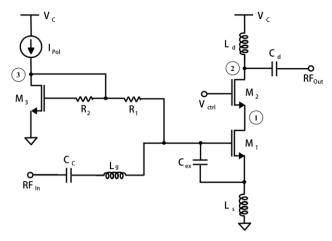

| Figura 4-2. Estructura del LNA.                                                        | 67    |

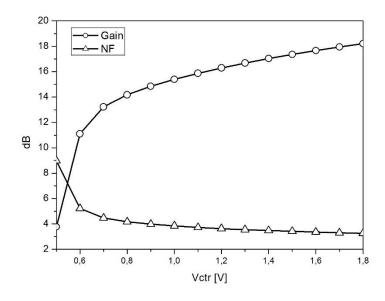

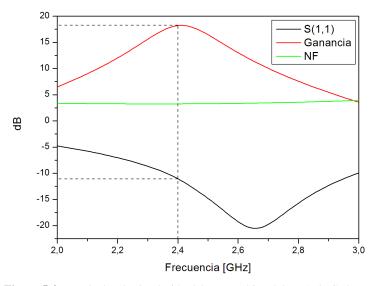

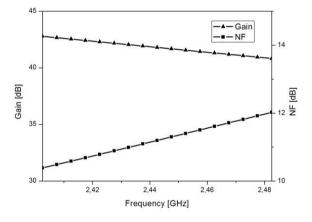

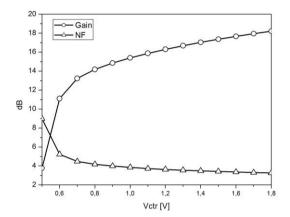

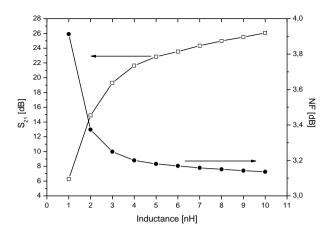

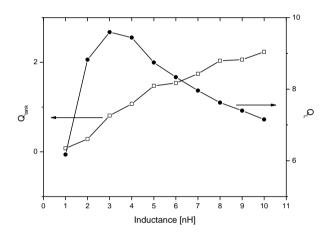

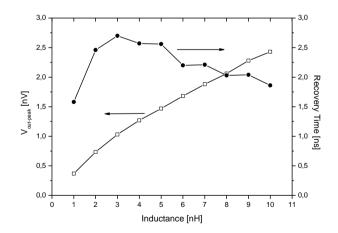

| Figura 4-3. Ganancia y NF en función de V <sub>ctr.</sub>                              | 68    |

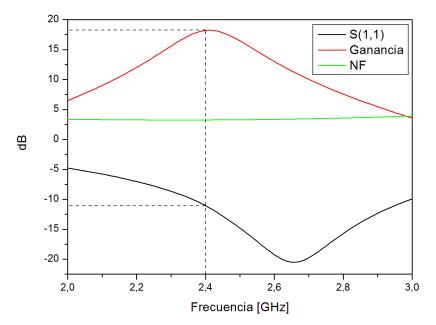

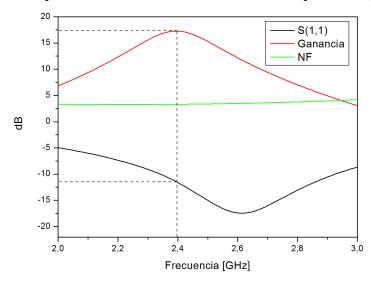

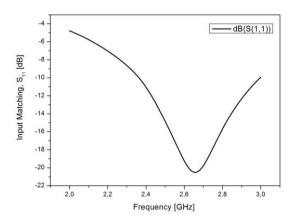

| Figura 4-4. Ganancia, NF y S (1,1) del LNA diseñado.                                   | 69    |

| Figura 4-5. Diseño del LNA.                                                            | 70    |

| Figura 4-6. Diagrama de bloques de un mezclador ideal                                  | 71    |

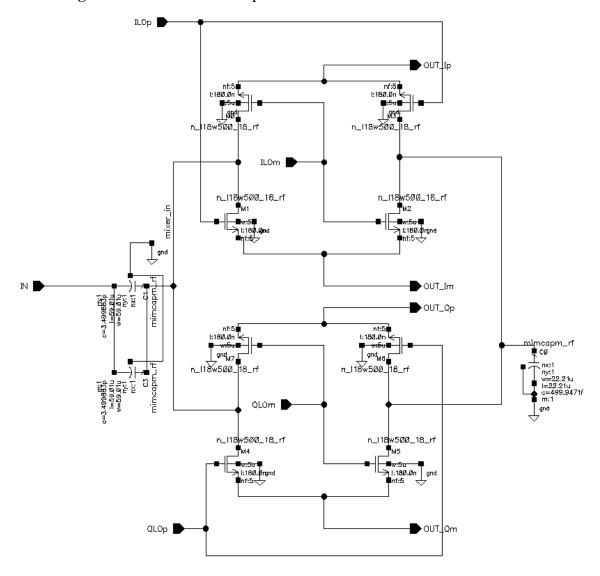

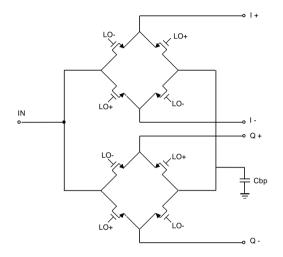

| Figura 4-7. Estructura del mezclador.                                                  | 74    |

| Figura 4-8. Diseño del mezclador.                                                      | 75    |

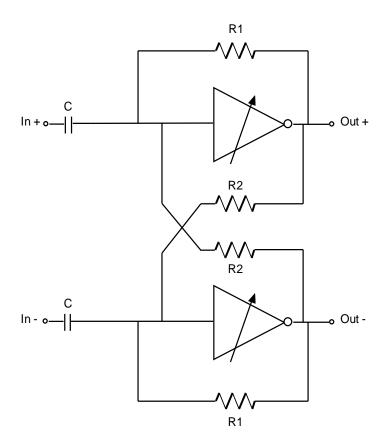

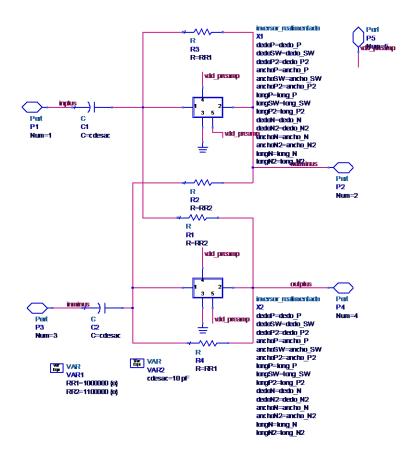

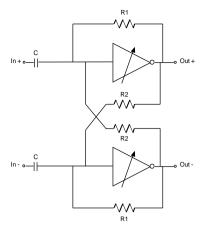

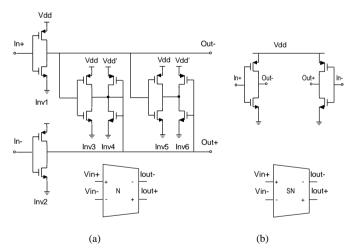

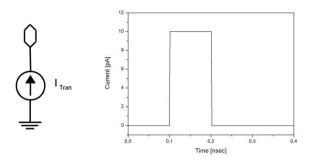

| <b>Figura 4-9</b> . Estructura del TIA                                            |

|-----------------------------------------------------------------------------------|

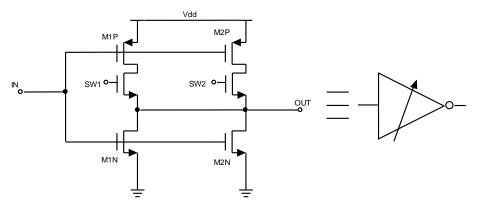

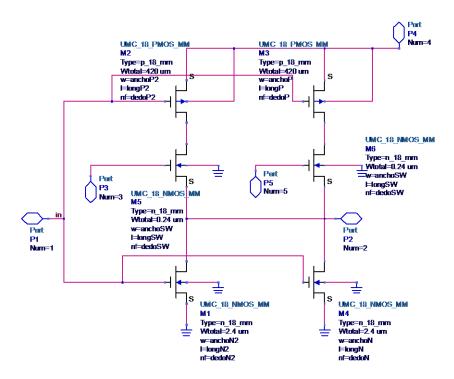

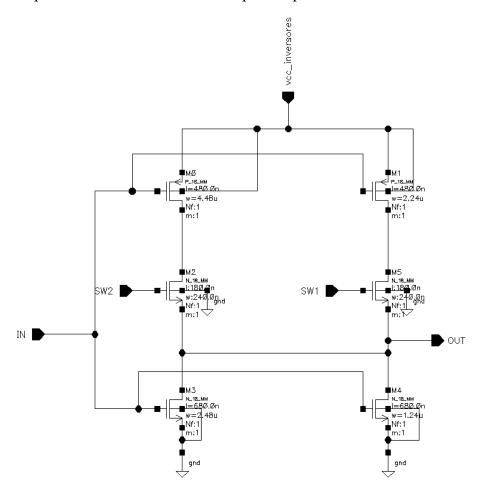

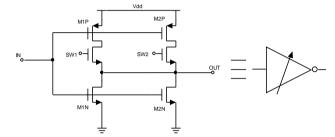

| <b>Figura 4-10</b> . Estructura de los inversores del TIA                         |

| <b>Figura 4-11</b> . Esquemático de los inversores del TIA                        |

| Figura 4-12. Esquemático del TIA                                                  |

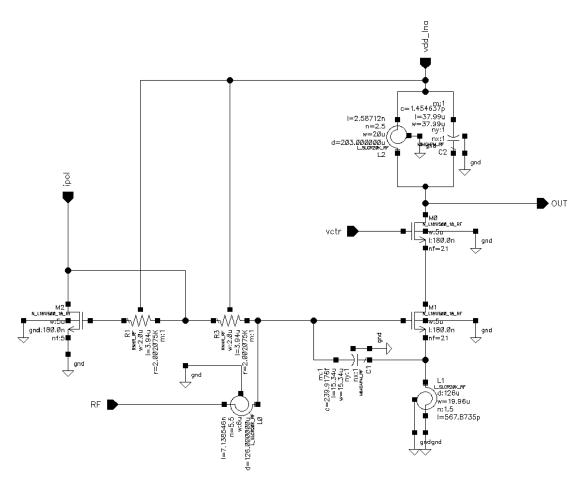

| Figura 5-1. Esquemático del LNA en Cadence                                        |

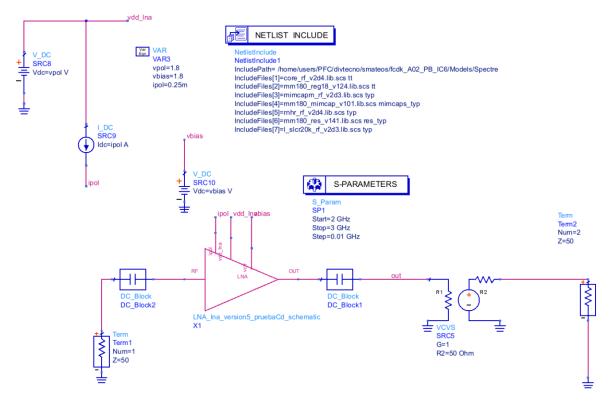

| Figura 5-2. Setup de simulación del esquemático del LNA usando ADS Dynamic Link   |

| 8                                                                                 |

| Figura 5-3. Resultados de simulación del esquemático del LNA de Cadence 8         |

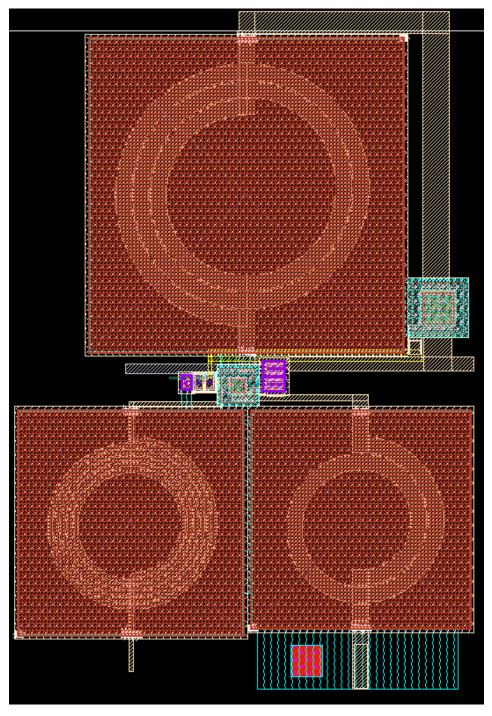

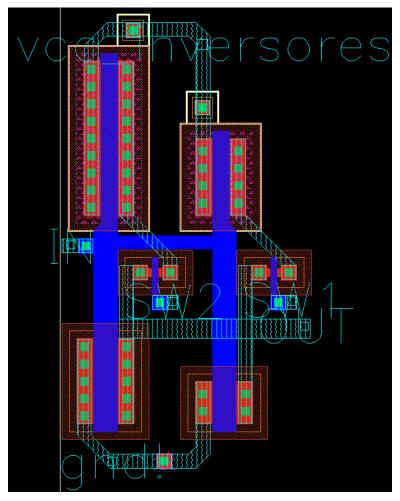

| Figura 5-4. Layout del LNA                                                        |

| <b>Figura 5-5</b> . <i>Layout</i> del transistor M2 y las resistencias R0 y R2    |

| <b>Figura 5-6</b> . <i>Layout</i> del nodo de salida del LNA                      |

| Figura 5-7. Resultados de simulación post-layout del LNA. Ganancia, NF y S (1,1)  |

| 99                                                                                |

| Figura 5-8. Resultados de simulación post-layout del LNA. Ganancia, NF y S (1,1)  |

| Extraído sólo resistencias                                                        |

| Figura 5-9. Resultados de simulación post-layout del LNA. Ganancia, NF y S (1,1)  |

| Extraído sólo capacidades9                                                        |

| Figura 5-10. Resultados de simulación post-layout del LNA. Ganancia, NF y S (1,1) |

| C <sub>2</sub> =1.4 pF9                                                           |

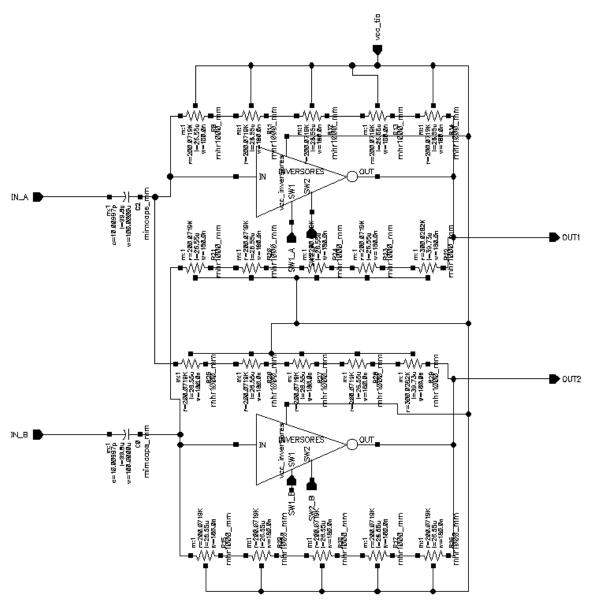

| <b>Figura 5-11</b> . Esquemático del mezclador con Cadence                        |

| Figura 5-12. Setup de simulación del mezclador utilizando ADS Dynamic Link9       |

| Figura 5-13. Layout del mezclador                                                 |

| <b>Figura 5-14</b> . Esquemático del TIA en Cadence.                              |

| <b>Figura 5-15</b> . Esquemático de los inversores del TIA en Cadence99           |

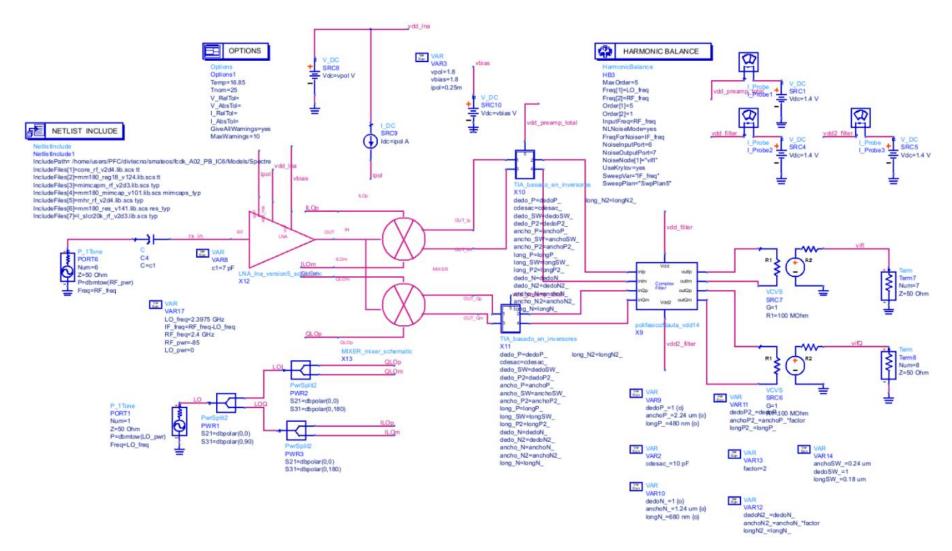

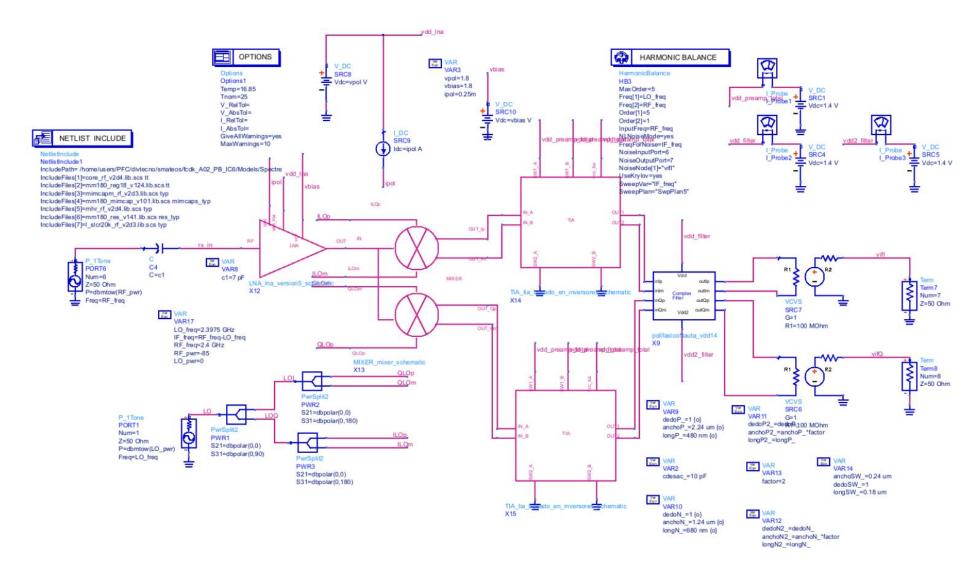

| Figura 5-16. Setup de simulación del mezclador utilizando ADS Dynamic Link 10     |

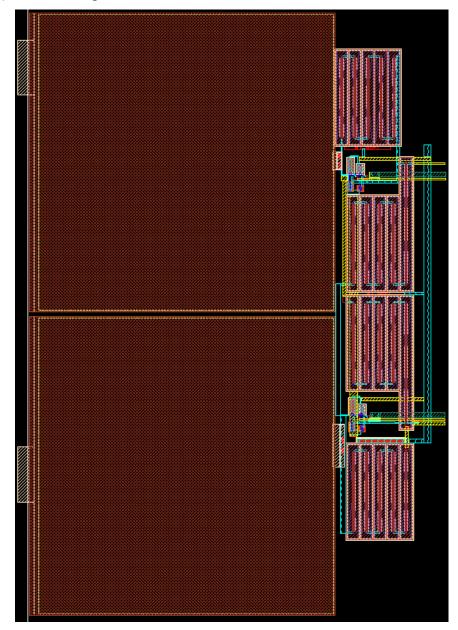

| Figura 5-17. Layout del TIA.                                                      |

| Figura 5-18. Layout de los inversores del TIA                                     |

| Figura 5-19. Esquemático del TIA en Cadence                                       |

| Figura 5-20. <i>Layout</i> del cabezal de recepción                               |

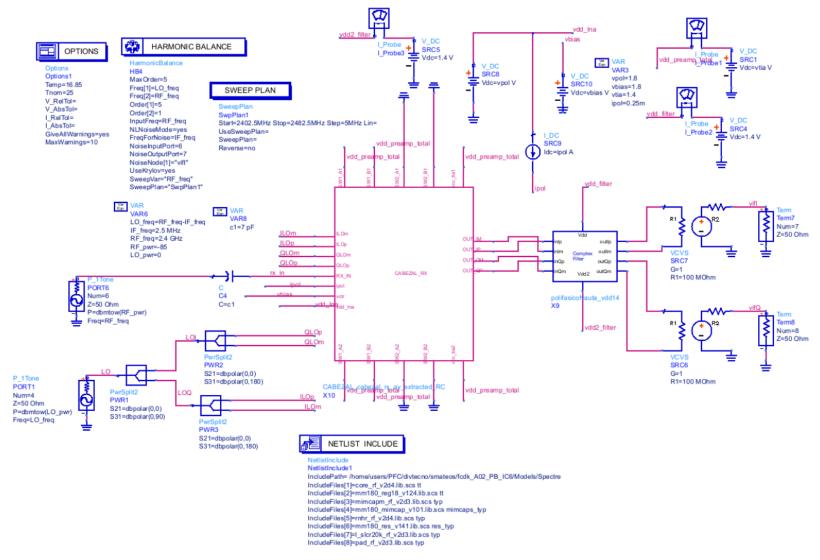

| Figura 6-1. Setup de simulación del cabezal de recepción utilizando ADS Dynami    |

| Link                                                                              |

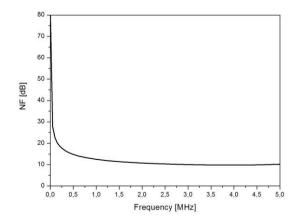

| Figura 6-2. Ganancia y NF para toda la banda del estándar 802.15.4                |

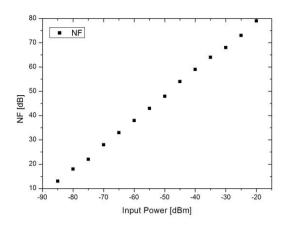

| Figura 6-3. NF para un canal.                                                     |

| Figura 6-4. NF máxima frente a la potencia de entrada de un receptor p             | para el estándar |

|------------------------------------------------------------------------------------|------------------|

| 802.15.4                                                                           | 114              |

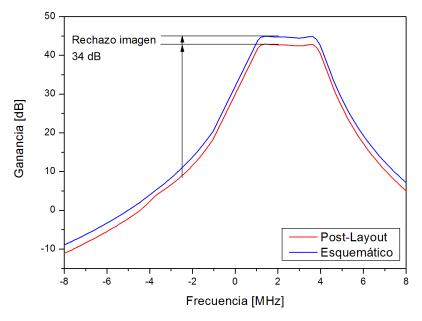

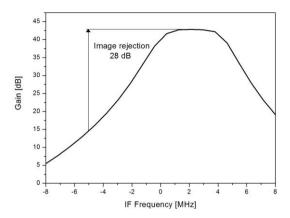

| Figura 6-5. Rechazo imagen.                                                        | 115              |

| Figura 6-6. Respuesta en frecuencia del receptor.                                  | 115              |

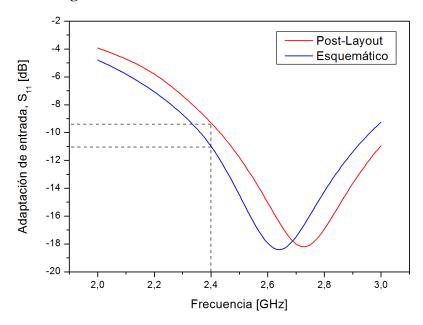

| Figura 6-7. Adaptación de entrada                                                  | 116              |

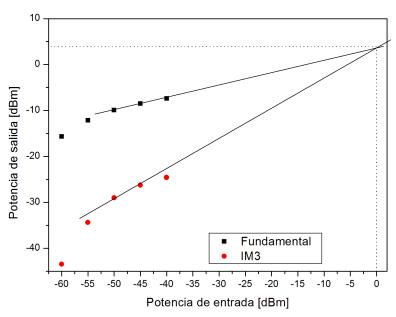

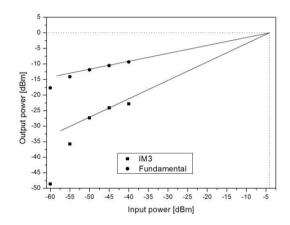

| Figura 6-8. Punto de intercepción IIP3 del receptor para simulación de             | le esquemático.  |

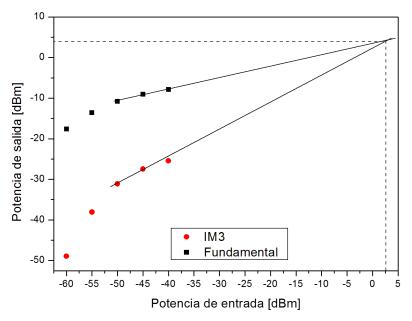

|                                                                                    | 117              |

| Figura 6-9. Punto de intercepción IIP <sub>3</sub> del receptor para simulación po | ost-layout 118   |

# Índice de Tablas

| Tabla 2-I. Características de ZigBee27                                                                    |

|-----------------------------------------------------------------------------------------------------------|

| Tabla 2-II. Especificaciones del estándar IEEE 802.15.4 para receptores de RF 28                          |

| Tabla 3-I. Capacidades de la zona de óxido de un transistor MOSFET         57                             |

| <b>Tabla 3-II.</b> Componentes de la tecnología UMC 0.18 μm CMOS                                          |

| $\textbf{Tabla 5-I.} \ \text{Resultados de simulación del esquemático del mezclador de Cadence} \dots 94$ |

| Tabla 5-II. Resultados de simulación post-layout del mezclador de Cadence97                               |

| Tabla 5-III. Resultados de simulación del esquemático del TIA de Cadence         100                      |

| Tabla 5-IV. Resultados de simulación post-layout del TIA de Cadence         104                           |

| Tabla 6-I. Ganancia y NF del receptor para distintas configuraciones. Simulación del                      |

| esquemático                                                                                               |

| Tabla 6-II. Ganancia y NF del receptor para distintas configuraciones. Simulación                         |

| post-layout                                                                                               |

| <b>Tabla 7-I.</b> Resultados de simulaciones del cabezal de recepción                                     |

| <b>Tabla 7-II</b> . Comparación del cabezal de recepción diseñado con otros modelos 123                   |

# Capítulo 1

## 1. Introducción

El desarrollo de transceptores CMOS (*Complementary Metal Oxide-Semiconductor*) de baja potencia para la banda de 2,4 GHz ha recibido especial atención en los últimos años debido a la demanda de dispositivos de bajo coste y el deseo de que posean baterías de larga vida útil. A pesar de la existencia de estándares como Bluetooth o IEEE 802.11 que operan en esta banda, el estándar IEEE 802.15.4 satisface la demanda de bajo coste y bajo consumo en el desarrollo de transceptores de baja tasa binaria. El estándar IEEE 802.15.4 permite trabajar en tres bandas de frecuencia: en la banda de 868 MHz para Europa, en la banda de 915 MHz en América y en la banda de 2,4 GHz a nivel global. La tasa de datos del estándar varía desde los 20 a los 250 kb/s en función de la banda en la que se opere. En cuanto a las aplicaciones de este estándar, se pueden nombrar una gran cantidad de ellas, como pueden ser la automoción, la domótica, aplicaciones industriales, sistemas médicos, aplicaciones comerciales, etc. Para estas aplicaciones, la batería debería durar entre varios meses y un año sin ser reemplazada [1].

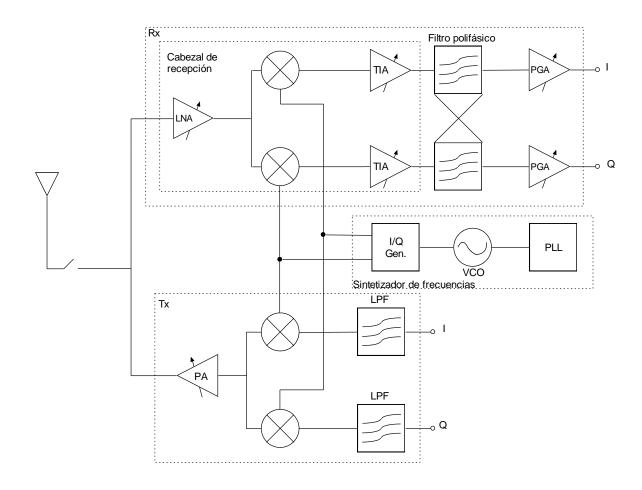

Un transceptor se puede dividir en varios bloques claramente diferenciados. En primer lugar, hay dos bloques principales como son el receptor y el transmisor. Dentro de cada uno de estos bloques se puede distinguir un bloque denominado cabezal. El cabezal (de recepción o de transmisión) trabaja en la frecuencia de RF (Radio Frecuencia) y es el encargado de adaptar la señal tras ser recibida, o para ser transmitida. Tras el cabezal se encuentra la etapa de filtrado, que permite al receptor o al transmisor quedarse con la banda de frecuencia deseada. Por otra parte, dentro de un transceptor se encuentra el sintetizador de frecuencias. Este bloque incluye el oscilador local que genera la señal necesaria para convertir la señal de entrada a una frecuencia determinada, a través de un mezclador. En la **Figura 1-1** se muestra el diagrama de bloques de un transceptor, en el cuál se pueden apreciar los distintos elementos que se han mencionado.

Figura 1-1. Diagrama de bloques de un transceptor.

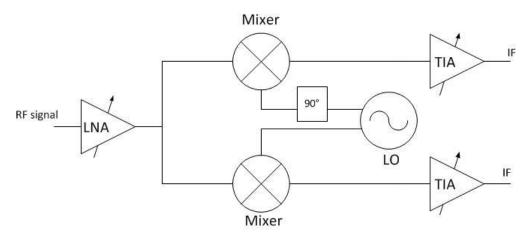

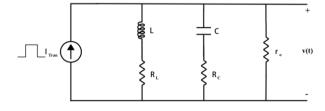

Este trabajo fin de máster se centra en el cabezal de recepción, el cual corresponde a la primera etapa de un receptor, donde se adapta la señal de entrada para su posterior tratamiento. Típicamente, un cabezal de recepción en un circuito de radiofrecuencia como el que se ha diseñado, está compuesto por una serie de elementos. El primero de estos elementos es el amplificador de bajo ruido (LNA: Low Noise Amplifier), que es el encargado de adaptar la señal que proviene de la antena de recepción y amplificarla, introduciendo el menor ruido posible. El siguiente elemento es el mezclador, que es el encargado de mezclar la señal de entrada con una señal generada por el oscilador local con el fin de llevar la señal desde una frecuencia de entrada (generalmente alta) a una frecuencia de trabajo (en los receptores, esta frecuencia es menor que la de entrada). Por último, se encuentran los amplificadores y filtros de procesado de señal en banda base.

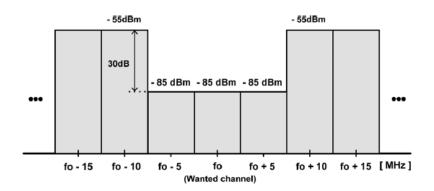

Por otra parte, el estándar 802.15.4 presenta un buen rechazo frente a señales próximas a la señal deseada, tal y como se muestra en la **Figura 1-2**. Este rechazo es considerablemente mejor que en otras tecnologías de radiofrecuencia (WLAN, GSM,

WCDMA, etc.) y las especificaciones del filtro de rechazo imagen son menos restrictivas. Como consecuencia, en la literatura se encuentran un gran número de receptores para el estándar 802.15.4 que implementan una arquitectura low-IF [1]-[4].

Figura 1-2. Rechazo de señales en la banda de 2.4 GHz.

El proceso de desarrollo de un transceptor integrado CMOS de radiofrecuencia consta de cuatro partes principales: en primer lugar, el diseño del transceptor a nivel de esquemático, en segundo lugar la creación del *layout*, previo a la fabricación, posteriormente se fabrica el transceptor en un circuito integrado y, por último, la toma de medidas del transceptor, una vez ha sido fabricado. Dicho de otra manera, una vez se ha realizado el diseño a nivel de esquemático y se han realizado las simulaciones pertinentes para comprobar el correcto funcionamiento del mismo, se pasa a realizar el *layout* a partir del esquemático. Esto supone el primer paso en el proceso de fabricación puesto que consiste en convertir el diseño (esquemático) en una representación física del mismo. Es decir, el *layout* es necesario para poder fabricar el transceptor ya que a partir de sus especificaciones se crean las diversas máscaras a emplear en el proceso de fabricación. Por tanto, una vez se tiene el *layout*, se realizan simulaciones *post-layout* y se comprueba que los resultados obtenidos corresponden con los obtenidos en la simulación. Por último, se manda a fabricar el transceptor y se realizan medidas al circuito fabricado para comprobar las prestaciones reales del circuito.

En este proyecto se realizará el *layout*, y las simulaciones *post-layout* correspondientes, partiendo de un cabezal de recepción para el estándar IEEE 802.15.4 ya diseñado [5],[6]. Cabe destacar que si bien en este trabajo fin de máster se va a realizar el *layout* del cabezal de recepción, este no se fabricará hasta que no se hayan diseñado el resto de componentes del transceptor. A fecha de redacción de este trabajo fin de máster, dentro del grupo de trabajo se han diseñado algunos circuitos como el filtro polifásico o el

amplificador de ganancia programable, además del transmisor. Sin embargo, estos circuitos aún están en fase de diseño a nivel de esquemático. Es decir, se mandará a fabricar el *chip* una vez se haya realizado el diseño de *layout* del transceptor completo. Es por esto por lo que, tal y como se comentará más adelante, no se han incluido los *pads* que permitan introducir las señales de entrada y medir las señales de salida. Este paso se realizará cuando se tenga el *layout* del transceptor completo y se sepa con seguridad cuántas señales de entrada y salida se tienen.

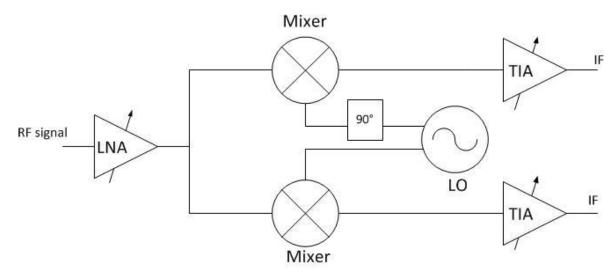

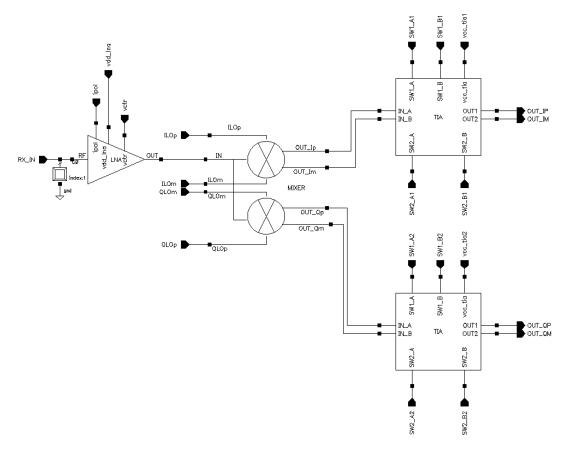

En cuanto a la estructura del cabezal de recepción, en la **Figura 1-3** se muestra un diagrama de bloques del mismo [5].

Figura 1-3. Estructura del cabezal de recepción.

Como se puede observar, el cabezal de recepción consta de tres partes principales. La primera corresponde al amplificador de bajo ruido o LNA (Low Noise Amplifier). La función del LNA es la de amplificar la señal de RF entrante (señal de radiofrecuencia) introduciendo el menor ruido posible, así como la de adaptar la señal que proviene de la antena. En segundo lugar se sitúan los mezcladores que están controlados por un oscilador local y cuya función es la de bajar la frecuencia de la señal a la frecuencia deseada, es decir, a la frecuencia intermedia (IF: Intermediate Frequency). En este caso, al ser un receptor del tipo de conversión a baja frecuencia (Low-IF), la señal de trabajo será de frecuencia baja. Por último se encuentran los amplificadores de transimpedancia (TIA: Trans-Impedance Amplifier) que convierten la señal de corriente en señal de tensión aportando ganancia en este proceso.

Por otra parte, este trabajo fin de máster forma parte de un proyecto de investigación científica coordinado entre el Instituto Universitario de Microelectrónica Aplicada (IUMA), el Grupo de Ingeniería Electrónica de la Universidad de Sevilla y el Centro de Estudios e Investigaciones Técnicas de Gipuzkoa (CEIT). Este proyecto de título "Diseño de circuitos de comunicaciones para alta radiación ambiental (ComRad)", tiene como objetivo

desarrollar el primer dispositivo que permita el despliegue de redes de sensores inalámbricos en entornos de alta radiación ambiental [7]. En el grupo de trabajo ya se han empezado a realizar pruebas de análisis del efecto de la radiación en circuitos de radiofrecuencia. Concretamente, se han realizado unas pruebas preliminares en el LNA diseñado en este trabajo fin de máster.

#### 1.1.Objetivos

El objetivo de este proyecto es obtener el *layout* de un cabezal de recepción basado en la arquitectura low-IF para el estándar IEEE 802.15.4 usando la tecnología CMOS 0.18 μm. Además, se realizarán simulaciones *post-layout* para comprobar el correcto funcionamiento del diseño realizado. Por otra parte, al tratarse de un circuito integrado se desea que nuestro cabezal de recepción ocupe el menor área posible.

Para ello se utiliza la herramienta software *Virtuoso* de Cadence y se realizan las simulaciones con el software *Advanced Design System* (ADS) de la empresa Keysight, utilizando el *ADS Dynamic Link*. De esta manera, se realiza una comunicación entre Cadence y ADS, pudiendo simular los *layout* de los circuitos integrados, desarrollados en Cadence, con las librerías de simulación de ADS [8].

Para poder utilizar los distintos componentes de la tecnología CMOS 0.18 μm es necesario instalar la librería o kit de diseño (*Design Kit*) de UMC correspondiente.

#### 1.2. Estructura de la memoria

Esta memoria está dividida en siete capítulos y dos anexos, además de una lista bibliográfica con las referencias consultadas durante el desarrollo del trabajo fin de máster y la elaboración de esta memoria.

En este primer capítulo se ha realizado una introducción con los antecedentes de este trabajo, y se definen los objetivos marcados para este trabajo fin de máster.

En el capítulo 2 se realiza un estudio del estado del arte de receptores de radiofrecuencia para el estándar IEEE 802.15.4. En primer lugar se estudian las características principales de una red de sensores y las ventajas que estas presentan. Este capítulo se centra en el estándar IEEE 802.15.4 puesto que el cabezal de recepción que se ha diseñado está basado en este estándar. Además, se explican las distintas arquitecturas de receptores de radiofrecuencia que existen. Posteriormente, se presentan las características básicas de cada

una de ellas y se comentan las ventajas y desventajas que presentan, para justificar la elección de la arquitectura más conveniente para el cabezal de recepción diseñado. Por último, se describe la arquitectura de receptor elegida, apoyándose en las conclusiones sacadas tras realizar el estudio de las distintas arquitecturas.

En el capítulo 3 se realiza un estudio de la tecnología *UMC 0.18 µm 1P6M Salicide Mixed Mode/RF CMOS* de la fundidora *United Microelectronics Corporation* (UMC), que es la que se ha utilizado en el diseño del cabezal de recepción. En este estudio se comenzará con una descripción teórica de los dispositivos, para posteriormente analizar los distintos modelos para cada componente. Por último, se estudiarán los componentes que han sido optimizados para radiofrecuencia y que, por tanto, serán de especial interés para este proyecto.

En el capítulo 4 se describen los distintos circuitos que han sido diseñados, los cuales forman el cabezal de recepción. En primer lugar se muestra la topología del amplificador de bajo ruido, explicando las ventajas y desventajas de dicha topología. En segundo lugar se describe la estructura del mezclador que se ha diseñado. Por último, al igual que para los otros dos circuitos mencionados, se explica la estructura de los amplificadores de transimpedancia presentes en el cabezal de recepción.

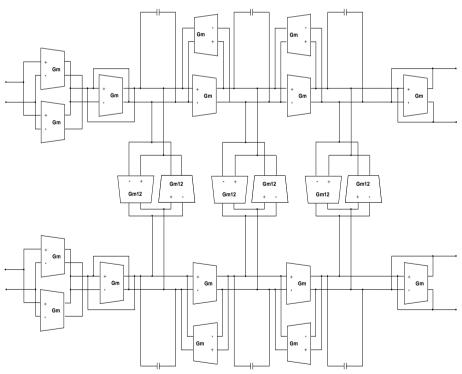

El capítulo 5 describe el siguiente paso en el proceso de fabricación: el diseño a nivel de *layout*. Tal y como se ha visto anteriormente, en este paso se definen las máscaras o planos de fabricación del circuito integrado. En este caso, se ha realizado un diseño de *layout* para cada circuito que compone el cabezal de recepción, para posteriormente unirlos y realizar el *layout* del cabezal de recepción al completo. Por tanto, este capítulo comenzará con la exposición del *layout* del amplificador de bajo ruido. Posteriormente se abordará el diseño de *layout* del mezclador y de los amplificadores de transimpedancia. Por último, se muestra el *layout* del cabezal de recepción. Además, en cada caso se comentarán las distintas decisiones de diseño que se han ido tomando durante el desarrollo del trabajo.

El capítulo 6 se centra en el análisis de los resultados obtenidos a la hora de simular el funcionamiento del cabezal de recepción, tanto a nivel de esquemático como tras realizar el *layout*. En estas simulaciones se incluye un filtro polifásico al final del cabezal de recepción diseñado, el cual es imprescindible para el correcto funcionamiento del receptor. El diseño del filtro polifásico no entra dentro del alcance de este proyecto y por ello se ha incluido un filtro polifásico diseñado por otro compañero dentro del grupo de trabajo. Por tanto, se muestran los resultados obtenidos, centrándose en los parámetros típicos de un receptor de

RF, comparando los resultados obtenidos en la simulación del esquemático con los obtenidos en las simulaciones *post-layout*.

En el capítulo 7 se comentan las conclusiones que se pueden extraer de este trabajo fin de máster. Además, se presenta un resumen de los resultados obtenidos con el fin de compararlos con los obtenidos en otras soluciones de este tipo que han sido desarrolladas. En este capítulo también se definen las líneas futuras de este trabajo.

En cuanto a los anexos que se incluyen al final de esta memoria de trabajo fin de máster, el primero de ellos muestra un artículo científico (paper) desarrollado en inglés, conjuntamente con otro compañero y los tutores, acerca del cabezal de recepción diseñado, así como del filtro polifásico que se incluye. Este artículo fue presentado en la XXX Conferencia en Diseño de Circuitos y Sistemas Integrados (DCIS: Design of Circuits and Integrated Systems). En el segundo anexo se puede encontrar un artículo científico desarrollado en el grupo de trabajo en el cual se explica el análisis del efecto de la radiación en circuitos de radiofrecuencia. Concretamente, el circuito que se ha analizado es el LNA que se encuentra en el cabezal de recepción diseñado.

#### 2. Estado del arte

Este capítulo se centra en el estudio de las características principales de una red de sensores. En concreto, se estudiará el estándar IEEE 802.15.4 sobre el cual se implementa la tecnología ZigBee. Además, se estudiarán los distintos tipos de arquitectura que se podrían implementar para diseñar un receptor de radiofrecuencia. En este estudio, se comentarán las ventajas y desventajas de cada una de las arquitecturas descritas para poder elegir la arquitectura más conveniente. Por último se comentará la arquitectura que se ha elegido para realizar el diseño del receptor.

#### 2.1. Redes de sensores inalámbricos

Una red de sensores inalámbricos se puede definir como una red con numerosos dispositivos distribuidos espacialmente, utilizada para monitorizar distintas condiciones ambientales o físicas, como la temperatura, presión, humedad, etc.[9]. En los últimos años ha proliferado el uso de estas redes frente a las redes cableadas utilizadas hasta entonces. Una de las grandes ventajas de las redes inalámbricas, la cual ha propiciado este crecimiento, es la posibilidad de un despliegue rápido de los sensores sin la necesidad de instalar grandes longitudes de cableado. Además, las redes inalámbricas poseen un alto grado de flexibilidad con respecto a las redes cableadas.

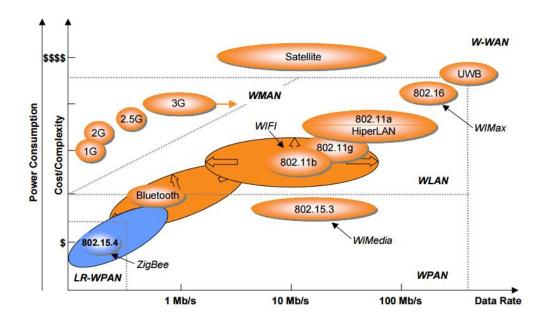

Estas ventajas han propiciado el auge de este tipo de redes en aplicaciones industriales de forma que, para cada aplicación en concreto se deberá elegir qué tecnología utilizar en función de cómo se ajusten las especificaciones de dicha tecnología a los requisitos de la aplicación en cuestión. Tal y como se muestra en la **Figura 2-1**, hay varias tecnologías que se pueden usar para aplicaciones de redes inalámbricas.

Figura 2-1. Tecnologías inalámbricas.

Como se puede observar, en la **Figura 2-1** se representan las distintas tecnologías inalámbricas existentes en función de la tasa binaria, de la potencia consumida y del coste. En la parte inferior se muestran las redes inalámbricas de área personal (WPAN: *Wireless Personal Area Network*) que se caracterizan por su bajo consumo de potencia y por su bajo coste. En la esquina inferior izquierda se muestra un caso especial de este tipo de redes, las redes de baja tasa de datos (LR-WPAN: *Low Rate Wireless Personal Area Network*). A medida que se aumentan tanto la potencia consumida como el coste, se entra en el rango de las redes inalámbricas de área local (WLAN: *Wireless Local Area Network*). Las redes inalámbricas de área metropolitana (WMAN: *Wireless Metropolitan Area Network*) se diferencian de las WLAN en que la tasa de datos máxima es menor. Por último, para una tasa de datos y potencia consumida elevados, existen las redes inalámbricas de área extensa (WWAN: *Wireless Wide Area Network*).

En este trabajo, al desear implementar un receptor de bajo consumo, y al no ser necesaria una tasa binaria elevada, se ha optado por usar la tecnología ZigBee basada en el estándar IEEE 802.15.4.

#### 2.2. Estándar IEEE 802.15.4

En este apartado se analizarán las principales características del estándar IEEE 802.15.4 centrándonos en los parámetros que afectan al diseño del cabezal de recepción. Este estándar fue desarrollado por el grupo de trabajo 802.15 perteneciente al *Institute of Electrical and Electronics Engineers*. Este grupo de trabajo está especializado en redes inalámbricas de área personal. En concreto, este estándar fue desarrollado por el subgrupo 4 de este grupo de trabajo. El estándar 802.15.4 define el nivel físico y el control de acceso al medio de redes LR-WPAN [10].

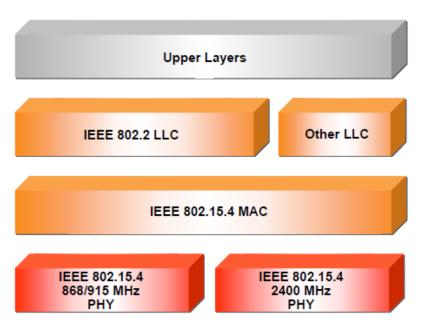

Por otro lado, este estándar define las dos primeras capas, la capa física y la de enlace, del protocolo OSI (*Open Systems Interconnect*). Sobre el estándar se basan varias tecnologías, como por ejemplo ZigBee, cuyo objetivo es el de dar una solución completa construyendo los niveles superiores del protocolo. En la **Figura 2-2** se muestra en rojo la capa física, en naranja la capa de enlace -que se divide en la subcapa de control de enlace lógico (LLC: *Logical Link Control*) y la subcapa de control de acceso al medio (MAC: *Media Access Control*)- y en gris las capas superiores (las capas de red, transporte, sesión, presentación y aplicación según el modelo OSI). Como se puede observar, tal y como se ha comentado, la capa física y la capa de enlace las gobierna el estándar 802.15.4 mientras que las capas superiores están controladas por ZigBee, u otra tecnología similar.

Figura 2-2. Arquitectura del protocolo.

En cuanto a las características principales, en primer lugar, cabe destacar que el estándar puede operar en tres bandas de frecuencia distintas. Estas bandas se encuentran a 868 MHz (sólo en Europa), a 915 MHz (en América) y a 2.4 GHz de forma global. Estas bandas de frecuencia cuentan con 1, 10 y 16 canales, respectivamente (ver **Figura 2-3**). Además, la tasa de datos varía entre los 20 y los 250 kb/s en función de la banda en la que se trabaje [11].

| )            | Channel | Center<br>Frequency<br>(MHz) | Availability                    |

|--------------|---------|------------------------------|---------------------------------|

| 868 MHz Band | 0       | 868,3                        | Europe                          |

|              | 1       | 908                          |                                 |

|              | 2       | 908                          | 90c00 00000000                  |

|              | 3       | 910                          |                                 |

|              | 4       | 912                          |                                 |

| 915 MHz      | 5       | 914                          |                                 |

| Band         | 6       | 916                          | 3.2                             |

| Duna         | 7       | 918                          |                                 |

|              | 8       | 920                          |                                 |

|              | 9       | 922                          | •                               |

|              | 10      | 924                          | Americas                        |

|              | 11      | 2405                         |                                 |

|              | 12      | 2410                         |                                 |

|              | 13      | 2415                         |                                 |

|              | 14      | 2420                         |                                 |

|              | 15      | 2425                         | \$0.000 \$0.000 \$0.000 \$0.000 |

|              | 16      | 2430                         | . The                           |

|              | 17      | 2435                         |                                 |

| 2.4 GHz      | 18      | 2440                         |                                 |

| Band         | 19      | 2445                         | C. Corr                         |

| Dana         | 20      | 2450                         | 1 1                             |

|              | 21      | 2455                         | <b>7</b> 7 9,                   |

|              | 22      | 2460                         |                                 |

|              | 23      | 2465                         |                                 |

|              | 24      | 2470                         |                                 |

|              | 25      | 2475                         | 14/04/-114/:-1-                 |

|              | 26      | 2480                         | World Wide                      |

Figura 2-3. Bandas de frecuencia y canales del estándar 802.15.4.

#### 2.2.1. Aplicaciones

Como ya se ha comentado, la tecnología ZigBee se basa en el estándar IEEE 802.15.4 que ha sido descrito. El uso de esta tecnología se realiza principalmente en aplicaciones que requieran muy bajo consumo y una baja transmisión de datos. Por tanto, puede utilizarse para realizar control industrial, albergar sensores empotrados, recolectar datos médicos o en aplicaciones domóticas. En la **Figura 2-4** se muestran algunas de las múltiples aplicaciones de esta tecnología.

Figura 2-4. Aplicaciones de ZigBee.

En la **Tabla 2-I** se muestra un resumen de las características más importantes de la tecnología ZigBee.

Tabla 2-I. Características de ZigBee

|                         | ZigBee                    |

|-------------------------|---------------------------|

| Bandas de frecuencia    | 2.4 GHz, 868/915 MHz      |

|                         | 250 kbps (2.4 GHz)        |

| Tasa de transferencia   | 40 kbps (915 MHz)         |

|                         | 20 kbps (868 MHz)         |

| Número de canales       | 16 (2.4 GHz)              |

|                         | 10 (915 MHz)              |

|                         | 1 (868 MHz)               |

| Rango de nodos internos | 10m-100m                  |

| Número de dispositivos  | 255/65535                 |

| Requisitos de           | Muy baja- años de batería |

| alimentación            |                           |

| Arquitecturas           | Estrella, árbol y malla   |

| Complejidad             | Simple                    |

Por otra parte, en la **Tabla 2-II** se muestran las especificaciones del estándar IEEE 802.15.4 para receptores de radiofrecuencia [1].

Tabla 2-II. Especificaciones del estándar IEEE 802.15.4 para receptores de RF

| Parámetros                    | Especificaciones                                             |

|-------------------------------|--------------------------------------------------------------|

| Consumo de potencia<br>[mW]   | El menor posible                                             |

| Ganancia del                  | >30 (FE <sup>1</sup> )                                       |

| receptor [dB]                 | [-20,65] (BB <sup>2</sup> )                                  |

| Variación de<br>ganancia [dB] | $65 (FE^1 + BB^2)$                                           |

| NF [dB]                       | <15.5                                                        |

| Rechazo imagen [dBc]          | >20                                                          |

| IIP <sub>3</sub> [dBm]        | >-32 para máxima<br>ganancia<br>>-10 para ganancia<br>mínima |

| Sensibilidad [dB]             | -85                                                          |

FE1: Front-End o Cabezal de RF

BB<sup>2</sup>: Banda Base

#### 2.3. Tipos de arquitectura

En los siguientes apartados se abordará el estudio de la arquitectura del receptor que se ha diseñado. En primer lugar se comentarán distintos tipos de arquitectura que se podrían implementar para diseñar un receptor de radiofrecuencia. Además, se comentarán las ventajas y desventajas de cada una de las arquitecturas descritas para poder elegir la arquitectura más conveniente. Por último se comentará la arquitectura que se ha elegido para realizar el diseño del receptor.

#### 2.3.1. Receptor heterodino simple

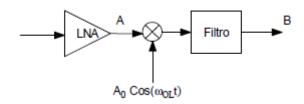

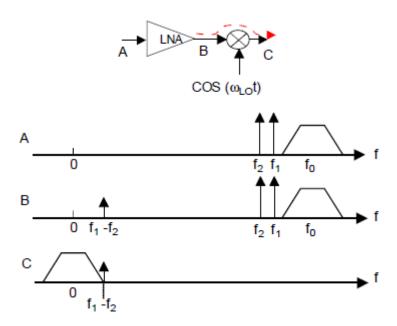

La primera arquitectura de receptor que se va a analizar es la conocida como heterodino simple. El diagrama de bloques de esta arquitectura se muestra en la **Figura 2-5**.

Figura 2-5. Diagrama de bloques de un receptor heterodino simple.

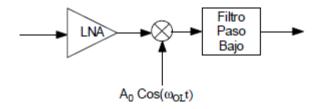

Como se puede observar, se trata de una arquitectura bastante simple. La señal de radiofrecuencia (RF) entrante se amplifica mediante un amplificador de bajo ruido (LNA: Low Noise Amplifier). Posteriormente, la señal amplificada se mezcla con la señal que proviene del oscilador local para bajar la señal a frecuencia intermedia (IF: Intermediate Frecuency). Por último, esta señal pasa por un filtro paso banda para quedarnos con la porción del espectro que nos interesa, que en este caso estará en función de la frecuencia del oscilador local.

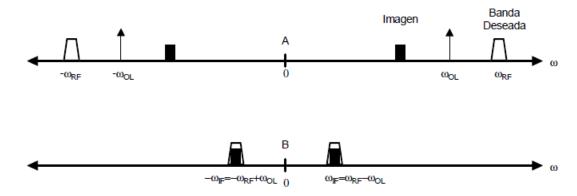

Sin embargo, esta arquitectura presenta varios inconvenientes o desventajas. El principal problema que aparece al implementar esta arquitectura es el problema de la frecuencia imagen. Esto sucede cuando la frecuencia de la señal imagen mezclada con la frecuencia del oscilador local da como resultado el valor de la frecuencia intermedia. En la **Figura 2-6** se puede observar este fenómeno.

Figura 2-6. Problema de la frecuencia imagen.

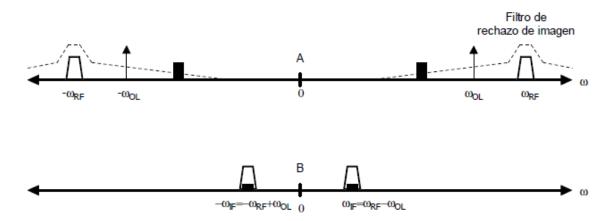

Para solventar este problema, es necesario implementar un filtro de rechazo de imagen que permita minimizar la aparición de la frecuencia imagen en la frecuencia intermedia deseada, tal y como se muestra en la **Figura 2-7**.

Figura 2-7. Implementación de un filtro de rechazo de imagen.

Sin embargo, al incluir un filtro de rechazo de imagen surge el problema del compromiso entre sensibilidad y selectividad. La sensibilidad se mide en función del rechazo a la frecuencia imagen mientras que la selectividad se mide en función del filtrado del canal. En el caso de que la frecuencia intermedia sea de un valor alto, se puede conseguir una buena sensibilidad pero a costa de tener una mala selectividad ya que es más complicado realizar un buen filtrado de canal. Al contrario, en el caso de que la frecuencia intermedia tenga un valor pequeño, la sensibilidad será mala pero se tendrá una buena selectividad.

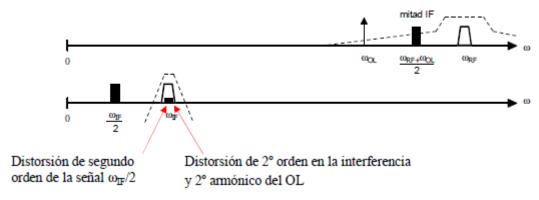

Otro problema que presenta esta arquitectura es el problema de mitad de IF. Este problema surge cuando la frecuencia imagen se encuentra a una frecuencia equidistante entre la frecuencia de RF entrante y la frecuencia del oscilador local. Esto provocará que aparezca una distorsión de segundo orden en la frecuencia de IF, tal y como se muestra en la **Figura 2-8**.

Figura 2-8. Problema de mitad de IF.

Para solventar este problema se deberá minimizar la distorsión de segundo orden tanto de la señal de RF como de la señal IF, así como minimizar el segundo armónico en el oscilador mediante un ciclo de trabajo (duty-cycle) del 50 %[12].

#### 2.3.2. Receptor superheterodino

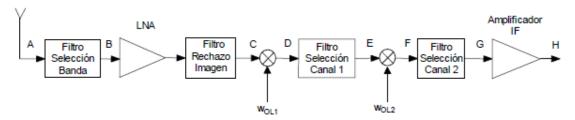

El receptor superheterodino (también conocido como Dual IF) es el más utilizado en la actualidad debido a que aporta un rendimiento alto y estable. Se emplea en equipos de radio, televisión, sistemas de radar, telefonía móvil y sistemas de comunicaciones en general. En la **Figura 2-9** se muestra el diagrama de bloques de esta arquitectura de receptor.

Figura 2-9. Diagrama de bloques de un receptor superheterodino.

Como se puede observar, en esta arquitectura se requiere el uso de más de un mezclador lo que resulta en un mayor consumo y una mayor complejidad en el diseño del receptor. Además, esta arquitectura también presenta el problema de la frecuencia imagen por lo que es necesario utilizar filtros de rechazo de imagen, aumentando el área del receptor. Por otro lado, esta arquitectura mejora el compromiso entre sensibilidad y selectividad ya que se incluyen dos etapas de mezcla o conversión. Para ello se usa una primera frecuencia intermedia alta para alcanzar el nivel de rechazo de imagen deseado, es decir, obtener una buena sensibilidad. En segundo lugar se utiliza una segunda frecuencia intermedia baja con el objetivo de alcanzar una selectividad adecuada. En la **Figura 2-10** se muestran los

distintos pasos de filtrado que se realizan en la cadena de recepción de este tipo de arquitectura.

Figura 2-10. Etapas de filtrado en un receptor superheterodino.

Otra ventaja que presenta esta arquitectura es que permite repartir la ganancia entre la etapa de RF y la IF, lo que reduce el riesgo de que se produzcan inestabilidades. Esto es especialmente ventajoso en aplicaciones en las que se requiera una ganancia elevada, puesto que es posible incluir una mayor cantidad de etapas de amplificación [13]. Sin embargo, se puede afirmar que este tipo de receptor no es el más idóneo para aplicaciones de bajo coste y bajo consumo [1].

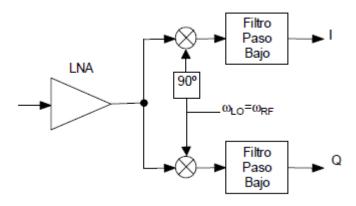

Para aplicaciones que requieran de un sistema digital, se debe diferenciar entre fase y cuadratura. Para ello es necesario utilizar dos mezcladores para obtener ambos canales, es decir, la amplitud y la fase de la envolvente compleja de la señal. Esto se debe a que las dos bandas laterales del espectro de RF contienen información diferente y si se solapan al realizar una mezcla, no es posible recuperar dicha información. En la **Figura 2-11** se muestra la estructura de un receptor superheterodino para sistemas digitales.

Figura 2-11. Receptor superheterodino para sistemas digitales.

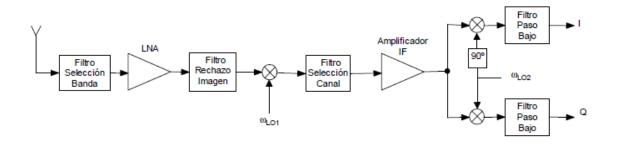

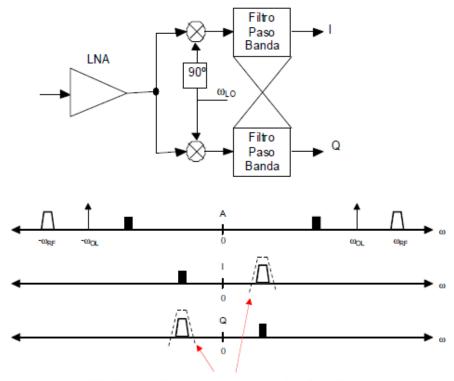

#### 2.3.3. Receptor homodino

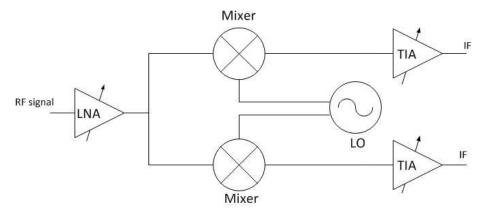

Este tipo de receptor también es conocido como receptor de conversión directa y se puede diferenciar, a su vez, en dos subtipos: receptor Cero-IF y receptor *Low-IF*. En la **Figura 2-12** se puede observar el diagrama de bloques de un receptor homodino o de conversión directa.

Figura 2-12. Diagrama de bloques de un receptor homodino.

Al igual que en el receptor superheterodino, en el receptor homodino se debe diferenciar entre fase y cuadratura para aplicaciones en sistemas digitales. En la **Figura 2-13** se muestra el diagrama de bloques de un receptor homodino para sistemas digitales.

Figura 2-13. Receptor homodino para sistemas digitales.

#### 2.3.3.1. Receptor Cero-IF

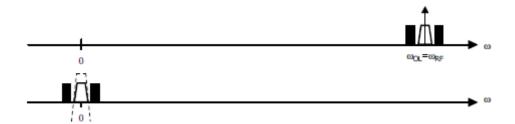

Este tipo de receptor destaca porque, en este caso, la frecuencia intermedia está situada en 0 Hz. Para ello, la señal de RF se mezcla con una señal del oscilador local de la misma frecuencia. Por tanto, la frecuencia intermedia se encuentra en banda base. En la **Figura 2-14** se muestra este procedimiento.

Figura 2-14. Receptor cero-IF.

Las principales ventajas de esta arquitectura son, en primer lugar, que se trata de una arquitectura bastante simple y se evita el problema de la frecuencia imagen. Esto supone un menor coste en área ya que no son necesarios filtros de rechazo de imagen. Otra ventaja de esta arquitectura es que se utiliza un filtro paso bajo en lugar de un filtro paso banda. Estos últimos son de implementación más compleja, por tanto, al usar los primeros, la simplicidad del receptor es mayor.

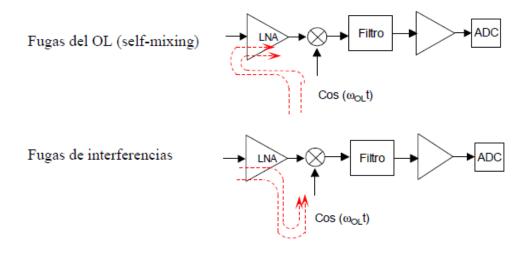

Sin embargo, esta arquitectura presenta una serie de desventajas que se deben tener en cuenta a la hora de implementar esta arquitectura en un receptor de radiofrecuencia. La principal desventaja es la de la aparición de tensiones de continua no deseadas (*DC offset*). Esto es especialmente problemático al estar trabajando en banda base, donde aparecen las tensiones de continua. Si estas tensiones aparecen en los bloques siguientes pueden corromper la señal o saturar el circuito. Estas tensiones pueden aparecer tanto por las fugas del oscilador local hacia la entrada o viceversa, desde la entrada hacia el oscilador local. Esto se muestra en la **Figura 2-15**.

Figura 2-15. Problema de DC offset.

Otra de las principales desventajas de esta arquitectura es la asimetría entre la fase y la cuadratura. Esto se produce puesto que en la generación de las señales en cuadratura, los caminos no son iguales. En la **Figura 2-16** se muestra un ejemplo del efecto de la asimetría en una constelación QPSK. En este caso se puede observar como hay tanto error de amplitud como error de fase.

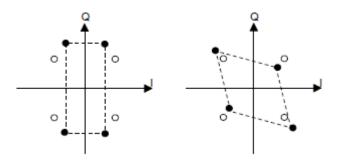

Figura 2-16. Ejemplo del efecto de la asimetría en una constelación QPSK.

La distorsión de segundo orden es otro de los inconvenientes de utilizar la arquitectura cero-IF. Esta se produce cuando los armónicos de segundo orden de la señal de entrada aparecen en la frecuencia intermedia, pudiendo corromper la señal. Esto afecta directamente a la linealidad del receptor, empeorándola ostensiblemente. En la **Figura 2-17** se ilustra este efecto.

Figura 2-17. Distorsión de segundo orden.

Entre los inconvenientes de esta arquitectura también cabe destacar el problema del ruido *flicker*. Este tipo de ruido se caracteriza porque su densidad espectral de potencia

aumenta a bajas frecuencias [12]. Por tanto, al estar trabajando en banda base en esta arquitectura, este ruido es un factor a tener en cuenta.

Las fugas del oscilador local hacia la entrada es otra de las desventajas de este tipo de arquitectura. Estas fugas pueden provocar interferencias en las bandas de los otros receptores.

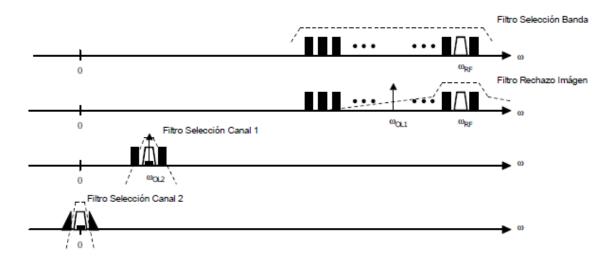

#### 2.3.3.2. Receptor Low-IF

Esta arquitectura es parecida a la cero-IF, con la diferencia de que en este caso la frecuencia intermedia es de un valor bajo, sin llegar a los 0 Hz. En otras palabras, se trabaja en bajas frecuencias pero no en banda base. Por tanto, en lugar de filtros paso bajo se utilizan filtros paso banda (de baja frecuencia). En la **Figura 2-18** se muestra el diagrama de bloques de un receptor con esta arquitectura.

Figura 2-18. Diagrama de bloques de un receptor Low-IF.

Las principales ventajas de esta arquitectura son, en primer lugar, que se trata de una arquitectura bastante simple y, en segundo lugar, que se minimizan los problemas del *DC* offset y el ruido flicker.

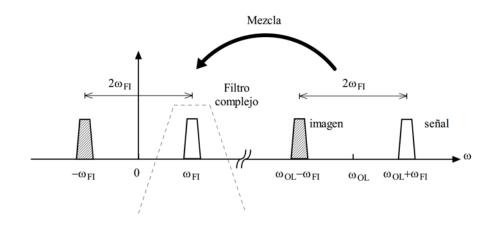

Por el contrario, en esta arquitectura se agravan los problemas del rechazo a la frecuencia imagen. Para solucionarlo se implementa un filtro polifásico que distinga entre la fase y la cuadratura, tal y como se muestra en la **Figura 2-19**.

Un filtro polifásico distingue entre la fase I y la Q

Figura 2-19. Filtro polifásico como solución al problema de la frecuencia imagen.

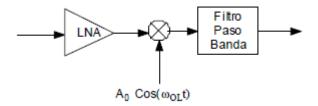

## 2.4. Arquitectura del cabezal de recepción diseñado

Una vez analizadas las distintas arquitecturas posibles de un receptor de radiofrecuencia, y analizadas las ventajas y desventajas de cada una, se ha optado por una arquitectura de receptor de conversión directa del tipo *Low-IF*. Como se ha analizado en el apartado anterior, la arquitectura de receptor superheterodino no es la más adecuada para aplicaciones de bajo coste y bajo consumo y, por tanto, queda descartada para este caso. Si se deseara utilizar una arquitectura de cero-IF, sería necesario implementar filtros complejos con realimentación para eliminar problemas como el nivel de continua introducido. Por tanto, por simplicidad a la hora de diseñar los filtros en un futuro, se ha optado por la arquitectura de conversión a baja frecuencia (*Low-IF*). Además, como ya se ha comentado, esta arquitectura minimiza los problemas del ruido *flicker*.

En cuanto a la estructura del cabezal de recepción, en la **Figura 2-20** se muestra un diagrama de bloques del cabezal que se ha diseñado.

Figura 2-20. Estructura del cabezal de recepción.

Como se puede observar, el cabezal de recepción consta de tres partes principales. La primera corresponde al amplificador de bajo ruido o LNA. La función del LNA es la de amplificar la señal de RF entrante introduciendo el menor ruido posible así como la de adaptar la señal que proviene de la antena. En segundo lugar se sitúan los mezcladores que están controlados por un oscilador local y cuya función es la de bajar la frecuencia de la señal a la frecuencia deseada, es decir, a la frecuencia intermedia. En este caso, al ser un receptor del tipo de conversión a baja frecuencia, la señal de trabajo será de frecuencia baja. Por último se encuentran los amplificadores de transimpedancia (TIA: Trans-Impedance Amplifier) que convierten la señal de corriente en señal de tensión.

Este cabezal de recepción será integrado posteriormente en un receptor completo, el cual deberá tener un filtro polifásico a la salida de los amplificadores de transimpedancia para resolver el problema de la frecuencia imagen. Sin embargo, el diseño del filtro polifásico queda fuera del alcance de este proyecto.

## 3. Estudio de la tecnología

En este capítulo se presenta una visión general de la tecnología *UMC* 0.18 μm 1P6M Salicide Mixed Mode/RF CMOS de la fundidora United Microelectronics Corporation (UMC). Esta tecnología consta de seis metales, siendo la última capa de metal la de mayor espesor y mayor conductividad. Esto permite mejorar el factor de calidad de los inductores integrados. En cuanto a los dispositivos activos, los transistores que se utilizan son del tipo MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor), siendo la longitud de puerta mínima en esta tecnología de 0.18 μm. Además, la tecnología UMC 0.18 μm ofrece una amplia librería de componentes pasivos [14].

En este estudio se comenzará con una descripción teórica de los dispositivos, para posteriormente analizar los distintos modelos para cada componente. Por último, se estudiarán los componentes que han sido optimizados para radio frecuencia y que, por tanto, serán de especial interés para este proyecto.

### 3.1. Resistencias

## 3.1.1. Construcción

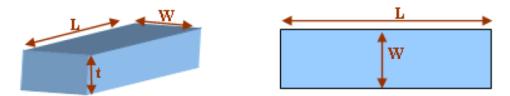

El valor óhmico de una resistencia integrada depende fundamentalmente del valor resistivo del material. En la **Figura 3-1** se muestra un modelo de una resistencia integrada y los parámetros que influyen en el valor óhmico.

Figura 3-1. Parámetros de una resistencia.

Partiendo de la **Figura 3-1**, el valor de la resistencia se obtiene a partir de la ecuación (3.1):

$$R = \frac{\rho}{t} \cdot \frac{W}{I} \tag{3.1}$$

Siendo  $\rho$  y t la resistividad y el espesor del material, y L y W la longitud y la anchura de la pista, respectivamente.

En procesos de fabricación de dispositivos basados en semiconductores, el espesor de las capas de material resistivo permanece constante, por lo que el valor de la resistencia puede determinarse mediante la ecuación (3.2):

$$R = R_{square} \cdot \frac{W}{I} \tag{3.2}$$

Siendo  $R_{square}$  la resistencia por cuadrado, que es igual al cociente entre la resistividad y el espesor del material.

## 3.1.2. Resistencias en la tecnología UMC 0.18 µm

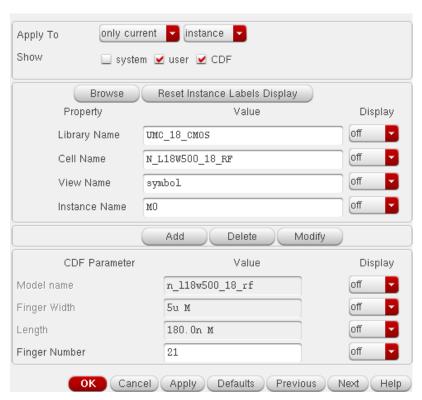

La tecnología UMC 0.18 µm presenta una amplia gama de resistencias: RNHR, RNNP0, RNPP0, etc. La elección del tipo de resistencia a utilizar se basa en el valor resistivo que se pretenda integrar. En la **Figura 3-2** se muestra el cuadro de diálogo de *Cadence* donde se ajustan los parámetros de las resistencias.

Figura 3-2. Cuadro de diálogo de Cadence de ajuste de parámetros de resistencias.

Teniendo en cuenta la ecuación (3.2), para obtener el valor resistivo deseado se deben variar tanto el ancho como la longitud de la pista.

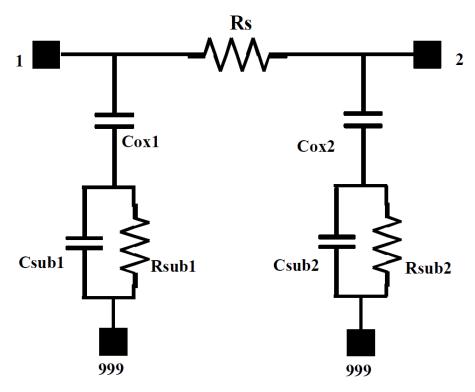

# 3.1.3. Resistencias optimizadas para RF en la tecnología UMC 0.18 µm

En este aparatado se estudiarán las resistencias optimizadas para radiofrecuencia que son RNHR\_RF y RNNPO\_RF/RNPPO\_RF. Durante la simulación de estos tipos de resistencias se utiliza el mismo circuito equivalente, si bien las ecuaciones que determinan los valores de los componentes que configuran dicho modelo varían en función del tipo de resistencia[15]. En la **Figura 3-3** se muestra el circuito equivalente de una resistencia en la tecnología UMC 0.18µm CMOS.

Figura 3-3. Circuito equivalente de una resistencia.

En la **Figura 3-3**, la resistencia  $R_s$  representa el valor resistivo deseado para la resistencia integrada. Por otra parte, la capacidad asociada al óxido de la resistencia se representa con los condensadores  $C_{ox1}$  y  $C_{ox2}$ . Por último, la influencia del sustrato ha sido modelada utilizando una red RC ( $R_{sub}$  y  $C_{sub}$ ).

Las características principales de estos tipos de resistencia son:

- El rango de frecuencias de operación va desde 100 MHz hasta 10 GHz.

- El ancho de pista debe ser mayor a 2 μm.

- La relación entre el largo y el ancho de la pista debe ser menor a 10.

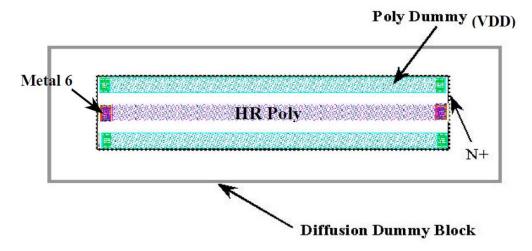

En la **Figura 3-4** se muestra el *layout* típico de una resistencia RNHR\_RF, generada a partir del asistente que presenta el *kit* de diseño de la tecnología.

Figura 3-4. Layout de una resistencia del tipo RNHR\_RF.

En la **Figura 3-5** se muestra el *layout* de una resistencia del tipo RNNPO\_RF, generada a partir del asistente que presenta el *kit* de diseño de la tecnología.

Figura 3-5. Layout de una resistencia del tipo RNNPO\_RF.

La principal diferencia entre estos dos tipos de resistencias, optimizados para RF, radica en el hecho que las RNHR\_RF permiten alcanzar unos valores resistivos más altos debido al uso de un polisilicio altamente resistivo (HR: *High Resistive*).

## 3.2. Condensadores

### 3.2.1. Construcción

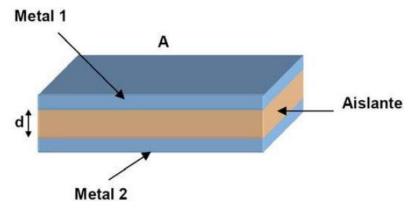

En sistemas integrados, la implementación de condensadores se reduce a la construcción de dos capas planas de metal, separadas por una capa de material aislante. En la **Figura 3-6** se muestra un esquema de la construcción de un condensador integrado.

Figura 3-6. Construcción de un condensador.

A partir de la **Figura 3-6** se puede calcular el valor de la capacidad del condensador mediante la ecuación (3.3):

$$C = \frac{\varepsilon_r \cdot \varepsilon_0 \cdot A}{d} \tag{3.3}$$

Siendo  $\varepsilon_r$  la permitividad relativa del material dieléctrico entre las placas metálicas,  $\varepsilon_0$  la permitividad del vacío, A el área efectiva y d la distancia entre placas metálicas.

## 3.2.2. Condensadores en la tecnología UMC 0.18 µm

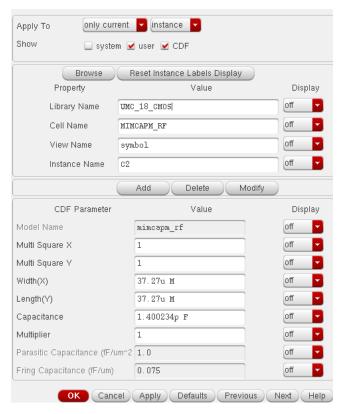

En esta tecnología se dispone de cuatro tipos de condensadores: NCAP\_MM, PCAP\_MM, MIMCAPM\_RF y MIMCAPS\_MM. La elección de un tipo de condensador a utilizar se basa en el valor capacitivo que se pretenda integrar. En la **Figura 3-7** se muestra el cuadro de diálogo donde se ajustan los parámetros de diseño del condensador.

Figura 3-7. Cuadro de diálogo de Cadence de ajuste de parámetros de condensador.

En este caso, se muestra el cuadro de diálogo de Cadence de ajuste de parámetros de un condensador del tipo MIMCAPM\_RF. Teniendo en cuenta que el valor capacitivo del condensador está directamente relacionado con las dimensiones del condensador, variando el ancho y la longitud del condensador se puede obtener el valor capacitivo deseado. Además, para este tipo de condensador los parámetros *Multi Square X* y *Multi Square Y* indican el número de bloques o *fingers* horizontales y verticales, respectivamente.

# 3.2.3. Condensadores optimizados para RF en la tecnología UMC 0.18 µm

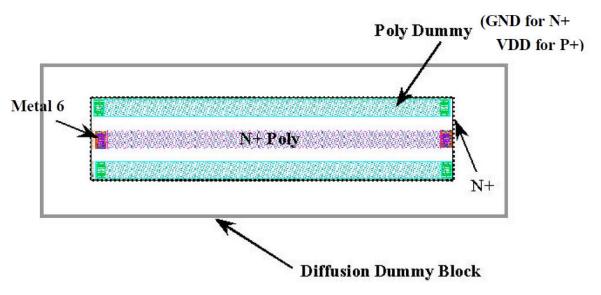

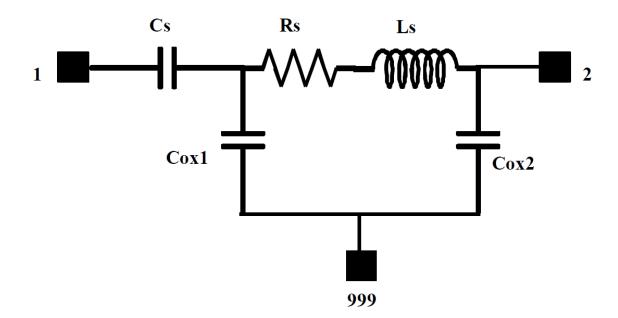

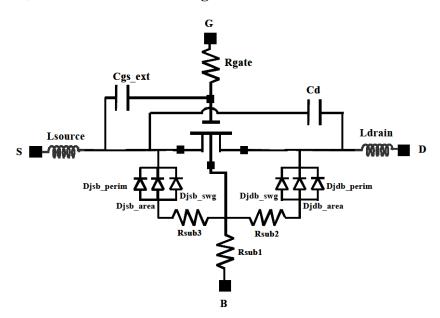

Este apartado se centra en el tipo de condensador optimizado para RF, el MIMCAPM\_RF. Este condensador se basa en un diseño modular que parte de un bloque o *finger* del condensador, el cual es replicado hasta obtener el valor capacitivo deseado. En la **Figura 3-8** se muestra el circuito equivalente del condensador MICAPM\_RF de la tecnología UMC 0.18 μm CMOS: Este condensador es del tipo *Metal-Insulator-Metal* (MIM).

Figura 3-8. Circuito equivalente del condensador MIMCAPM\_RF.

Tal y como se puede observar, el valor capacitivo deseado se representa con el condensador  $C_s$ . En cuanto a  $R_s$  y  $L_s$ , representan la resistencia e inductancia parásitas. Por último, la capacidad parásita que aparece entre el metal de menor nivel y el óxido se modela con los condensadores  $C_{ox1}$  y  $C_{ox2}$ .

Las características principales de este tipo de condensador son:

- El rango de frecuencias de operación va desde los 100 MHz hasta los 10 GHz.

- El tamaño mínimo del condensador es de 10 μm x 10 μm.

- Existe una limitación entre el ancho (W) y la longitud (L) del transistor. Esta limitación se modela con la ecuación (3.4).

$$1 \le \frac{L \cdot nx}{W \cdot ny} \le 6 \tag{3.4}$$

Donde nx y ny son el número de bloques o *fingers* horizontales y verticales, respectivamente.

En la **Figura 3-9** se muestra el *layout* de condensadores del tipo MIMCAPM\_RF, generado a partir del asistente que presenta el *kit* de diseño de la tecnología.

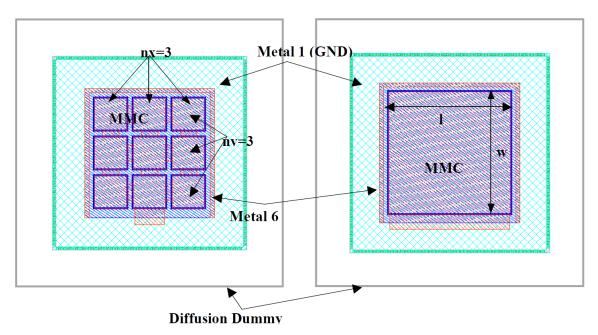

Figura 3-9. Layout de condensadores del tipo MICAPM\_RF.

Si se observa detenidamente la **Figura 3-9**, en la parte izquierda de la misma se muestra un condensador en el que se tiene tres bloques horizontales y tres verticales. Por otra parte, en la parte derecha de la **Figura 3-9** se muestra un condensador con un único bloque. El primer tipo de condensador se denomina *Multi-Rectangle* (MR), mientras que el segundo tipo se denomina *Single-Rectangle* (SR).

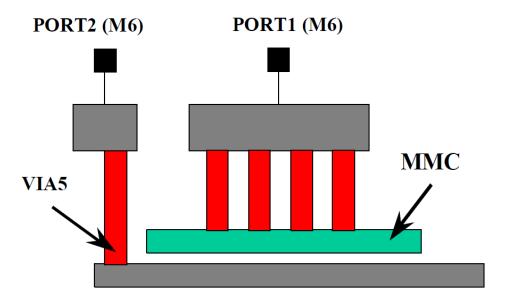

En la **Figura 3-10** se muestra una representación de la sección transversal de un condensador del tipo MIMCAPM\_RF.

Figura 3-10. Sección transversal del *layout* de un condensador MICAPM\_RF.

Como se puede observar en la **Figura 3-10**, el puerto 1 se conecta a la placa conductora superior del condensador, mientras que el puerto 2 se conecta a la placa inferior. Ambos puertos están fabricados con la capa de metal superior, que se corresponde con el Metal6 en esta tecnología.

### 3.3.Bobinas

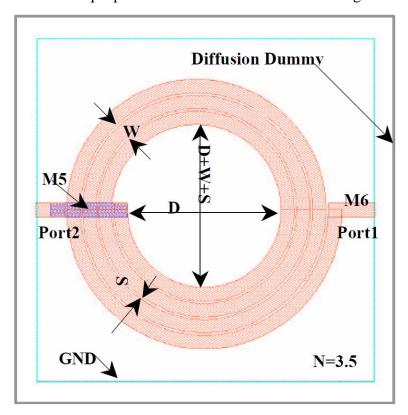

### 3.3.1. Construcción

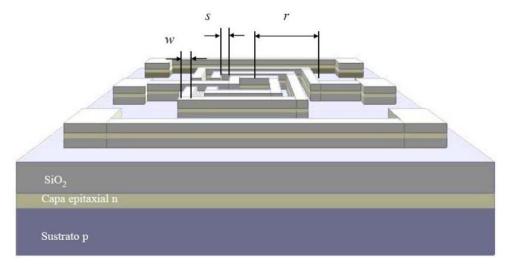

Típicamente, un inductor integrado se diseña generando una espiral con pistas metálicas sobre un sustrato determinado. Debido a que uno de los extremos de la espiral queda en el interior de la misma, será necesario disponer de al menos dos niveles de metal para poder acceder a este terminal. Al trozo de pista que pasa por debajo de la espiral principal para acceder al terminal interior se le conoce como *underpass* o *cross-under*. En la **Figura 3-11** se muestra una bobina espiral cuadrada simple, donde se puede apreciar la disposición del *underpass*, además de los parámentros geométricos más importantes de una bobina. Concretamente, se muestra el radio (r), la anchura (w) y la separación entre pistas (s).

Figura 3-11. Modelo de una bobina cuadrada simple.

### 3.3.2. Funcionamiento

Un inductor se caracteriza principalmente por su factor de calidad, cuyo valor se calcula con la ecuación (3.5):

$$Q = -\frac{\text{Im}(Y_{11})}{\text{Re}(Y_{11})}$$

(3.5)

En la práctica, el factor de calidad de los inductores integrados sobre silicio suele ser bastante deficiente debido a las pérdidas asociadas al dispositivo. La respuesta de los inductores integrados sigue siendo objeto de investigación, sin embargo, los fenómenos físicos causantes de la degradación de la misma han sido identificados. Los fenómenos más relevantes están asociados a las pérdidas en el sustrato, pérdidas en los metales por su alta resistividad, además de las pérdidas causadas por el efecto pelicular (*skin effect*) y por las corrientes de torbellino (*eddy currents*) [16]. Estas dos últimas fuentes de pérdidas, el efecto pelicular y las corrientes de torbellino, no son fáciles de modelar.

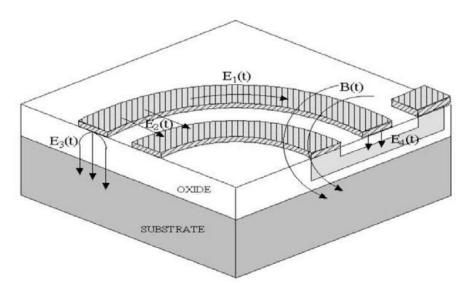

Cuando se aplica tensión en los extremos de una espiral, aparecen campos eléctricos y magnéticos como los que se muestran en la **Figura 3-12**:

- El campo magnético B (t) está originado por la corriente de alterna que circula por las espirales. Es el responsable del comportamiento inductivo del dispositivo, así como de las corrientes inducidas en el sustrato y en las pistas de la espiral. Teniendo en cuenta que este campo magnético atraviesa el sustrato y las pistas de la espira, se inducen *eddy currents* en ambas.

- E<sub>1</sub> (t) es el campo eléctrico en las pistas de la espiral. Produce la corriente de conducción a la cual están asociadas unas pérdidas óhmicas en las pistas debido a la resistividad de los conductores.

- E<sub>2</sub> (t) es el campo eléctrico entre las pistas de la espiral y está causado por la diferencia de tensión entre los conductores. Ocasiona el acoplamiento capacitivo entre ellos actuando el óxido como dieléctrico.

- E<sub>3</sub> (t) es el campo eléctrico entre la espiral y el sustrato, el cual está causado por la diferencia de tensión existente entre ambos. Genera el acoplamiento capacitivo entre la espira y el sustrato, además de pérdidas óhmicas en el sustrato.

- E<sub>4</sub> (t) es el campo eléctrico que aparece entre la espiral y el *underpass*. Este campo genera una capacidad parásita en paralelo a la bobina.

Figura 3-12. Campos eléctricos y magnéticos en un inductor integrado.

### 3.3.3. Modelo de la bobina

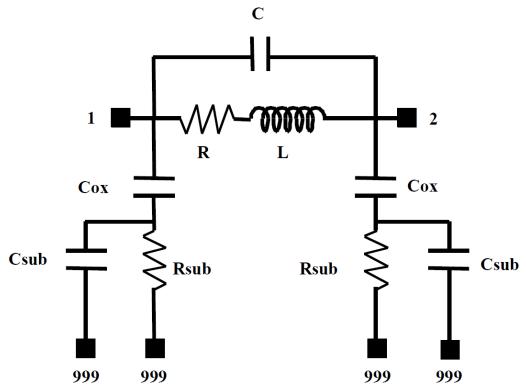

El modelo clásico se basa en la interpretación de los fenómenos físicos estudiados en el apartado anterior. La estructura de este modelo, considerando al inductor como un dispositivo de dos puertos, se muestra en la **Figura 3-13**.

Figura 3-13. Modelo clásico de un inductor espiral integrado.

En la **Figura 3-13** se puede observar que en serie con la inductancia deseada L, aparece una resistencia R que representa las pérdidas óhmicas generadas por  $E_1$  (t) (ver **Figura 3-12**). El condensador C modela el acoplamiento capacitivo generado por  $E_2$  (t) y  $E_4$  (t). El resto

de elementos que aparecen en el circuito describen los efectos del sustrato. En particular, los condensadores  $C_{ox}$  representan las capacidades que aparecen entre la espiral y el sustrato, mientras que los condensadores  $C_{sub}$  representan las capacidades parásitas asociadas al sustrato. Por último, las resistencias  $R_{sub}$  modelan las pérdidas óhmicas del sustrato.

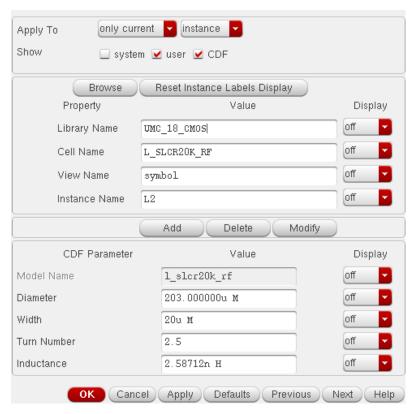

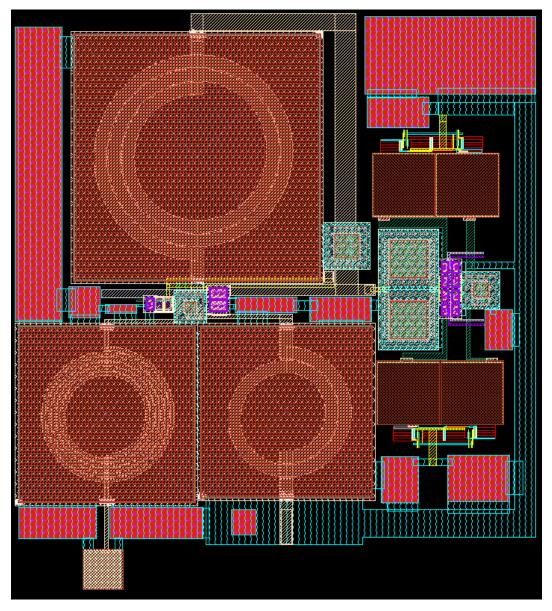

## 3.3.4. Bobinas en la tecnología UMC 0.18 µm

La tecnología de UMC 0.18 µm dispone de un único modelo de bobina integrada, el L\_SLCR20K\_RF. En la **Figura 3-14** se muestra el cuadro de diálogo en el que se pueden ajustar los parámetros de la bobina.

Figura 3-14. Cuadro de diálogo de Cadence de ajuste de parámetros de bobinas.

Para obtener el valor de inductancia deseado, se varían los parámetros geométricos de la bobina. Concretamente, los parámetros que se varían son el ancho de la pista, el diámetro de la bobina y el número de vueltas de la espira.

Las características principales de este tipo de bobinas son:

- El rango de frecuencias de operación va desde 100 MHz hasta 10 GHz.

- El rango de valores de inductancia efectivos está entre 1 y 12 nH a la frecuencia de 300 MHz.

- El ancho de la capa de metal superior debe tener un valor entre 6 y 20 µm.

- El diámetro interior de la bobina debe estar en un rango entre 126 y 238 μm.

- El número de vueltas debe estar entre 1.5 y 5.5, con pasos de 1. Es decir, solo puede tomar los siguientes valores: 1.5, 2.5, 3.5, 4.5, 5.5.

- El espacio entre las pistas metálicas está fijado a 2 μm.

- El espesor de la capa de metal superior es de 20 KA.

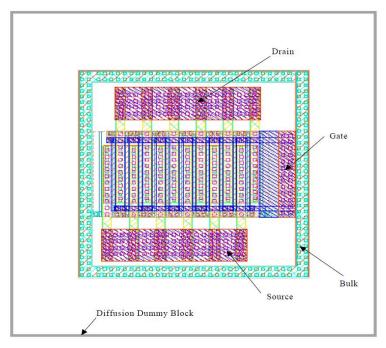

En la **Figura 3-15** se muestra el *layout* de una bobina del tipo L\_SLCR20K\_RF, generada a partir del asistente que presenta el *kit* de diseño de la tecnología.

Figura 3-15. Layout de una bobina del tipo L\_SLCR20K\_RF.

### 3.4.El Transistor MOSFET

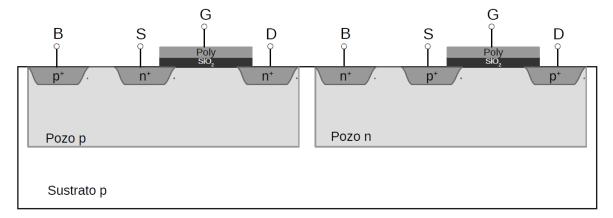

## 3.4.1. Construcción

En la **Figura 3-16** se muestra una sección transversal de dos transistores MOS, uno tipo n y el otro tipo p. En el caso del transistor tipo n, el surtidor (S: *Source*) y el drenador (D: *Drain*) se construyen sobre difusiones n+, sobre un sustrato p. Por otra parte, en el transistor tipo p el surtidor y el drenador están formados con difusiones tipo p+ sobre un pozo n. Tanto en el transistor tipo n como en el transistor tipo p, la puerta (G: *Gate*) está aislada del sustrato mediante una capa de óxido de silicio (SiO<sub>2</sub>). Además, en el caso de transistor tipo n, el sustrato se debe conectar a la tensión más negativa para eliminar los

diodos rectificadores que aparecen en las uniones del surtidor y el drenador. En el caso de un transistor tipo p, el sustrato se debe conectar a la tensión más positiva.

Figura 3-16. Sección transversal de transistores MOS.

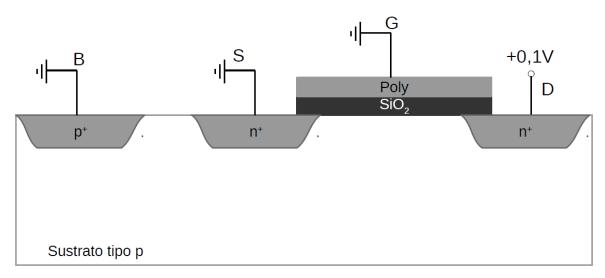

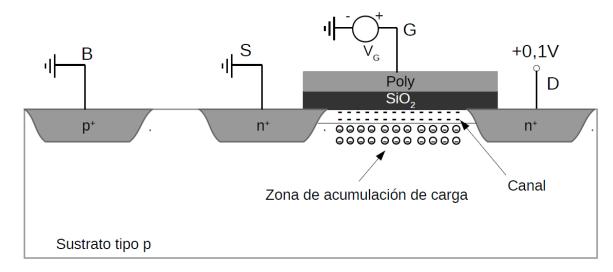

## 3.4.2. Funcionamiento

En la **Figura 3-17** se muestra un MOSFET tipo n al cual se le aplican tensiones externas. Suponiendo que la tensión entre la puerta y el surtidor es nula  $(V_{GS})$ , y la tensión entre el drenador y el surtidor es positiva  $(V_{DS})$ , no circulará corriente entre los terminales de drenador y surtidor. En esta situación se dice que el transistor MOSFET se encuentra en corte.

Figura 3-17. Transistor MOSFET tipo n en corte.

A medida que se aumenta la tensión  $V_{GS}$ , los huecos que se encuentran en el sustrato p son repelidos por la puerta, dejando iones negativos en su lugar. De esta manera se crea una región de enriquecimiento o de acumulación de carga. Si  $V_{GS}$  sigue aumentando, se ensanchará la zona de acumulación de carga y, por tanto, aumenta el potencial de la interfaz

óxido-silicio. Cuando este potencial alcanza una tensión umbral (V<sub>TH</sub>), los electrones fluyen desde el surtidor al drenador. De esta forma se crea bajo la puerta el canal entre el surtidor y el drenador. En este caso, se dice que el transistor se encuentra en la región de tríodo o zona óhmica. La **Figura 3-18** muestra un transistor MOSFET tipo n cuando se encuentra en zona óhmica.

Figura 3-18. Transistor MOSFET tipo n en zona óhmica.

En la zona óhmica, la ecuación (3.6) determina la corriente de drenador del MOSFET:

$$I_{D} = \mu_{n} C_{ox} \frac{W}{L} \left[ \left( V_{GS} - V_{TH} \right) \cdot V_{DS} - \frac{1}{2} V_{DS}^{2} \right]$$

(3.6)

#### Donde:

- $\mu_n$  es la movilidad de los electrones.

- C<sub>ox</sub> es la capacidad de óxido de la puerta por unidad de área.

- L es la longitud del canal del transistor (µm).

- W es el ancho del canal del transistor (µm).

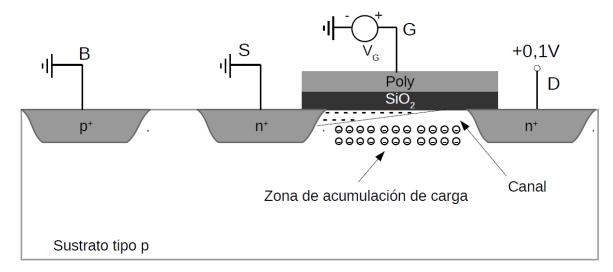

Como ya se ha comentado anteriormente, cuando el valor de  $V_{GS}$  es mayor que  $V_{TH}$ , la densidad de los portadores libres en el canal aumenta, dando como resultado un mayor nivel de  $I_D$ . Sin embargo, si se mantiene  $V_{GS}$  constante y sólo se aumenta el nivel de  $V_{DS}$ , la corriente de drenador alcanza un nivel de saturación cuando su valor es superior a  $V_{GS}$ - $V_{TH}$ . Esta saturación se debe a un estrechamiento del canal (*pinch-off*), tal y como se muestra en la **Figura 3-19**.

Figura 3-19. Transistor MOSFET tipo n en zona de saturación.

En esta situación la corriente de drenador se calcula con la ecuación(3.7):

$$I_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L} \cdot \left( V_{GS} - V_{TH} \right)^2 \tag{3.7}$$

De la misma manera que se ha analizado el transistor MOSFET tipo n, el transistor tipo p mantiene las mismas ecuaciones. Sin embargo, en el caso del tipo p el sentido de la corriente  $I_D$  es contrario al caso del tipo n. Esto se debe a que en un tipo p los huecos son mayoritarios y fluyen en el sentido contrario a los electrones [17].

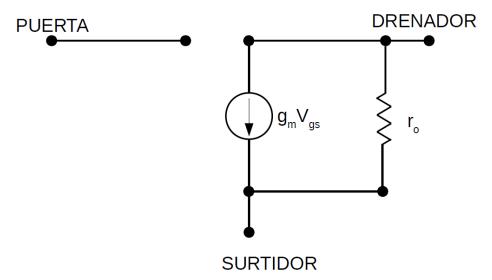

## 3.4.3. Modelo de pequeña señal

En la **Figura 3-20** se muestra el modelo simplificado de pequeña señal de un transistor MOSFET.

Figura 3-20. Modelo simplificado de pequeña señal de un transistor MOSFET.

### Donde:

- r<sub>o</sub> representa la parte real de la impedancia de salida del transistor.

- g<sub>m</sub> es la transconductancia del transistor y se calcula según la ecuación (3.8).

$$g_{m} = K \cdot \frac{W}{L} \cdot \left(V_{GS} + V_{T}\right) \tag{3.8}$$

Donde K es la constante de transconductancia del transistor.

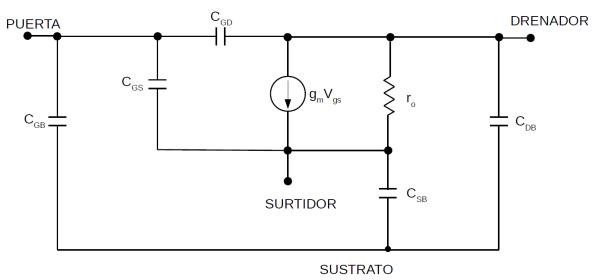

Sin embargo, en el modelo simplificado no se han tenido en cuenta las capacidades parásitas, las cuales pueden ser de dos tipos: capacidades de la zona de carga espacial y capacidades de la zona del óxido. En la **Figura 3-21** se muestra el modelo completo en pequeña señal de un transistor MOSFET.

Figura 3-21. Modelo completo de pequeña señal de un transistor MOSFET.

En cuanto a las capacidades de la zona de carga espacial, éstas se producen en las uniones PN debido a la presencia de cargas en las zonas N y P con igual magnitud pero con polaridad de carga opuesta. Estas capacidades vienen dadas por las ecuaciones (3.9) y (3.10).

$$C_{DB} = \frac{C_{DB0}}{\left(1 - \frac{V_{DB}}{\psi_0}\right)^m}$$

(3.9)

$$C_{SB} = \frac{C_{SB0}}{\left(1 - \frac{V_{SB}}{\psi_0}\right)^m}$$

(3.10)

### Donde:

- C<sub>DB0</sub> y C<sub>SB0</sub> son las densidades de la capacidad de la unión cuando la polarización es nula.

- V es la tensión directa de la unión.

- $\Psi_0$  es la barrera de potencial.

- m es la constante dependiente de la unión.

En cuanto a las capacidades en la zona del óxido, éstas aparecen entre dos zonas conductoras separadas por óxido, cada una sometida a una tensión distinta. El valor de estas capacidades depende de las variables de diseño y de las dispersiones en el proceso de fabricación.

Las principales capacidades de óxido son:

- C<sub>GB</sub>: Capacidad de óxido entre puerta y sustrato.