# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### TRABAJO FIN DE GRADO

## "DISEÑO DE UN AMPLIFICADOR INTEGRADO EN CONFIGURACIÓN CHIREIX EN TECNOLOGÍA GAN"

Titulación: Grado en Ingeniería en Tecnologías de la Telecomunicación

Mención: Sistemas electrónicos

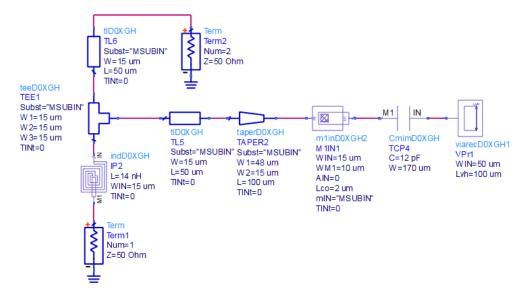

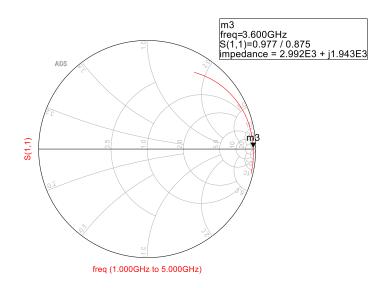

Autor: Ayoze Diaz Carballo

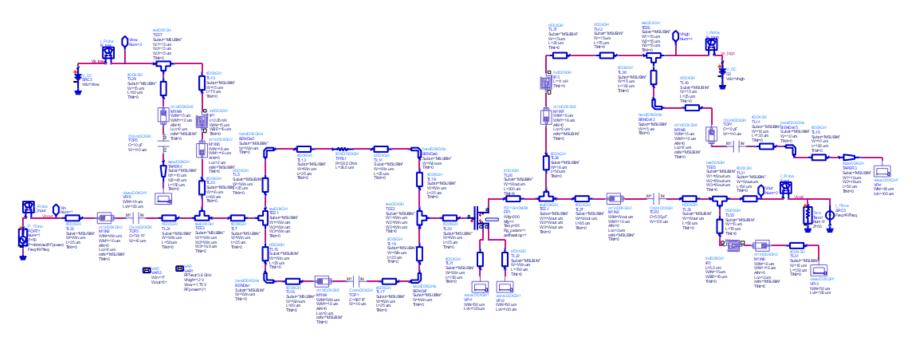

Tutor: Dr. Francisco Javier Del Pino Suárez

Cotutora: Victoria Díez Acereda

Fecha: Enero de 2019

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### TRABAJO FIN DE GRADO

# "DISEÑO DE UN AMPLIFICADOR INTEGRADO EN CONFIGURACIÓN CHIREIX EN TECNOLOGÍA GAN" HOJA DE EVALUACIÓN

| Calificació | n:           |

|-------------|--------------|

| Presidente  |              |

|             |              |

|             |              |

| Vocal       | Secretario/a |

Fecha: Enero de 2019

### Tabla de contenidos

| PARTE I: MEMORIA                                  | 1  |

|---------------------------------------------------|----|

| 1. Introducción                                   | 3  |

| 1.1. Antecedentes                                 | 3  |

| 1.2. Objetivos                                    | 4  |

| 1.3. Estructura de la memoria                     | 5  |

| Estudio de la tecnología                          | 7  |

| 2.1. Tecnología 5G                                | 7  |

| 2.1.1. Bandas de frecuencia                       | 8  |

| 2.1.2. Aplicaciones                               | 9  |

| 2.2. Tecnología GaN                               | 11 |

| 2.2.1. Comparativa del GaN frente al Si y el GaAs | 11 |

| 2.2.2. Comparativa con el SiC                     | 13 |

| 2.3. Resumen                                      | 14 |

| 3. Estudio de los amplificadores de potencia      | 15 |

| 3.1. Amplificadores de potencia                   | 15 |

| 3.1.1. Transistores                               | 15 |

| 3.1.1.1. Funcionamiento                           | 16 |

| 3.1.1.2. Curvas características                   | 18 |

| 3.1.2. Estabilidad                                | 19 |

| 3.1.2.1. Estabilidad par                          | 20 |

| 3.1.2.2. Estabilidad impar                        | 21 |

| 3.1.3. Ganancia                                   | 22 |

| 3.1.4. Eficiencia                                 | 22 |

| 3.1.4.1. Eficiencia del drenador                  | 22 |

| 3.1.4.2 PAF                                       | 22 |

| 3.1.5. Back-Off                                                     | 23 |

|---------------------------------------------------------------------|----|

| 3.1.6. Clases                                                       | 24 |

| 3.1.6.1. Clase A                                                    | 26 |

| 3.1.6.2. Clase B                                                    | 26 |

| 3.1.6.3. Clase AB                                                   | 26 |

| 3.1.6.4. Clase C                                                    | 27 |

| 3.2. Amplificador Outphasing Chireix                                | 27 |

| 3.2.1. Combinadores                                                 | 28 |

| 3.3. Resumen                                                        | 31 |

| 4. Diseño del amplificador clase B ideal                            | 33 |

| 4.1. Obtención de las curvas del transistor                         | 33 |

| 4.2. Estabilidad de los transistores                                | 36 |

| 4.3. Load-Pull y Source-Pull                                        | 40 |

| 4.3.1. Aplicación práctica                                          | 40 |

| 4.4. Adaptación de impedancias                                      | 44 |

| 4.5. Resumen                                                        | 50 |

| 5. Diseño del amplificador clase B real                             | 51 |

| 5.1. Sustitución del transistor                                     | 51 |

| 5.2. Sustitución de la red de estabilización por componentes reales | 52 |

| 5.3. Sustitución de las redes de adaptación                         | 59 |

| 5.3.1. Red de adaptación de entrada                                 | 65 |

| 5.3.2. Red de adaptación de salida                                  | 72 |

| 5.3.3. Redes de polarización                                        | 82 |

| 5.4. Resumen                                                        | 92 |

| 6. Implementación del amplificador Chireix                          | 95 |

| 6.1. Construcción del amplificador Chireix                          | 95 |

| 6.2 Realización del combinador                                      | 96 |

| 6.3. I    | Estabilidad del amplificador Chireix   | 102 |

|-----------|----------------------------------------|-----|

| 6.3       | .1. Estabilidad par                    | 102 |

| 6         | S.3.1.1. Pequeña señal                 | 102 |

| 6         | 6.3.1.2. Gran señal                    | 103 |

| 6.3       | 3.2. Estabilidad impar                 | 105 |

| 6.4.      | Creación del <i>layout</i>             | 107 |

| 6.5. I    | Resultados finales                     | 109 |

| 7. Con    | clusiones y líneas futuras             | 113 |

| 7.1. (    | Conclusiones                           | 113 |

| 7.1       | .1. Resultados                         | 114 |

| 7.2. I    | Líneas futuras                         | 115 |

| PARTE II: | BIBLIOGRAFÍA                           | 117 |

| Bibliogr  | afía                                   | 119 |

| PARTE III | : PLIEGO DE CONDICIONES                | 123 |

| PARTE IV  | /: PRESUPUESTO                         | 127 |

| P1.       | Trabajo tarifado por tiempo empleado   | 129 |

| P2.       | Amortización del inmovilizado material | 130 |

| P2.1.     | Amortización del material hardware     | 130 |

| P2.2.     | Amortización material software         | 130 |

| P3.       | Redacción del trabajo                  | 131 |

| P4.       | Derechos de visado del COITT           | 131 |

| P5.       | Costes de tramitación y envío          | 132 |

| P6.       | Material fungible                      | 132 |

| P7.       | Aplicación de impuestos y coste total  | 133 |

### Índice de figuras

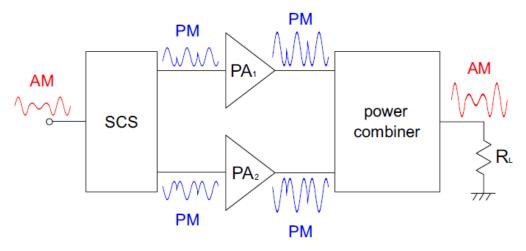

| Figura 1.1. Estructura de un amplificador Chireix                                      | 4        |

|----------------------------------------------------------------------------------------|----------|

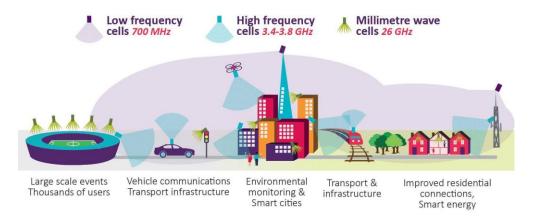

| Figura 2.1. Bandas de frecuencias 5G.                                                  | 9        |

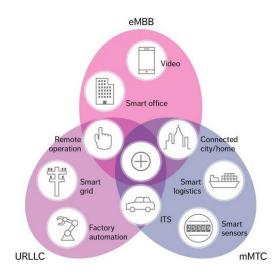

| Figura 2.2. Los distintos servicios que ofrecerá el 5G y algunas de sus aplicad        |          |

|                                                                                        |          |

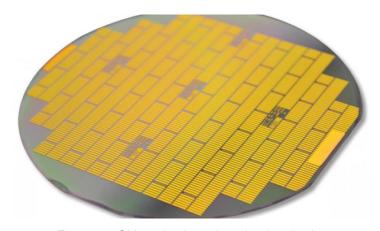

| Figura 2.3. Obleas donde se depositan los circuitos                                    |          |

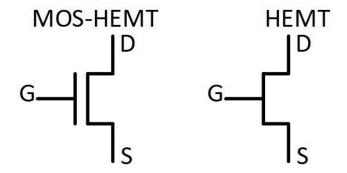

| Figura 3.1. Símbolo de un transistor HEMT.                                             | 16       |

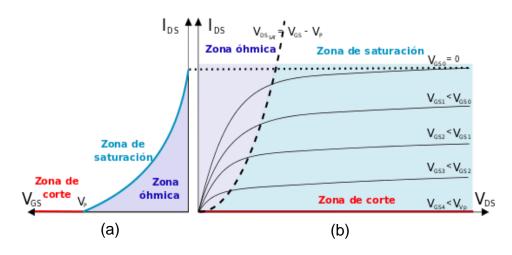

| Figura 3.2. (a) Curva de transferencia y (b) curva característica del drenactransistor |          |

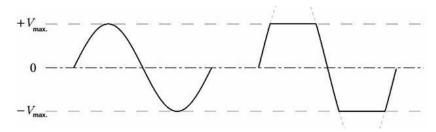

| Figura 3.3. Señal de salida de un transistor (izquierda) y señal en comp               |          |

| (derecha)                                                                              | 23       |

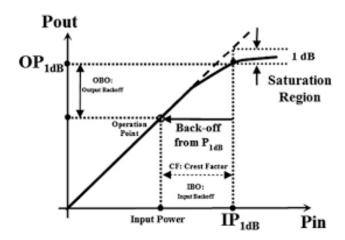

| Figura 3.4. Representación gráfica del back-off de entrada y de salida                 | 24       |

| Figura 3.5. Clases de amplificadores según el ángulo de conducción frenteficiencia.    |          |

| Figura 3.6. Circuito simplificado de la salida de un amplificador outphasing ide       | eal. (a) |

| Sin compensación. (b) Con compensación (Chireix)                                       | 28       |

| Figura 3.7. Trayectorias de las cargas para un barrido de la fase de 0º-90º.           | (a) Sin  |

| compensación. (b) Con compensación (Chireix)                                           | 29       |

| Figura 3.8. Curvas de la eficiencia frente al OBO de los amplificadores Ch             |          |

| Figura 3.9. Arquitecturas para el combinador de salida de un amplificador C            | Chireix. |

| Figura 4.1. Modelos de los transistores ofrecidos por OMMIC                            |          |

| Figura 4.2. Circuito para la obtención de las curvas del transistor                    | 35       |

| Figura 4.3. Curvas características del transistor                                      | 35       |

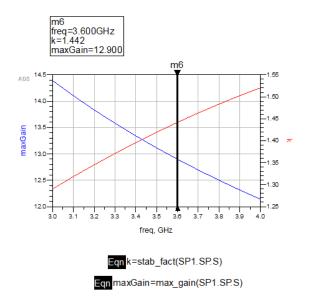

| Figura 4.4. Circuito para obtener los rangos de estabilidad                            | 36       |

| Figura 4.5. (a) Red de estabilización RC en serie. (b) Red de estabilización           |          |

| paralelo                                                                               |          |

| Figura 4.6. Estabilidad (rojo) y ganancia (azul) del transistor frente a la frecu      | uencia.  |

| Figura 4.7. Circuito con la red de estabilización.                                     |          |

| ı iuura 4.7. Oliculu cur ia ieu ue eslabilizaciur                                      | JO       |

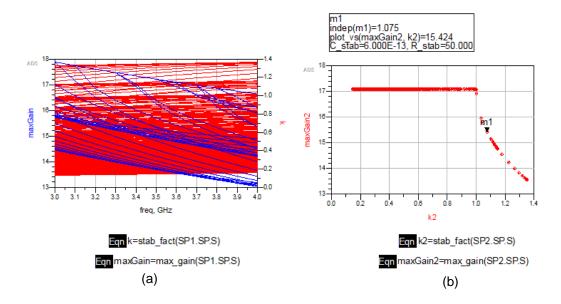

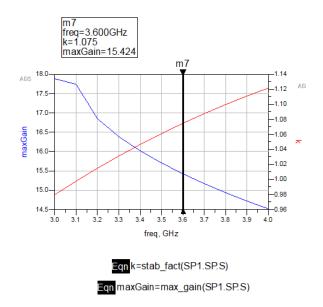

| Figura 4.8. (a) Barrido de la estabilidad (rojo) y la ganancia (azul) del transistor       |

|--------------------------------------------------------------------------------------------|

| frente a la frecuencia. (b) Barrido de la ganancia frente a la estabilidad del transistor. |

|                                                                                            |

| Figura 4.9. Estabilidad del amplificador tras introducir una red de estabilización. 39     |

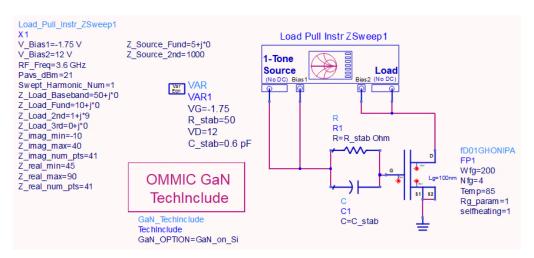

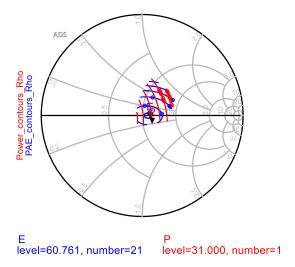

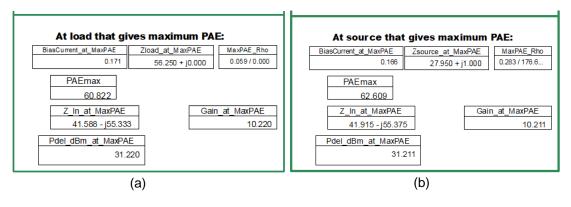

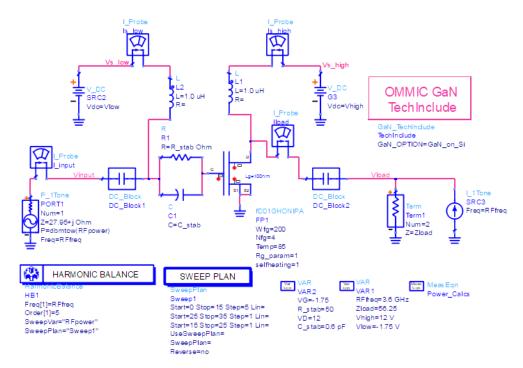

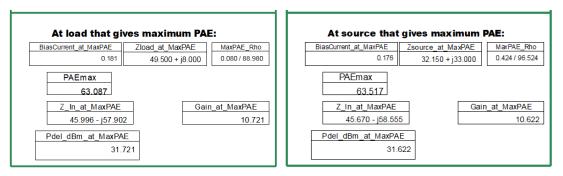

| Figura 4.10. Esquemático utilizado para la realización del Load-Pull41                     |

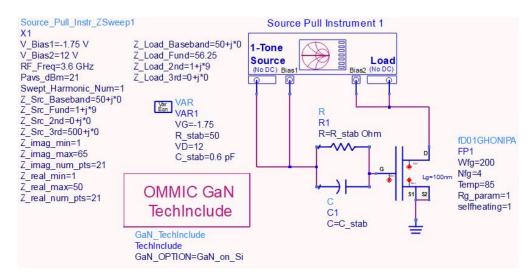

| Figura 4.11. Esquemático utilizado para la realización del Source-Pull 41                  |

| Figura 4.12. Curvas de PAE (azul) y de potencia (rojo)                                     |

| Figura 4.13. (a) Impedancia óptima de carga. (b) Impedancia óptima de fuente 42            |

| Figura 4.14. Esquemático para la comprobación de la correcta realización del               |

| Load/Source-Pull43                                                                         |

| Figura 4.15. Arriba los resultados de la comprobación. Abajo la potencia transmitida       |

| (azul) y el PAE (rojo) frente a la potencia de entrada                                     |

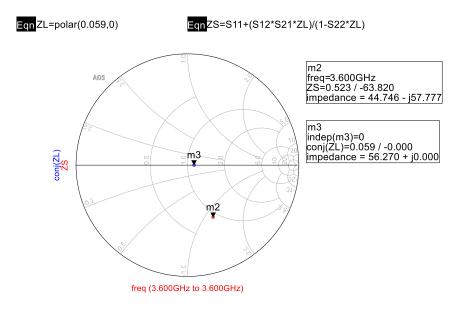

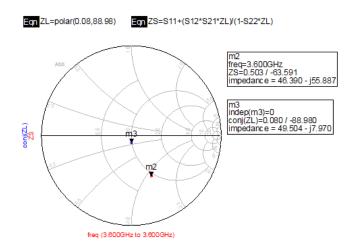

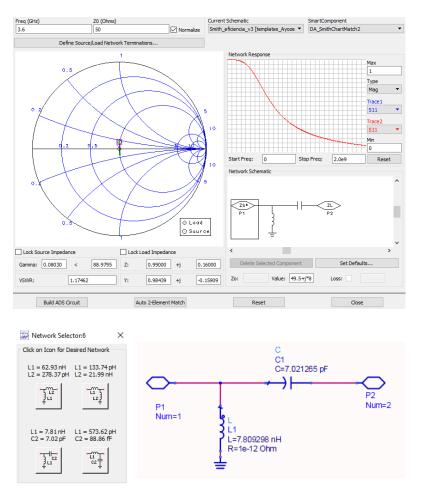

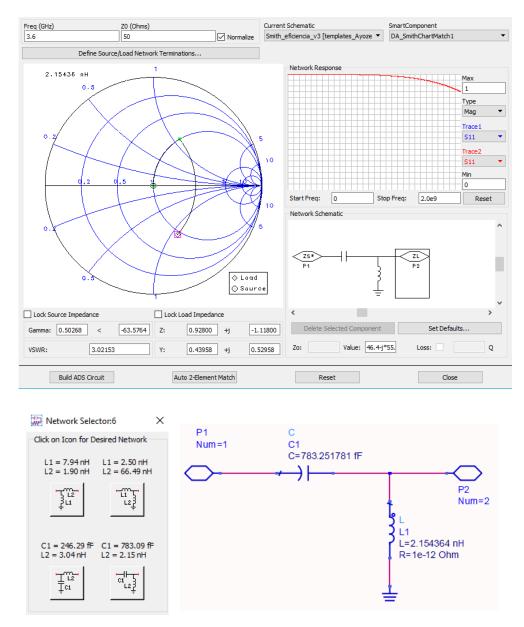

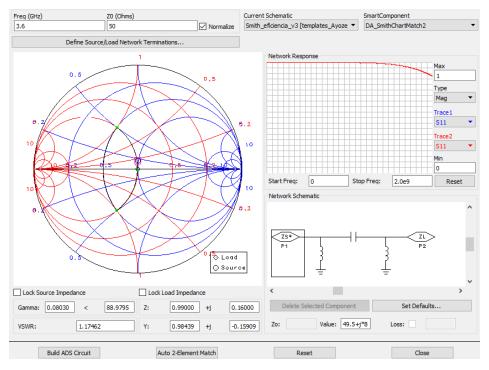

| Figura 4.16. Componente de Smith Chart empleado para la adaptación 44                      |

| Figura 4.17. Adaptación simultánea de la entrada y de la salida 45                         |

| Figura 4.18. Cálculo de Zs representado en la carta de Smith 45                            |

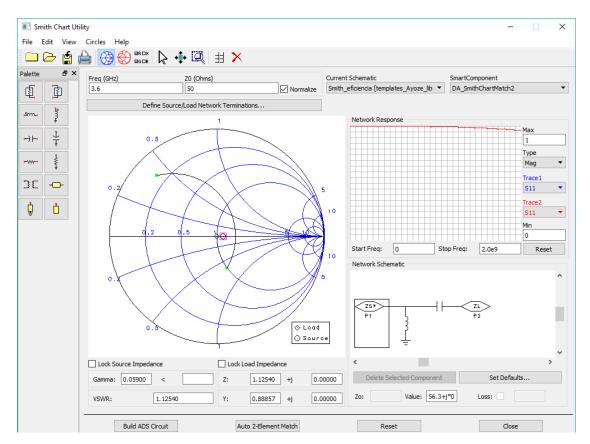

| Figura 4.19. Ventana de configuración del componente de la carta de Smith.                 |

| Adaptación a la salida46                                                                   |

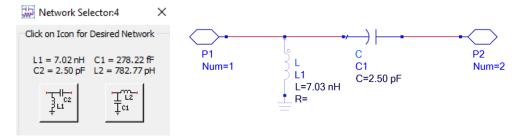

| Figura 4.20. Red de adaptación de salida construida mediante la herramienta                |

| "Smith Chart"                                                                              |

| Figura 4.21. Arriba la ventana de configuración del componente de la carta de              |

| Smith. Abajo la red de adaptación construida. Adaptación a la entrada 47                   |

| Figura 4.22. Esquemático para la comprobación del correcto diseño de las redes             |

| de adaptación48                                                                            |

| Figura 4.23. Arriba los resultados de la comprobación. Abajo la potencia transmitida       |

| (azul) y el PAE (rojo) frente a la potencia de entrada49                                   |

| Figura 4.24. Resultados de la comprobación de la correcta adaptación en pequeña            |

| señal49                                                                                    |

| Figura 5.1. Incorporación de las vías de conexión a tierra del transistor 52               |

| Figura 5.2. Layout del transistor 52                                                       |

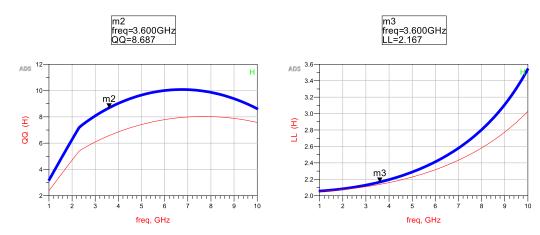

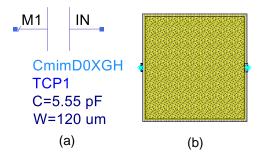

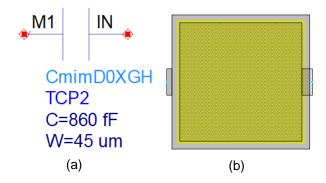

| Figura 5.3. Comparativa entre los dos modelos de condensador ofrecidos por                 |

| OMMIC53                                                                                    |

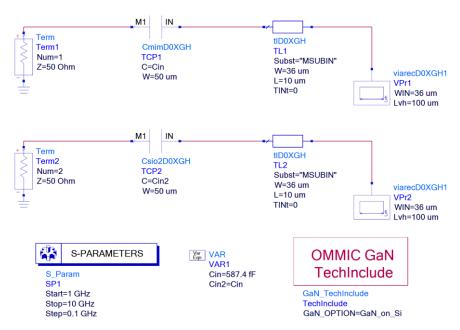

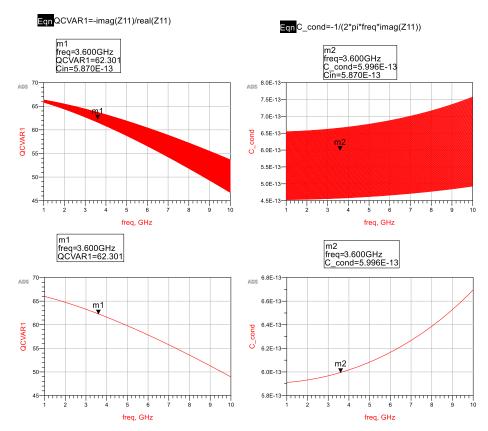

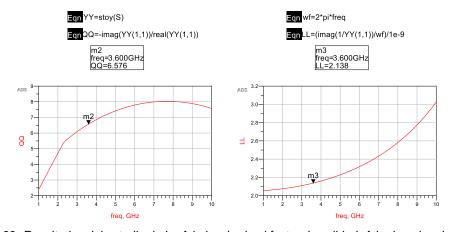

| Figura 5.4. Arriba el factor de calidad y la capacidad de CmimD0XGH. Abajo el              |

| factor de calidad y la capacidad de Csio2D0XGH54                                           |

| Figura 5.5. Estudio del condensador C Stab de la red de estabilización 55                  |

| Figura 5.6.(Arriba) Resultados del estudio de Cin con un barrido, a la izquierda el                |

|----------------------------------------------------------------------------------------------------|

| factor de calidad y a la derecha el valor de la capacitancia. (Abajo) Resultados con               |

| una capacitancia fija de 586fF56                                                                   |

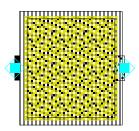

| Figura 5.7. Layout del condensador de la red de estabilización 56                                  |

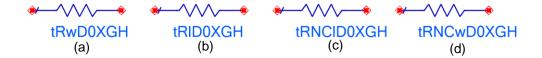

| Figura 5.8. Modelos de resistencias ofrecidos por OMMIC 57                                         |

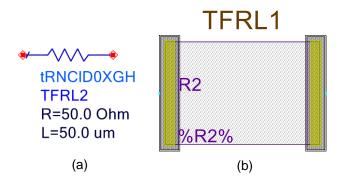

| Figura 5.9. (a) Valor real de R_Stab. (b) Layout de la resistencia de la red de                    |

| estabilidad57                                                                                      |

| Figura 5.10. Comprobación de la estabilidad con los valores reales 58                              |

| Figura 5.11. Estabilidad (rojo) y ganancia (azul) del transistor frente a la frecuencia.           |

| Figura 5.12. Layout de la red de estabilización junto al transistor 59                             |

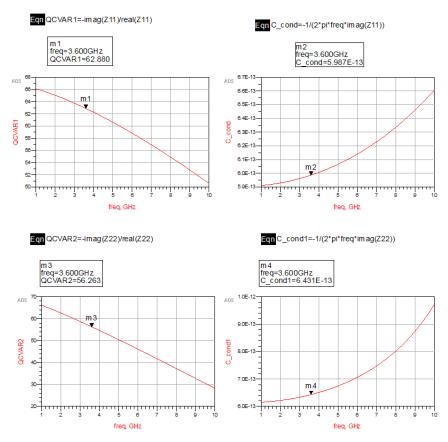

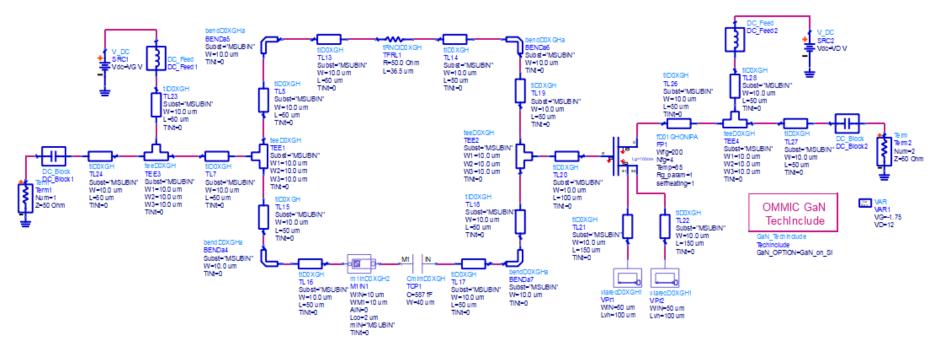

| Figura 5.13. (a) Esquemáticos usados para el Load-Pull y (b) el Source-Pull 60                     |

| Figura 5.14. A la izquierda impedancia óptima de carga. A la derecha impedancia                    |

| óptima de fuente61                                                                                 |

| Figura 5.15. Esquemático para la comprobación de la correcta realización del                       |

| Load/Source-Pull62                                                                                 |

| Figura 5.16. Arriba los resultados de la comprobación. Abajo la potencia transmitida               |

| (azul) y el PAE (rojo) frente a la potencia de entrada                                             |

| Figura 5.17. Cálculo de Z <sub>S</sub> representado en la carta de Smith 64                        |

| Figura 5.18. Arriba la ventana de configuración del componente de la carta de                      |

| Smith. Abajo la red de adaptación construida. Adaptación a la salida 64                            |

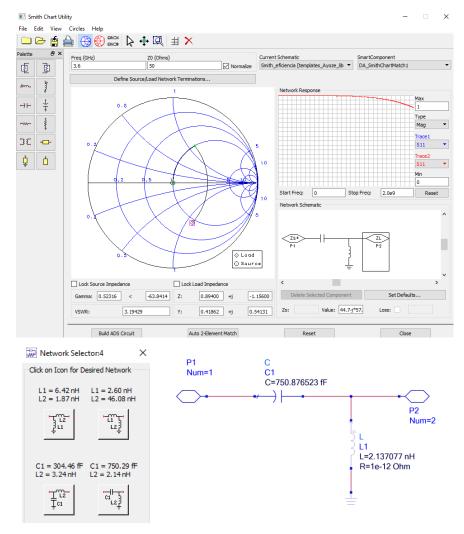

| Figura 5.19. Arriba la ventana de configuración del componente de la carta de                      |

| Smith. Abajo la red de adaptación construida. Adaptación a la entrada 65                           |

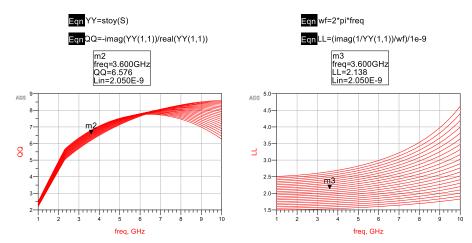

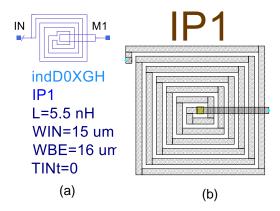

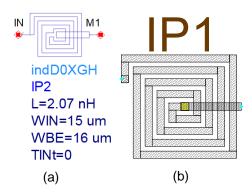

| Figura 5.20. Estudio de la bobina la red de adaptación a la entrada 66                             |

| Figura 5.21. Resultados del estudio de L <sub>in</sub> con un barrido. A la izquierda el factor de |

| calidad. A la derecha el valor de la inductancia67                                                 |

| Figura 5.22. Resultados del estudio de Lin A la izquierda el factor de calidad. A la               |

| derecha el valor de la capacitancia                                                                |

| Figura 5.23. Configuración de los parámetros de la bobina proporcionada en el kit                  |

| de OMMIC68                                                                                         |

| Figura 5.24. Estudio de Lin. Nuevos valores de ancho (azul), viejos valores de ancho               |

| (rojo). A la izquierda el factor de calidad. A la derecha el valor de la bobina 69                 |

| Figura 5.25. Layout de la bobina de la red de adaptación de la entrada 69                          |

| Figura 5.26. (a) Valor real del condensador de la red de adaptación de entrada. (b)    |

|----------------------------------------------------------------------------------------|

| Layout del condensador de la red de adaptación de entrada                              |

| Figura 5.27. Esquemático con los valores reales de la red de adaptación de entrada     |

| 71                                                                                     |

| Figura 5.28. Layout del transistor junto a las redes de estabilización y de adaptación |

| de entrada72                                                                           |

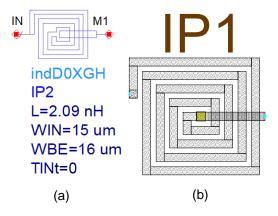

| Figura 5.29. (a) Valor real de la bobina de la red de adaptación de salida. (b) Layout |

| de la bobina de la red de adaptación de salida73                                       |

| Figura 5.30. (a) Valor real del condensador de la red de adaptación de salida. (b)     |

| Layout del condensador de la red de adaptación de salida                               |

| Figura 5.31. Esquemático con los valores reales de la red de adaptación de salida.     |

| 74                                                                                     |

| Figura 5.32. Layout del transistor junto a las redes de estabilización y de adaptación |

| de entrada y salida75                                                                  |

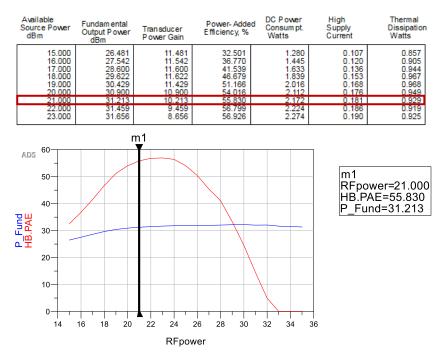

| Figura 5.33. Arriba los resultados de la comprobación. Abajo la potencia transmitida   |

| (azul) y el PAE (rojo) frente a la potencia de entrada                                 |

| Figura 5.34. Ventana de configuración del componente de la carta de Smith.             |

| Adaptación a la salida para una red LCL en pi77                                        |

| Figura 5.35. Red de adaptación a la salida LCL en pi construida77                      |

| Figura 5.36. (a) Valor real de la bobina de la red de adaptación de salida (choke).    |

| (b) Layout de la bobina de la red de adaptación de salida (choke) 78                   |

| Figura 5.37. (a) Valor real de la bobina de la red de adaptación de salida. (b) Layout |

| de la bobina de la red de adaptación de salida                                         |

| Figura 5.38. (a) Valor real del condensador de la red de adaptación de salida. (b)     |

| Layout del condensador de la red de adaptación de salida                               |

| Figura 5.39. Esquemático con los valores reales de la red de adaptación de salida.     |

| Red LCL en pi80                                                                        |

| Figura 5.40. Layout del transistor junto a las redes de estabilización, de adaptación  |

| de entrada y la red LCL en pi a la salida 81                                           |

| Figura 5.41. Arriba los resultados de la comprobación. Abajo la potencia transmitida   |

| (azul) y el PAE (rojo) frente a la potencia de entrada                                 |

| Figura 5.42. Resultados de la comprobación de la correcta adaptación en pequeña        |

| señal. Red de adaptación LCL en pi82                                                   |

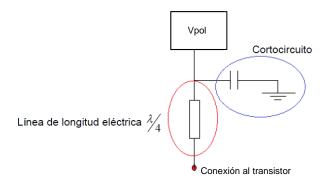

| Figura 5.43 Red de polarización 83                                                     |

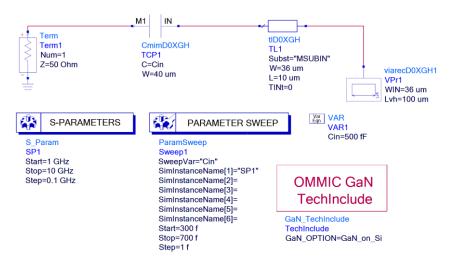

| Figura 5.44. Estudio del condensador de la red de polarización                             | 83     |

|--------------------------------------------------------------------------------------------|--------|

| Figura 5.45. Resultados del barrido del condensador de la red de polarización              | ı 84   |

| Figura 5.46. Layout del condensador de la red de polarización                              | 84     |

| Figura 5.47. Resultado del condensador de la red de polarización                           | 85     |

| Figura 5.48. Estudio de la línea λ /4 de la red de polarización                            | 85     |

| Figura 5.49. Resultado de la línea λ/4 de la red de polarización                           | 86     |

| Figura 5.50. Sustitución de la línea λ/4 de la red de polarización por una bobir           | าล.86  |

| Figura 5.51. Resultado de la bobina de la red de polarización                              | 87     |

| Figura 5.52. Layout de la bobina                                                           | 87     |

| Figura 5.53. Esquema de la red de polarización                                             | 88     |

| Figura 5.54. Resultado de la red de polarización                                           | 88     |

| Figura 5.55. Esquemático con los valores reales de las redes de polarización.              | 89     |

| Figura 5.56. Layout del transistor junto a las redes de estabilización, de adapt           | ación  |

| de entrada y la red salida con sus respectivas redes de polarización                       | 90     |

| Figura 5.57. Arriba los resultados de la comprobación. Abajo la potencia transr            | nitida |

| (azul) y el PAE (rojo) frente a la potencia de entrada                                     | 90     |

| Figura 5.58. Resultados de la comprobación de la correcta adaptación en peq                | ueña   |

| señal. Red de adaptación LCL en pi                                                         | 91     |

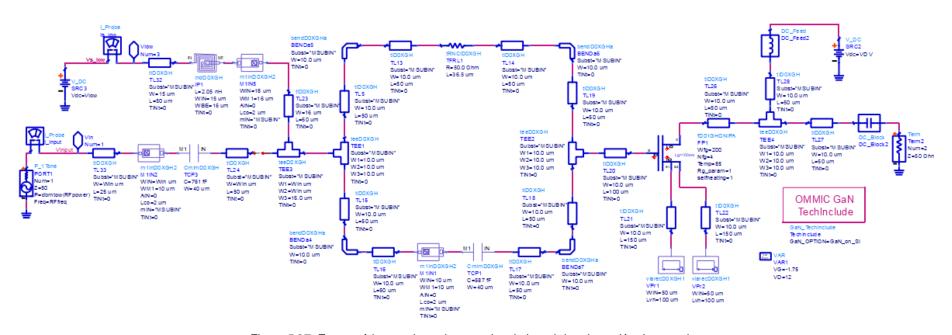

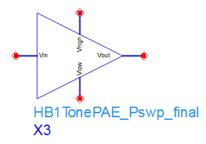

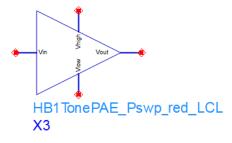

| Figura 6.1. Símbolo del esquemático del amplificador con red LC y polarización             | real.  |

|                                                                                            | 95     |

| Figura 6.2. Símbolo del esquemático del amplificador con red LCL en pi                     | 95     |

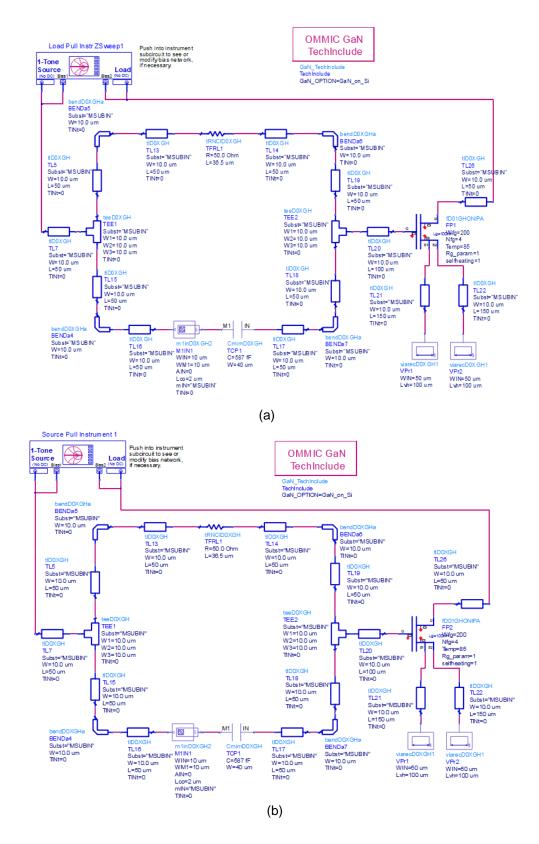

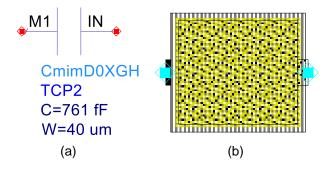

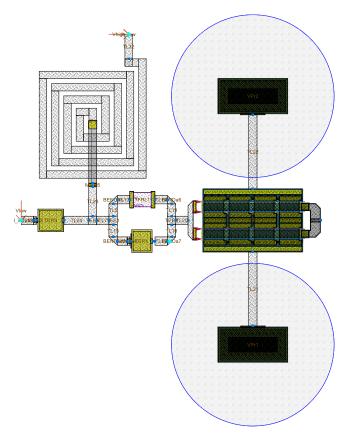

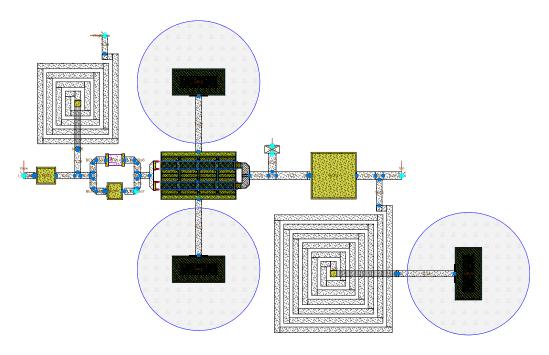

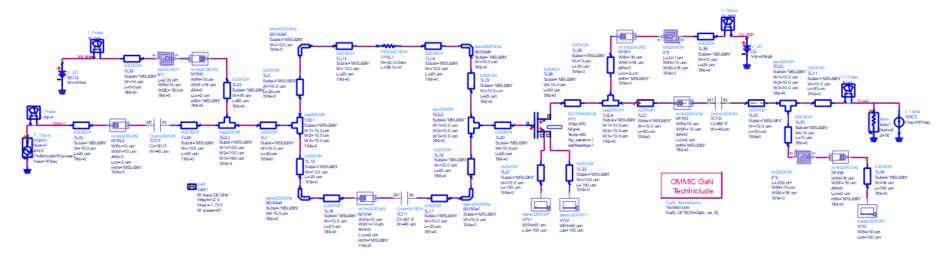

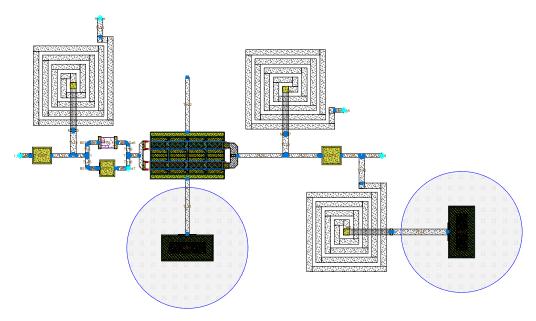

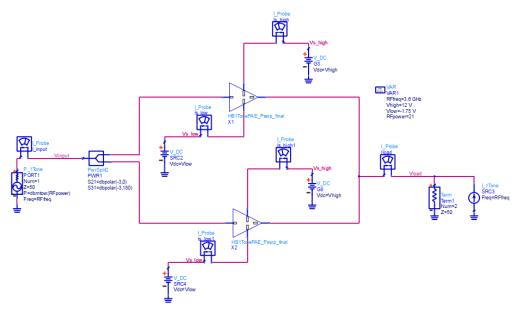

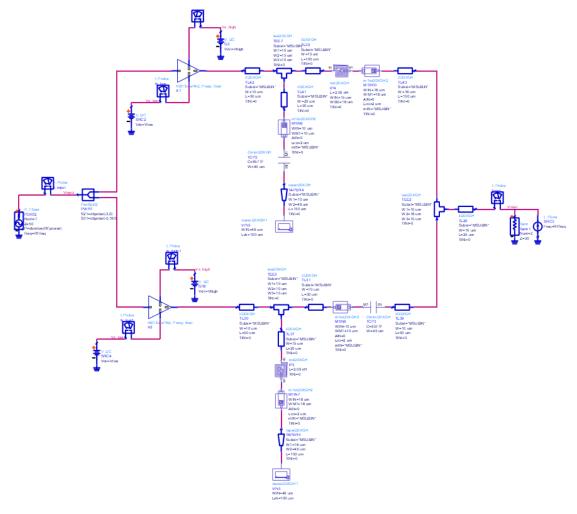

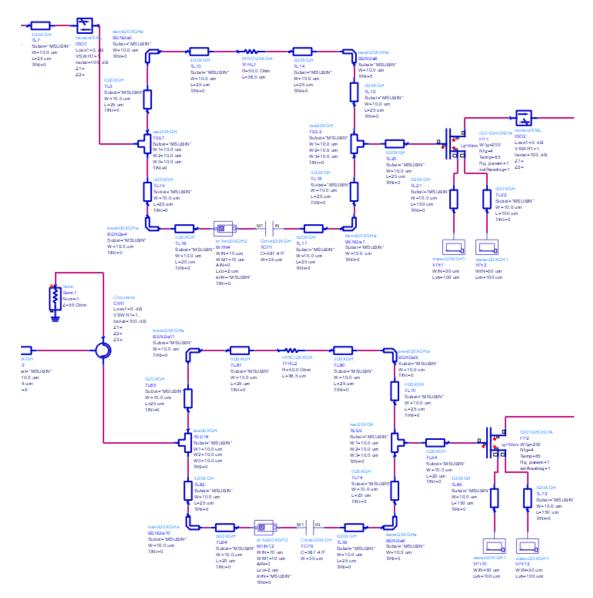

| Figura 6.3. Esquemático del amplificador Chireix                                           | 96     |

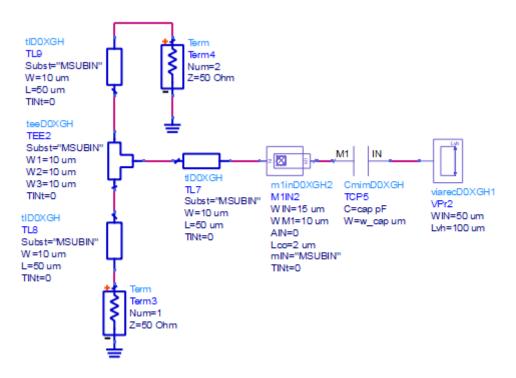

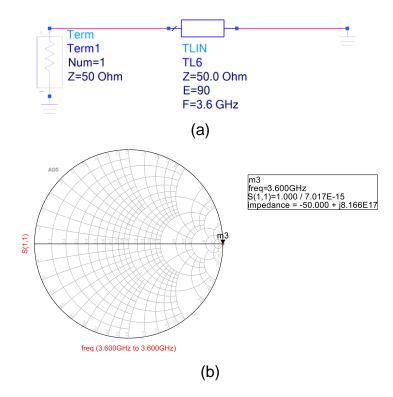

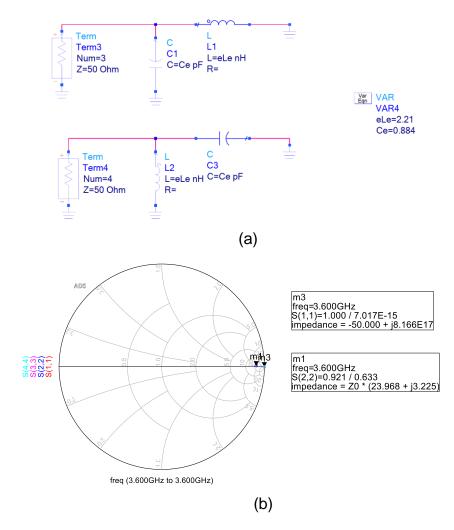

| Figura 6.4. (a) Esquemático para el estudio de un combinador con líneas λ/4                | ideal. |

| (b) Resultados del estudio de un combinador con líneas λ/4 ideal                           | 97     |

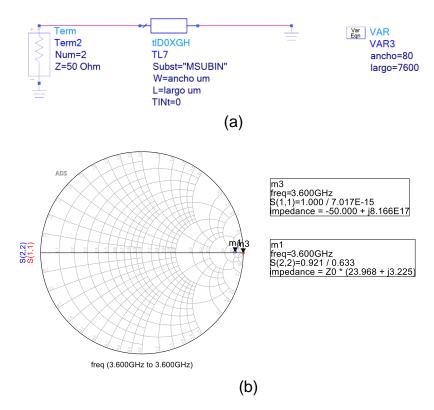

| Figura 6.5. (a) Esquemático para el estudio de un combinador con líneas $\lambda / \omega$ | 1 con  |

| tecnología Gan. (b) Resultados del estudio de un combinador con líneas $\lambda / 2$       | 1 con  |

| tecnología GaN                                                                             | 98     |

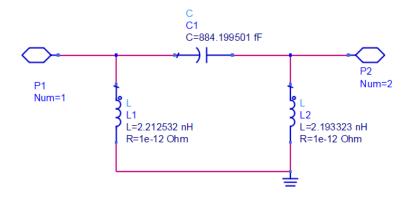

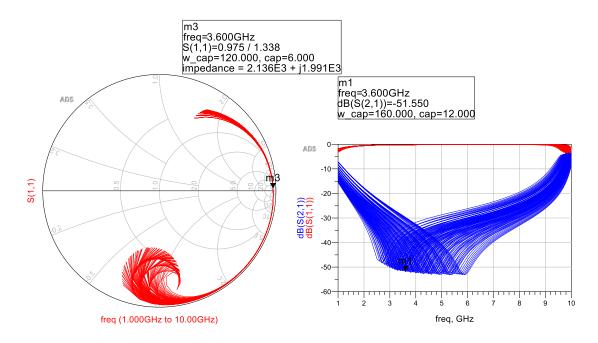

| Figura 6.6. (a) Esquemático para el estudio de un combinador con una red LC                | y CL   |

| ideales. (b) Resultados del estudio de un combinador con una red LC y CL ide               | ales.  |

|                                                                                            | 99     |

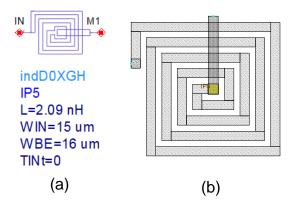

| Figura 6.7. (a) Valor real de la bobina del combinador. (b) Layout de la bobin             | a del  |

| combinador                                                                                 | . 100  |

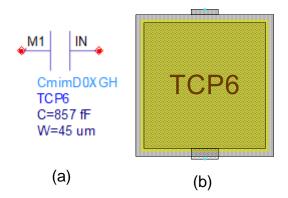

| Figura 6.8. (a) Valor real del condensador del combinador. (b) Layou                       | t del  |

| condensador del combinador                                                                 | . 100  |

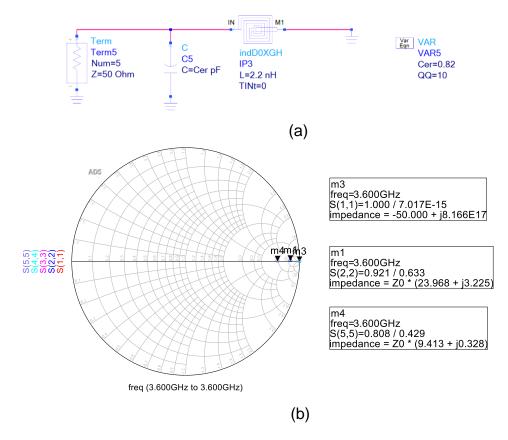

| Figura 6.9. (a) Esquemático para el estudio de un combinador con una red LC y CL    |

|-------------------------------------------------------------------------------------|

| reales. (b) Resultados del estudio de un combinador con una red LC y CL junto con   |

| los resultados de los combinadores basados en líneas N4 reales e ideales 101        |

| Figura 6.10. Esquemático del amplificador Chireix                                   |

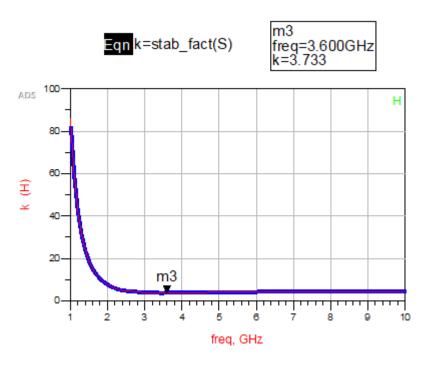

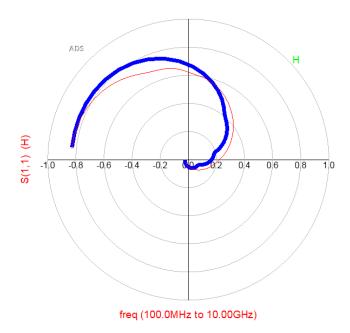

| Figura 6.11. Estabilidad del factor de Rollet. Red LC con polarización real (rojo). |

| Red LCL en pi (azul)                                                                |

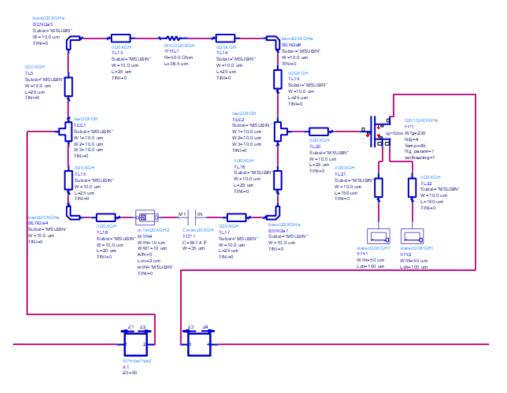

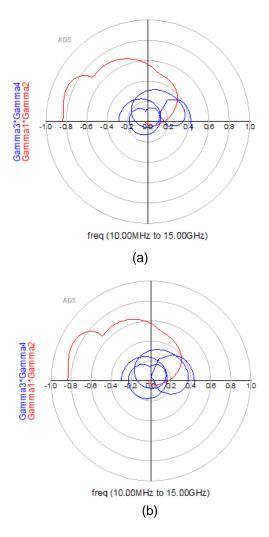

| Figura 6.12. Análisis de la estabilidad par con la herramienta SprobePairT 104      |

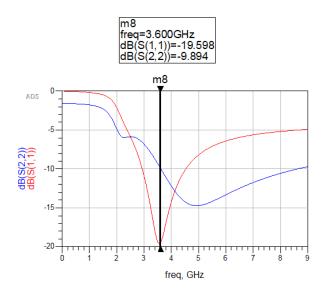

| Figura 6.13. (a) Estabilidad par. Red LC con polarización real. (b) Red LCL en pi.  |

|                                                                                     |

| Figura 6.14. Esquemático para el análisis de la estabilidad impar 106               |

| Figura 6.15. Estabilidad impar. Red LC con polarización real (rojo). Red LCL en pi  |

| (azul)                                                                              |

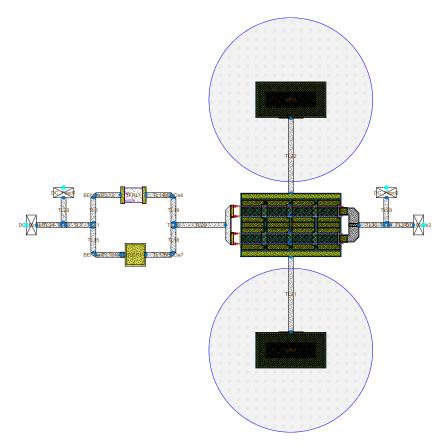

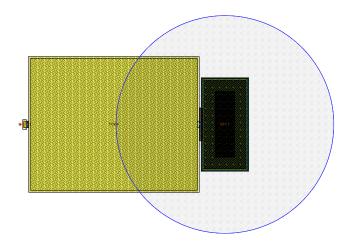

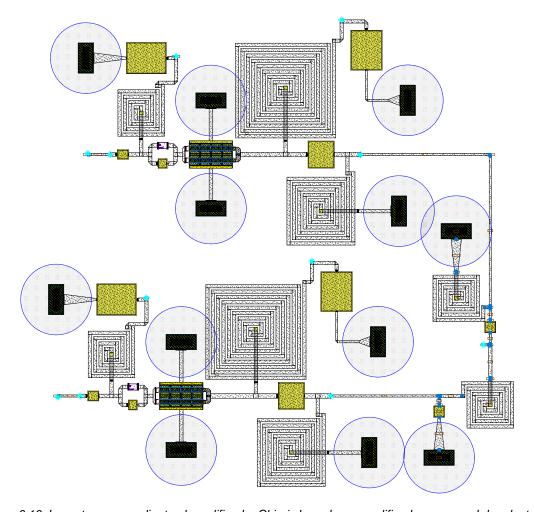

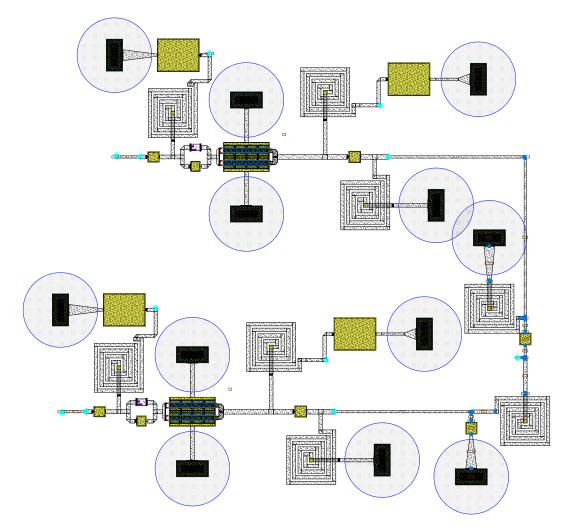

| Figura 6.16. Layout correspondiente al amplificador Chireix basado en               |

| amplificadores con red de adaptación de salida LC y red de polarización real 108    |

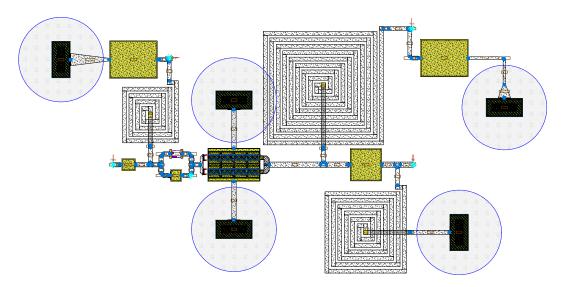

| Figura 6.17. Layout correspondiente al amplificador Chireix basado en               |

| amplificadores con red de adaptación de salida LCL en pi                            |

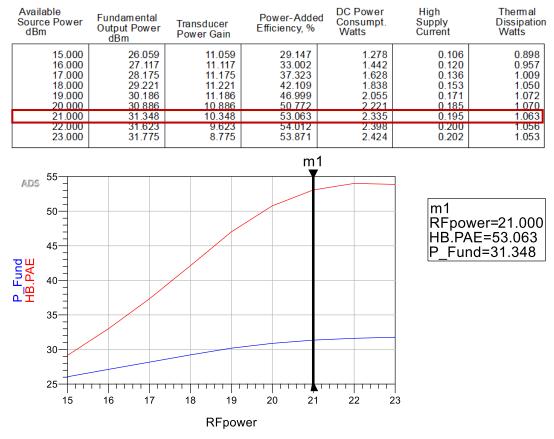

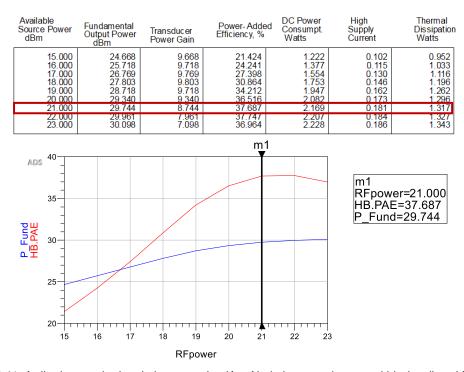

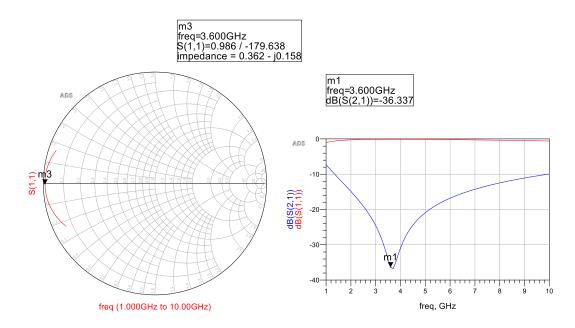

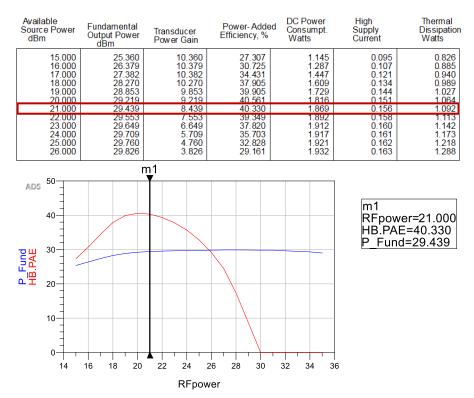

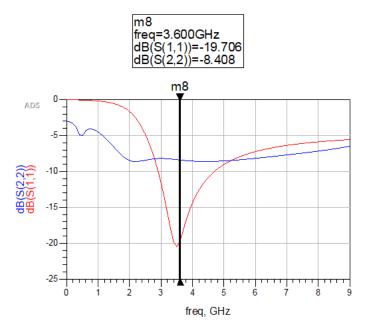

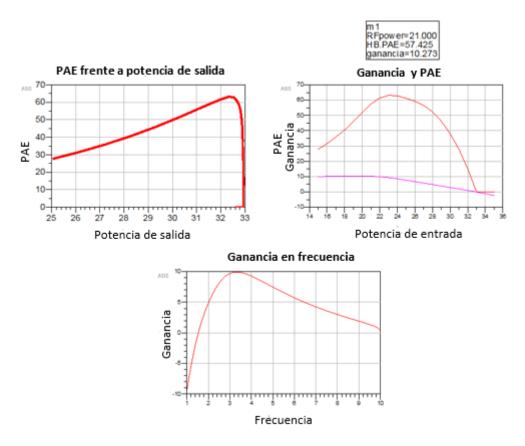

| Figura 6.18. Resultados de la simulación del amplificador Chireix. Red LC con       |

| polarización real                                                                   |

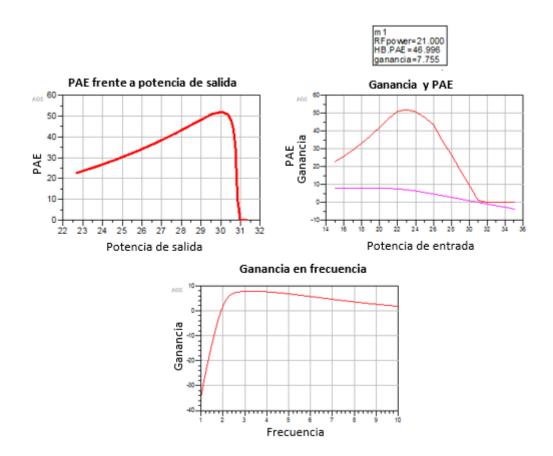

| Figura 6.19. Resultados de la simulación del amplificador Chireix. Red LCL en pi.   |

| 111                                                                                 |

### Índice de tablas

| Tabla 1.1. Especificaciones a cumplir por el amplificador Chireix 5                   |

|---------------------------------------------------------------------------------------|

| Tabla 2.1. Tabla comparativa del 4G y 5G8                                             |

| Tabla 3.1. Eficiencia máxima y ángulo de conducción de cada clase lineal 25           |

| Tabla 4.1. Resultados de las simulaciones variando la configuración (Nfg=6) 39        |

| Tabla 4.2. Resultados de las simulaciones variando la configuración (Nfg=4) 39        |

| Tabla 4.3. Resultados de las simulaciones variando la potencia de entrada 50          |

| Tabla 5.1. Comparación entre los resultados con los valores ideales y los valores     |

| reales                                                                                |

| Tabla 5.2. Comparativa entre los tres tipos de redes de adaptación a la salida frente |

| a la realizada con valores ideales                                                    |

| Tabla 7.1. Prestaciones del amplificador Chireix114                                   |

| Tabla 7.2. Comparativa entre varios amplificadores Chireix                            |

| Tabla P.1. Costes de amortización hardware130                                         |

| Tabla P.2. Costes de amortización del software                                        |

| Tabla P.3. Presupuesto total sin IGIC131                                              |

| Tabla P.4. Presupuestos totales con redacción del trabajo                             |

| Tabla P.5. Costes de material fungible                                                |

| Tabla P.6. Presupuesto total del proyecto                                             |

#### Lista de acrónimos

3GPP. Third Generation Partnership

4G. Fourth Generation

5G. Fifth Generation

ADS. Advanced Design System

AM. Amplitude Modulation

ATIS. Alliance for Teleccomunications Industry Solutions

BJT. Bipolar Junction Transistor

CCSA. China Communications Standards Association

DC. Direct Current

EHF. Extremely High Frequency

eMBB. enhanced Mobile Broadband

ETSI. European Telecommunication Standards Institute

FET. Field Effect Transisor

FOM. Figure of Merit

GaAs. Gallium Arsenide

GaN. Gallium Nitride

HEMT. High Electron Mobility Transistor

IBO. Input Back-Off

IoT. Internet of Things

ITU. International Telecommunication Union

LINC. Linear amplification using Non-linear Components

MESFET. Metal-Semiconductor Field-Effect Transistor

mMTC. massive Machine Type Communications

OBO. Output Back-Off

PA. Power Amplifier

PAE. Power Added Efficiency

PAPR. Peak to Average Ratio

P-HEMT. Pseudomorphic High Electron Mobility Transistor

PM. Phase Modulation

RF. Radio Frequency

SCS. Signal Component Separate

Si. Silicon

uRLLC. ultra Reliable and Low Latency Communications

# PARTE I: MEMORIA

#### Capítulo 1.

#### 1. Introducción

En este capítulo se presentarán los antecedentes del trabajo y los conceptos que se verán a lo largo de este proyecto, como la quinta generación de tecnologías de telefonía móvil (5G) y el amplificador Chireix. Posteriormente, se expondrán los principales objetivos que se pretenden alcanzar. Por último, se detalla la estructura de la memoria.

#### 1.1. Antecedentes

Las redes móviles que se manejan en la actualidad en los sistemas de comunicación inalámbricas requieren cada vez más de una alta tasa de transferencia de datos, así como de un bajo consumo de potencia, lo que conlleva diseñar amplificadores de potencia, que además de operar en bandas más anchas deben ser eficientes energéticamente.

Hoy en día los sistemas de comunicaciones inalámbricos poseen unas tasas de datos muy elevadas, lo cual implica un aumento de los anchos de banda. Para reducirlo se suele hacer uso de modulaciones con amplitud no constante. Sin embargo, esto hace que aumente el PAPR (*Peak to Average Ratio*), obligando a trabajar con elevados niveles de *back-off* para poder operar de manera lineal, [1]–[3]. En los amplificadores de potencia, esto se traduce en diseños que deben soportar picos elevados de potencia sobre el nivel medio de potencia de salida. En los amplificadores de potencia tradicionales la curva de eficiencia alcanza su máximo cerca del punto de compresión 1 dB mientras que cae de manera considerable en los niveles de *back-off*, donde queda definida la región principal de trabajo para operar de manera lineal. Esta es una de las principales razones por las que resulta de especial transcendencia encontrar estructuras que permitan mejorar la eficiencia en los niveles de *back-off* [4].

Además de la eficiencia de los sistemas, otro de los problemas que se precisa solventar en los diseños de sistemas inalámbricos es el consumo de potencia. En la arquitectura de un transmisor, el componente de mayor importancia es el que más consume, el cual es el amplificador. En sistemas de radio con carga

máxima, el consumo del amplificador de potencia supone más de la mitad del consumo de DC del sistema entero. Aparte de los problemas de rendimiento causados por el calor generado, los sistemas de alta potencia que funcionan en niveles de *back-off* llevan asociado un incremento de la complejidad del sistema. En consecuencia, existe la necesidad de diseñar amplificadores de potencia eficientes.

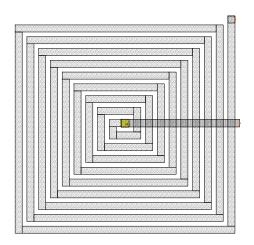

Existen varias técnicas para mejorar la eficiencia en *back-off* como, por ejemplo, la modulación por pulsos de RF (*RF-pulse modulation*), seguidores de envolvente (*envelope tracking*) y modulación dinámica de la carga (*dynamic load modulation*). Un ejemplo de esto último es el amplificador de potencia Chireix, cuya estructura básica se muestra en la Figura 1.1, que consta de dos amplificadores idénticos en paralelo, pero con diferente fase, donde se busca combinar las señales de PM (*Phase Modulation*) con una amplitud constante para alcanzar una amplificación de una señal de AM (*Amplitude Modulation*) [4], [5]. El principio de funcionamiento de este circuito es el siguiente; un separador de componente de señales traduce una señal AM en dos señales PM constantes con la misma amplitud, pero opuestas en fase. Después de pasar las señales PM por los amplificadores, que tienen una amplitud de salida constante en ambas ramas, ambas salidas se recombinan para obtener la señal AM amplificada [6].

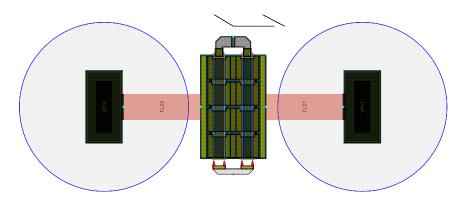

Figura 1.1. Estructura de un amplificador Chireix.

#### 1.2. Objetivos

El objetivo principal de este trabajo fin de grado (TFG) es el diseño de un amplificador de potencia integrado para el estándar 5G en configuración Chireix.

Para ello, se empleará la tecnología GaN (Nitruro de Galio) proporcionada por la fundidora OMMIC [7].

Las especificaciones preliminares que debe cumplir el diseño son las que se ven reflejadas en la Tabla 1.1.

| 1201211    | -cnaciticacionac | a cumpur nor a    | i amniiticador | I hiroiv  |

|------------|------------------|-------------------|----------------|-----------|

| Tabla I.I. | Especificaciones | a cullibili bul c | annbillicador  | CHILLEIX. |

| Bandas de frecuencia | 3,4 – 3,8 GHz                  |  |

|----------------------|--------------------------------|--|

| Madulasianas         | IT/L BPSK, BPSK, QPSK, 16-QAM, |  |

| Modulaciones         | 64-QAM, 256-QAM                |  |

| PAPR                 | >7 dB                          |  |

| Potencia de salida   | 25 dBm                         |  |

Para llevar a cabo el proyecto se ha empleado la herramienta software ADS (Advanced Design System) de la empresa Keysight. Esta herramienta es ampliamente utilizada para el diseño de circuitos RF puesto que es un instrumento muy potente y posee un gran de número de librerías, así como opciones de simulación.

#### 1.3. Estructura de la memoria

La memoria de este TFG se compone de 7 capítulos. En el primero de ellos se comienza con una breve introducción sobre el proyecto y se exponen los principales objetivos que se pretenden alcanzar.

En el segundo capítulo se realizará un estudio del estado del arte, donde se examinará el desarrollo de la tecnología 5G y el impacto del GaN que se ha llevado a cabo en los últimos años.

En el capítulo 3 se presentan los conceptos más relevantes relacionados con los amplificadores de potencia, y se detallan las diferentes clases de amplificadores existentes. Posteriormente, se realiza un estudio teórico sobre el amplificador Chireix.

En el cuarto capítulo se procede a realizar el diseño de un amplificador en clase B con elementos ideales, necesario para la implementación del amplificador Chireix. Posteriormente, en el capítulo 5 se lleva a cabo un diseño análogo al capítulo anterior, pero con los componentes reales de la tecnología de GaN.

En el sexto capítulo se realiza la implementación del amplificador Chireix por completo, y se obtienen los resultados. Asimismo, se presenta el *layout* completo del amplificador.

Por último, en el capítulo 7, se exponen las conclusiones a partir de los resultados obtenidos, y se muestran las posibles líneas futuras de este trabajo.

#### Capítulo 2.

#### 2. Estudio de la tecnología

En este capítulo se exponen los principales datos de la tecnología 5G, además de las características que hacen destacar el Nitruro de Galio (GaN) como semiconductor frente a otros ya existentes en el mercado.

#### 2.1. Tecnología 5G

El desarrollo de la tecnología de los dispositivos electrónicos como los teléfonos móviles o las *tablets* se ha visto incrementado en los últimos años, superando incluso en rendimiento y capacidad a dispositivos como los ordenadores, algo impensable hasta hace no mucho. A medida que ha ido creciendo la demanda en distintos campos, la tecnología móvil ha evolucionado poco a poco, pasando por diferentes generaciones hasta que actualmente se encuentra en nuestros sistemas móviles, el 4G [8].

Las necesidades de los usuarios han hecho que se desarrolle una nueva tecnología, la 5G, que trae consigo un aumento de la tasa de transferencia de datos y la disminución de la latencia. A su vez, la aparición del 5G hace posible el desarrollo a gran escala de aplicaciones que llevan poco tiempo en el mercado como son por ejemplo los coches autónomos, el IoT (*Internet of Things*), el Big Data o la realidad aumentada.

Se estima que en 2021 el tráfico de datos de teléfonos móviles superará los 50 petabytes; 12 veces más que en 2016 [9]. Esto vendrá acompañado de un aumento en el número de dispositivos IoT, cuya estimación es que en 2020 habrá más de 20 mil millones de dispositivos [10].

La organización encargada de estandarizar esta nueva tecnología es la 3GPP (*Third Generation Partnership*) [11]; un consorcio formado por los órganos de estandarización a nivel mundial, como son la ETSI (*European Telecommunication Standards Institute*) a nivel europeo, CCSA (*China Communications Standards Association*) en China o ATIS (*Alliance for Teleccomunications Industry Solutions*) en Estados Unidos.

En la Tabla 2.1 se puede ver de forma resumida las principales características que diferencian el 5G de su antecesor. La velocidad de transmisión aumentará de 10 a 100 veces con respecto al 4G; la latencia se reducirá hasta en un factor de cinco veces a la actual y se permitirá una densidad de dispositivos por  $km^2$  diez veces mayor [12].

Tabla 2.1. Tabla comparativa del 4G y 5G.

|                          | 4G            | 5 <b>G</b>     |

|--------------------------|---------------|----------------|

| Número de conexiones     | Hasta 100.000 | Hasta 1 millón |

| Velocidad de transmisión | Hasta 1 Gbps  | Hasta 10 Gbps  |

| Latencia                 | 10ms          | <5ms           |

#### 2.1.1. Bandas de frecuencia

Una de las grandes ventajas que ofrece esta tecnología es su gran versatilidad, gracias a la cual se puede optimizar para cada aplicación específica. Así, se permite el uso de bandas de menos de 1 GHz, otras que se sitúan entre 1 y 6 GHz y otras por encima de 6 GHz, cada una con las ventajas que conlleva su uso.

El 5G trabajará en tres bandas de frecuencia distintas, comprendidas en los rangos mencionados anteriormente. La más baja, sub 1GHz, se empleará para una cobertura de área amplia y profunda en interiores. La ventaja de esta banda es la posibilidad de desplegarla mediante las redes ya existentes, haciendo así más fluida su transición [13].

La segunda banda que se usará se encuentra en el rango de 1 GHz-6 GHz. Se basa en el espectro de banda C alrededor de la marca 3,5 GHz para ofrecer el mejor compromiso entre la capacidad y cobertura. Su banda permitirá cubrir un área de tamaño mediano-grande mientras transmite una gran cantidad de datos. Los reguladores europeos han identificado la banda 3,4 GHz – 3,8 GHz, ya que es la que mayor impacto tendrá a nivel europeo.

En los planes de despliegue del 5G esta banda se considerará prioritaria, para poder ofrecer los servicios de banda ancha mejorada a empresas y así poder desarrollar el máximo potencial de esta tecnología.

La tercera banda se encuentra por encima de los 6 GHz. En Europa se ha acordado definirla entre 24,25 GHz y 27,5 GHz. Se usa un espectro de ondas milimétricas de mayor frecuencia para brindar altas velocidades de datos. Esto lo hará ideal para puntos estratégicos que requieran una gran tasa de transferencia de datos, como puede ser un estadio de fútbol, hospitales, etc.

Las ondas a esta frecuencia y mayores se conocen como "ondas milimétricas", y pertenecen a la banda *Extremely High Frequency* (EHF) cuyo rango va de 30 a 300 GHz. Estas son cada vez más atractivas para los fabricantes y diseñadores, al ser una parte del espectro que apenas se encuentra en uso, además de tener un *throughtput* muy elevado y una latencia muy reducida.

Se percibe que haciendo uso de las tres bandas de forma simultánea, se pretende dar cobertura a ciudades enteras y prevenir la saturación de las redes, dando a cada zona los requisitos que ésta requiera (ver Figura 2.1).

Figura 2.1. Bandas de frecuencias 5G.

#### 2.1.2. Aplicaciones

Las ventajas que ofrecen la tecnología 5G sobre sus antecesores es que permite que las aplicaciones cubran una gran cantidad de sectores y cada una con sus propios requisitos para operar correctamente. Esta tecnología influirá en campos como son la realidad virtual/mixta/aumentada, los coches autónomos, como alternativa al acceso al internet cableado, en hospitales, para consumir información en dispositivos móviles, etc. [8].

Los coches autónomos que harán uso de esta tecnología requieren de una reducida latencia, mientras que por ejemplo si se quieren ver vídeos en alta

definición, se precisa de un gran ancho de banda. Mientras, el loT necesitará poder conectar gran cantidad de dispositivos a una red, sin necesitar un ancho de banda elevado.

Debido a esta diferencia, la *International Telecommunication Union* (ITU) [14] ha clasificado los servicios que ofrecerá el 5G en función de tres categorías [15]): enhanced Mobile Broadband (eMBB), massive Machine Type Communications (mMTC) y ultra Reliable and Low Latency Communications (uRLLC). En la Figura 2.2 se clasifican varias aplicaciones y los servicios del 5G que requerirán.

- eMBB: Este servicio tiene como objetivo satisfacer las aplicaciones que requieren un elevado ancho de banda, pudiendo ofrecer hasta picos de 20 Gbps y 100 Mbps a cada usuario. Está orientado al consumo de la información: como es ver vídeos en alta definición (4k y 8k), realidad virtual, videojuegos, etc.

- mMTC: Su objetivo es permitir la conexión de una gran cantidad de nodos a la red, hasta 1 millón/ $km^2$ , lo cual es útil para, por ejemplo, el desarrollo de las ciudades inteligentes o la agricultura inteligente.

- uRLLC: Está centrado en ofrecer una mejor latencia, de hasta 1 ms, para servicios que necesitan una rápida transmisión de datos, como es el caso de los coches autónomos o las plantas industriales.

Figura 2.2. Los distintos servicios que ofrecerá el 5G y algunas de sus aplicaciones.

El espectro sub 1GHz, descrito en el anterior apartado, hará uso de uRLLC y mMTC, ya que necesitará soportar una alta movilidad y una gran área de

cobertura. Las otras dos bandas, 3,6 GHz y 26 GHz, principalmente ofrecerán un gran ancho de banda, eMBB.

#### 2.2. Tecnología GaN

Durante la última década han surgido nuevas aplicaciones que requieren de una gran potencia, como el 3G, 4G y WiMAX, que hacen uso de la banda de microondas (1 GHz – 300 GHz). Esto ha producido un aumento del uso de la tecnología GaN como compuesto para semiconductores en radiofrecuencia. Previamente, su principal uso era en áreas relacionadas con la defensa, como son los inhibidores de frecuencia o radares, aunque ahora su uso a nivel comercial es cada vez mayor y sus ventajas notables.

## 2.2.1. Comparativa del GaN frente al Si y el GaAs

Hasta ahora los compuestos más usados eran el Arseniuro de Galio (GaAs) y el Silicio (Si), Sin embargo, en los últimos años ha aparecido un nuevo semiconductor, el GaN, que presenta unas características que lo hacen muy atractivo para las aplicaciones de alta frecuencia [16].

Tanto el GaN como el GaAs, tienen en común ser utilizados como semiconductores que son depositados sobre obleas o *wafers*, como la que se muestra en la Figura 2.3. Sobre estas obleas se fabrican todos los elementos que forman parte de un circuito electrónico. Ambas tecnologías se comercializan en forma de lingotes con diámetros en torno a los 5cm.

Figura 2.3. Obleas donde se depositan los circuitos.

El GaAs se encuentra a día de hoy en una gran variedad de dispositivos, tales como los *smartphones*, *tablets*, etc. Este semiconductor por tanto está muy establecido en el mercado como opción preferente para diseños de alta frecuencia en los que se requiere una figura de ruido lo menor posible, como puede ser por ejemplo en las primeras etapas de un equipo receptor de RF. En general estos componentes operan a tensiones y corrientes lo suficientemente bajas como para no requerir más de una batería como fuente de alimentación.

Por otro lado, el GaN es capaz de soportar tensiones de alimentación elevadas, por lo que se suele escoger este material para diseñar amplificadores de potencia en estaciones base o para sustituir amplificadores basados en tubos de vacío. Comparando las salidas de dos amplificadores basados en GaN y GaAs, los primeros tienden a ser más lineales y presentar menos distorsión.

Las ventajas que ofrece el GaN frente a otros semiconductores para justificar su uso cada vez mayor en aplicaciones de radiofrecuencia y microondas son varias, siendo algunas de ellas:

- La banda prohibida de un semiconductor es la energía mínima necesaria para excitar un electrón desde su estado libre a un estado que le permita participar en la conducción de corriente. Cuanta más anchura tiene esta banda, más energía necesita un electrón para pasar de la banda de valencia a la de conducción. El GaN es un material considerado de banda prohibida ancha [16], ya que dicha dimensión es de unos 3,4 eV, frente a los 1,4 eV del GaAs.

- Debido al punto anterior, las propiedades del GaN suelen superar a las del GaAs en cuanto a energía, potencia y velocidad para alcanzar estados de alta energía. La velocidad de saturación, que es la velocidad máxima a la que se pueden mover los electrones por un canal [22], tiene un valor típico de 2,7·10<sup>7</sup> cm/s en el GaN, mientras que en el GaAs es de 2,0·10<sup>7</sup> cm/s. Es importante tener una velocidad de saturación adecuada, ya que, si no el transistor puede entrar en saturación independientemente de que la tensión aplicada no sea la máxima.

- La tensión de ruptura determina el nivel de tensión que se puede aplicar de forma segura a un dispositivo de estado sólido sin dañarlo. La tensión del

GaN, que es de 4·10<sup>6</sup> V/cm, es muy superior a la del GaAs, de 5·10<sup>5</sup> V/cm. El GaN también cuenta con una constante dieléctrica relativa mucho mayor (9) que la del GaAs (1,28), permitiendo así fabricar capacidades de más alto valor en una menor superficie [17].

Ya que la densidad de potencia en compuestos de GaN es mucho mayor que en compuestos de GaAs e incluso mayor que en otros materiales semiconductores como el Silicio, su conductividad térmica es superior a otros materiales. Este es un parámetro fundamental para caracterizar cómo de bien disipa calor el dispositivo debido a pérdidas en el dieléctrico e ineficiencias. La conductividad térmica del GaN es de 1,7 W/cm·K, tres veces superior a la del GaAs. Una conductividad térmica alta favorece que la temperatura crezca lo mínimo posible en conducción, algo que permite a los dispositivos basados en GaN manejar niveles mayores de potencia que aquellos basados en GaAs, usando ambos la misma estructura física.

#### 2.2.2. Comparativa con el SiC

Otro material ampliamente usado hoy en día es el Carburo de Silicio (SiC). Al igual que el GaN, éste se emplea principalmente en aplicaciones de alta potencia y de gran frecuencia [18]. Ambos son de banda prohibida ancha y tienen en común la alta tensión de ruptura y movilidad de electrones comentada anteriormente.

La ventaja del GaN frente al SiC es que el primero permite la fabricación de transistores de alta movilidad de electrones o *High Electron Mobility Transistor* (HEMT), mientas que el SiC solo permite la fabricación de *Metal-Semiconductor Field-Effect Transistor* (MESFET).

Los transistores tipo HEMT tienen como ventaja una alta concentración de portadores y movilidad de electrones debido a su reducido scattering por impurezas. Estos dos factores permiten una alta densidad de corriente y una baja resistencia del canal, lo que es especialmente importante en las aplicaciones de altas frecuencias y de conmutación de potencia.

#### 2.3. Resumen

En este capítulo se han presentado las principales características que diferencian la tecnología 5G de su antecesor, cabe destacar una velocidad de transmisión de hasta 10Gbps, una latencia menor de 5ms y una densidad de dispositivos por  $km^2$  de hasta 1 millón. Además, esta tecnología trabaja en tres bandas de frecuencia, la primera banda está por debajo de 1 GHz, otra que se sitúa entre 1 y 6 GHz y la última por encima de 6 GHz, cada una con las ventajas que conlleva su uso. En cuanto a las aplicaciones, esta tecnología cubre un amplio número de sectores, es por ello que los servicios que ofrece se clasifican en función de tres categorías: enhanced Mobile Broadband (eMBB), massive Machine Type Communications (mMTC) y ultra Reliable and Low Latency Communications (uRLLC).

En cuanto al GaN, se decide hacer uso de esta tecnología debido a sus ventajas sobre el resto de materiales. El GaN es un material considerado de banda prohibida ancha con una dimensión de unos 3,4 eV, debido a esto las propiedades del GaN suelen ser mejores en cuanto a energía, potencia y velocidad para alcanzar estados de alta energía. Además, esta tecnología es la primera que permite la fabricación de transistores de alta movilidad de electrones o *High Electron Mobility Transistor* (HEMT).

# 3. Estudio de los amplificadores de potencia

En este capítulo se definen los conceptos relacionados a los amplificadores de potencia. Primero se definirá el concepto de transistor FET (*Field Effect Transisor*), así como su funcionamiento y sus principales parámetros a tener en cuenta a la hora de utilizarlos. A continuación, se entrará en detalle de los distintos parámetros de un amplificador de potencia que se tendrán en cuenta para la realización de este trabajo. Por último, se detalla el amplificador con estructura Chireix, así como su proceso de diseño.

#### 3.1. Amplificadores de potencia

Los amplificadores de potencia o PA (*Power Amplifier*) son dispositivos que amplifican la potencia de la señal que reciben a su entrada. Su principal objetivo es proporcionar la tensión máxima requerida por una carga, sin que la señal sufra distorsión de algún tipo. Este tipo de amplificadores vienen determinados por una serie de parámetros, tales como la eficiencia, la ganancia y la estabilidad.

#### 3.1.1. Transistores

Un transistor de efecto de campo (FET) es un componente electrónico que consta de tres terminales: la puerta (o *Gate*), el drenador (o *Drain*) y el surtidor (o *Source*) (ver Figura 3.1). Estos dispositivos funcionan controlando la corriente entre drenador y surtidor a través del campo eléctrico establecido mediante la tensión aplicada al terminal de puerta, es decir, se regulan por la tensión. Otras ventajas es que generan menos ruido que los BJT y son fáciles de fabricar. Son usados comúnmente como resistencias controladas por tensión y fuentes de corriente [19].

Figura 3.1. Símbolo de un transistor HEMT.

En este trabajo se usarán transistores tipo *Pseudomorphic High Electron Mobility Transistor* (P-HEMT) en tecnología GaN, que pertenecen a la familia de los transistores FET. Las principales ventajas de este tipo de transistores son una eficiencia y ganancia elevadas, además de una alta tensión de ruptura y un elevado valor de tensión de saturación y un reducido tamaño.

#### 3.1.1.1. Funcionamiento

Para que un transistor entre en funcionamiento y ejerza su función de amplificador, se aplica una tensión entre la puerta y el surtidor (V<sub>GS</sub>) y otra del drenador al surtidor (V<sub>DS</sub>). En función del valor de cada una de estas tensiones el transistor estará funcionando o no. Así, se pueden definir distintas regiones de funcionamiento del transistor [19]: zona de corte, zona óhmica o lineal y zona de saturación.

#### 3.1.1.1. Regiones de funcionamiento

#### 3.1.1.1.1.1. Zona de corte

Existe una tensión, denominada tensión de umbral ( $V_T$ ) a partir de la cual el transistor comienza a operar. En caso de que la tensión entre la puerta y el surtidor ( $V_{GS}$ ) sea menor o igual que esta ( $V_{GS} \le V_T$ ), no circulará corriente entre el drenador y el surtidor ( $I_D$ ), aunque exista tensión positiva entre dichos terminales ( $V_{DS}$ ). Esto se debe a que al ser  $V_{GS}$  menor que  $V_T$ , no se llega a crear un canal en el transistor por el que pueda fluir la corriente.

Para V<sub>GS</sub>≤V<sub>T</sub> y V<sub>DS</sub>>0 se tiene la siguiente expresión (3.1):

$$I_{\rm D} = 0 \tag{3.1}$$

#### 3.1.1.1.1.2. Zona lineal u óhmica

Suponiendo una tensión  $V_{DS}$  mayor que cero, cuando la tensión  $V_{GS}$  aumenta lo suficiente y supera la tensión umbral  $V_T$ , se crea un canal entre el drenador y el surtidor que permite el paso de la corriente  $I_D$ . A medida que  $V_{GS}$  aumenta, dicho canal se va ensanchando, permitiendo el paso de una mayor cantidad de corriente. En esta zona de operación, la cantidad de corriente que fluye también es proporcional al valor de  $V_{DS}$ , como se verá en el siguiente apartado, en las curvas características del transistor.

Para V<sub>GS</sub>>V<sub>T</sub> y 0<V<sub>DS</sub>≤V<sub>GS</sub>-V<sub>T</sub> se tiene la siguiente expresión (3.2):

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{TH}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(3.2)

Siendo:

- μ<sub>n</sub>: la movilidad de los electrones.

- Cox: la capacidad de óxido de la puerta por unidad de área.

- L: la longitud del canal del transistor (µm).

- W: el ancho del canal del transistor (µm).

#### 3.1.1.1.3. Zona de saturación

Como ya se ha comentado anteriormente, cuando el valor de V<sub>GS</sub> es mayor que V<sub>T</sub>, la densidad de los portadores libres en el canal aumenta, dando como resultado un mayor nivel de I<sub>D</sub>. Sin embargo, si se mantiene V<sub>GS</sub> constante y sólo se aumenta el nivel de V<sub>DS</sub>, la corriente de drenador alcanza un nivel de saturación cuando su valor es superior a V<sub>GS</sub> -V<sub>T</sub>. Esta saturación se debe a un estrechamiento del canal (*pinch-off*), encontrándose así el transistor en zona de saturación.

Para V<sub>GS</sub>>V<sub>T</sub> y V<sub>DS</sub>>V<sub>GS</sub>-V<sub>T</sub> se tiene la siguiente expresión (3.3):

$$I_D = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda (V_{DS} - V_{DS_{sat}}))$$

(3.3)

Estando en la zona de saturación, si se continúan aumentando las tensiones del circuito, se excederán los límites recomendados por el fabricante y se podrá dañar el componente electrónico; provocando una zona conocida como *breakdown*.

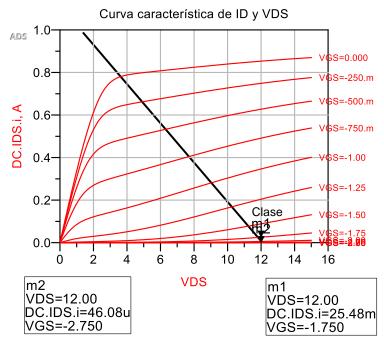

#### 3.1.1.2. Curvas características

Conociendo las distintas zonas que rigen la operación de los transistores, se pueden trazar las denominadas "curvas características". Estas curvas muestran las prestaciones de un transistor ante distintas tensiones de entrada de V<sub>GS</sub>, V<sub>DS</sub> y con ello la corriente I<sub>D</sub> que fluye en las distintas regiones de trabajo. En la Figura 3.2 se puede ver un ejemplo de estas curvas.

Figura 3.2. (a) Curva de transferencia y (b) curva característica del drenador del transistor.

En la Figura 3.2 (a) se puede ver la curva de transferencia de un transistor, con  $I_D$  en función de  $V_{GS}$ . También se observa que por debajo de la tensión umbral  $V_T$ , el transistor se encuentra en zona de corte y que cuando ésta se supera, el transistor se encuentra en conducción (zona óhmica).

Por otro lado, en la Figura 3.2 (b) se encuentra la curva característica del drenador. En ella, se traza la corriente I<sub>D</sub> frente a V<sub>DS</sub> y V<sub>GS</sub>. En función de los valores que obtenga V<sub>GS</sub>, la cantidad de corriente es mayor o menor. Además, cuando el valor de V<sub>DS</sub> supera el de V<sub>GS</sub> - V<sub>T</sub>, el transistor entra en saturación y el valor de la corriente se mantiene casi constante. Por debajo de dicho valor el transistor se encuentra en zona óhmica y el valor de la corriente tiene una relación cuadrada con las tensiones.

A partir de las curvas características de un transistor se puede también definir su recta de carga y punto de trabajo [20] y, por tanto, su polarización. Polarizar un transistor consiste en establecer un punto de trabajo mediante

restricciones de circuito, es decir, estableciendo las tensiones  $V_{GS}$ ,  $V_{DS}$  y la corriente  $I_D$  para que el transistor opere en la región que cumpla los siguientes requisitos [19]:

- Estar ubicado de tal forma que el dispositivo trabaje en zona activa (de saturación del canal o de corriente constante) y permitir suficiente variación de la señal sin que el dispositivo salga de esa zona de funcionamiento y entre en zona de corte, lineal o resistiva.

- Ser permanente, predecible y estable ante cualquier posible variación de los parámetros del dispositivo.

- Disipar la mínima potencia posible.

La ventaja de obtener la recta de carga es que permite conocer todos los puntos de trabajo posibles para el circuito. A partir de ahí, se puede variar los distintos parámetros del circuito y elegir el punto más conveniente para la aplicación específica para el que se está fabricando el circuito.

### 3.1.2. Estabilidad

La estabilidad es un factor fundamental a tener en cuenta. Este determina la capacidad que tiene un amplificador de mantener su eficacia en los valores nominales de operación, es decir, es la oposición que presta a oscilar.

En una red de dos puertos (entrada y salida) las oscilaciones son posibles cuando en cualquiera de ellos se presenta una impedancia con parte real negativa. Que se cumplan estos requisitos depende de varios factores, tales como los parámetros S del dispositivo, las redes de adaptación utilizadas y las terminaciones del circuito. Además, un circuito puede ser estable a algunas frecuencias y a otras no, para los mismos valores de impedancias de generadores y de carga [21].

Existen dos tipos de estabilidad. La primera, denominada "incondicionalmente estable", se cumple cuando para una frecuencia dada, el transistor es estable para todas las impedancias de fuente y carga, es decir, que las impedancias de entrada y salida tienen siempre parte real positiva.

Un transistor también puede ser "condicionalmente estable". Se encuentra en este estado cuando para una frecuencia dada, algunas de las impedancias de fuente y carga pueden producir impedancias de entrada y salida con parte real negativa [21].

En el caso de los amplificadores de potencia multietapa, es importante no solo analizar la estabilidad par con el factor de Rollet global (K) sino que se aplican distintos criterios para la verificación de la misma. Lo más común a la hora de estudiar la estabilidad de un circuito compuesto por varias etapas, es analizar las estabilidades par e impar de cada "celda" que lo compone. Se considera celda a cada transistor incluyendo su red de estabilización.

Para realizar este tipo de análisis de estabilidad se aplicada el criterio de Nyquist. A continuación, se explica brevemente dicho criterio para ambos modos de estabilidad [22] [23].

## 3.1.2.1. Estabilidad par

### 3.1.2.1.1. Pequeña señal

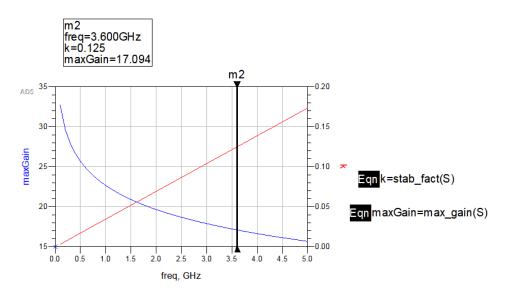

Para saber si un amplificador es estable, se deben cumplir un número de condiciones, que se reúnen en el factor de Rollett o de estabilidad, representado mediante una K y cuya expresión matemática es (3.4). Si este valor es menor que la unidad (K < 1), el transistor es inestable; en caso contrario (K > 1) es estable.

$$K = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* * \Delta| + |S_{21} * S_{12}|} > 1$$

(3.4)

Siendo los parámetros S:

- S11: Indica el grado de adaptación de la impedancia de entrada. Estando bien adaptada, no habría potencia reflejada y por tanto S11 = 0 + 0j.

- S22: Indica el grado de adaptación de la impedancia de salida. Bien adaptada, no se refleja potencia a la carga y S22 = 0 + 0j.

- S12: Ganancia en potencia en inversa. Mide el nivel de aislamiento.

- S21: Ganancia de potencia en directa. Interesa que sea elevado.

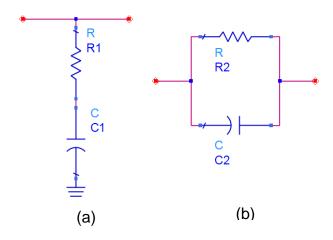

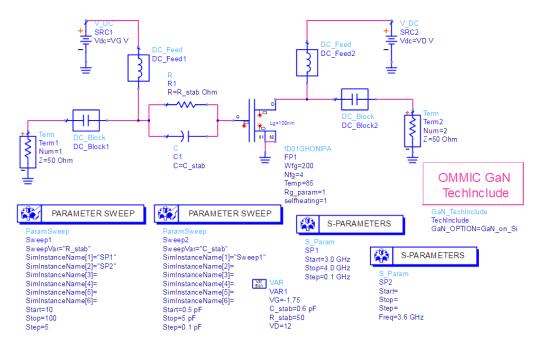

Para proporcionar estabilidad a un transistor es posible añadir una red de estabilidad. Este tipo de redes reducen la ganancia del transistor en favor de un mayor factor de estabilidad.

#### 3.1.2.1.2. Gran señal

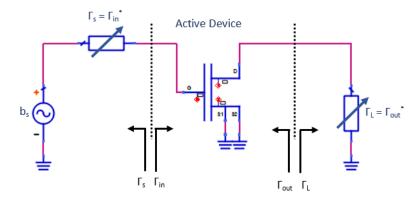

El criterio de Nyquist para el modo par sirve para comprobar si un transistor del circuito es estable por sí mismo. Es decir, se analiza que cada transistor (o celda) sea estable sin que el resto de los transistores interfieran en el análisis.

Por otra parte, se dice que una celda es estable en modo par según el criterio de Nyquist si el producto de los coeficientes de reflexión a la entrada o a la salida del circuito es menor que 1 y no engloba el punto -1+j0 en el sentido de las agujas del reloj. En otras palabras, si el producto es menor que 1 se asegura que no van a ocurrir inestabilidades de esta naturaleza. Sin embargo, en caso de ser mayor que 1, si no engloba el punto -1+j0 se puede asegurar que no ocurrirán inestabilidades de modo par [23].

## 3.1.2.2. Estabilidad impar

Las inestabilidades de modo impar ocurren en gran señal y cabe destacar que aparecen normalmente en amplificadores con más de un dispositivo (celda) debido a las distintas características de los transistores y las técnicas de adaptación aplicadas. En este tipo de amplificadores, la combinación en paralelo de los transistores se emplea para conseguir altas potencias de salida. Esta combinación en paralelo puede causar inestabilidades por fugas de la señal entre celdas debido a los bucles existentes. Otra razón que puede causar inestabilidades de modo impar son las posibles asimetrías que existan entre las redes de adaptación de los transistores.

En este caso, se vuelve aplicar el criterio de Nyquist, pero para el modo impar. Este método determina las inestabilidades asociadas a los bucles mediante el análisis de su función de transferencia en bucle abierto en las uniones entre las redes pasivas y la entrada de los dispositivos activos. De esta forma, se analiza el coeficiente de reflexión de entrada en ese punto para cada uno de los dispositivos activos  $(G_1(jw), \ldots, G_k(jw),$  siendo k el número de dispositivos activos) y se comprueba que ninguno de ellos engloba el punto 1+j0 [23].

## 3.1.3. Ganancia

La ganancia (G) de un amplificador se define como el ratio de potencia de salida (Po) frente a la potencia de entrada (Pi). Su expresión matemática viene dada por la ecuación (3.5).

$$G = \frac{P_o}{P_i} \tag{3.5}$$

## 3.1.4. Eficiencia

El amplificador de potencia es, con diferencia, uno de los componentes que más consume en un circuito. Una mayor eficiencia implica menores pérdidas y, por tanto, una mejor gestión del calor generado y mejores costes de operación del amplificador.

La eficiencia es un parámetro que permite medir la cantidad de la corriente continua de la señal de entrada que se transforma en potencia. La parte que no es transformada se disipa en forma de calor. Existen dos formas de representar numéricamente la eficiencia en un amplificador: mediante la eficiencia del drenador  $(\eta)$  y la *Power Added Efficiency* (PAE).

### 3.1.4.1. Eficiencia del drenador

La eficiencia del drenador viene dada por la expresión (3.6) y se define como la potencia de salida del amplificador (P<sub>out</sub>) frente a la potencia en continua (P<sub>dc</sub>) que recibe de alimentación [17].

$$\eta_{drenador} = \frac{P_{out}}{P_{dc}} \tag{3.6}$$

El problema contemplado en esta ecuación es la falta de consideración de la potencia de entrada y por tanto no se puede saber con precisión la cantidad de potencia proveniente de la fuente de alimentación que es convertida en potencia de la señal de salida. Es decir, es independiente de la ganancia del amplificador.

## 3.1.4.2. PAE

Para solucionar el problema anterior, otra forma de medir la eficiencia del circuito es mediante el PAE, cuya ecuación (3.7) incluye la potencia de entrada del amplificador.

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} \tag{3.7}$$

Otra forma de obtener el PAE es mediante la expresión (3.8), que, como se puede observar, sí contempla la ganancia del circuito para obtener la eficiencia del circuito.

$$PAE = \eta_{drenador} \frac{G - 1}{G} \tag{3.8}$$

En el caso de un amplificador real, el PAE siempre será menor que la eficiencia del drenador (PAE  $< \eta$ ). Sin embargo, a partir de los 30 dB de ganancia, o 1000 en la escala lineal, la diferencia será del 0,1%, lo cual es una diferencia despreciable.

El PAE es considerada FOM (*Figure of Merit*) y por esta razón será usada a lo largo de este trabajo.

## 3.1.5. Back-Off

Como se ha comentado anteriormente, la finalidad de un amplificador es amplificar la potencia de la señal a los niveles requeridos por la carga que está conectada a él. Debido a la polarización y la linealidad del transistor, cuando se recibe una señal de entrada demasiado grande, este entra en saturación y la señal de salida se comprime, como se puede ver en la Figura 3.3.

Figura 3.3. Señal de salida de un transistor (izquierda) y señal en compresión (derecha).

En la Figura 3.4 se muestra la potencia de salida (P<sub>out</sub>) en función de la potencia de entrada (P<sub>in</sub>), donde para valores bajos de P<sub>in</sub> se obtiene una potencia de salida de la señal lineal. Sin embargo, cuando los valores de P<sub>in</sub> son elevados, la potencia de salida de la señal se satura. Para conseguir una mayor linealidad, es necesario operar por debajo del punto de compresión de 1 dB [23].

Figura 3.4. Representación gráfica del back-off de entrada y de salida.

El *Input Back-Off* (IBO) en un amplificador de potencia mide cuánto hay que reducir la potencia de entrada para obtener la potencia y linealidad deseada en la señal de salida. En otras palabras, es la diferencia en dB entre la potencia de entrada en el punto de operación y el punto de compresión a 1 dB.

El *Output Back-Off* (OBO) es la diferencia entre la potencia de salida de saturación y la potencia media transmitida después de la amplificación. Suele ser 5 dB menos que el IBO y depende del punto de compresión del circuito. Viene dada por la ecuación (3.9).

$$OBO = P_{sat}(dB) - P_{av}(dB)$$

(3.9)

Reducir el OBO puede ser de gran interés, si un circuito para operar correctamente necesita un reducido *back-off*, es decir, que la potencia de operación P<sub>av</sub> sea próxima a P<sub>sat</sub>. De esta forma el circuito será más eficiente y por tanto se verá reducido su consumo de potencia. Los amplificadores de potencia tienen su mayor eficiencia cuando se usan a la máxima potencia, o lo que es lo mismo, con 0 dB de *back-off*.

## 3.1.6. Clases

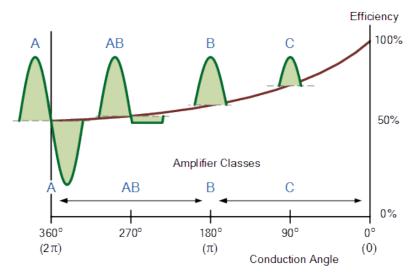

Los amplificadores de potencia se pueden clasificar por el porcentaje de tiempo que están operando al recibir una entrada senoidal [24]. Este principio depende del denominado "ángulo de conducción", que muestra durante qué parte de los ciclos de las ondas de entrada el transistor está conduciendo. Dicho ángulo de conducción se puede regular mediante la tensión de polarización de puerta-surtidor  $V_{\rm GS}$ .

En función de cada ángulo de conducción se define una "clase" de amplificador, pudiendo así clasificar estas dentro de dos grupos. Por una parte, los amplificadores lineales; cuya salida es proporcional a la entrada. Dentro de este grupo se encuentran las clases A, AB, B y C, que se observan de forma más detallada en la Figura 3.5 donde se encuentran los ejemplos gráficos de la conducción de las clases de los amplificadores.

En el segundo grupo el transistor actúa como *switch*, variando la tensión de puerta surtidor (V<sub>GS</sub>), consiguiendo así que funcione en ciertos rangos de entrada. Cada una de las clases de los amplificadores de potencia difiere en términos de linealidad, potencia de salida y eficiencia.

Figura 3.5. Clases de amplificadores según el ángulo de conducción frente a la eficiencia.

El ángulo de conducción es importante ya que define la eficiencia y la linealidad de los amplificadores de potencia. Estos valores ya están calculados y están resumidos en la Tabla 3.1.

Tabla 3.1. Eficiencia máxima y ángulo de conducción de cada clase lineal.

| Clase | Ángulo  | Eficiencia  |

|-------|---------|-------------|

| Α     | 2π      | 50%         |

| В     | π       | 78,5%       |

| AB    | π<σ<2 π | 50%<η<78,5% |

| С     | <π      | >78,5%      |

#### 3.1.6.1. Clase A

Esta clase de amplificadores conducen durante el periodo entero de una onda, es decir,  $2\pi$  radianes. Se polarizan la corriente y el voltaje DC en medio de los máximos y mínimos de la onda, para así asegurar la conducción en todo momento.

Como se ve en la Figura 3.5, la función de un amplificador clase A es prácticamente una función lineal y destaca por tener una ganancia elevada y una reducida distorsión. El principal inconveniente que se encuentra es la baja eficiencia, debido al alto consumo de energía. La máxima eficiencia que se puede obtener es del 50%.

Este tipo de amplificadores se usan en la mayoría de los casos cuando se requiere una elevada linealidad de la señal de salida.

#### 3.1.6.2. Clase B

El transistor polarizado en clase B se distingue por tener un ángulo de conducción de  $\pi$  radianes, es decir, conduce medio ciclo de una onda de entrada. Esto queda reflejado en su punto de polarización, que está en  $V_{DSmax}/2$ . Existen varias diferencias frente a un transistor polarizado en clase A. Una de ellas es que un transistor en clase B tiene una mayor eficiencia, de hasta 78,5%, pero sacrificando linealidad debido a una mayor presencia de armónicos.

## 3.1.6.3. Clase AB

Esta clase se distingue por estar entre la clase A y B, es decir, su ángulo de conducción se encuentra entre  $\pi$  y  $2\pi$ . Como se ha comentado con anterioridad, en un transistor polarizado en clase A, la eficiencia es del 50% y tiene un bajo contenido armónico, mientras que en el clase B la eficiencia es del 78,5% y con un alto contenido armónico.

Consecuentemente, mediante un clase AB se puede obtener una eficiencia que se encuentre en el rango  $50\% < \eta < 78,5\%$  y una linealidad mayor o menor. Esto depende de si el transistor es polarizado más cerca de clase A o clase B.

Este tipo de configuración es usada ampliamente hoy en día porque su estructura representa el punto óptimo entre linealidad y eficiencia.

#### 3.1.6.4. Clase C

Los transistores polarizados en clase C tienen un ángulo de conducción menor que  $\pi$ . La principal razón para hacer uso de transistores polarizados en esta clase es debido a su alta eficiencia, ya que no consume potencia para más de la mitad del ciclo de una señal.

Como se puede ver en la Figura 3.5, la corriente de salida de un transistor polarizado en clase C son picos de corta duración. Como en el nivel de corriente máximo, el voltaje también es bajo, la potencia disipada es menor y, por ello, la potencia consumida por el amplificador es casi igual a la que se entrega a la carga.

La distorsión de la señal, en comparación con la señal de entrada, es elevada debido a la alta frecuencia de encendido y apagado del transistor; es la clase menos lineal de todas las nombradas anteriormente. Su mayor uso es para amplificar señales moduladas en frecuencia, donde la distorsión armónica y la falta de linealidad no son importantes.

## 3.2. Amplificador *Outphasing* Chireix

Existen diferentes arquitecturas que funcionan como amplificadores tipo *Outphasing*. Esta técnica trata de combinar señales moduladas en fase (PM) con una misma amplitud constante con el fin de obtener una amplificación en la señal de entrada que está modulada en amplitud (AM). La señal AM pasa a través de un módulo que la divide en dos señales PM de amplitud constante, pero con fase opuesta. Debido a que estas señales tienen una amplitud constante los amplificadores de potencia pueden trabajar en modo saturación para obtener una elevada eficiencia. Una vez amplificadas ambas ramas se recombinan las señales, alcanzando así la señal AM amplificada. Como puede verse, se está realizando una amplificación lineal, usando bloques no-lineales, por lo que a este tipo de amplificación se le denomina *Linear amplification using Non-linear Components* (LINC) [5].

Esta arquitectura está formada por tres bloques: El separador de componentes de señal (*Signal Component Separate*, SCS), los amplificadores de potencia y el combinador de potencia, tal y como se puede ver en la Figura 1.1.

## 3.2.1. Combinadores

Los dos amplificadores trabajan con una potencia de salida constante, esto hace que ambos deban polarizarse con una carga constante igual a la resistencia óptima. El PA clásico, para alcanzar dicho resultado, hace uso de un combinador de potencia aislado que produce una alta eficiencia solo con máxima potencia de salida. Uno de los problemas es que en condiciones de *back-off* la potencia restante en cada rama de los PA se malgasta en el puerto aislado del combinador de salida.

En 1935, Chireix propuso un cambio significativo al esquema clásico del *Outphasing*, en el que mediante un combinador de salida no-aislado introduce un efecto de modulación de carga que mejora considerablemente la eficiencia a la vez que se mantiene la linealidad típica del modelo clásico del *Outphasing* [4].

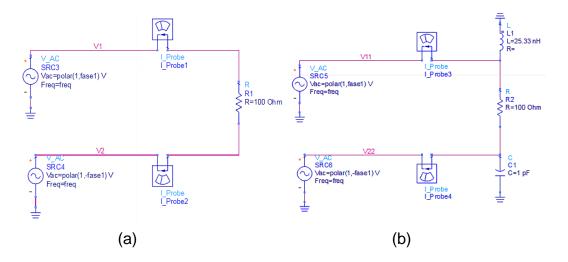

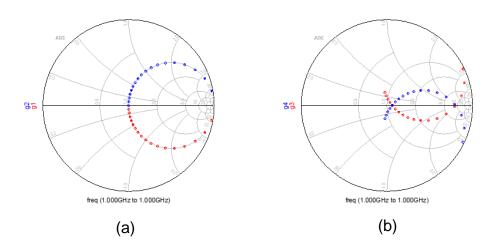

Para entender mejor el efecto de la modulación de carga propuesto por Chireix se puede simplificar el circuito reemplazando los dos PA por dos fuentes de tensión ideales con una misma amplitud constante V, pero en contra fase  $(\pm\phi)$ , conectadas en serie a una carga diferencial R, tal y como se puede ver en la Figura 3.6 (a).

Figura 3.6. Circuito simplificado de la salida de un amplificador outphasing ideal. (a) Sin compensación. (b)

Con compensación (Chireix).

La carga vista por cada uno de los PA es diferente y varía en base a la fase φ según las expresiones (3.10) y (3.11) [5].

$$Z_1 = \frac{R}{2}(1 - j\cot\phi) \tag{3.10}$$

$$Z_2 = \frac{R}{2}(1 + j\cot\phi) \tag{3.11}$$

Se puede observar como cuando  $\phi = 0^{\circ}$ , la potencia de salida es nula, por lo tanto, las dos cargas se comportarán como un circuito abierto. En cambio, con una  $\phi = 90^{\circ}$ , la potencia de salida es máxima, proporcionando una carga resistiva pura (R/2). Tal y como se puede ver en la Figura 3.7 (a) la impedancia de carga de ambas ramas de los PAs se mueve en un semicírculo de resistencia constante.

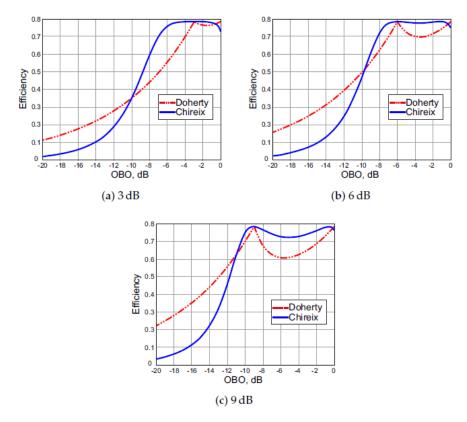

El problema que se da es que las trayectorias de carga solo pasan por el eje real con valores de  $\phi = 90^\circ$  y  $\phi = 0^\circ$ , mientras que para los otros valores presentan una parte imaginaria significante. Esto produce que la eficiencia disminuya con el sen  $\phi$ . Sin embargo, se puede forzar un segundo pico de eficiencia añadiendo dos elementos reactivos de compensación, con una susceptancia de igual valor y opuesta. El circuito que hace esto se muestra en la Figura 3.6 (b) y su trayectoria de carga se muestra en la Figura 3.7 (b) donde se observa que ahora se producen dos cruces por el eje real. Estos dos puntos proporcionan dos puntos de eficiencia máxima tal y como se muestra en la Figura 3.8 donde se representa la eficiencia en función del OBO para diferentes valores de la susceptancia de compensación. Como se puede observar, variando la susceptancia de compensación es posible aumentar el OBO aunque el valle entre los dos picos se hace más acentuado. En cualquier caso este valle es mucho menor que el que proporcionas otras estructuras clásicas como la tipo Doherty.

Figura 3.7. Trayectorias de las cargas para un barrido de la fase de 0°-90°. (a) Sin compensación. (b) Con compensación (Chireix).

Figura 3.8. Curvas de la eficiencia frente al OBO de los amplificadores Chireix y Doherty.

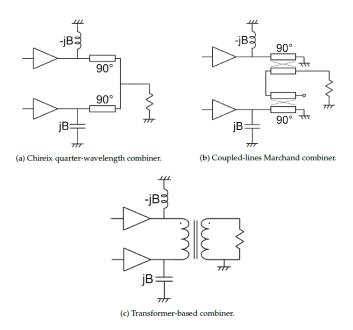

La arquitectura mostrada en la Figura 3.6 no se puede realizar en la práctica debido a que la mayoría de los sistemas de alta frecuencia usan cargas asimétricas en lugar de diferentes. Por lo tanto, para realizar la combinación de la señales, en [25] se propone un combinador con dos líneas de transmisión  $\lambda/4$ , mientras que [26]-[27] usan un balun y un transformador, respectivamente (ver Figura 3.9).

Figura 3.9. Arquitecturas para el combinador de salida de un amplificador Chireix.

## 3.3. Resumen

En este capítulo se han explicado los conceptos básicos de un amplificador de potencia, así como sus parámetros fundamentales (estabilidad, ganancia, eficiencia, *back-off*).

Los amplificadores se dividen en dos grupos: los amplificadores lineales, cuya salida es proporcional a la entrada y los no lineales donde el transistor actúa como *switch*, variando la tensión de puerta surtidor (V<sub>GS</sub>), consiguiendo así que funcione en ciertos rangos de entrada. A su vez, los amplificadores lineales se dividen en diferentes clases (clase A, B, AB y C) en función del ángulo de conducción, que es el que define la linealidad y la eficiencia de estos.

Por último, se ha definido el amplificador *Outphasing* y en concreto de la estructura Chireix, que estará configurado en clase B ya que se pretende diseñar un amplificador con una elevada linealidad y eficiencia.

# 4. Diseño del amplificador clase B ideal

En este capítulo se procede a realizar el diseño del amplificador clase B necesario para la implementación del amplificador Chireix. Para ello, primero se obtendrán las curvas del transistor y se estudiará la estabilidad del mismo y se llevará a cabo la simulación Load & Source Pull. Por último, se efectuará la adaptación de la entrada y la salida del amplificador.

## 4.1. Obtención de las curvas del transistor

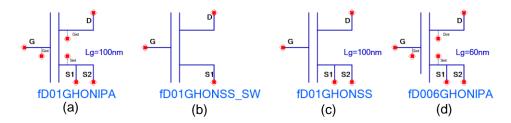

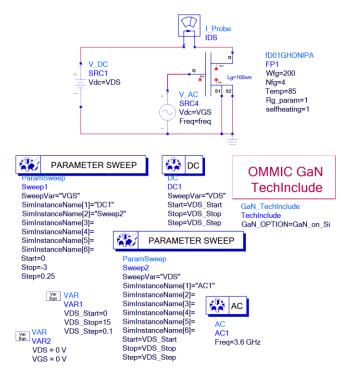

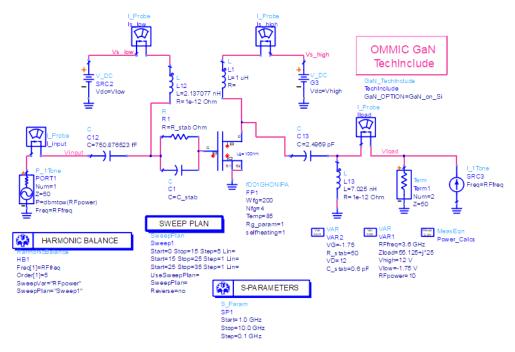

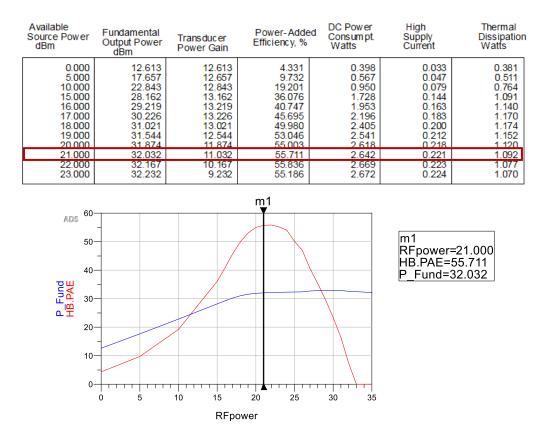

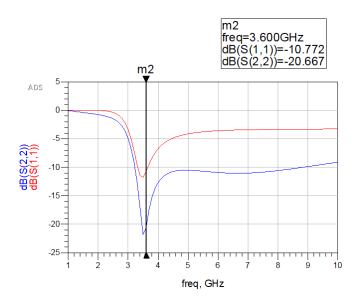

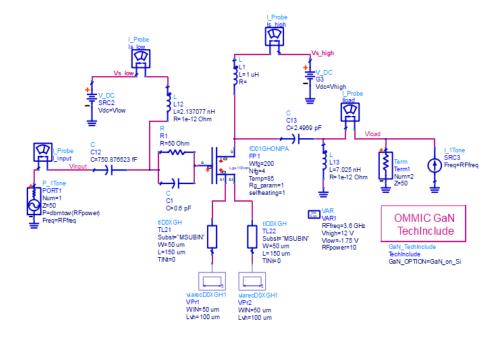

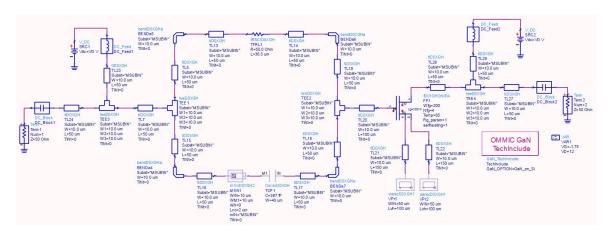

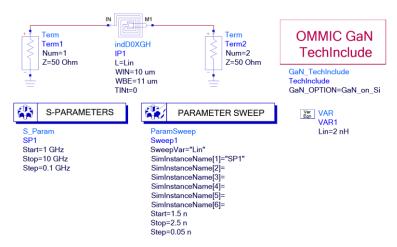

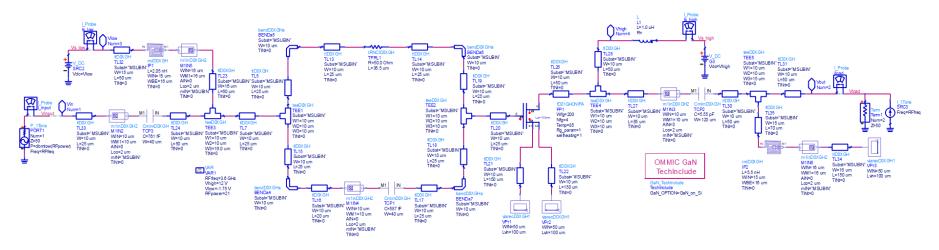

Para obtener las curvas características del transistor y su recta de carga primero se debe realizar un estudio de estos. La tecnología de OMMIC ofrece cuatro modelos de transistores como se observa en la Figura 4.1, de los cuales dos de ellos son para el diseño de amplificadores y los otros dos para el diseño en bajo ruido [7]. A continuación, se realiza una breve descripción de cada uno de ellos:

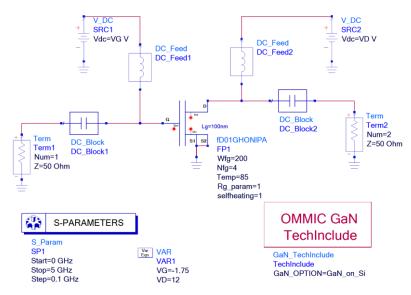

Figura 4.1. Modelos de los transistores ofrecidos por OMMIC.

- FD01GHONIPA (a): Modelo de gran señal del D<sub>01</sub>GH. Longitud de puerta de

0.1 μm, GaN HEMT. El surtidor tiene dos conexiones.

- FD01GHONSS\_SW (b): Modelo en pequeña señal del modelo D<sub>01</sub>GH. Longitud de puerta de 0,1 μm, GaN HEMT. El surtidor tiene una conexión.

- FD01GHONSS (c): Modelo en pequeña señal del modelo D<sub>01</sub>GH. Longitud de puerta de 0,1 μm, GaN HEMT. El surtidor tiene una conexión. Incluye odelo de ruido.

- FD006GHONIPA (d): Modelo de gran señal del D006GH. Longitud de puerta de 60 nm, GaN HEMT. El surtidor tiene dos conexiones.

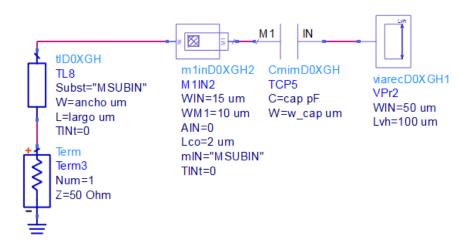

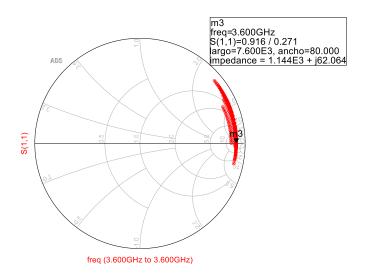

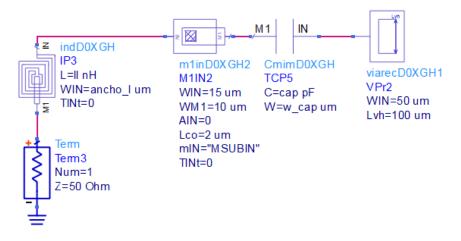

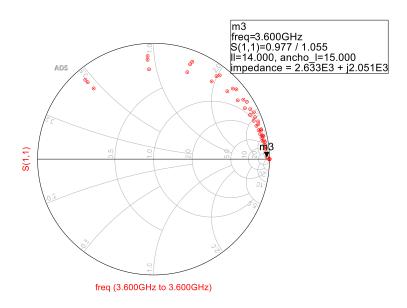

Como en este proyecto se trabajará en gran señal, se descartan los transistores que son de pequeña señal. De los modelos restantes, se opta por el uso del transistor (a), pues según OMMIC, el nivel de madurez o *Technology Readiness Level* (TRL) de éste ronda el nivel 3-4, mientras que de la opción (d) posee un TRL de 1-2 niveles, es decir; el más básico de todos [7].