### Diseño de un mezclador basado en convertidores de corriente en tecnología CMOS 0.18 µm

Escuela de Ingeniería de Telecomunicación y Electrónica

Titulación: Sistemas electrónicos

Tutores: Dr. Francisco Javier del Pino Suárez D. Roberto Díaz Ortega Autor: D. Guillermo García Saavedra

Fecha: Abril 2010

Bloque 1

Introducción

Objetivos

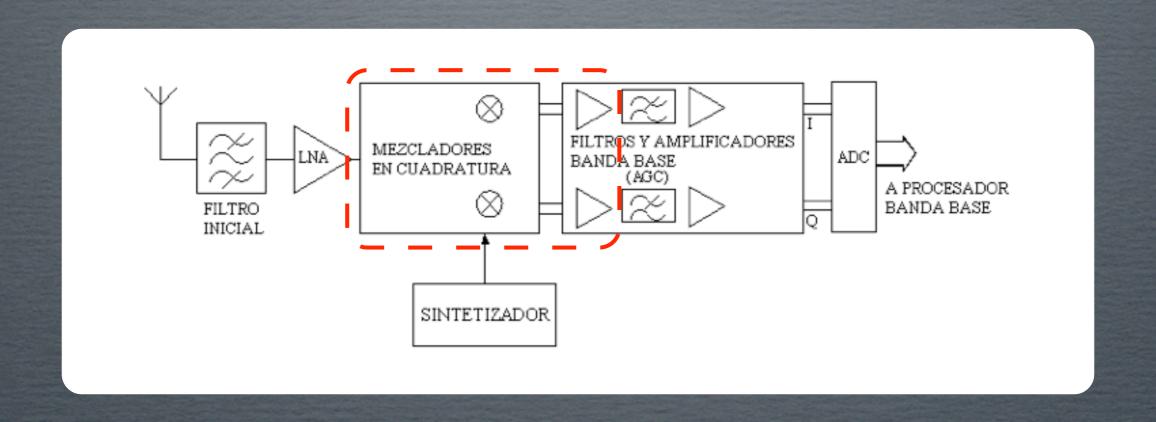

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

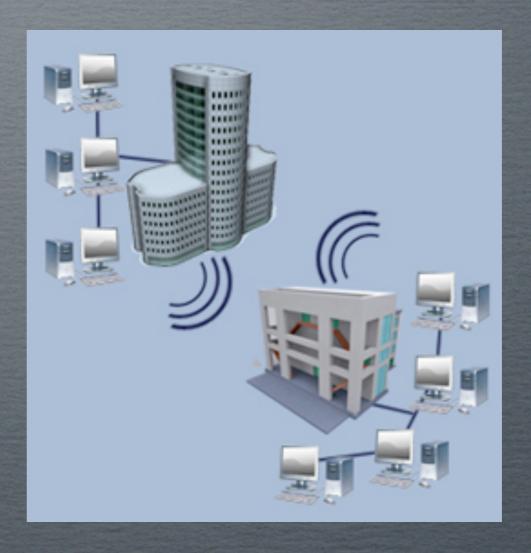

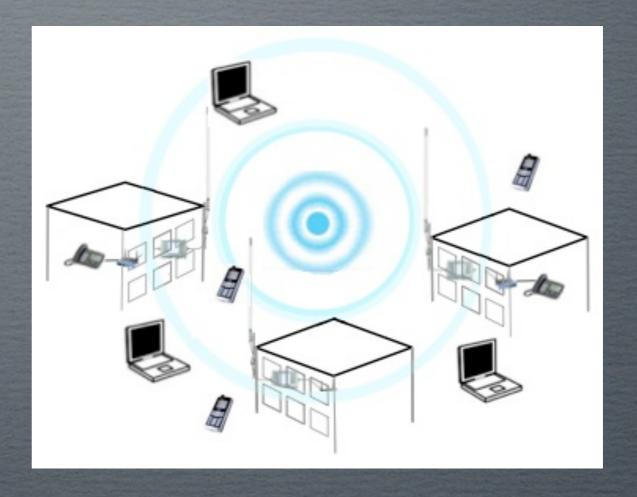

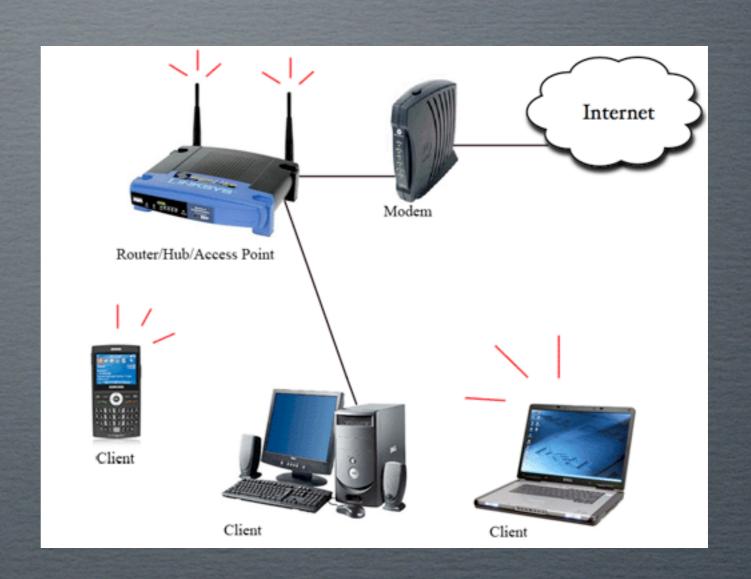

### Redes inalámbricas

### Bloque 1

Móviles:

### Bloque 1

### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

### Móviles:

- WWAN

Bloque 1

Introducción

Objetivos

Características RF

Teoría current conveyor

Móviles:

- WMAN

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

### Móviles:

- WLAN

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría current conveyor

### Móviles:

- WPAN

### Bluetooth

### Bloque 1

### Bluetooth

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Opera en la banda ISM (2.45 GHz)

Velocidad de hasta 2.1 Mbps (versión 2.0)

### Ultra Wide Band (UWB)

### Ultra Wide Band (UWB)

### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Velocidades de transmisión 400-500 Mbps

### Bloque 1

Corto alcance

Alta velocidad

Bajo consumo

### Bloque 1

- Detección de dispositivos

- Gestión de WPAN y acceso al medio

- Gestión de energía

- Quality of service (QoS)

### Bloque 1

### Estándar ISO 29907:

### Bloque 1

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

### Estándar ISO 29907:

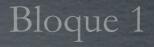

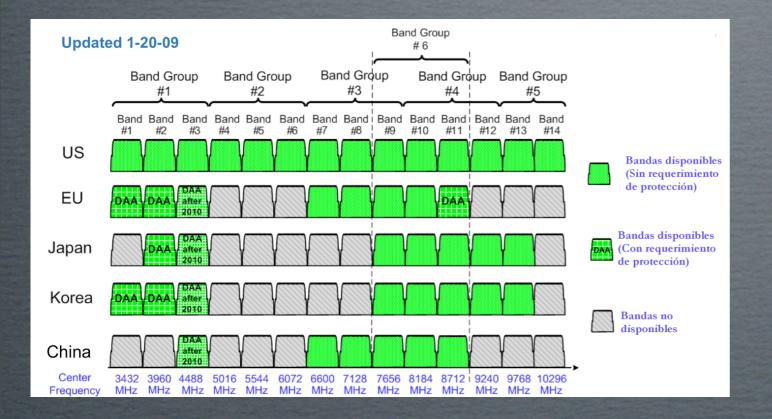

- Espectro de 3 a 10 GHz

- Bandas de 528 MHz

- Modulación QPSK-OFDM 128

- Tasas de datos de 53.3 a 480 Mb/s

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

### Bloque 1 Introducción Objetivos Características RF

Estándar WiMedia Teoría mezcladores Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

## Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción Objetivos

Características de los sistemas RF Estándar WiMedia Teoría de los mezcladores Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

### Objetivos

### Bloque 1

### Objetivos

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

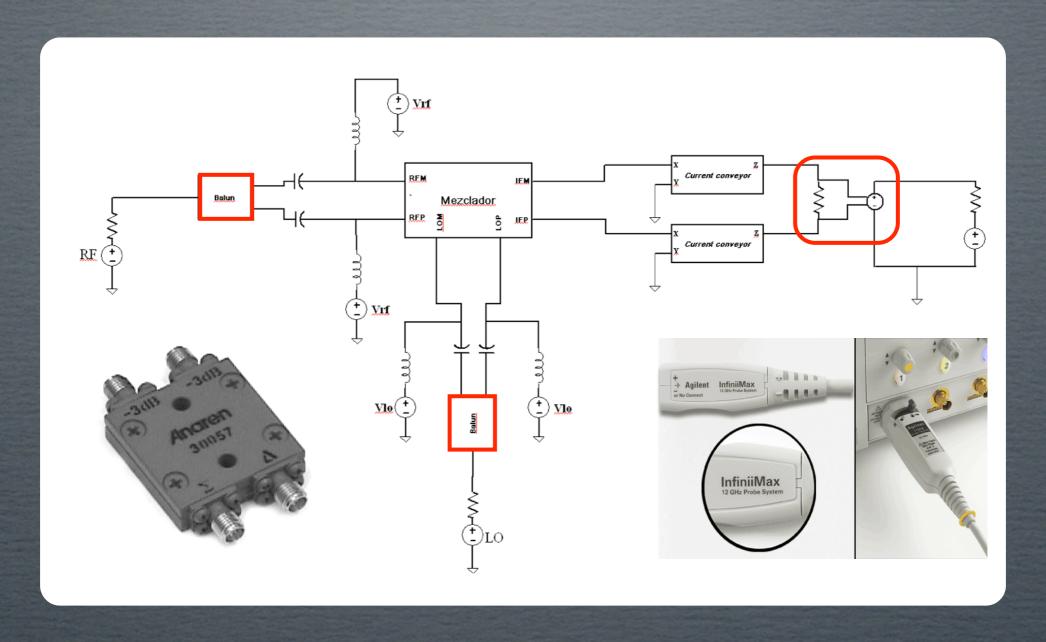

- Diseño de un Mezclador para tecnología UWB basado en Convertidores de Corriente en tecnología CMOS 0.18 µm y estudiar la viabilidad de esta tecnología para implementar dispositivos de RF aplicados al estándar WiMedia.

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

#### Ganancia

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- La ganancia en tensión determina la relación entre las amplitudes de la señal de salida y la de entrada

$$G = \frac{V_{salida}}{V_{entrada}}$$

#### Ganancia

#### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- La ganancia en tensión determina la relación entre las amplitudes de la señal de salida y la de entrada

$$G = \frac{V_{salida}}{V_{entrada}}$$

- Siendo su valor en decibelios

$$G(dB) = 20 \cdot \log \left( \frac{V_{salida}}{V_{entrada}} \right)$$

### Bloque 1

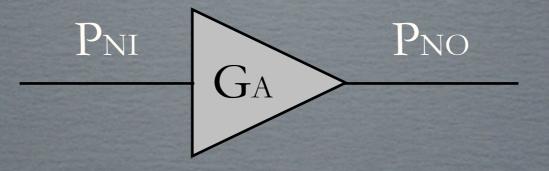

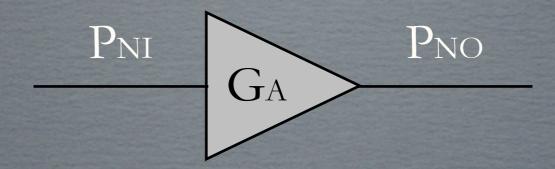

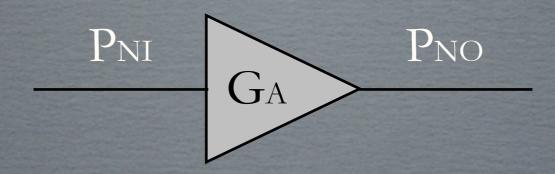

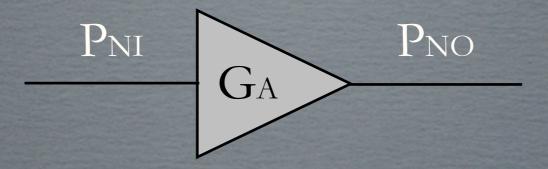

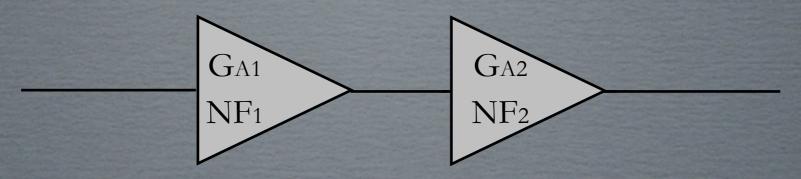

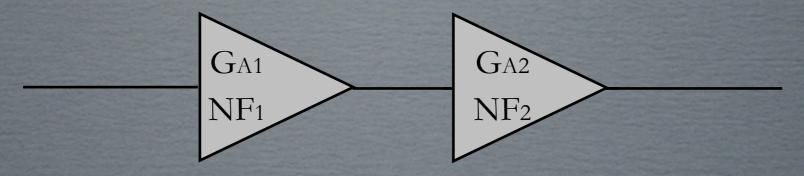

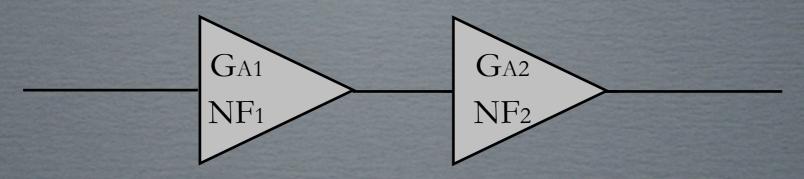

- El factor de ruido viene dado por la expresión:

$$F = \frac{P_{N0}}{P_{Ni} \cdot G_A}$$

PNO = Potencia de ruido de salida PNI =  $k \cdot T \cdot B$

- El factor de ruido viene dado por la expresión:

$$F = \frac{P_{N0}}{P_{Ni} \cdot G_A}$$

$F = \frac{P_{N0}}{P_{Ni} \cdot G_A}$  Pno = Potencia de ruido de salida  $P_{NI} = k \cdot T \cdot B$

- Tendiendo el cuenta que  $G_A = P_{SO}/P_{SI}$  se obtiene que:

$$F = \frac{P_{S_i}/P_{N_i}}{P_{S_0}/P_{N_0}} = \frac{SNR_i}{SNR_0}$$

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- La figura de ruido no es más que el factor de ruido en decibelios:

$$NF = 10\log(F)$$

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Cuando se trata de varias etapas en cascada el factor de ruido viene dado como:

$$F = F_1 + \frac{F_2 - 1}{G_{A1}}$$

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Cuando se trata de varias etapas en cascada el factor de ruido viene dado como:

$$F = F_1 + \frac{F_2 - 1}{G_{A1}}$$

- El ruido de la primera etapa es la que más contribuye al ruido total

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Cuando se trata de varias etapas en cascada el factor de ruido viene dado como:

$$F = F_1 + \frac{F_2 - 1}{G_{A1}}$$

- El ruido de la primera etapa es la que más contribuye al ruido total

- La ganancia de la primera etapa disminuirá la figura de ruido de las etapas siguientes

#### Bloque 1

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

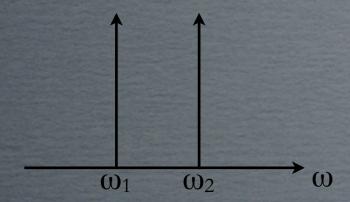

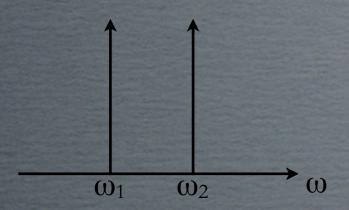

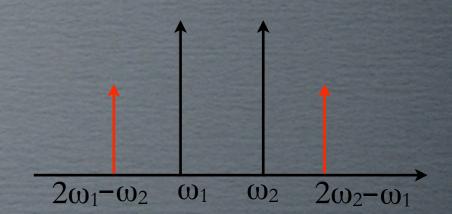

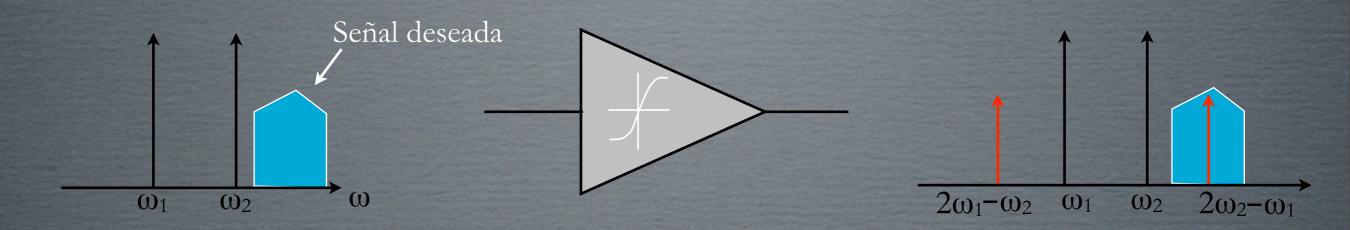

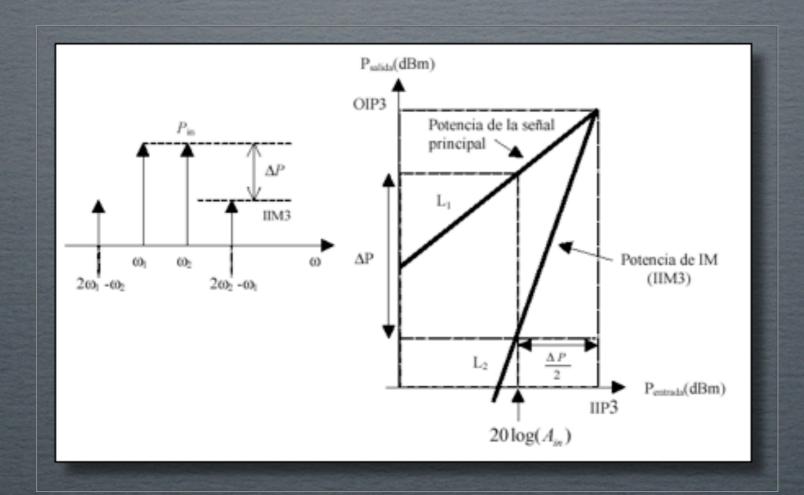

- Los sistemas no lineales en la salida aparecen términos armónicos de la señal de entrada que siguen la ley  $m\omega_1\pm n\omega_2$

- Los sistemas no lineales en la salida aparecen términos armónicos de la señal de entrada que siguen la ley  $m\omega_1\pm n\omega_2$

- Los productos de intermodulación de tercer orden son los más peligrosos porque pueden solaparse con la señal deseada

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- El IP3 determina la degradación de la señal debido a los productos de intermodulación

### Coeficiente de onda estacionaria (VSWR)

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Es una medida cuantitativa de la adaptación del circuito a la entrada VSWR2

$$\left| \Gamma_L \right| = \left| \frac{Z_L - Z_0}{Z_L + Z_0} \right| = \frac{VSWR - 1}{VSWR + 1}$$

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

#### Estándar WiMedia

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

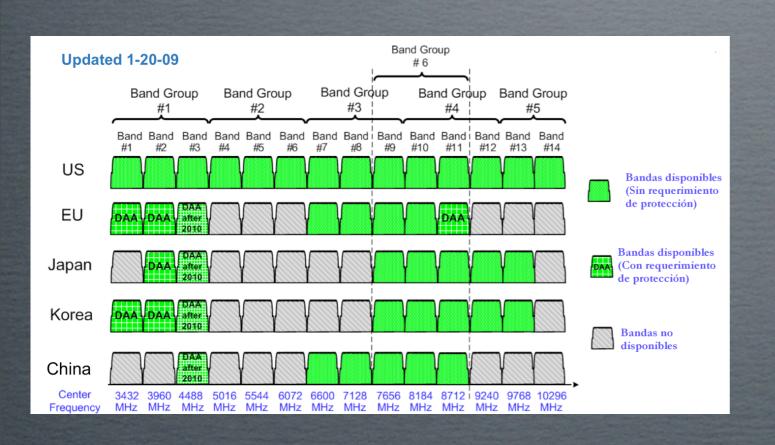

## - Requisitos del receptor

| Parámetro                    | Valor         |

|------------------------------|---------------|

| Sensibilidad (dBm)           | -83,6 a -72,6 |

| Máxima señal entrada (dBm)   | -41           |

| Figura de ruido (dB)         | 6 dB          |

| Ganancia de compresión (dBm) | -18,56 / -9   |

| Ganancia (dB)                | 50 / 64       |

| Control de ganancia (dB)     | 14            |

#### Estándar WiMedia

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

## - Requisitos del mezclador

| Parámetro            | Valor          |

|----------------------|----------------|

| Ganancia (dB)        | Máxima posible |

| Figura de ruido (dB) | < 18           |

| IIP3 (dBm)           | > -9           |

| Consumo (mA)         | Menor posible  |

| BW IF (MHz)          | > 250          |

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

### Bloque 1

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

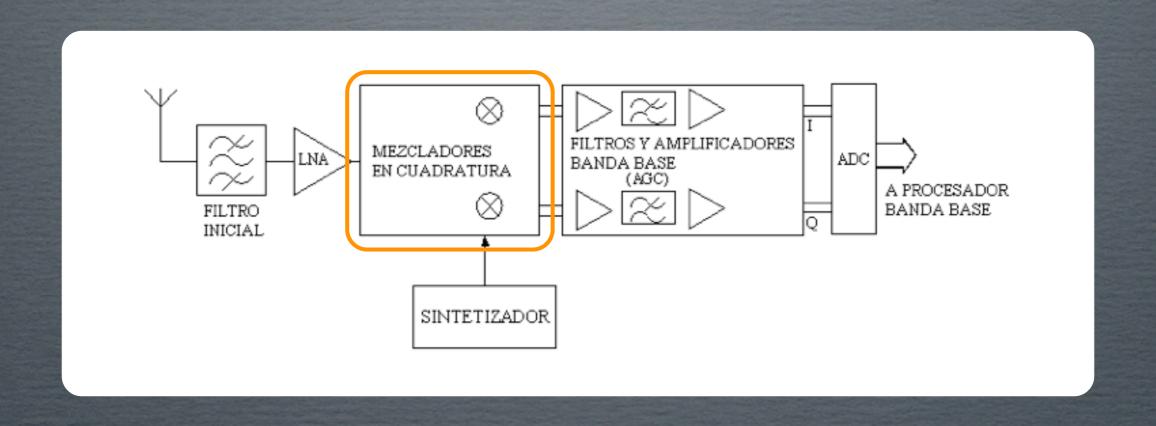

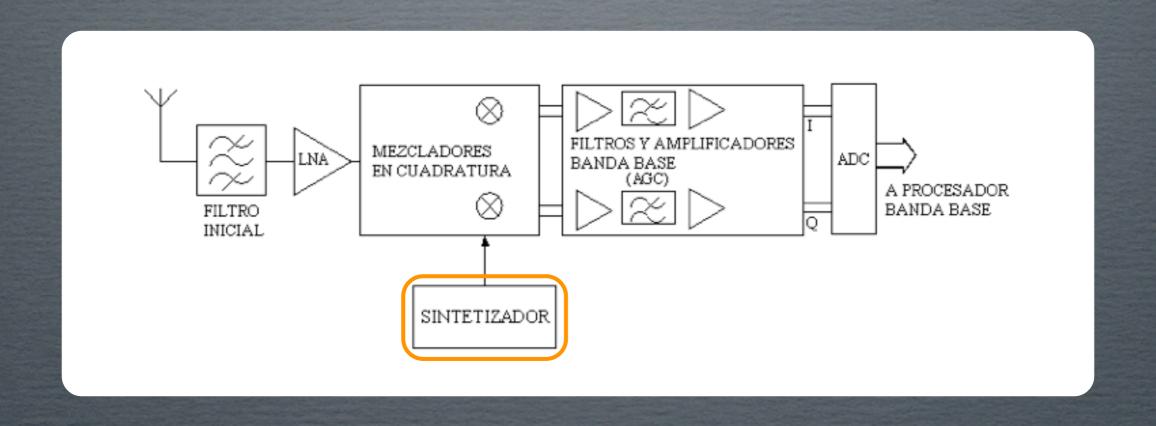

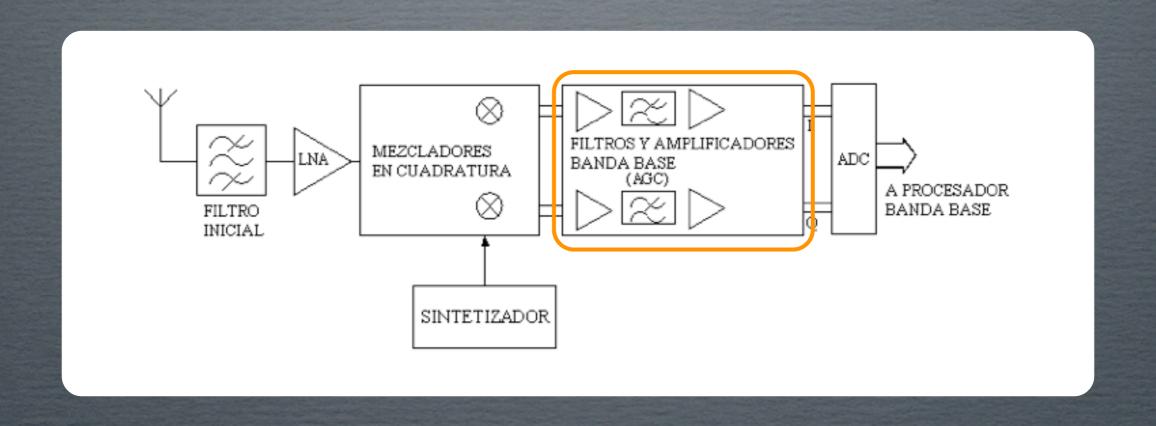

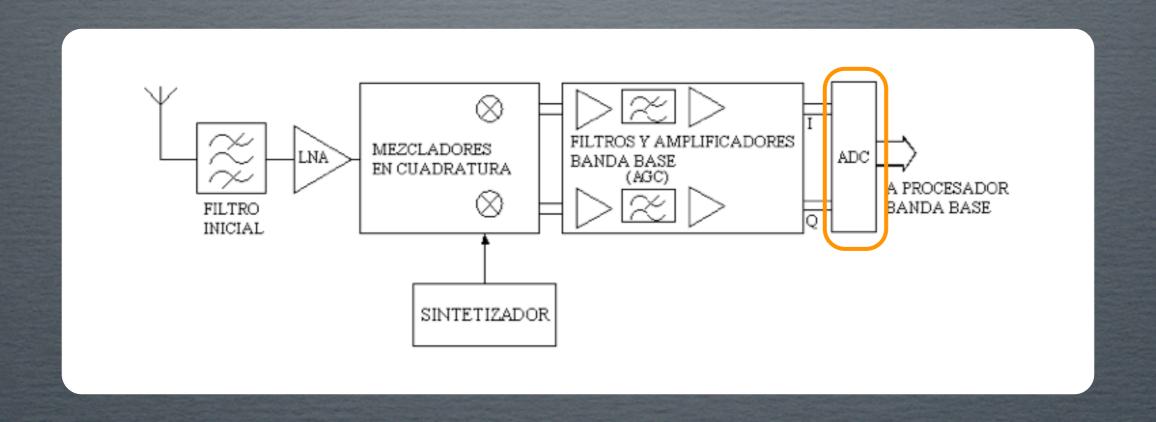

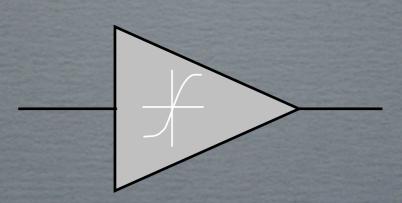

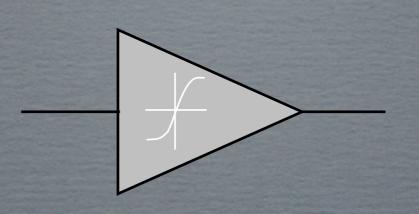

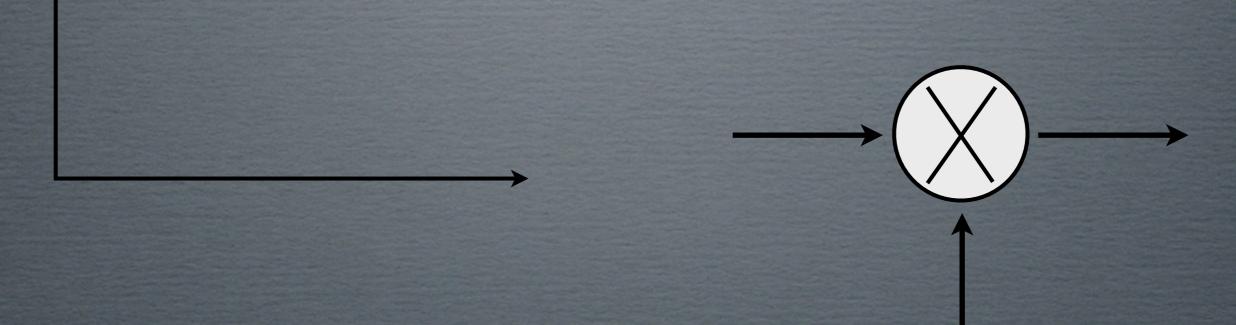

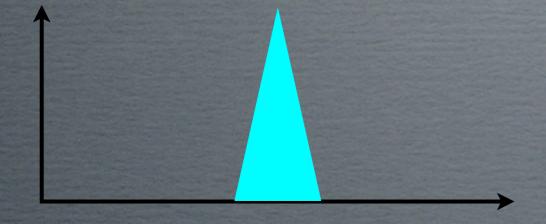

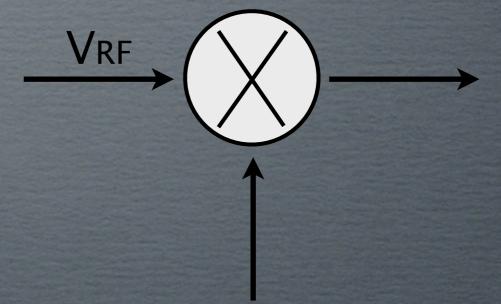

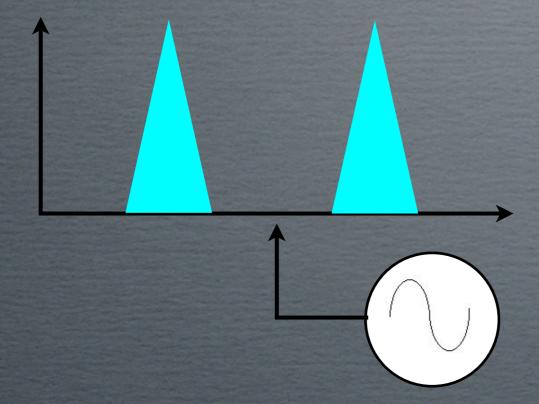

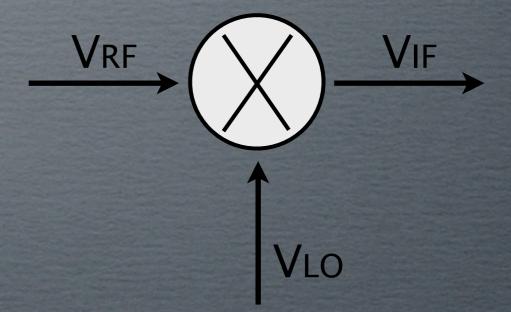

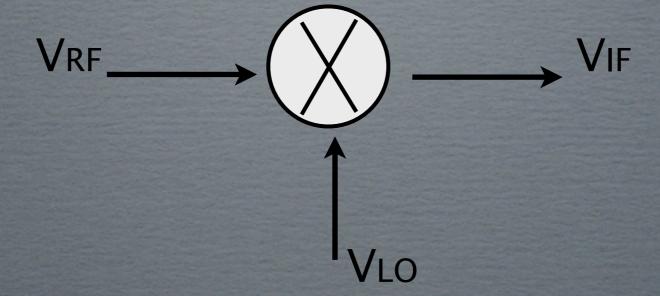

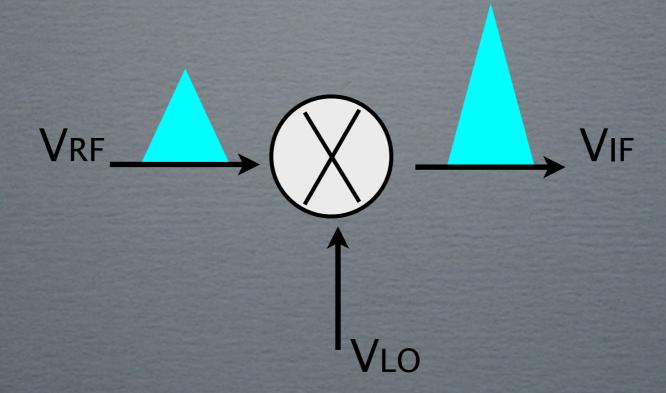

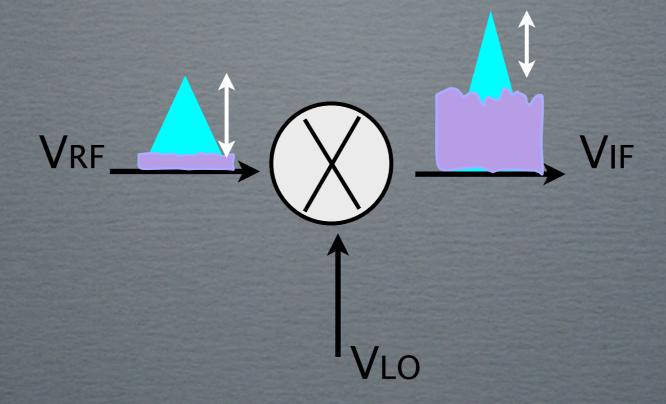

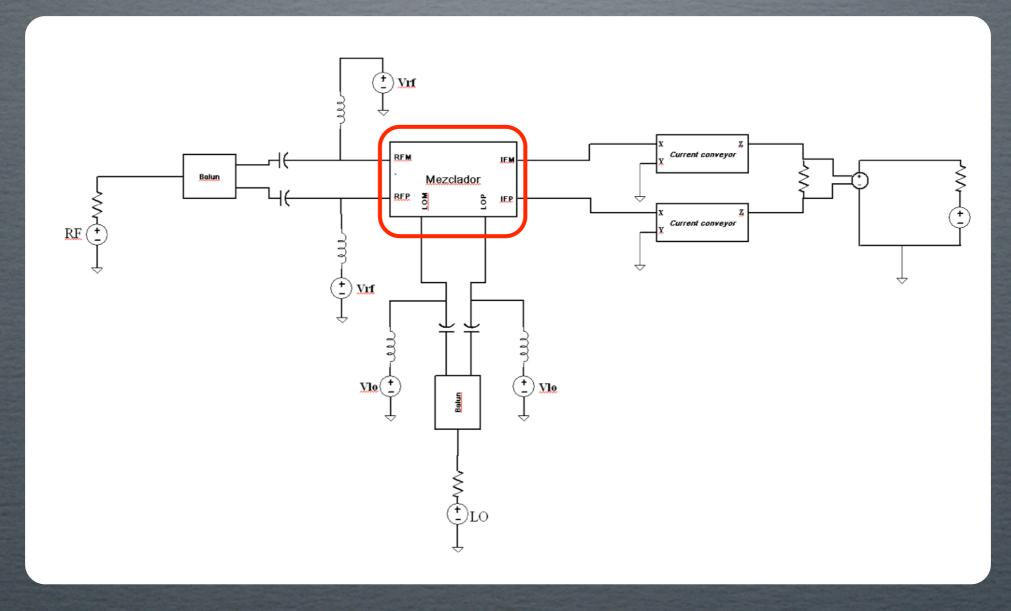

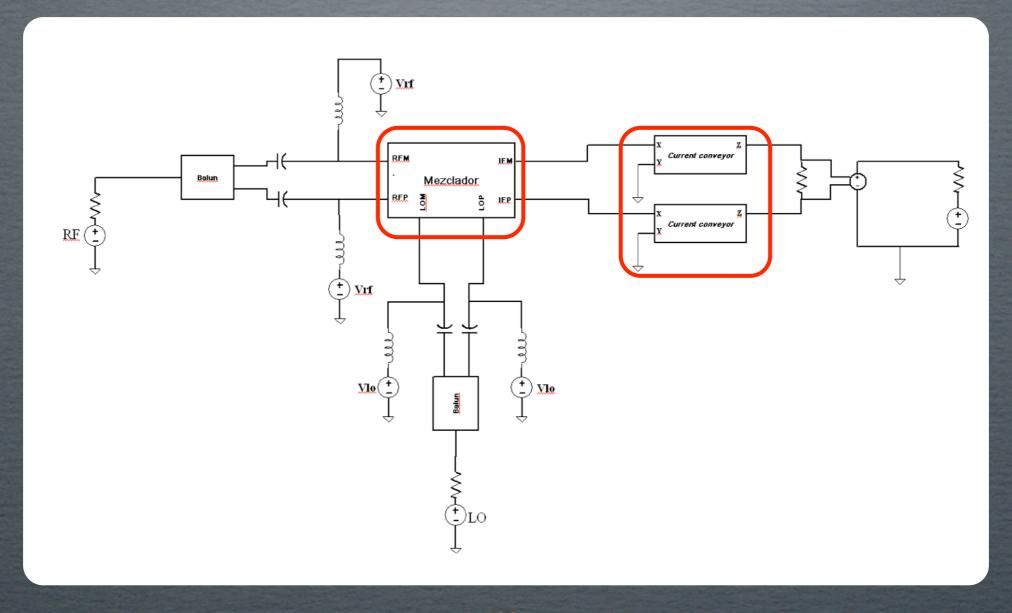

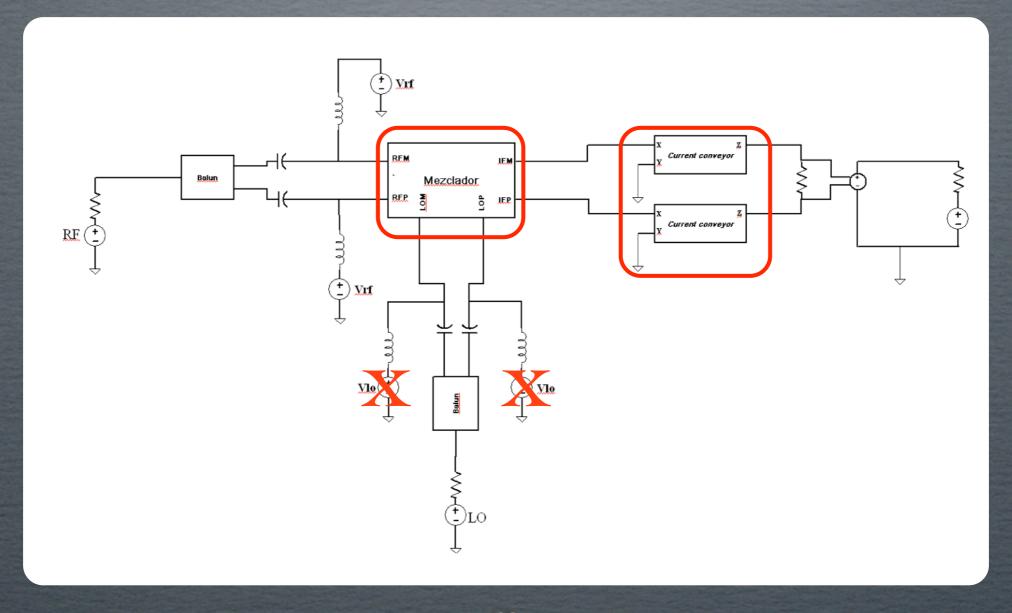

- Un mezclador traslada la señal a un rango de frecuencias diferente sin modificar las características de la señal

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Un mezclador traslada la señal a un rango de frecuencias diferente sin modificar las características de la señal

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Un mezclador traslada la señal a un rango de frecuencias diferente sin modificar las características de la señal

- Ganancia de conversión

#### Bloque 1

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Ganancia de conversiónFigura de ruido

### Bloque 1

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

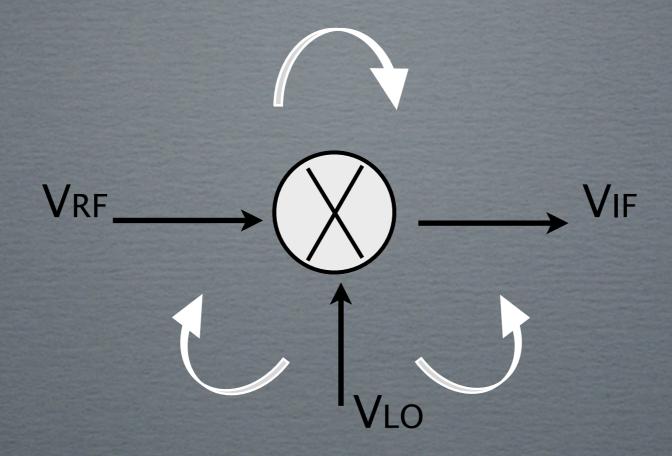

- Ganancia de conversión

- Figura de ruido

- Linealidad

Bloque 1

- Ganancia de conversión

- Figura de ruido

- Linealidad

- Aislamiento

Bloque 1

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

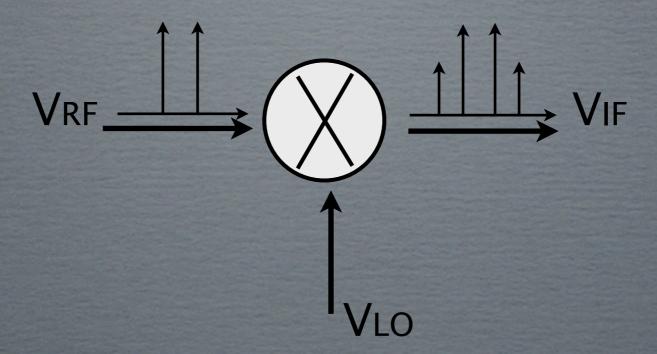

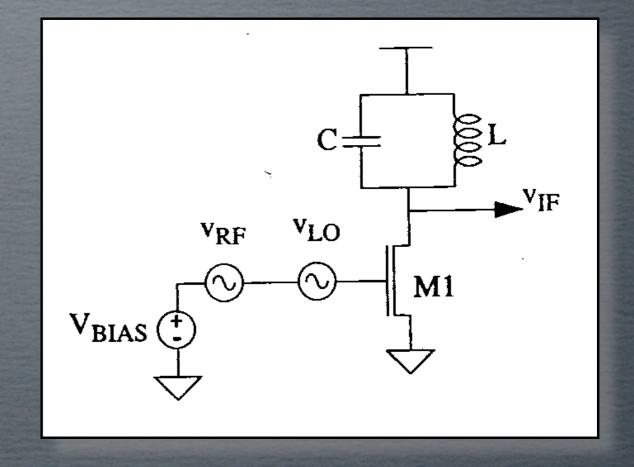

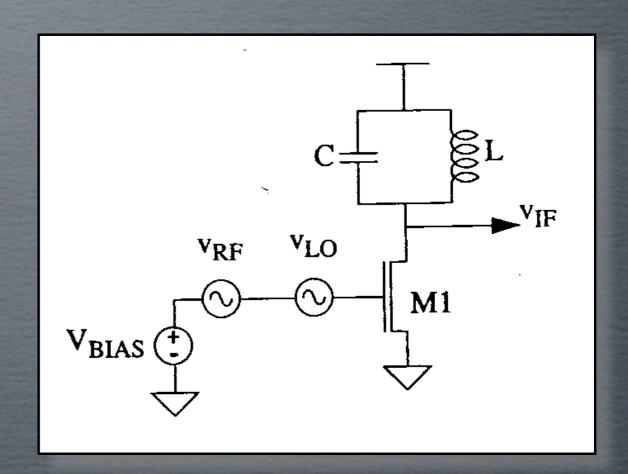

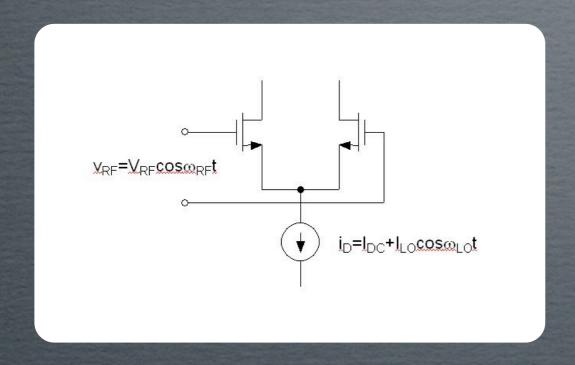

- Basados en sistemas no-lineales

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Basados en sistemas no-lineales

- Menor rendimiento

- RF y LO no están aisladas

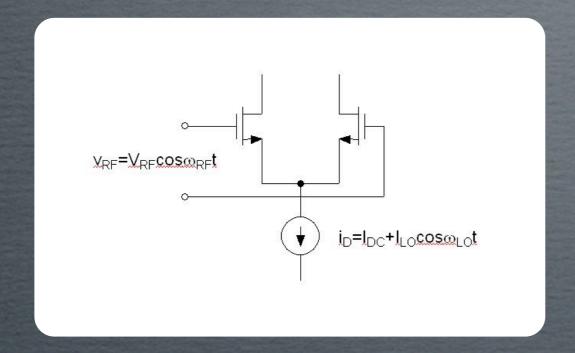

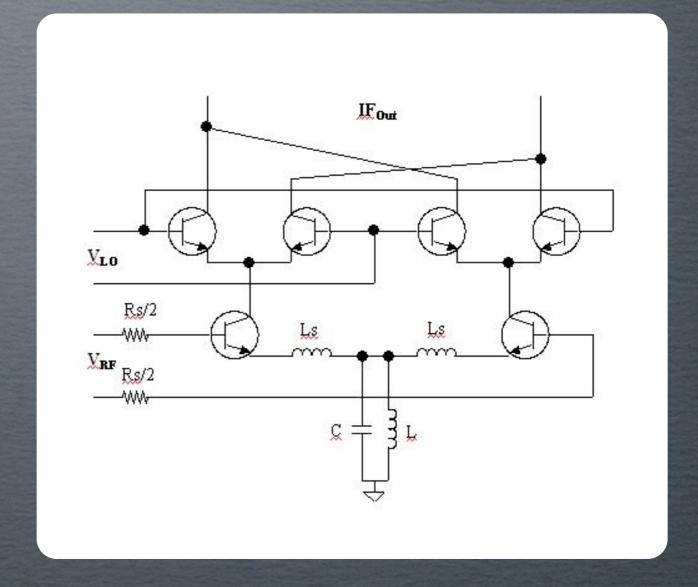

## - Basados en multiplicadores

#### Mezclador simple-balanceado

#### Bloque 1

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

## - Basados en multiplicadores

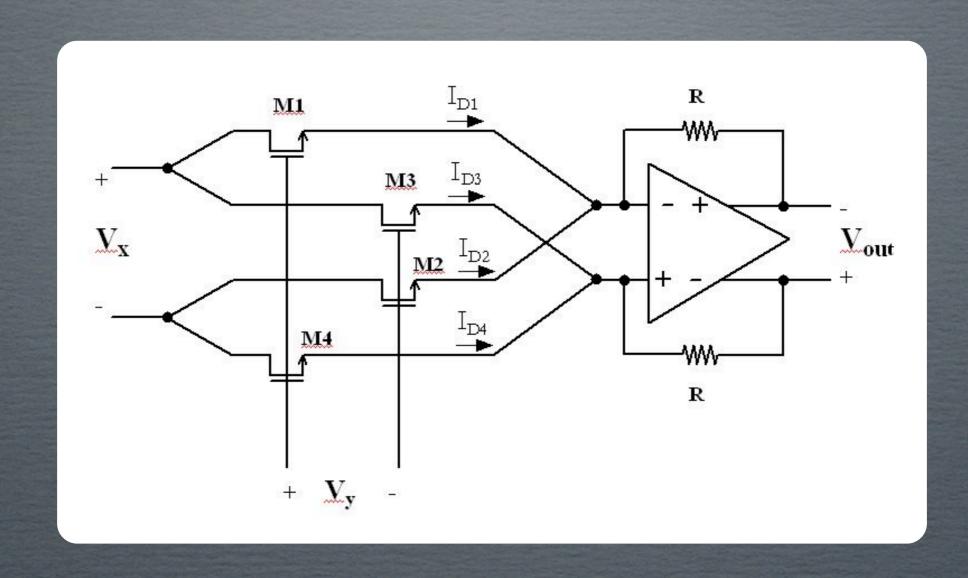

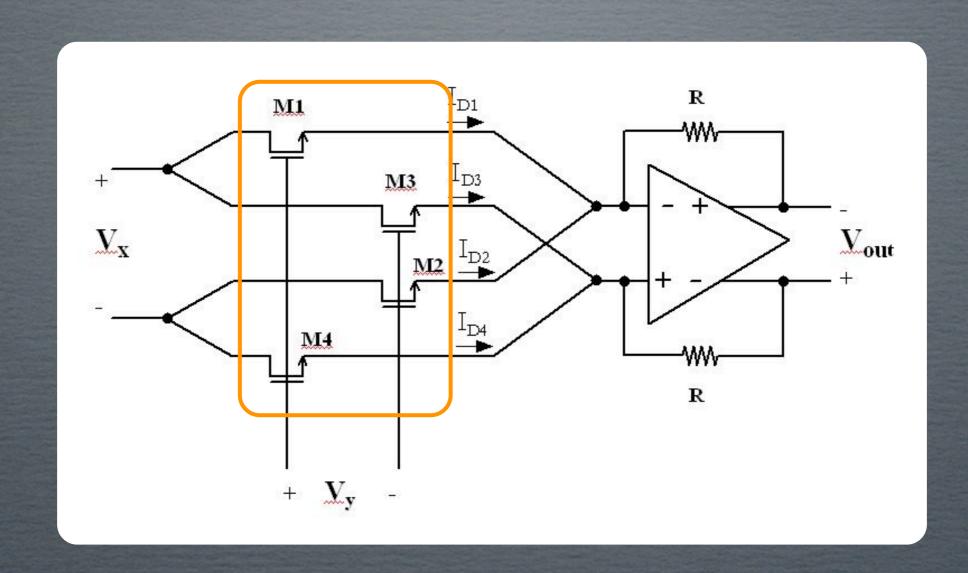

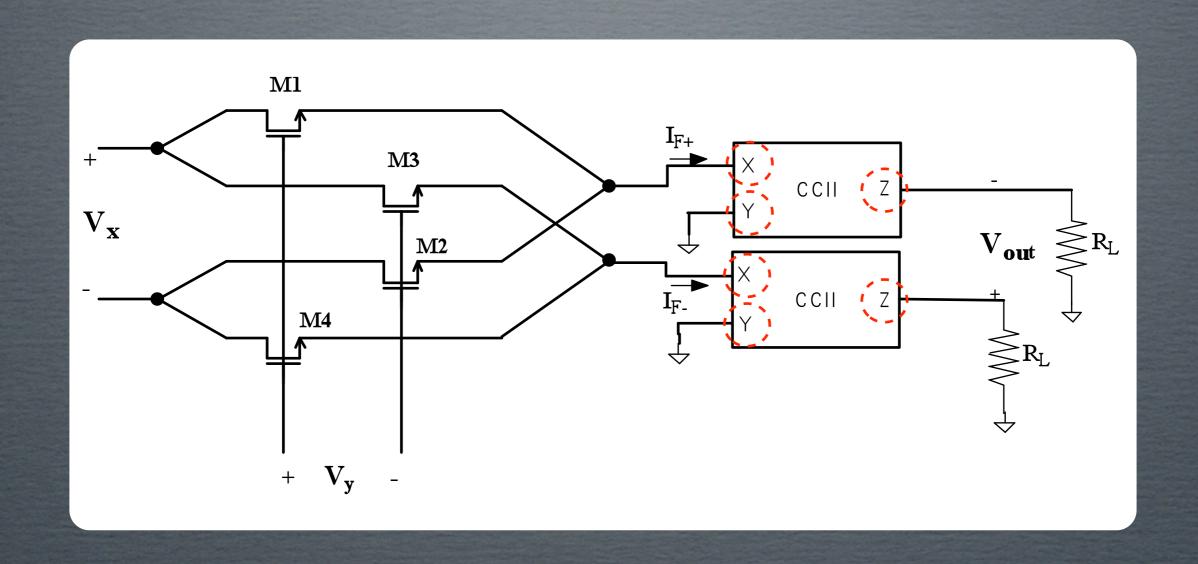

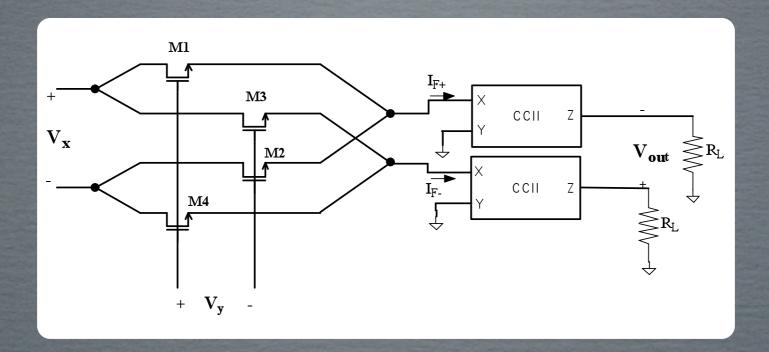

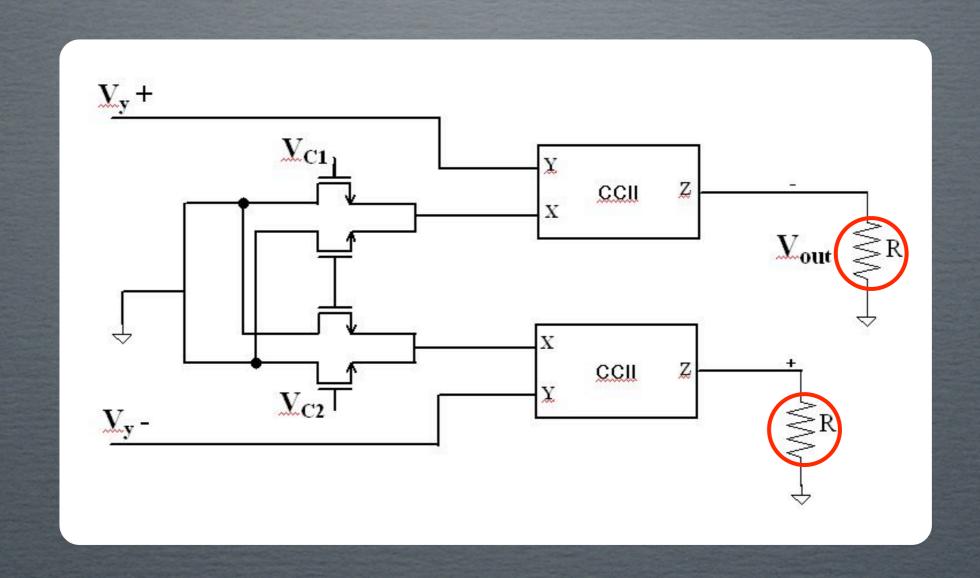

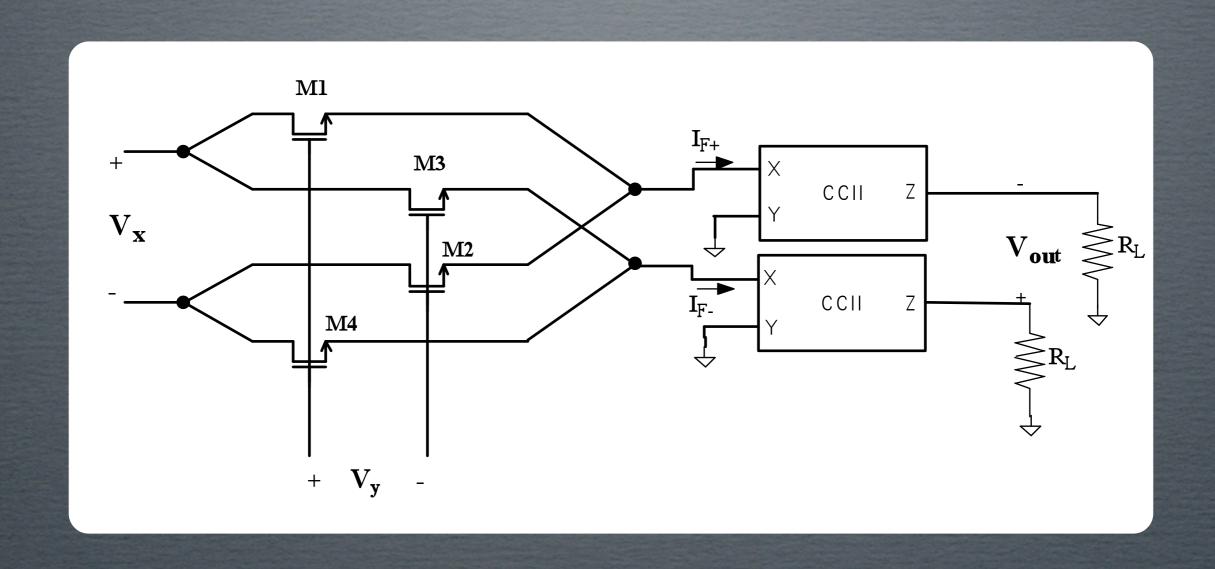

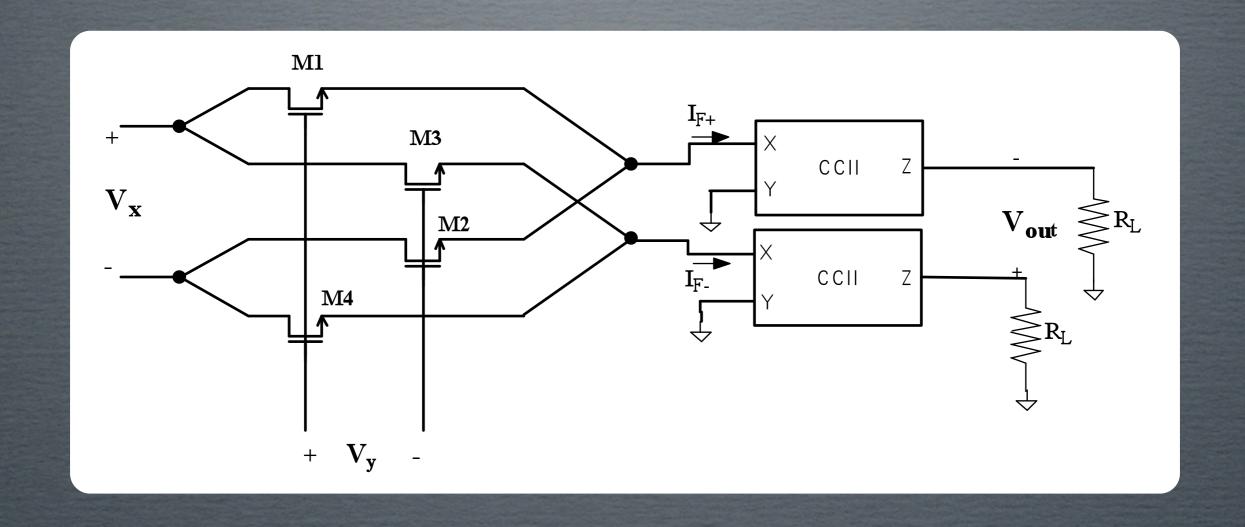

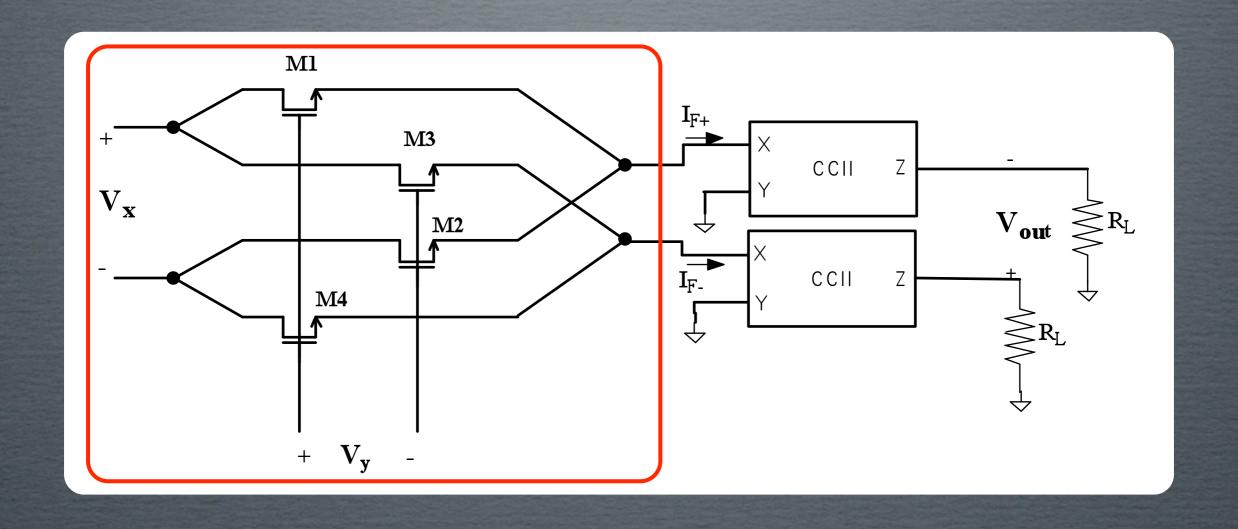

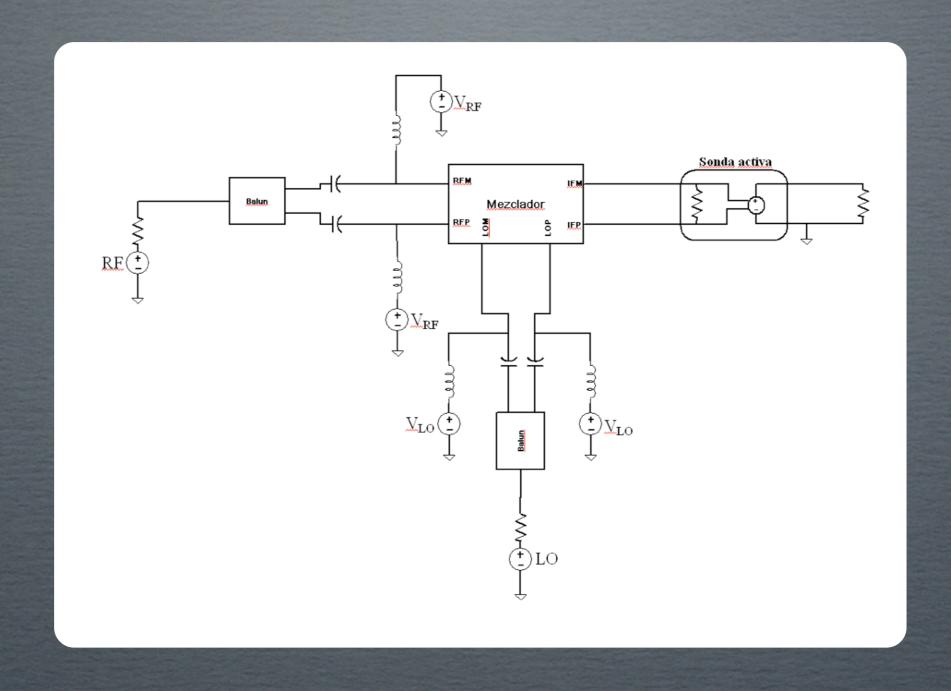

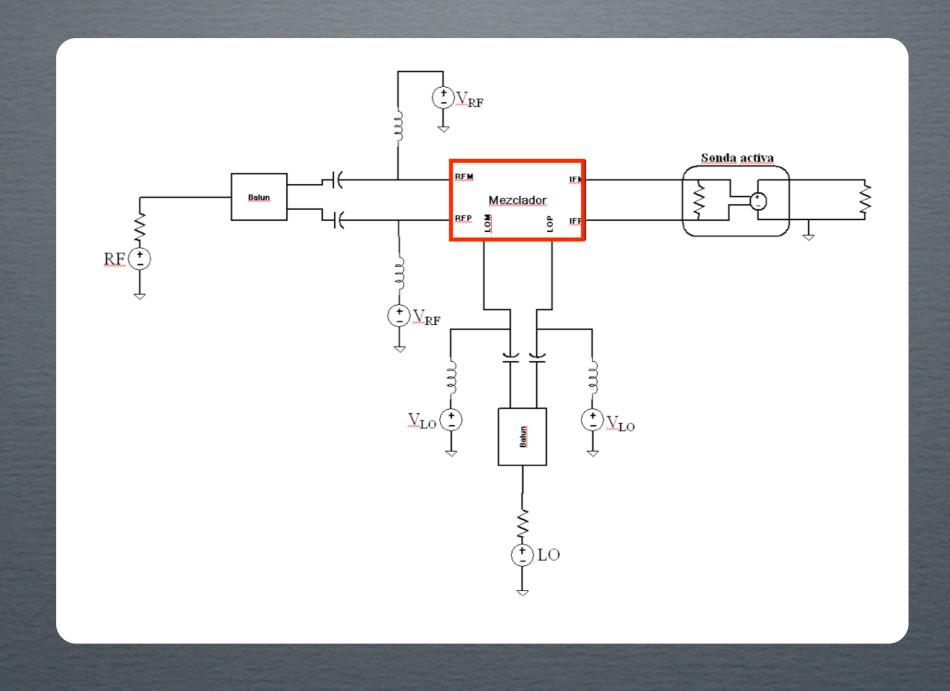

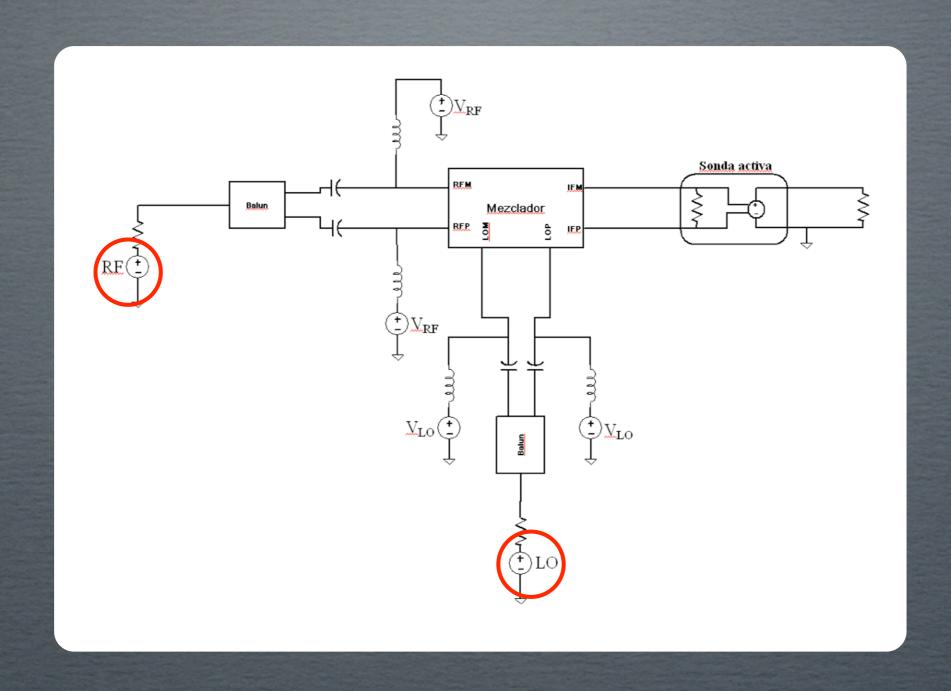

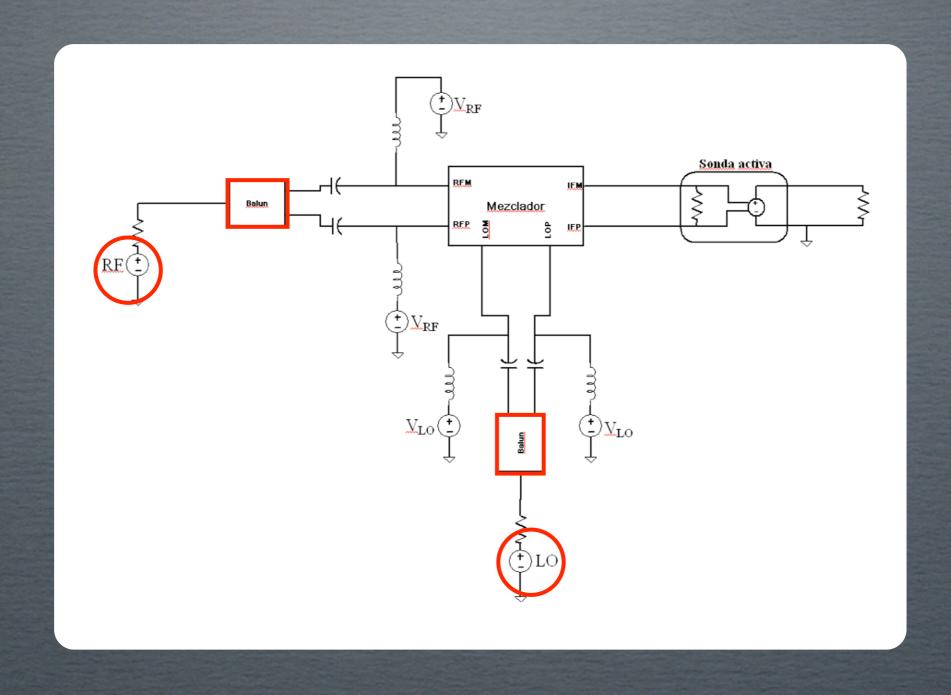

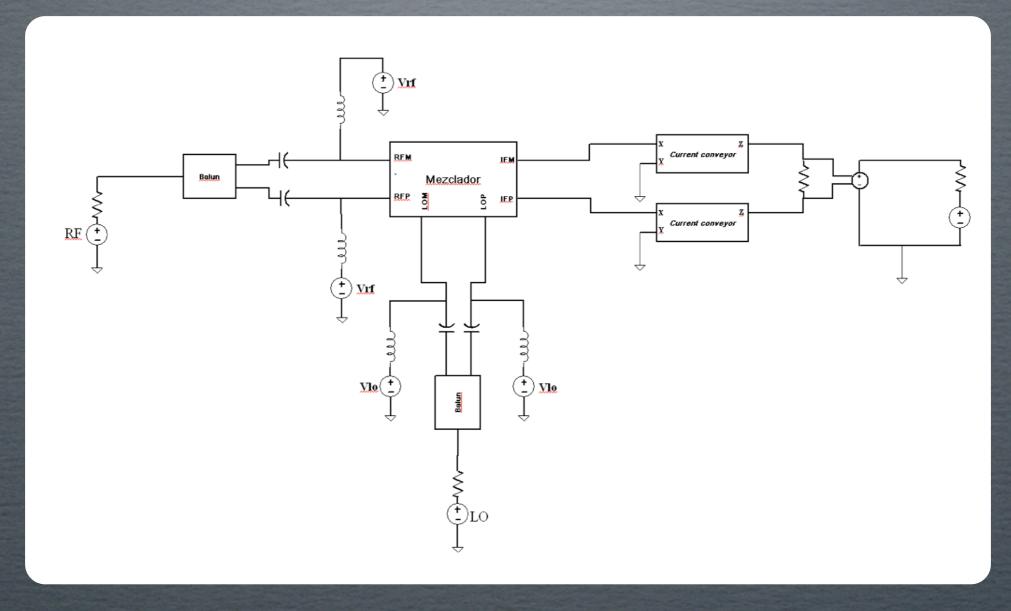

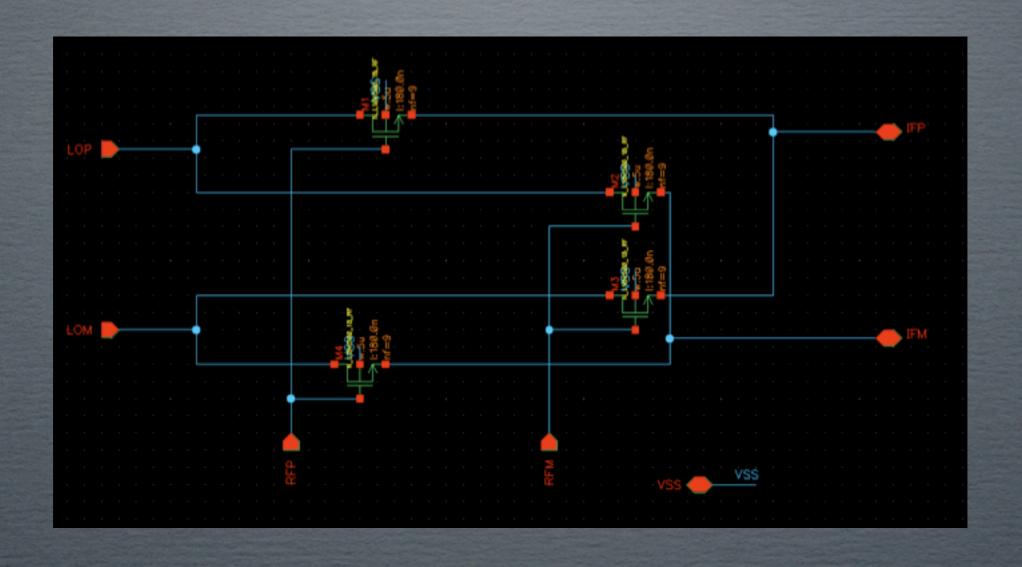

Mezclador doble balanceado (Célula de Gilbert)

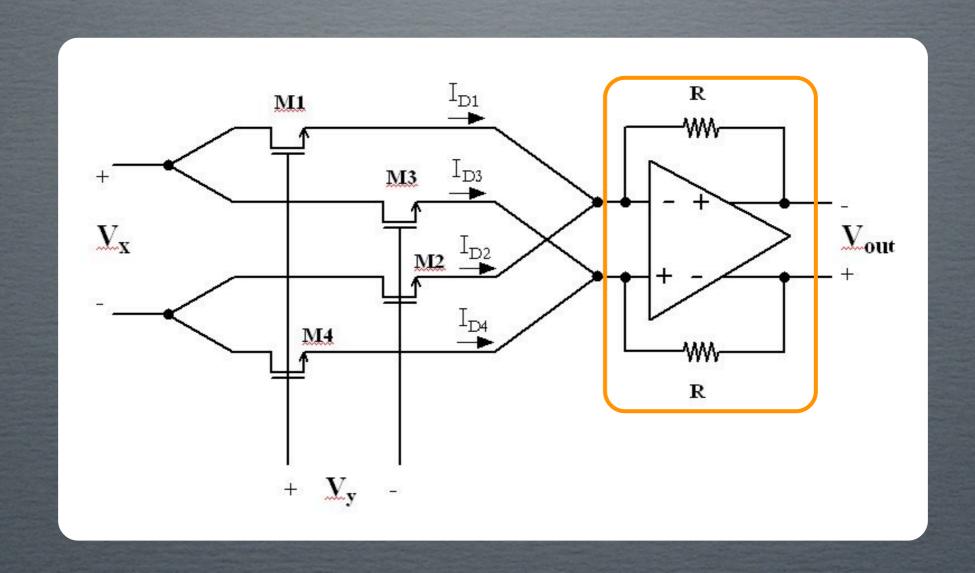

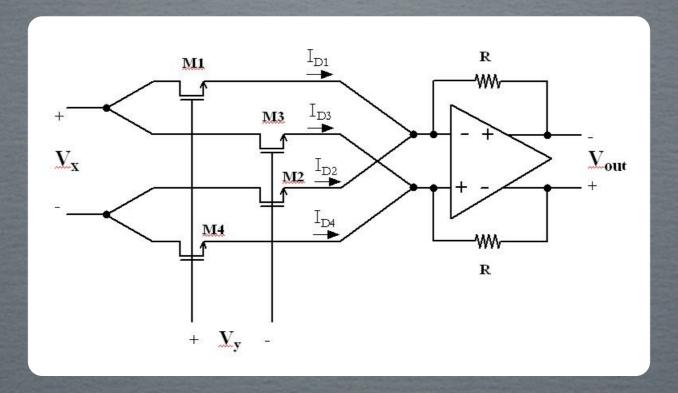

### Bloque 1

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

$$V_{o-} = -R(I_{D1} + I_{D2})$$

$$V_{o+} = -R (I_{D3} + I_{D4})$$

$$V_{out} = V_{o+} - V_{o-} = -R (I_{D1} + I_{D2} - I_{D3} - I_{D4})$$

#### Bloque 1

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

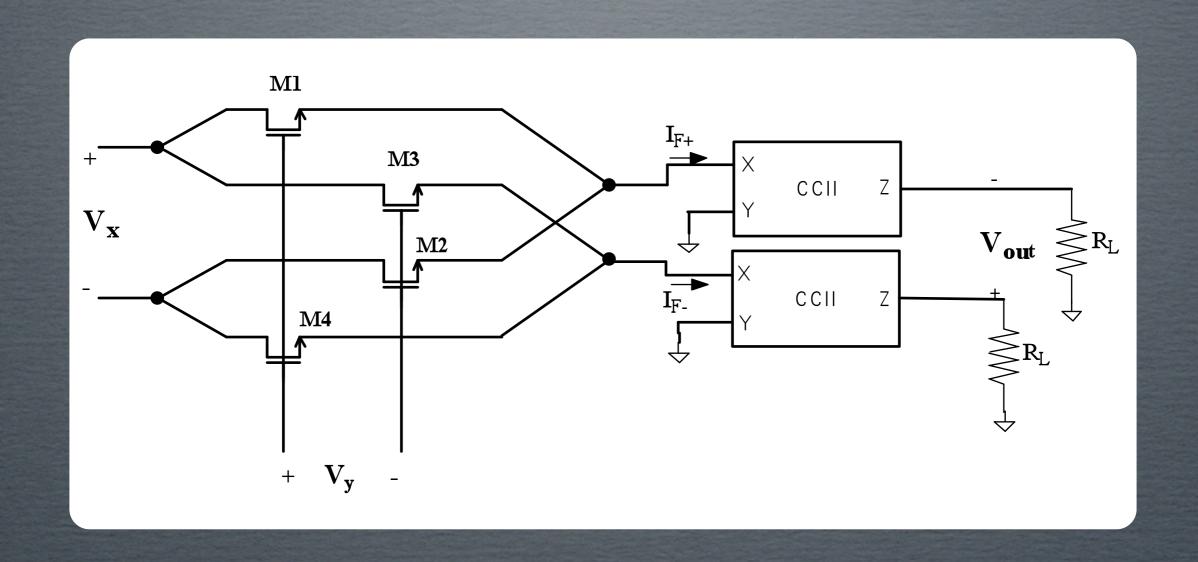

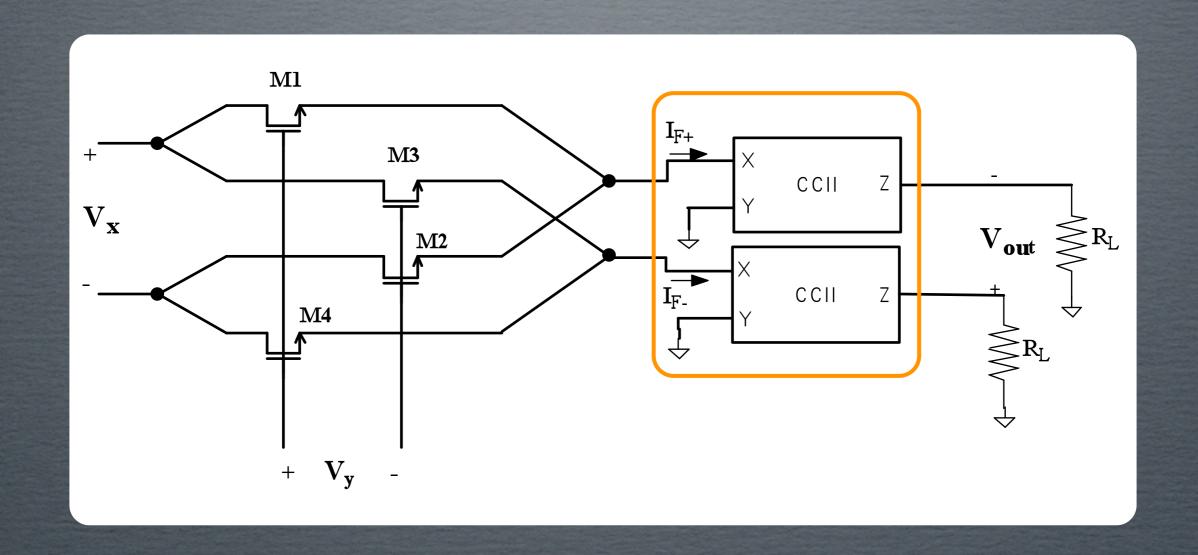

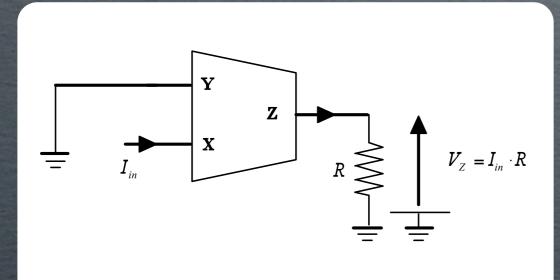

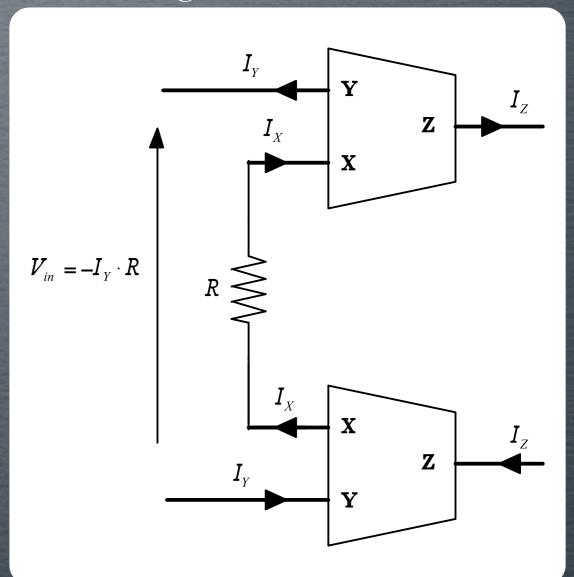

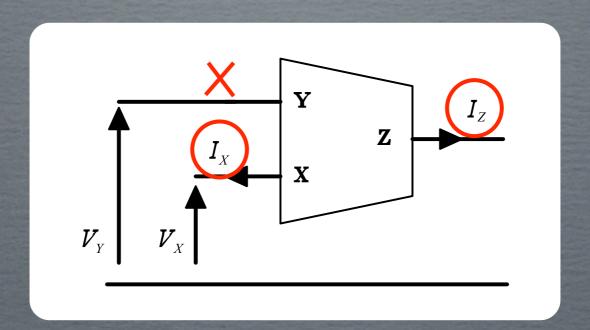

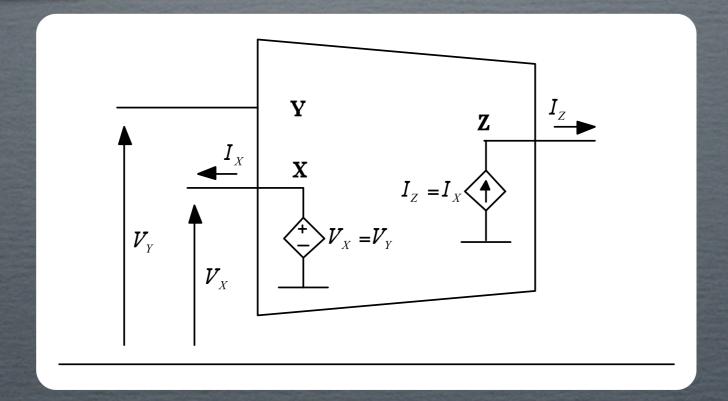

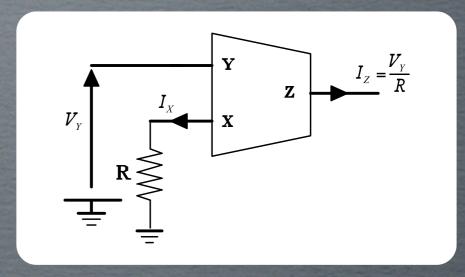

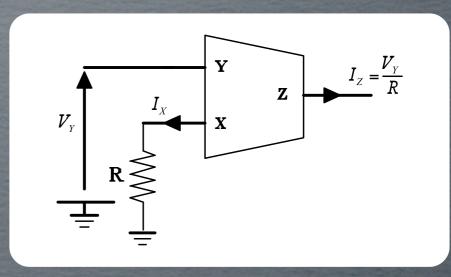

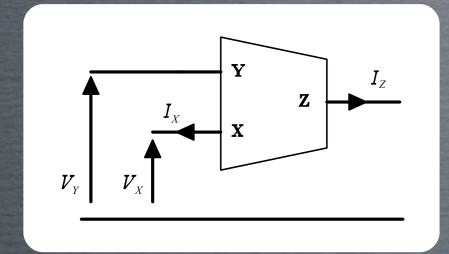

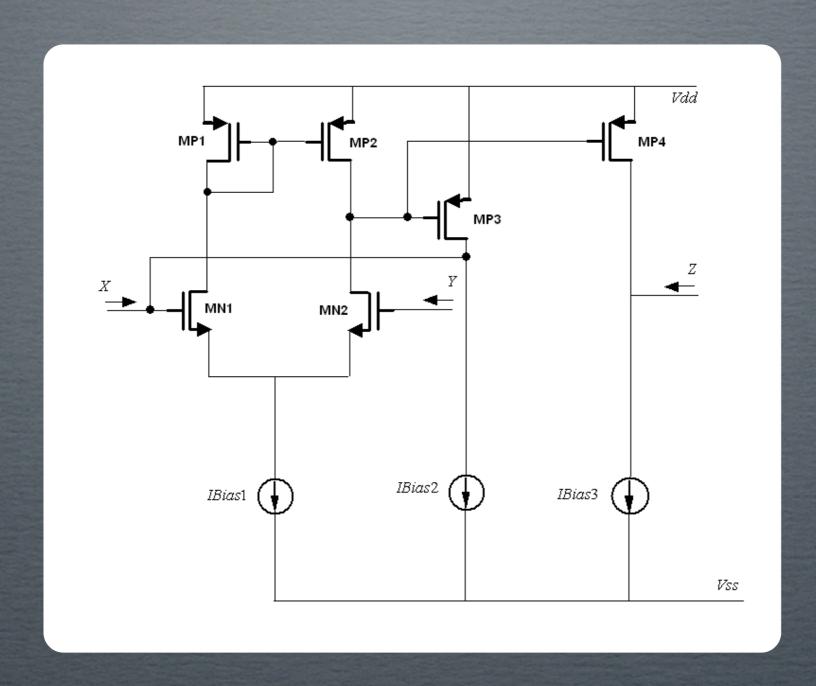

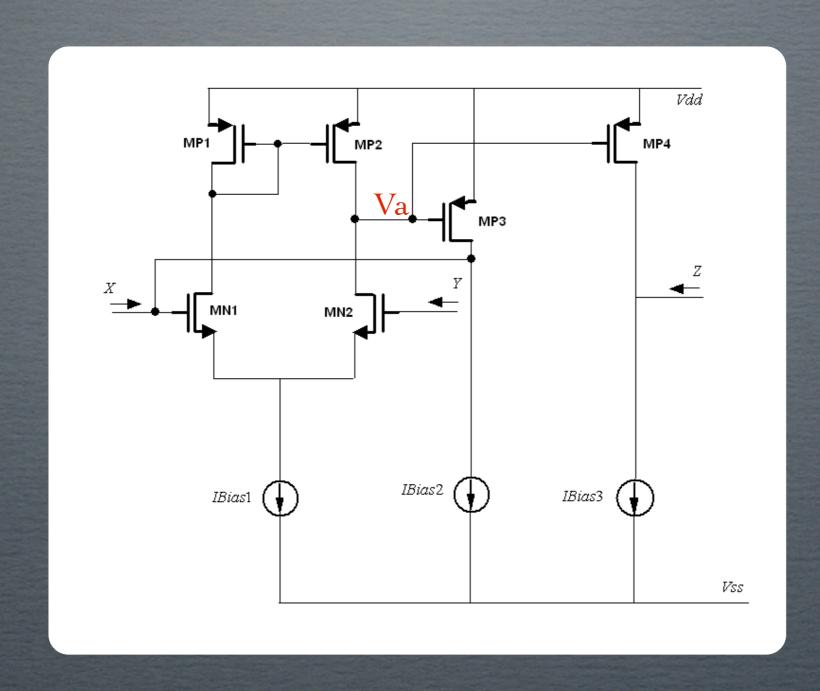

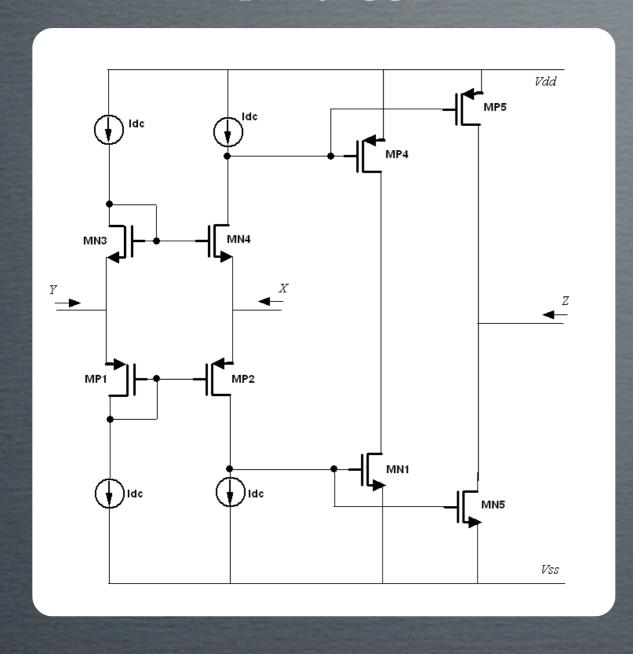

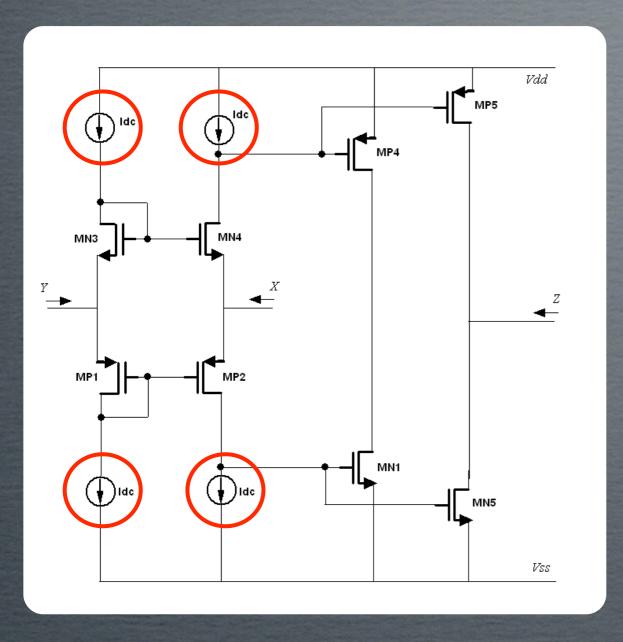

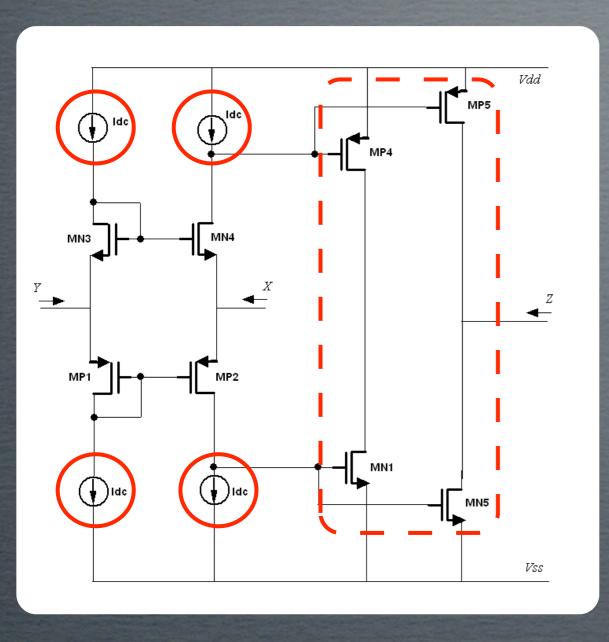

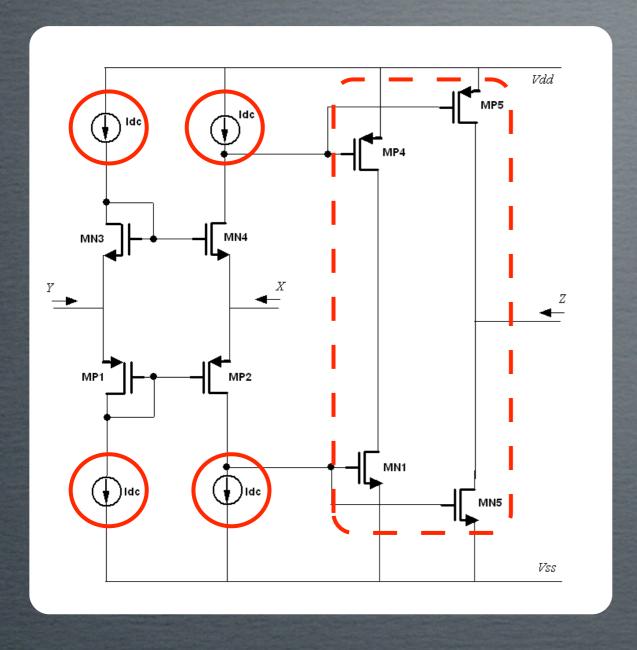

$$V_X = V_Y$$

$$V_Y = 0 \longrightarrow V_X = 0$$

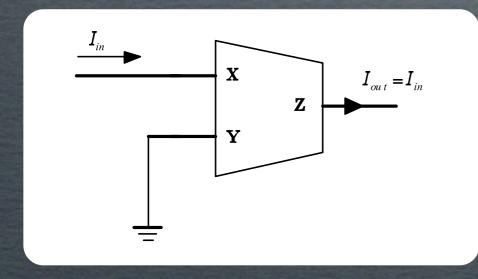

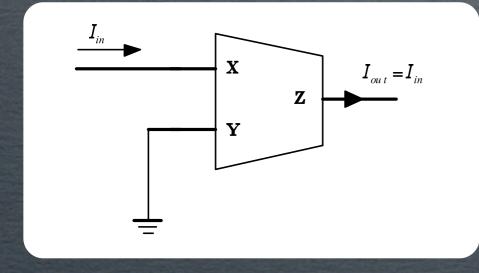

$$I_X = I_Z$$

$$V_{out+} = R_L I_{F+}$$

$$V_{\text{out-}} = R_L I_{F-}$$

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

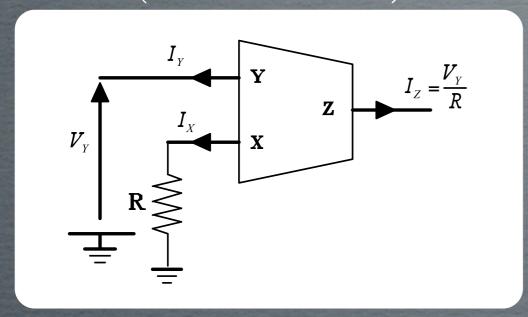

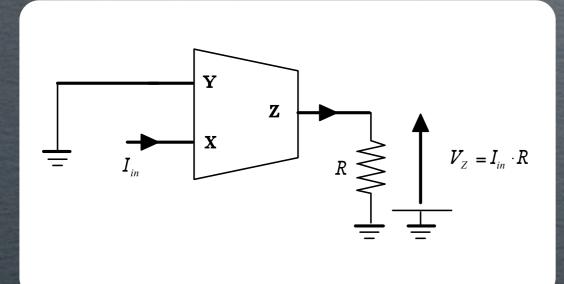

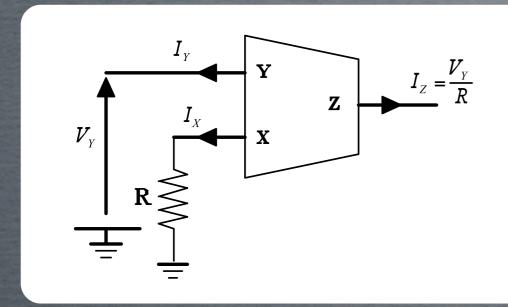

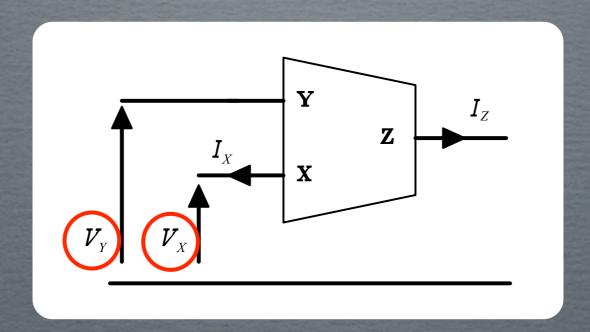

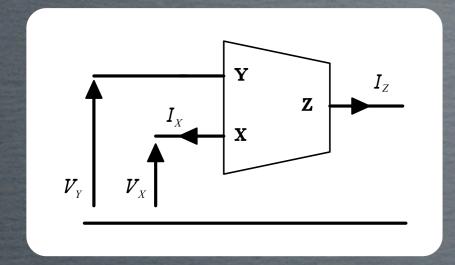

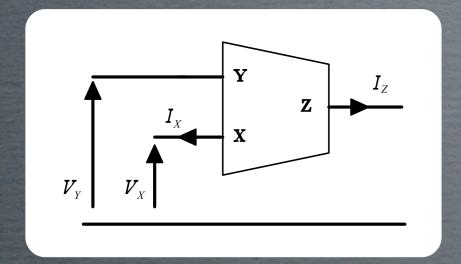

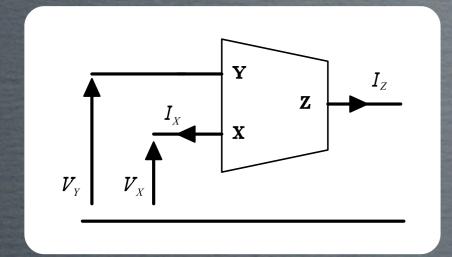

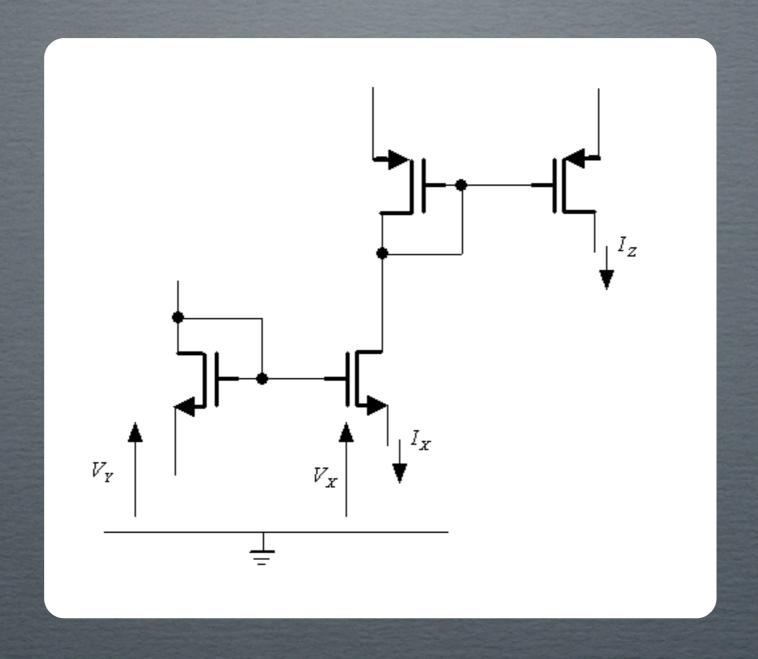

# Current conveyor de primera generación (CCI)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCI | Nivel de impedancia |

|---------------|---------------------|

| Х             | Bajo (idealmente 0) |

| Υ             | Bajo (idealmente 0) |

| Z             | Alto (idealmente ∞) |

# Current conveyor de primera generación (CCI)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCI | Nivel de impedancia |

|---------------|---------------------|

| Х             | Bajo (idealmente 0) |

| Υ             | Bajo (idealmente 0) |

| Z             | Alto (idealmente ∞) |

# Current conveyor de primera generación (CCI)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCI | Nivel de impedancia  |

|---------------|----------------------|

| Х             | Bajo (ide almente 0) |

| Υ             | Bajo (ide almente 0) |

| Z             | Alto (idealmente ∞)  |

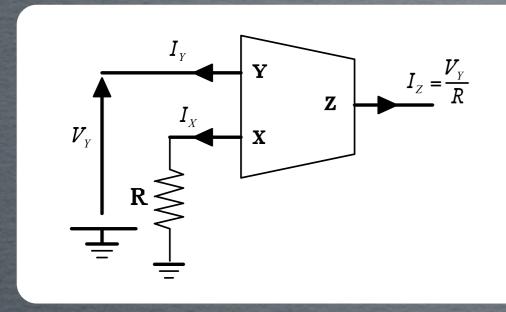

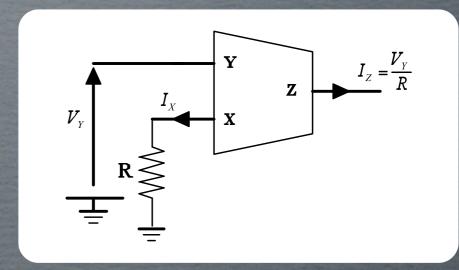

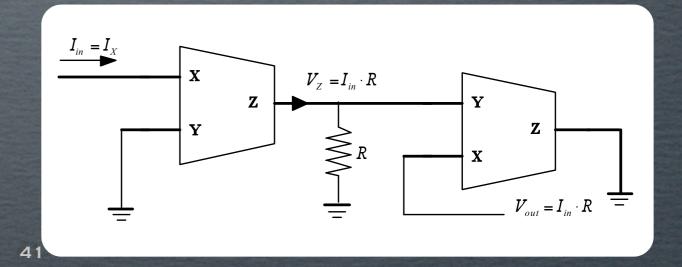

# Bloque 1

Convertidor de V-I (Transconductor)

#### Bloque 1

Convertidor de V-I

(Transconductor)

Convertidor de I-V (Transimpedancia)

#### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría current conveyor

# Convertidor de V-I (Transconductor)

# Convertidor de I-V (Transimpedancia)

# Convertidor de impedancia negativa diferencial

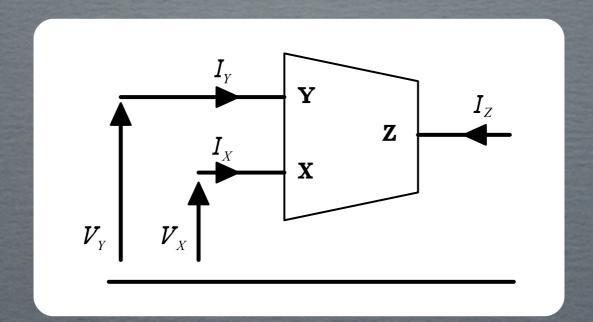

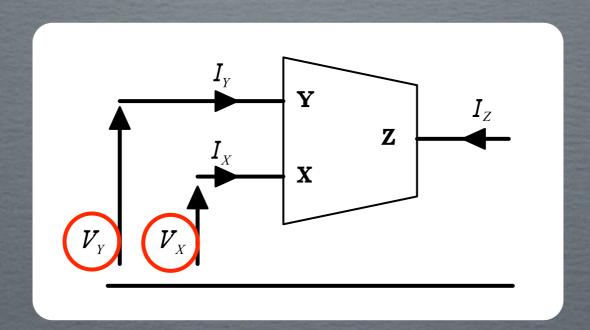

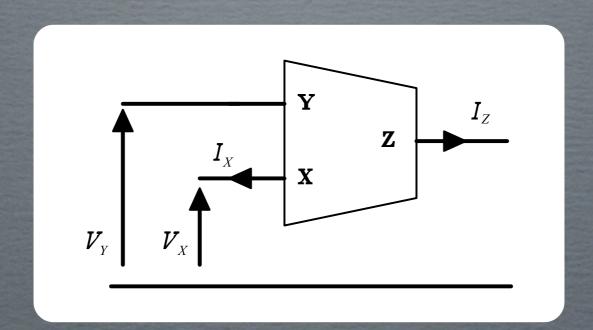

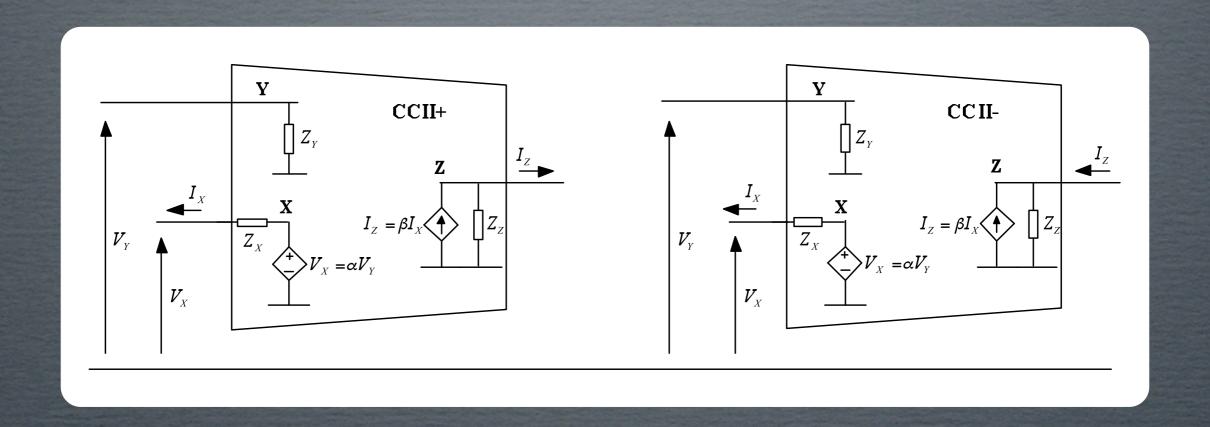

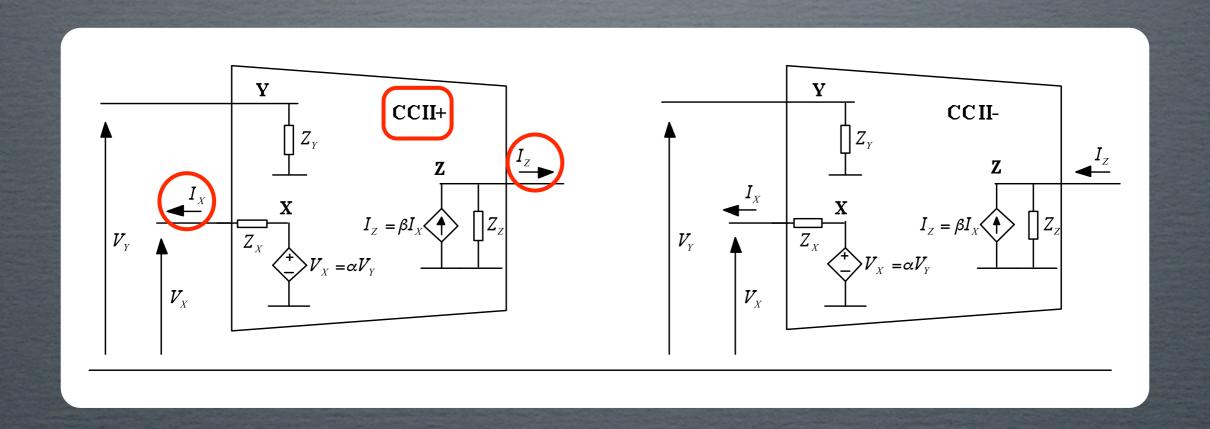

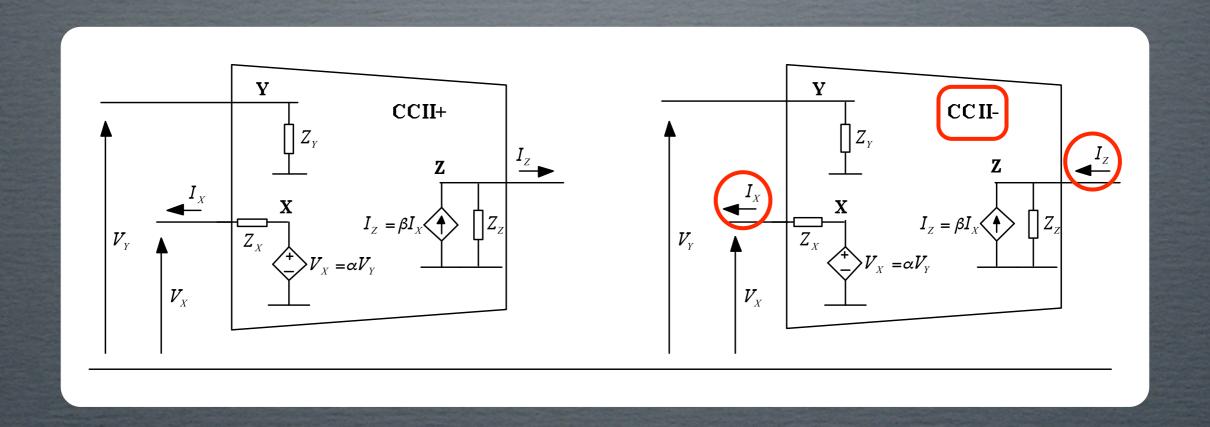

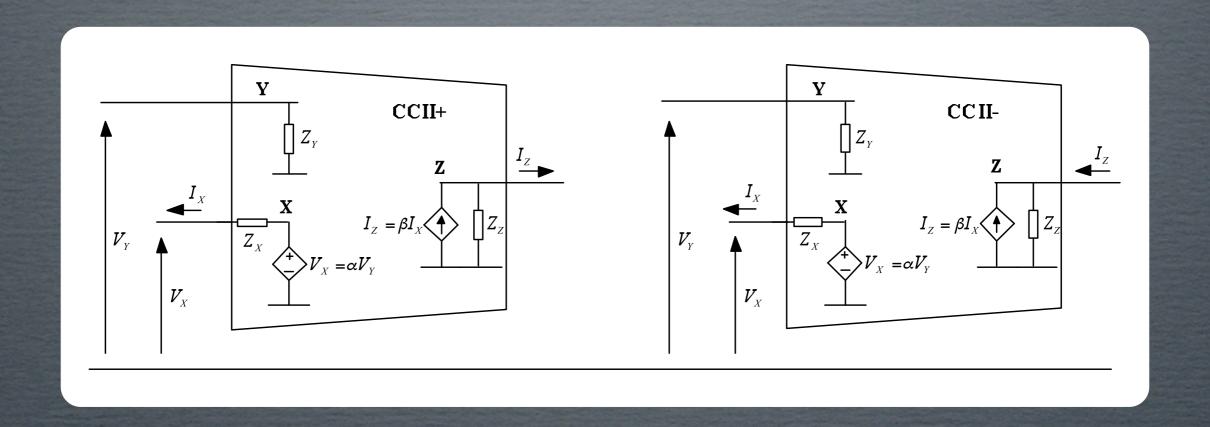

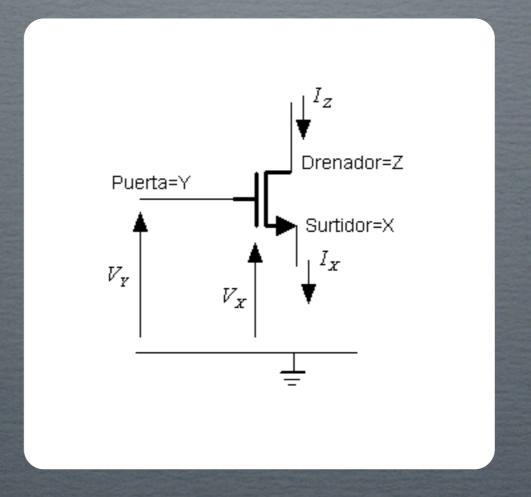

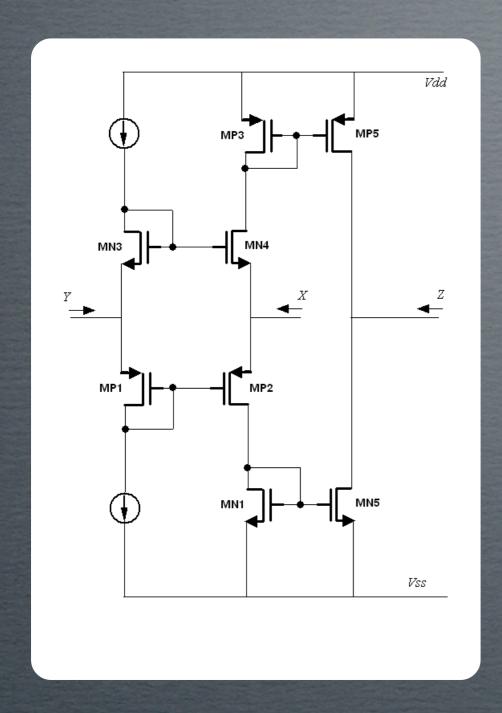

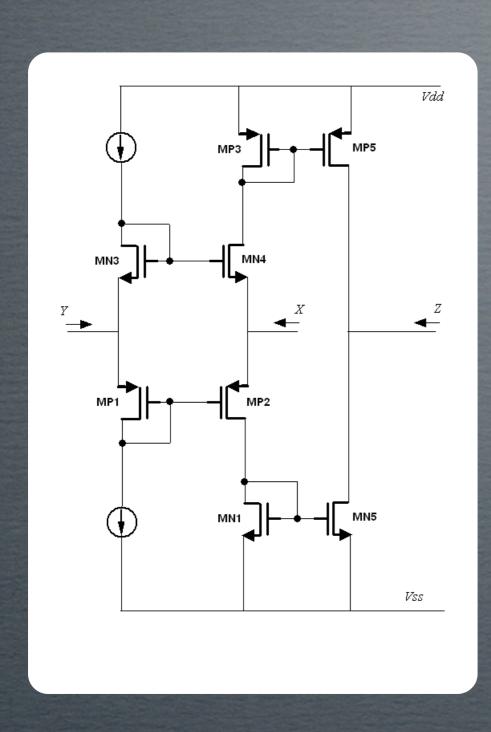

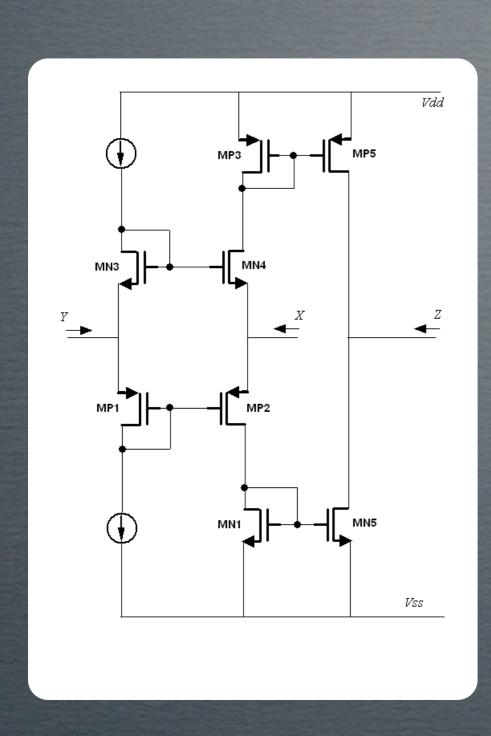

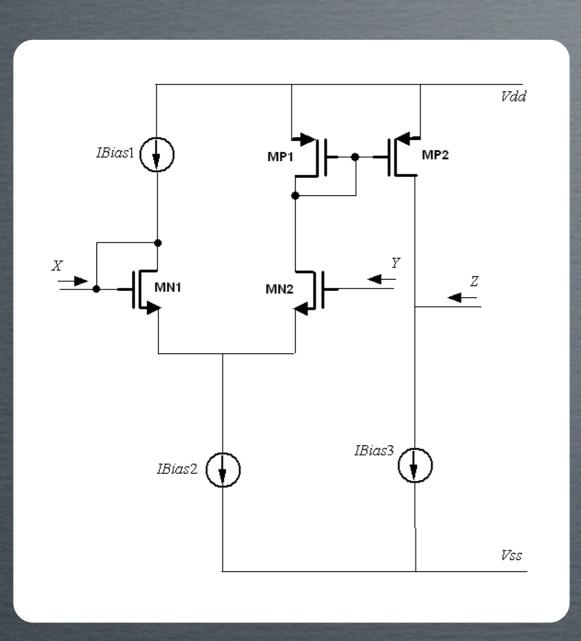

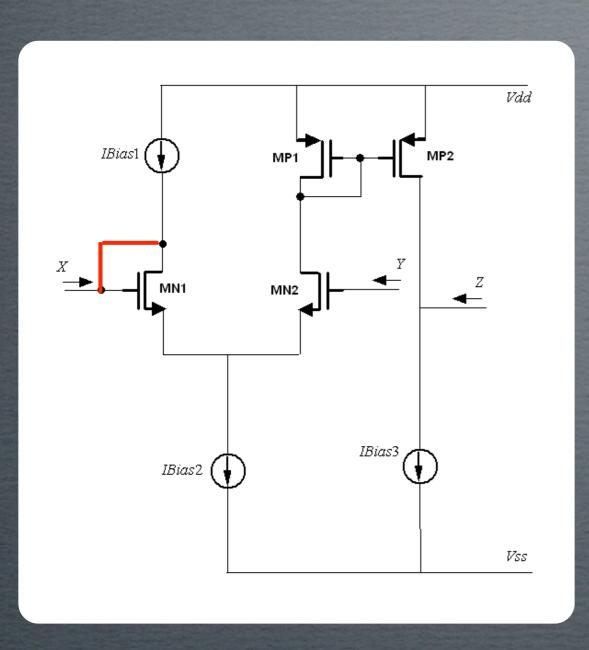

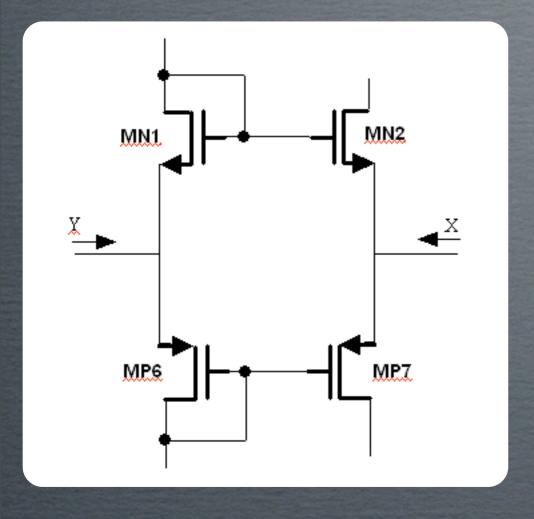

# Current conveyor de segunda generación (CCII)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCII | Ni∨el de impedancia  |

|----------------|----------------------|

| Х              | Bajo (ide almente 0) |

| Υ              | Alto (idealmente ∞)  |

| z              | Alto (idealmente ∞)  |

# Current conveyor de segunda generación (CCII)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCII | Nivelde impedancia   |

|----------------|----------------------|

| Х              | Bajo (ide almente 0) |

| Υ              | Alto (idealmente ∞)  |

| Z              | Alto (idealmente ∞)  |

# Current conveyor de segunda generación (CCII)

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}$$

| Nodos del CCII | Ni∨elde impedancia   |

|----------------|----------------------|

| Х              | Bajo (ide almente 0) |

| Υ              | Alto (idealmente ∞)  |

| Z              | Alto (idealmente ∞)  |

El modelo ideal está formado por una fuente de tensión y otra de corriente ideales

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Fuente de tensión controlada por tensión

#### Bloque 1

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

Fuente de tensión controlada por tensión

Fuente de corriente controlada por tensión

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría current conveyor

Fuente de tensión controlada por tensión

Fuente de corriente controlada por corriente

Fuente de corriente controlada por tensión

### Bloque 1

Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores

Teoría current conveyor

Fuente de tensión controlada por tensión

Fuente de corriente controlada por corriente

Fuente de corriente controlada por tensión

Fuente de tensión controlada por corriente

#### Bloque 1

#### Bloque 1

#### Bloque 1

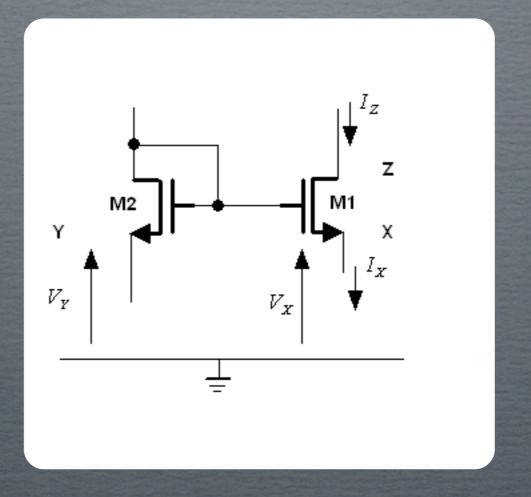

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

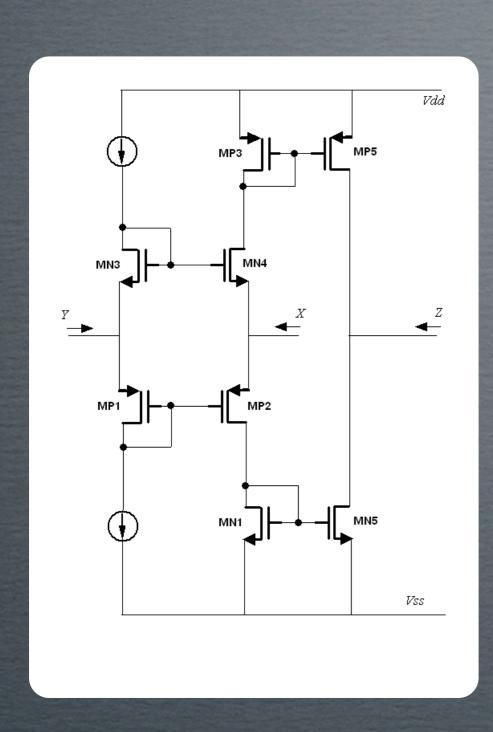

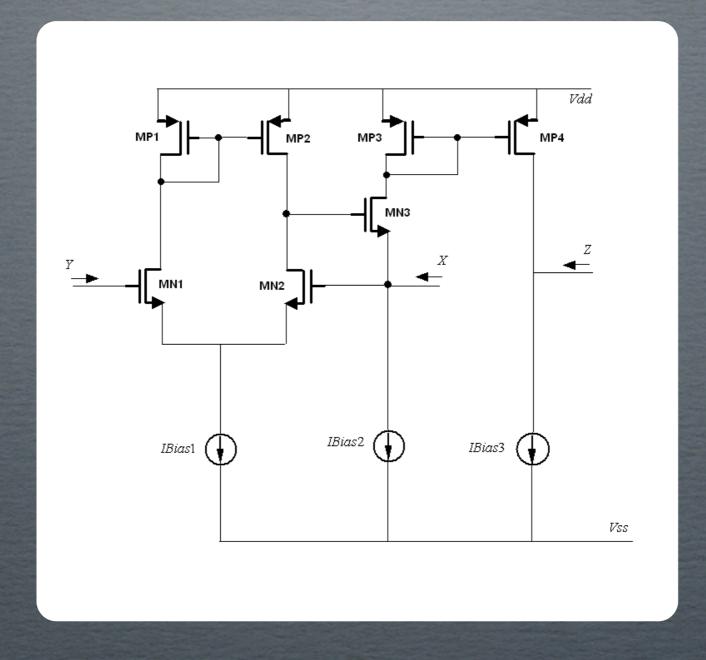

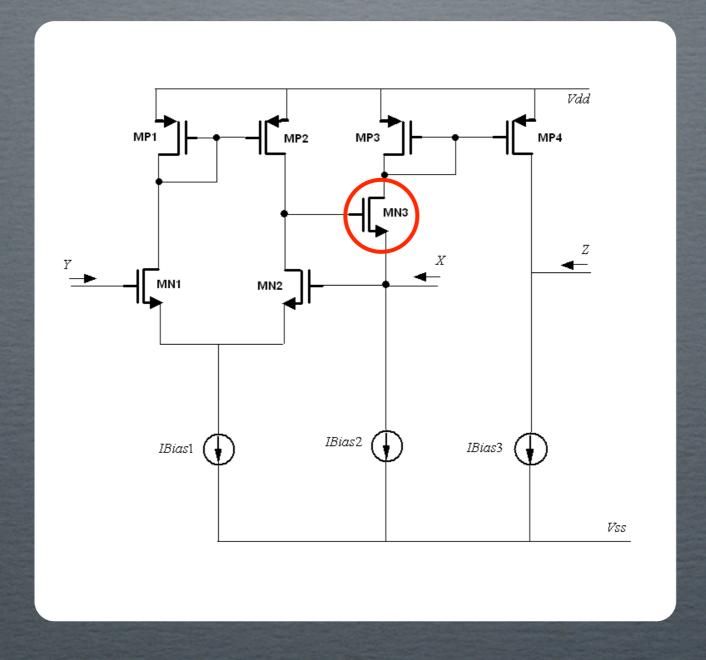

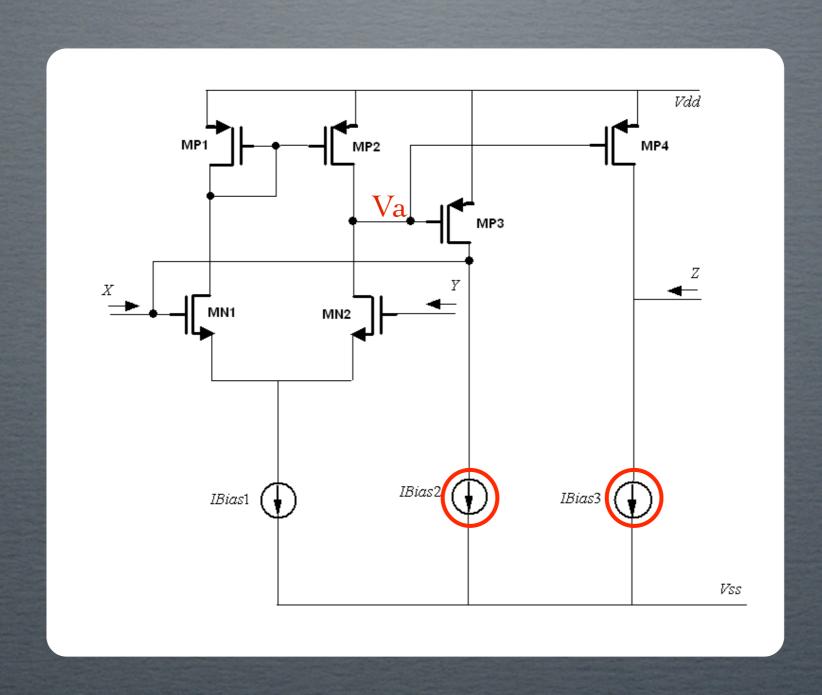

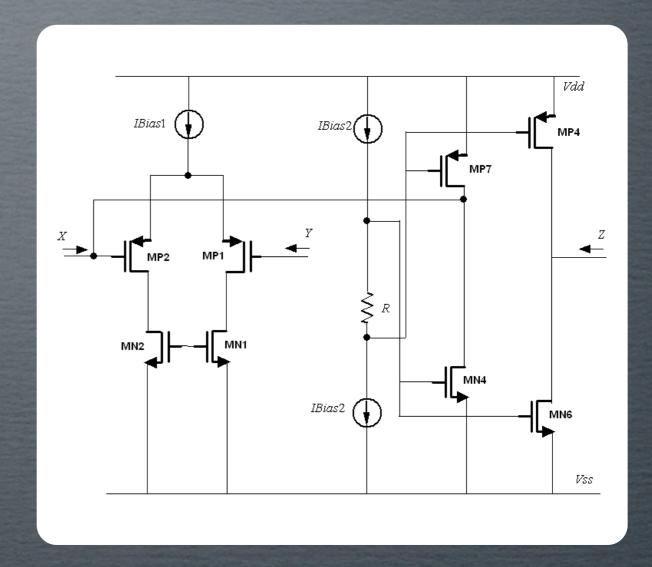

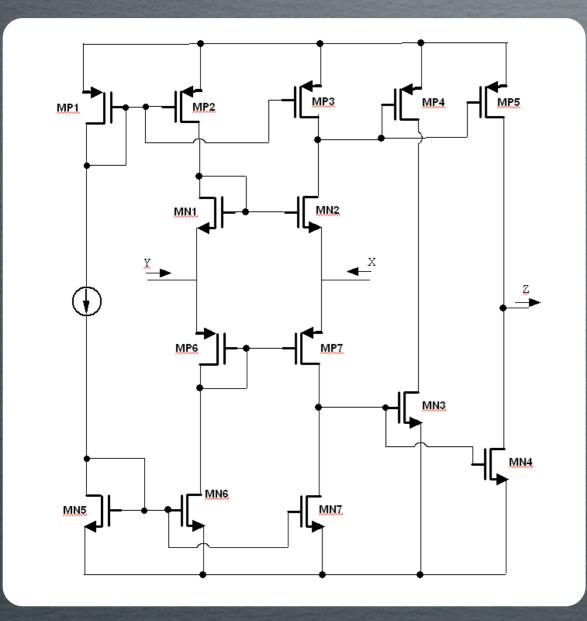

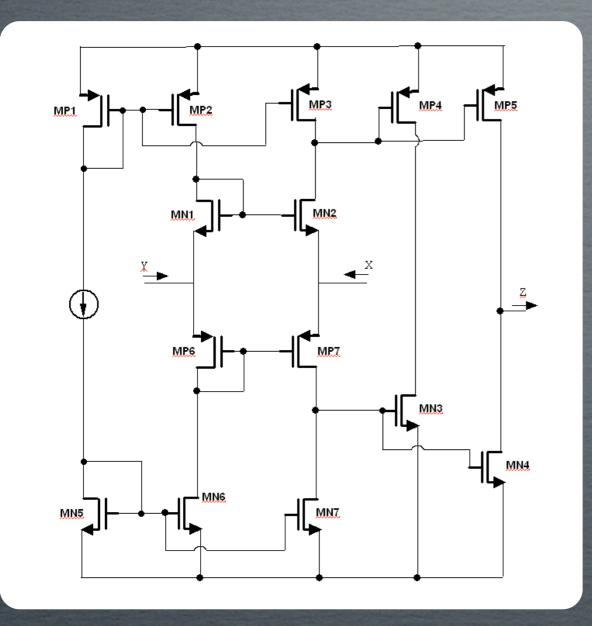

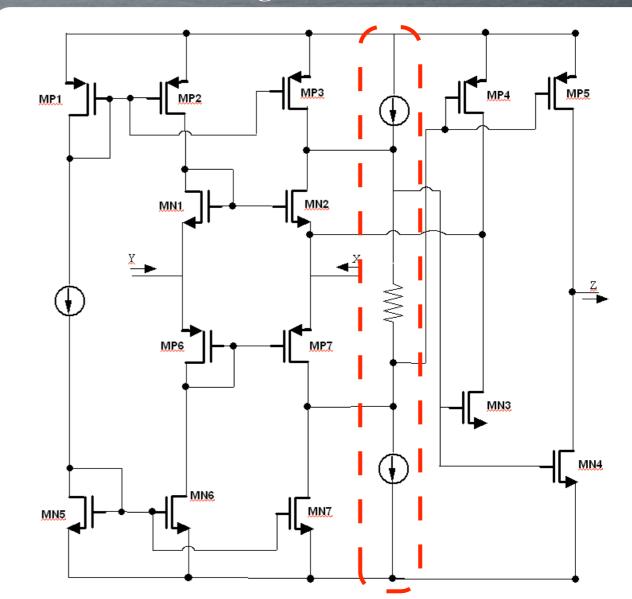

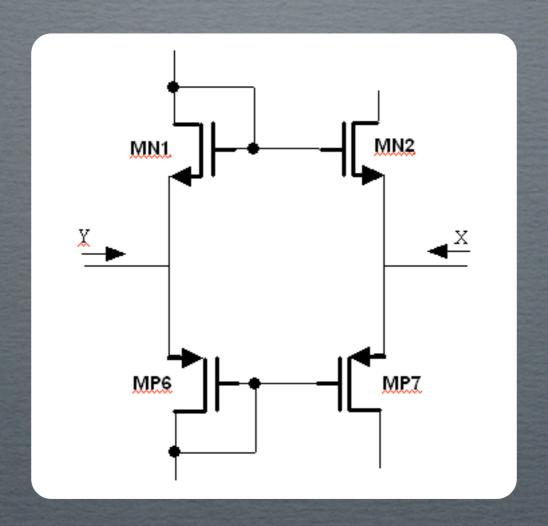

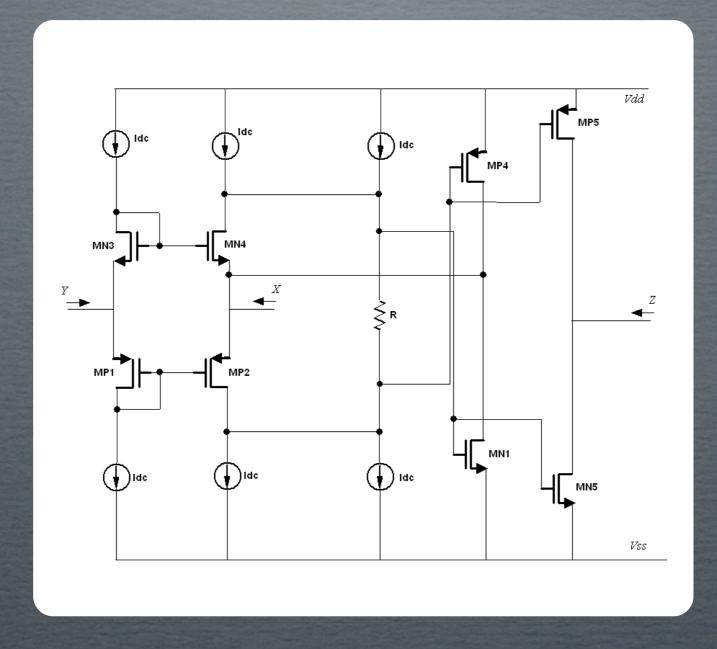

- Basada en espejos de corriente

- Basada en espejos de corriente

- Amplio ancho de banda

- Basada en espejos de corriente

- Amplio ancho de banda

- Limitaciones en máxima excursión de salida

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

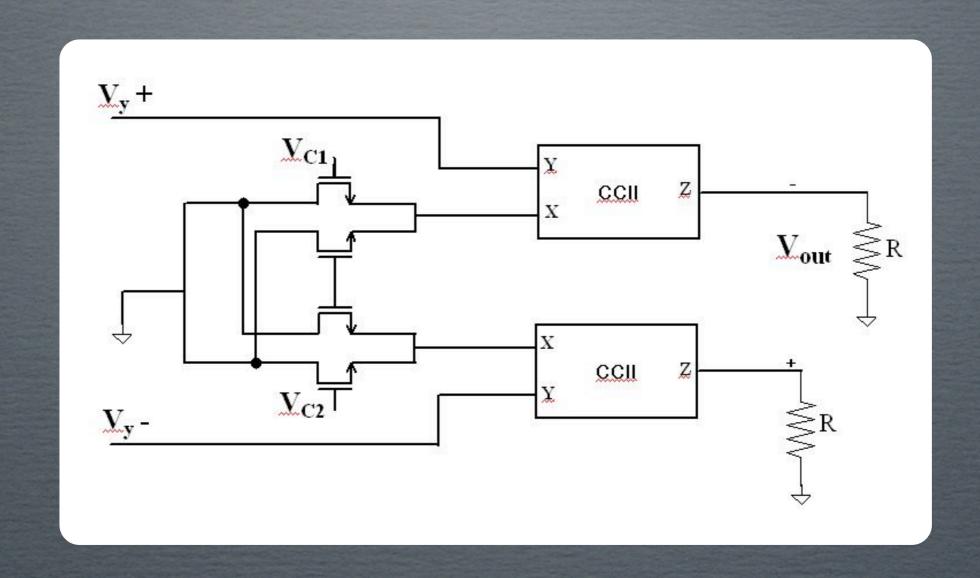

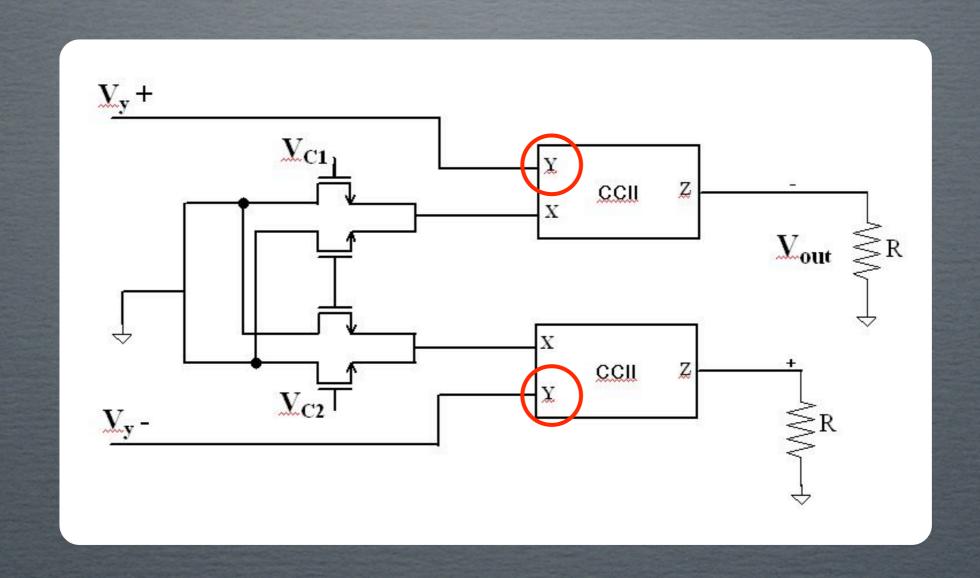

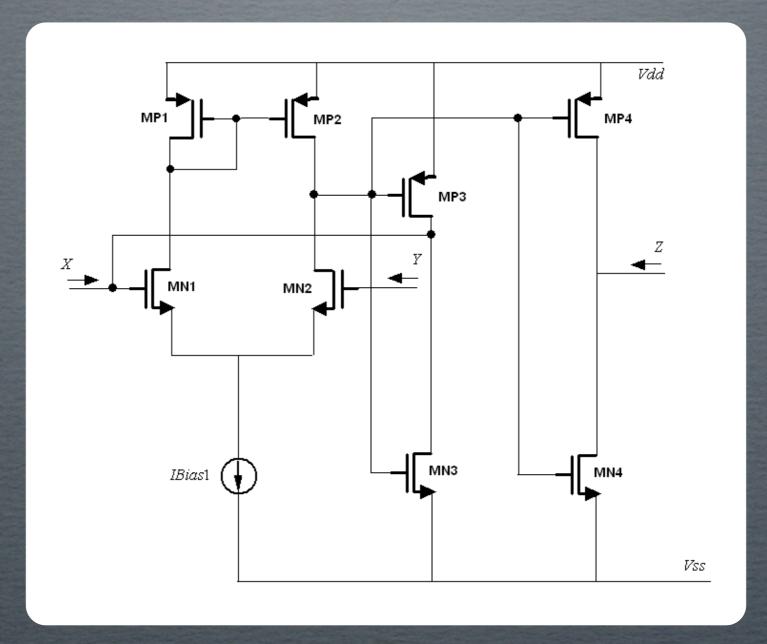

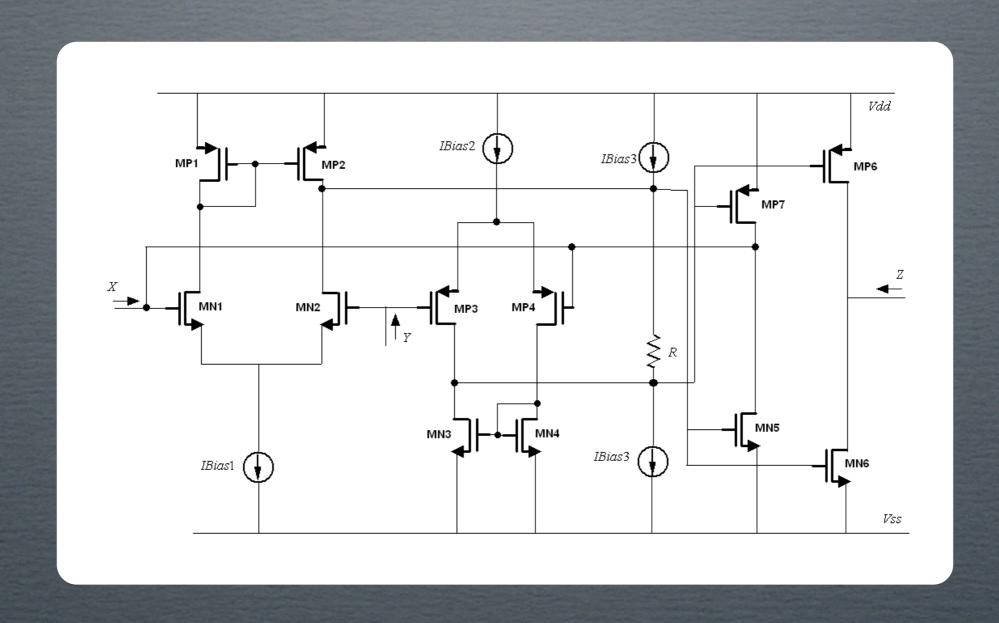

- Basada en entrada diferencial

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

- Basada en entrada diferencial

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

- Basada en entrada diferencial

- Impedancia pocos K $\Omega$

#### - Basada en entrada diferencial

#### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

#### - Basada en entrada diferencial

#### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

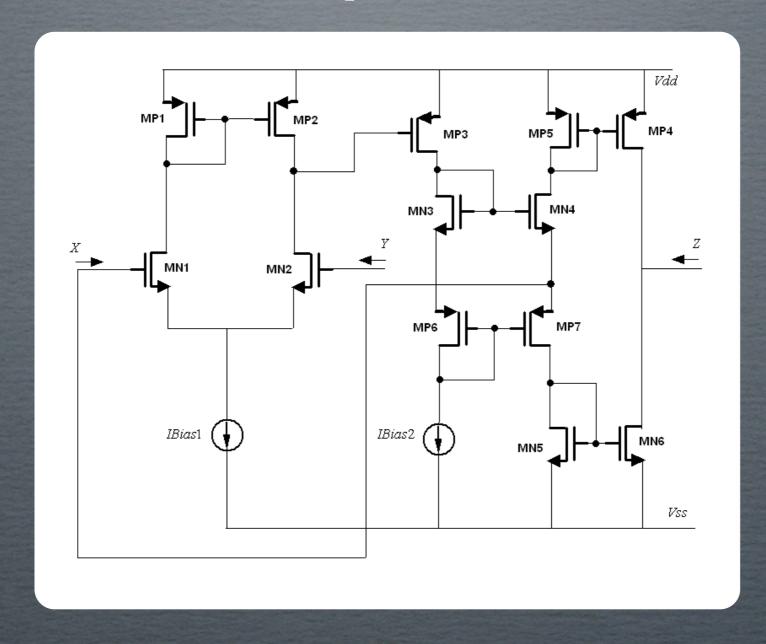

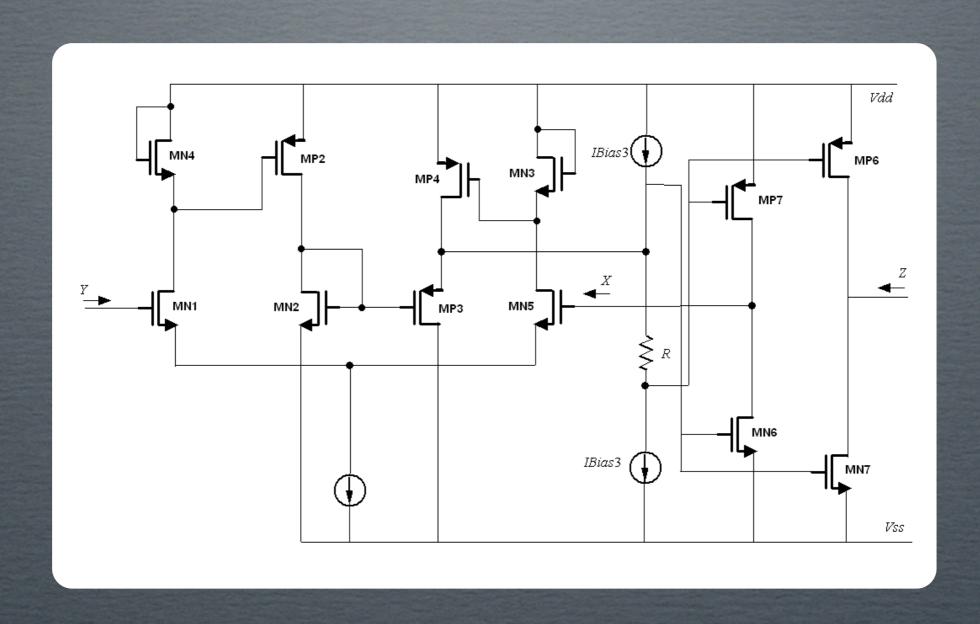

#### - Clase AB

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

- Clase AB con etapa de salida modificada

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría current conveyor

- Clase AB con solución de referencia mejorada

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

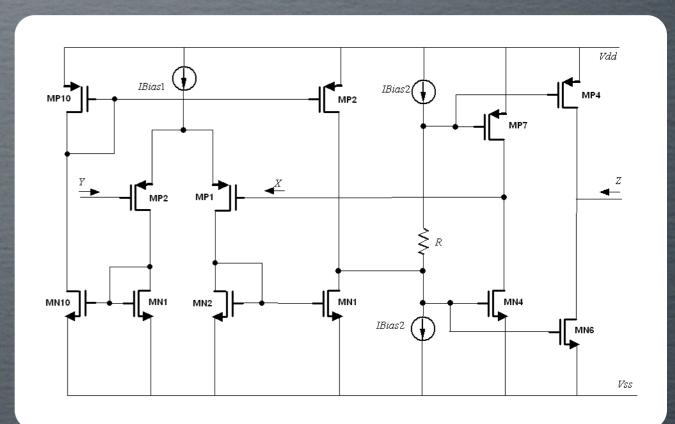

#### - Clase AB rail-to-rail

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

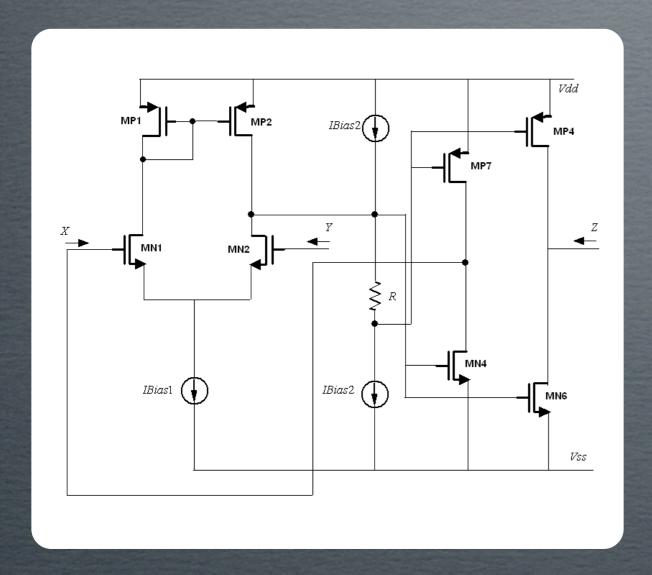

#### - Basada en OTA

Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

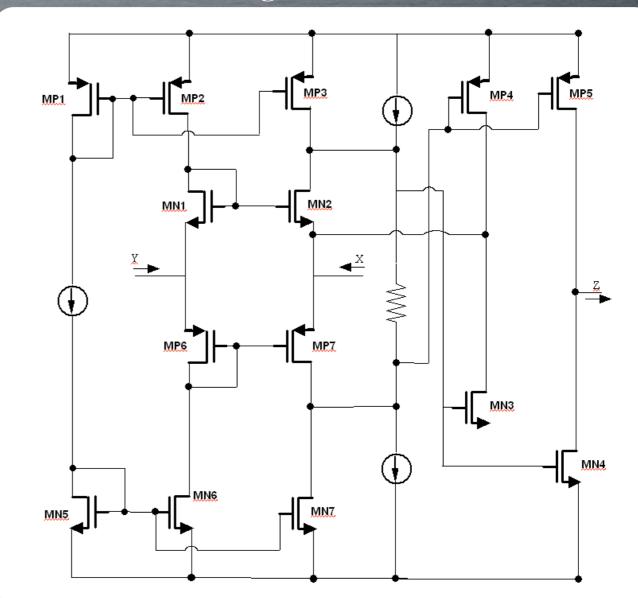

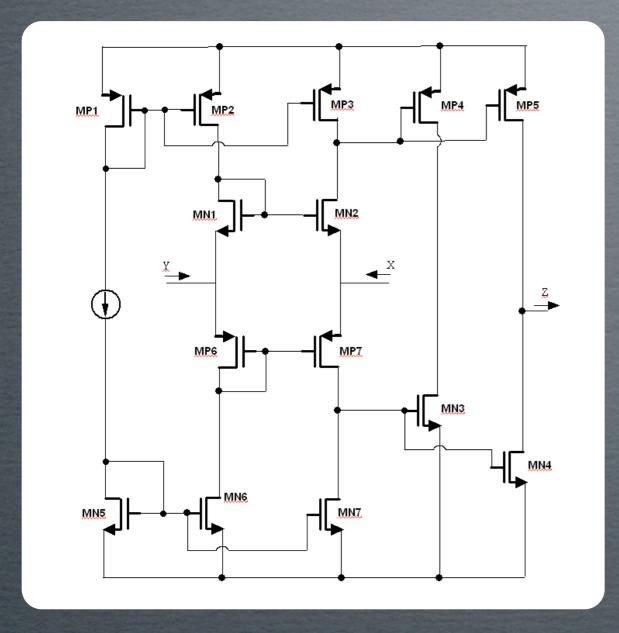

#### - OTA simétrico tipo n

#

#### - OTA simétrico tipo p

# Bloque 1 Introducción Objetivos Características RF Estándar WiMedia Teoría mezcladores Teoría current conveyor

#### - OTA simétrico rail-to-rail

# Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

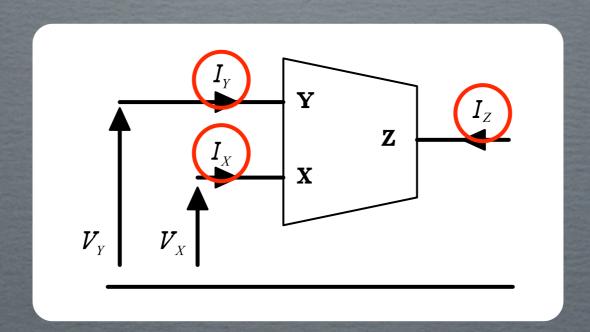

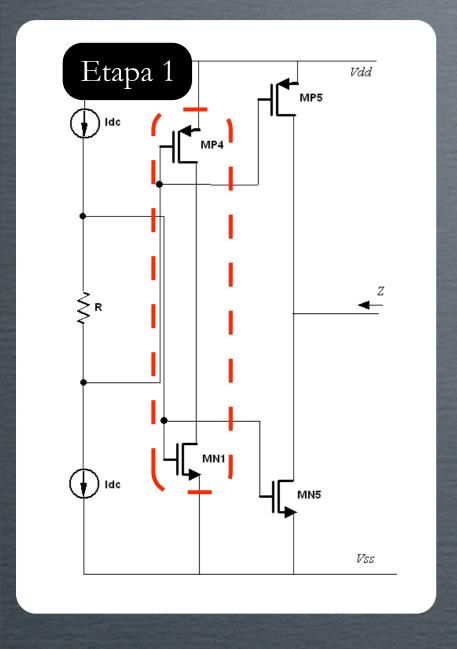

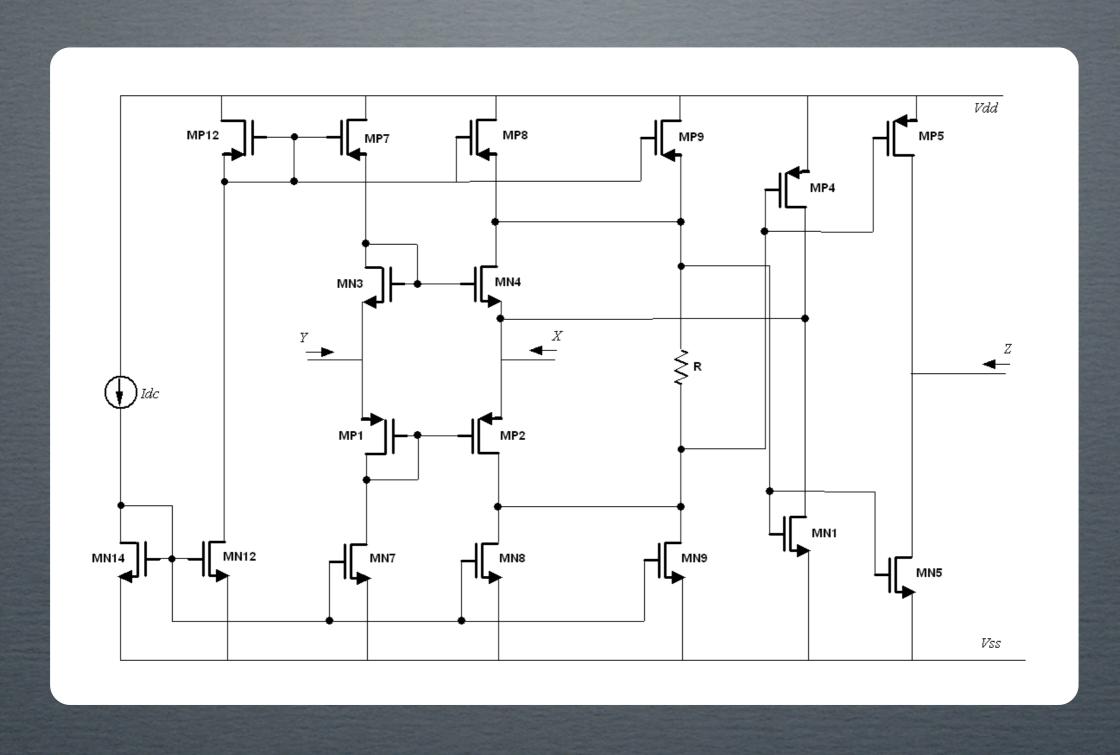

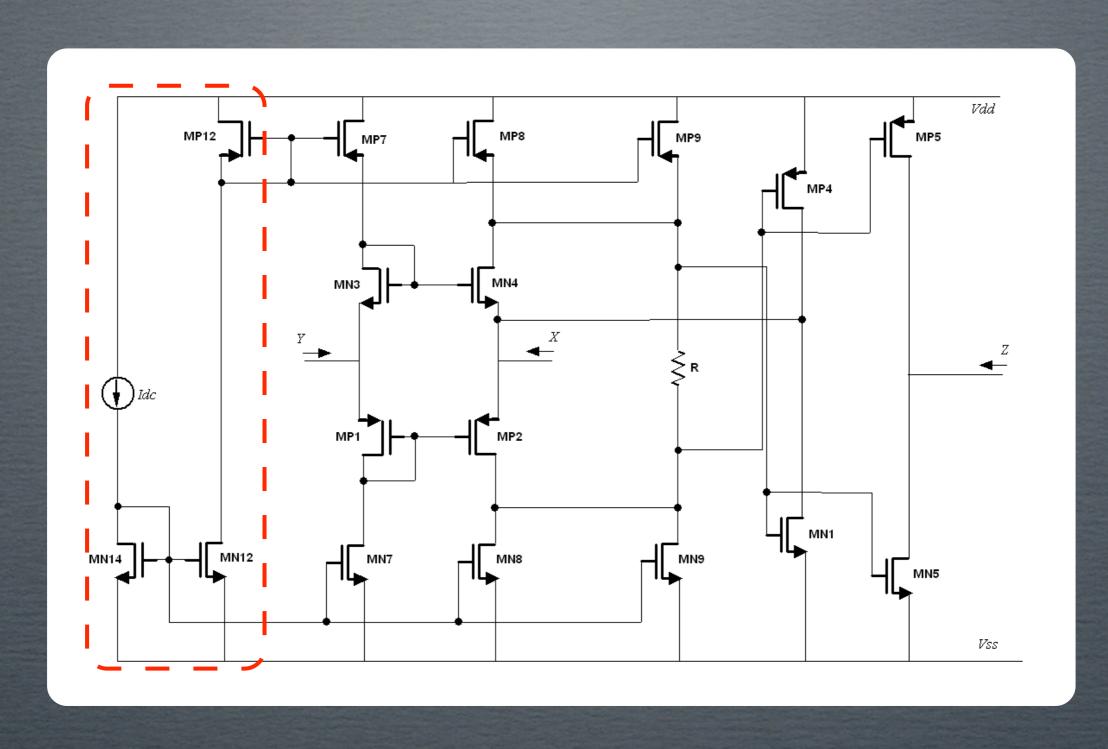

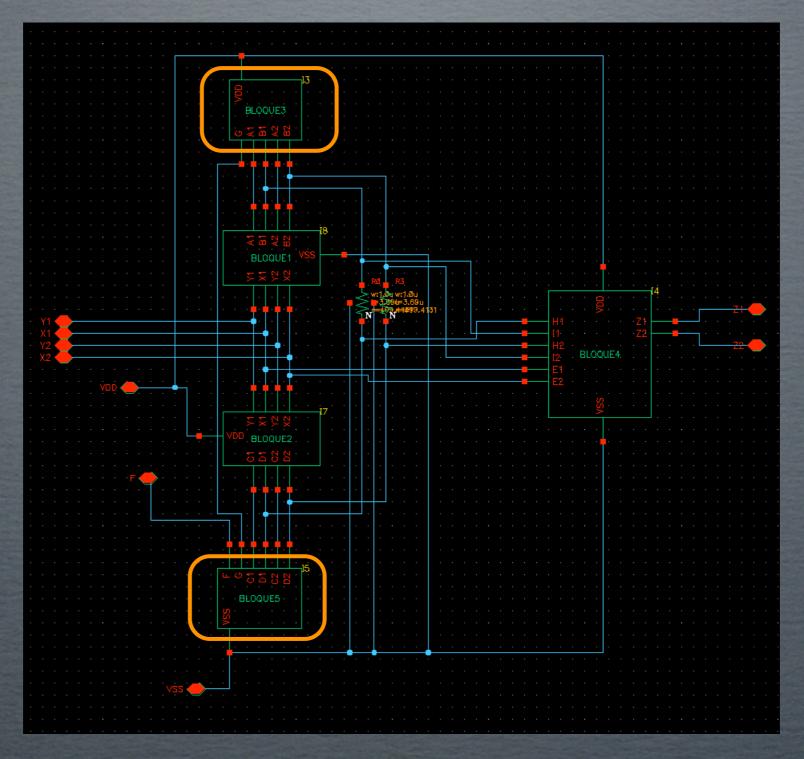

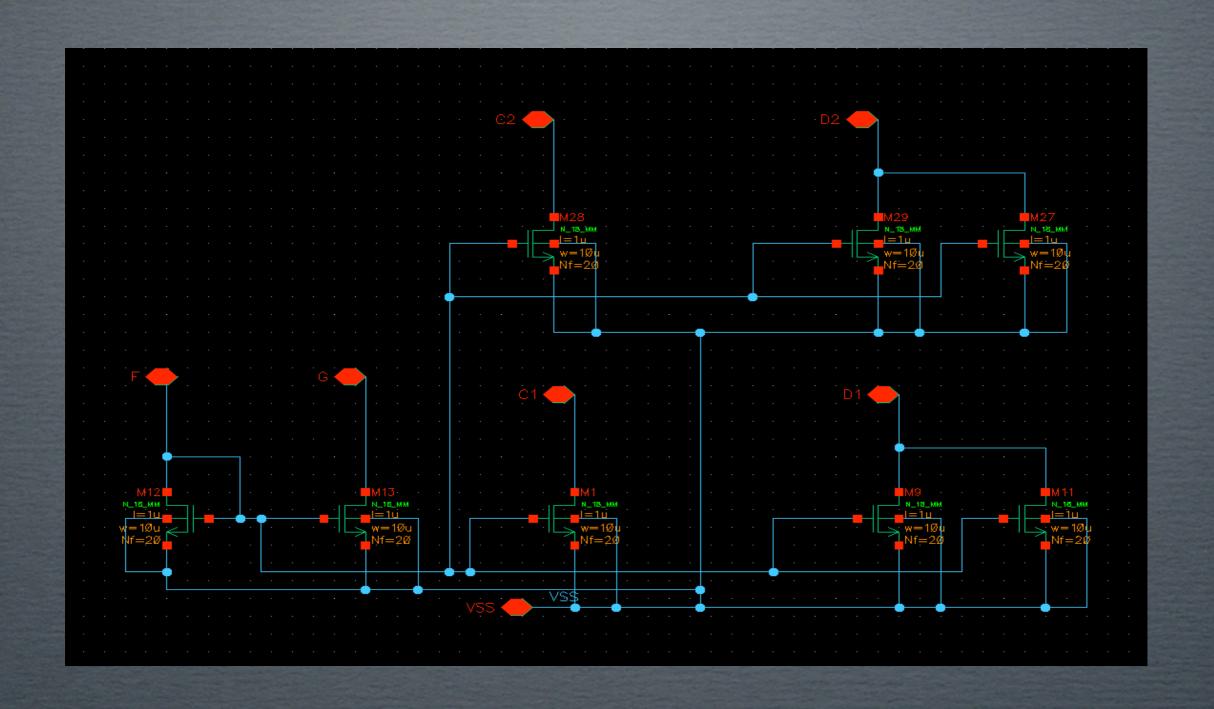

#### Diseño del current conveyor

#### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

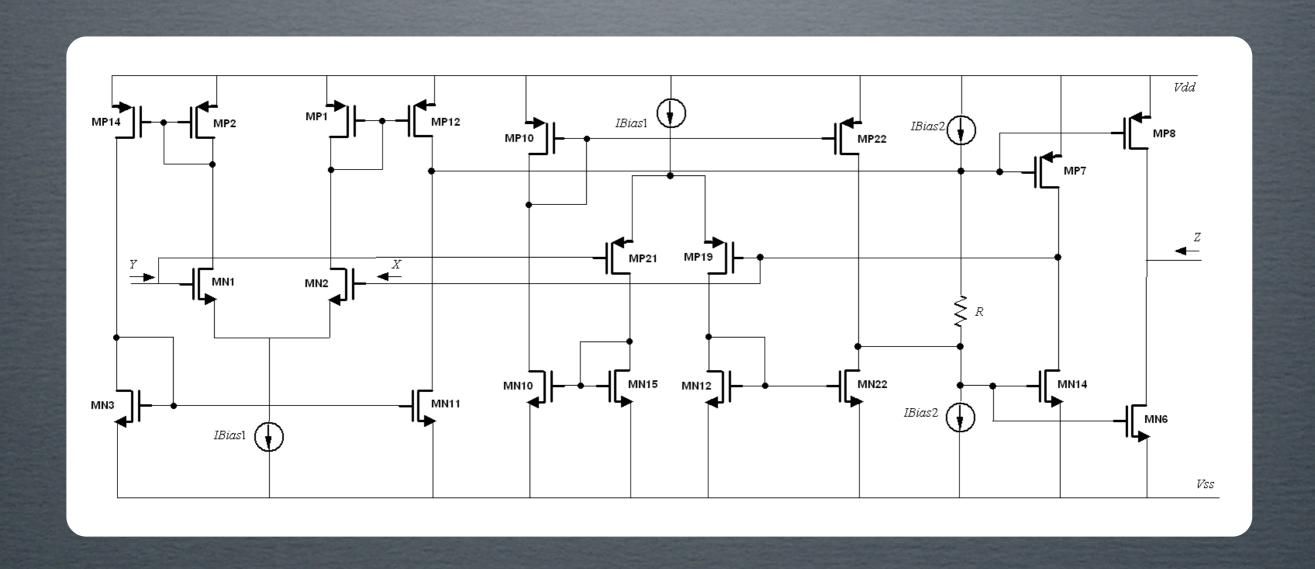

#### - Primer CCII

#### - Segundo CCII

#### Diseño del current conveyor

### Bloque 1

Introducción

Objetivos

Características RF

Estándar WiMedia

Teoría mezcladores

Teoría current conveyor

#### - Primer CCII

#### - Segundo CCII

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

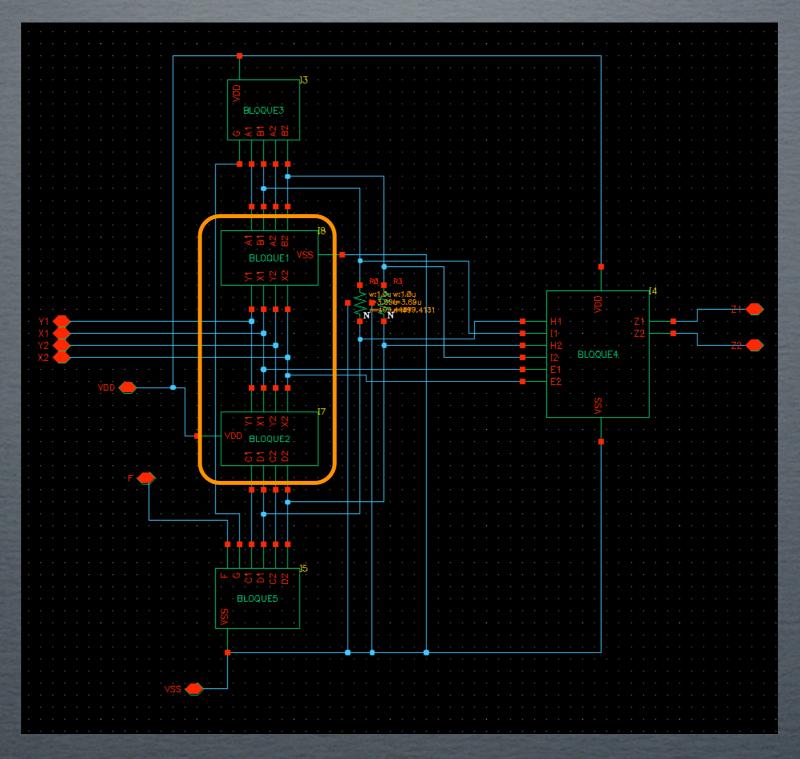

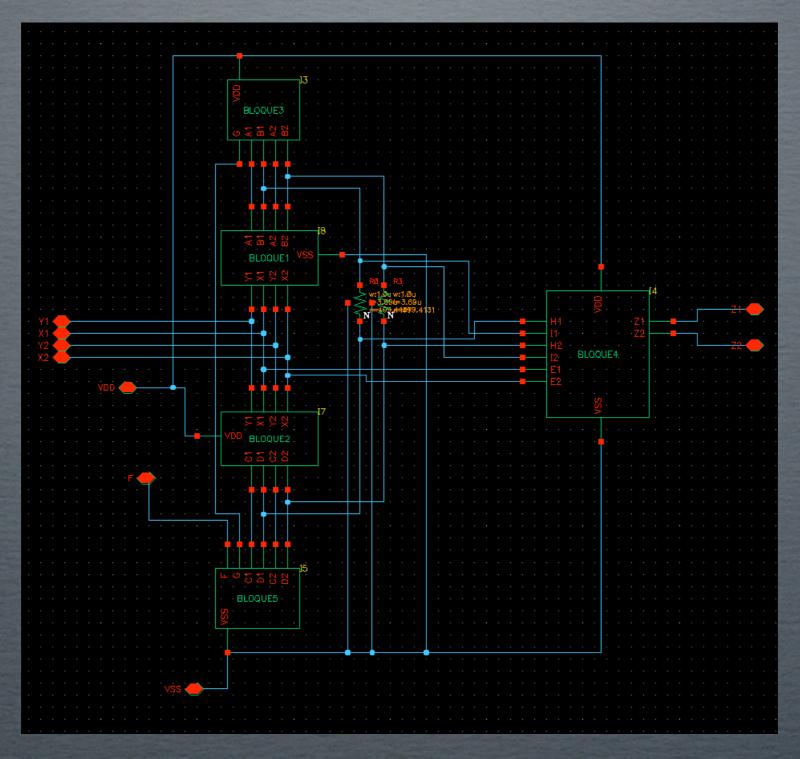

Diseño a nivel esquemático Diseño a nivel layout

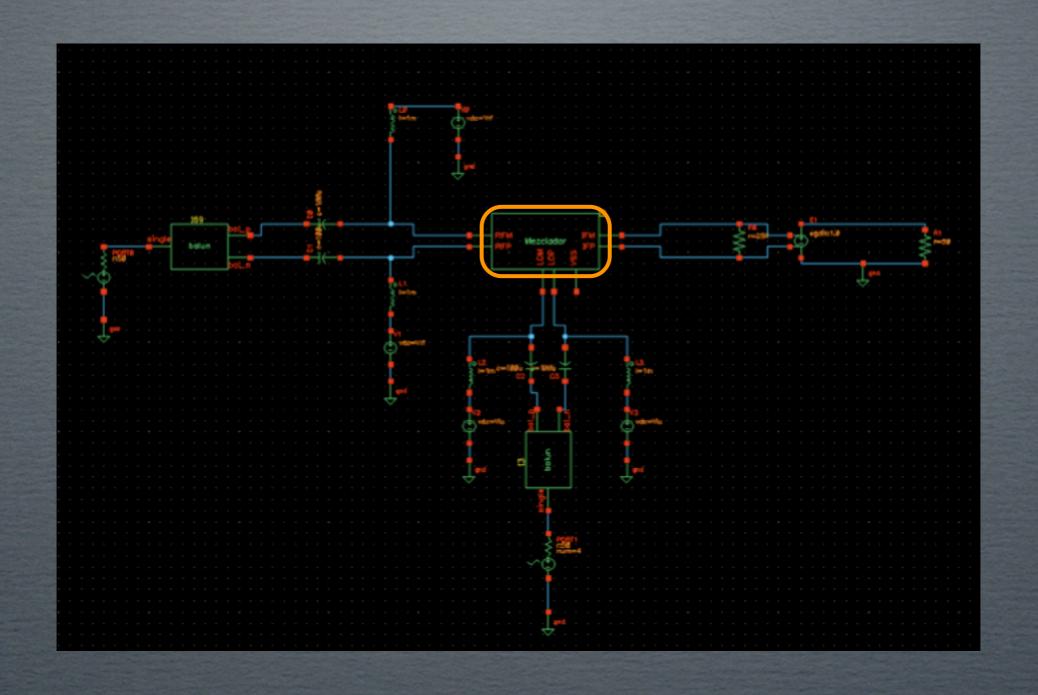

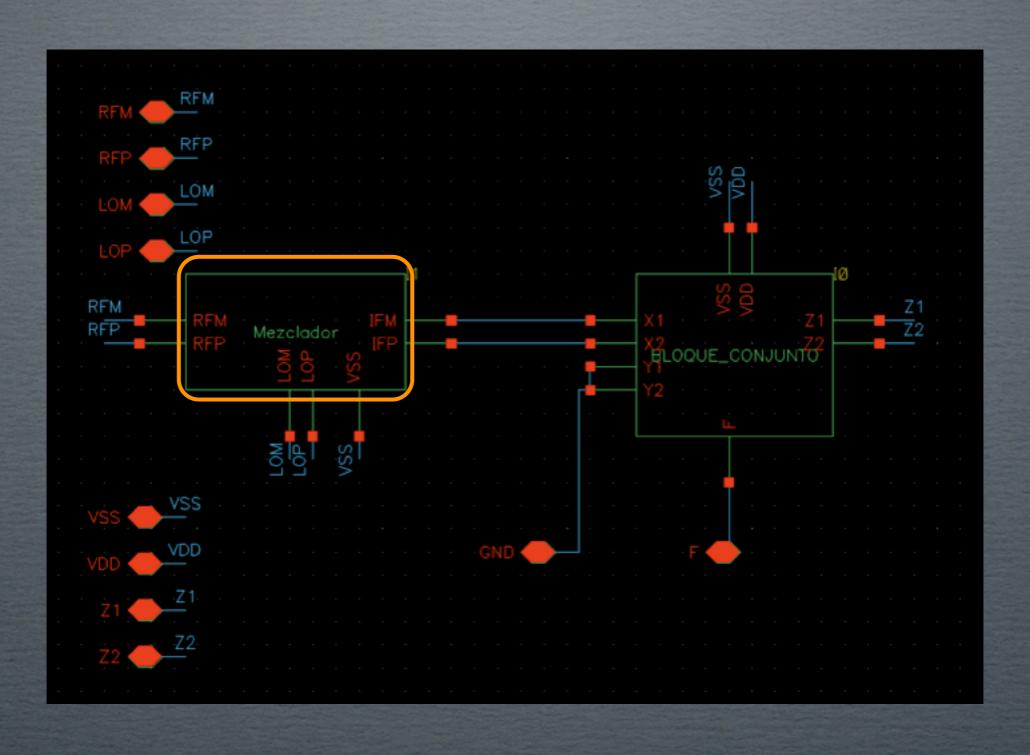

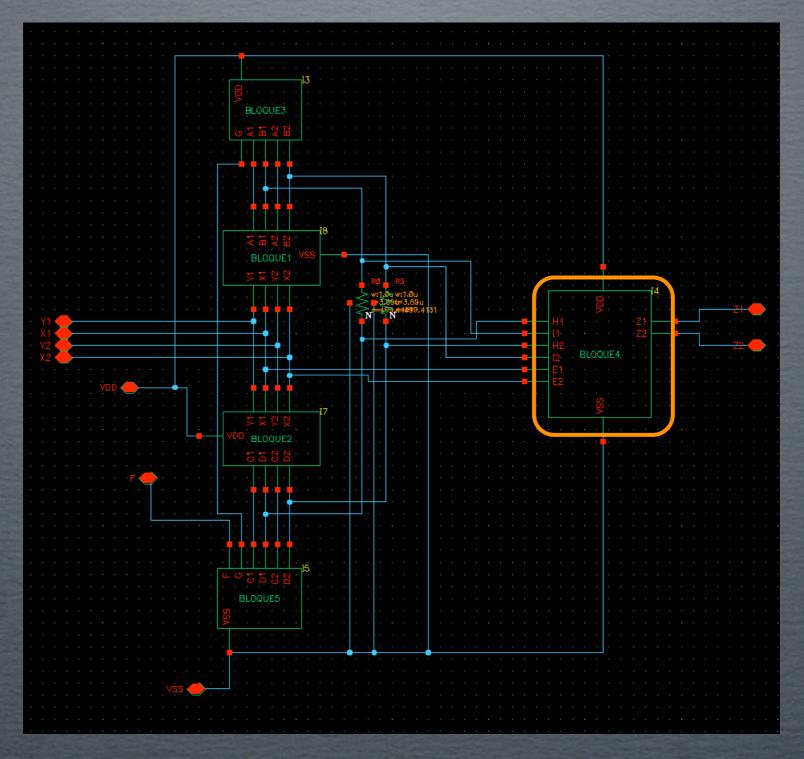

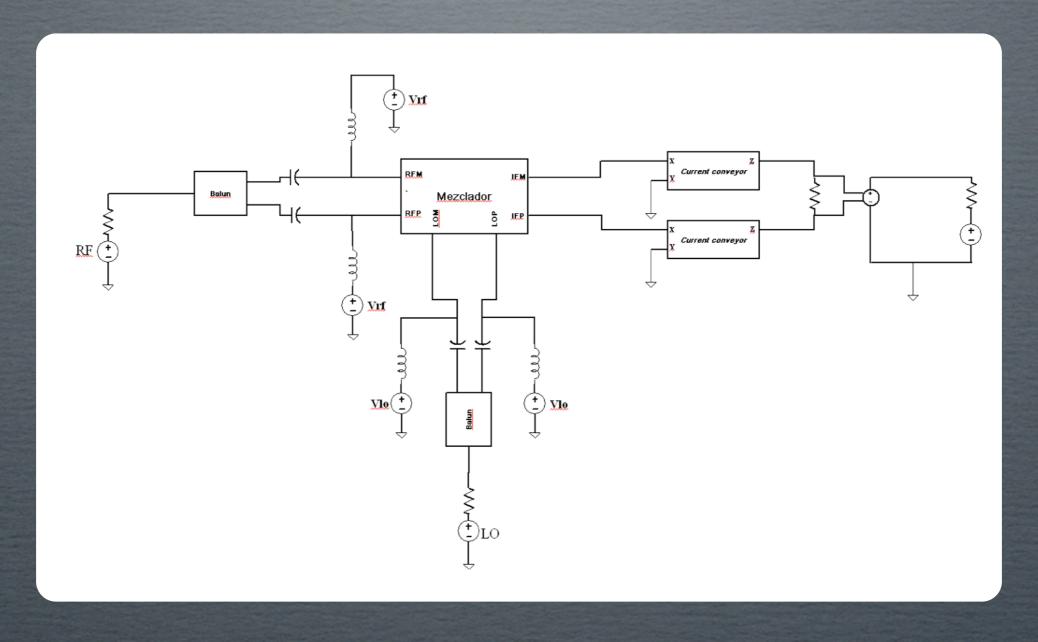

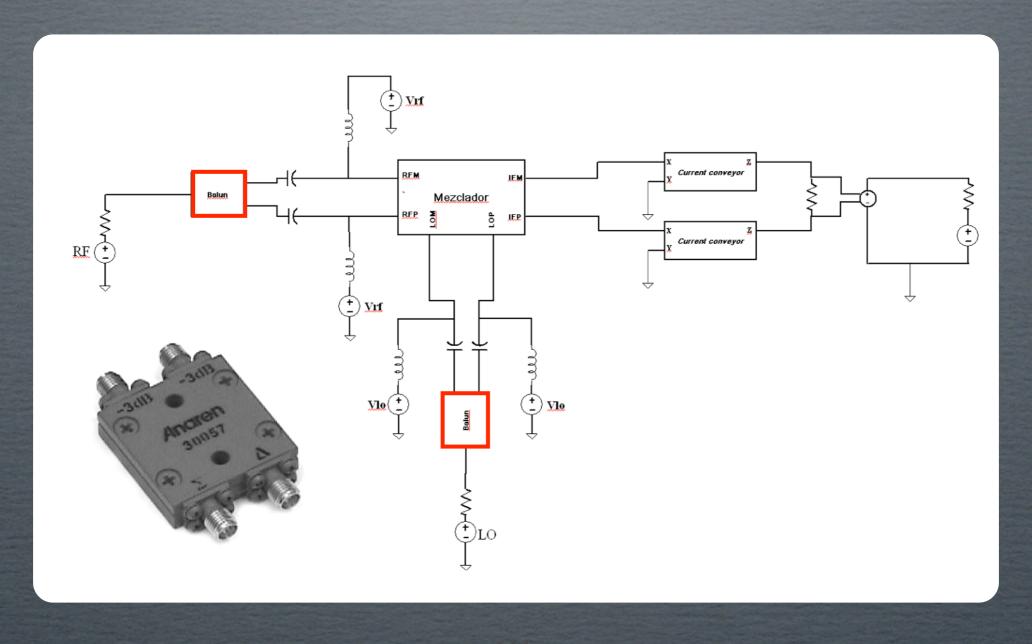

# Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

# Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel layout

Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

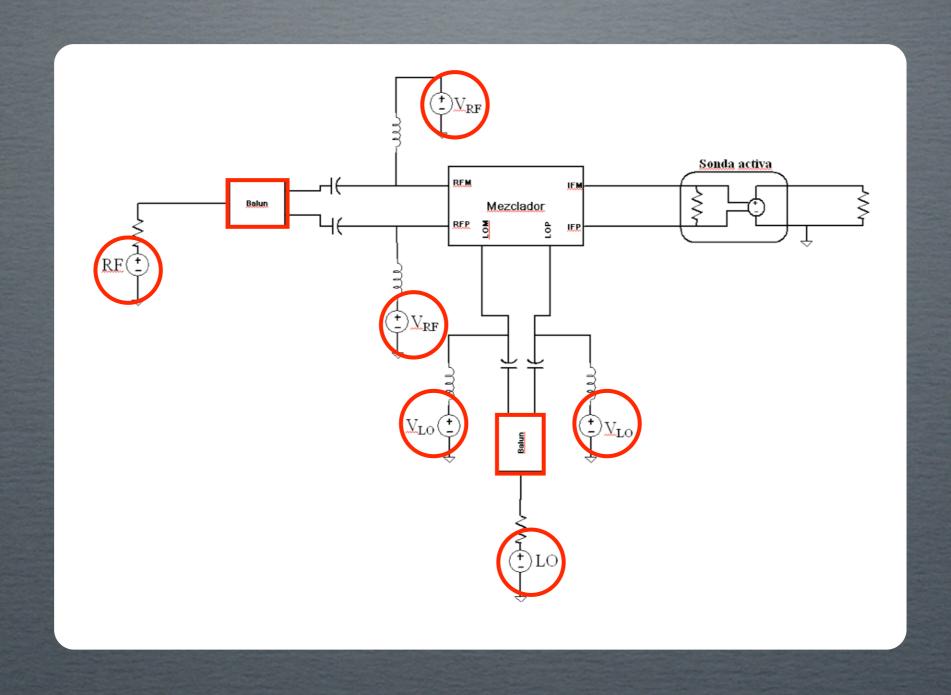

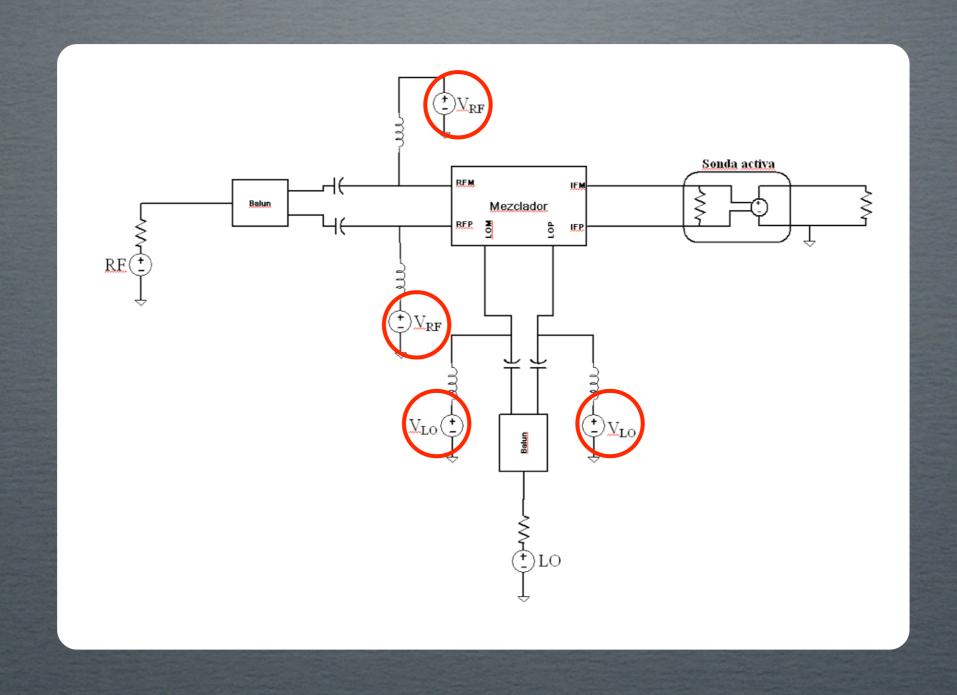

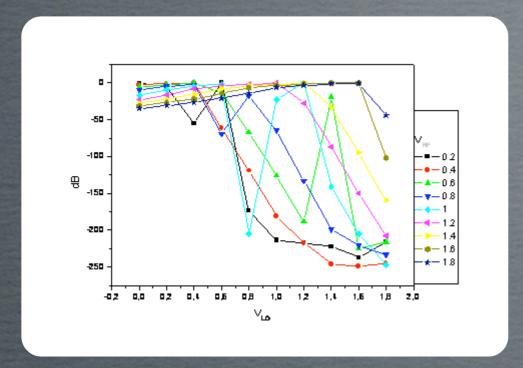

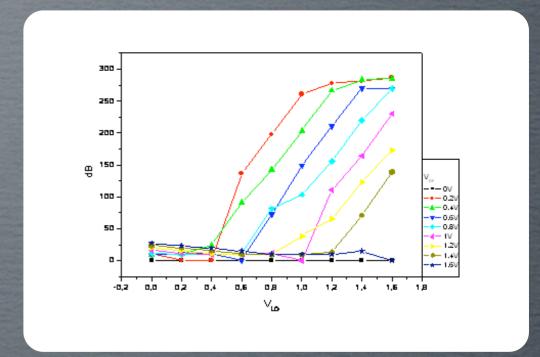

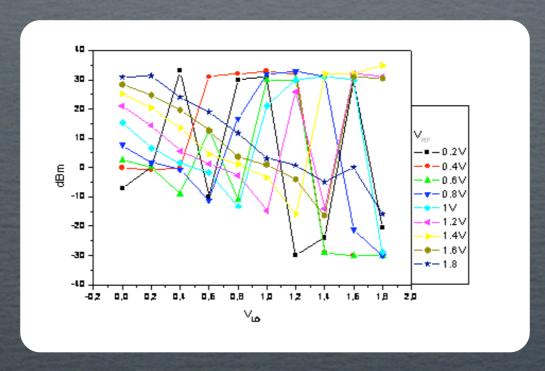

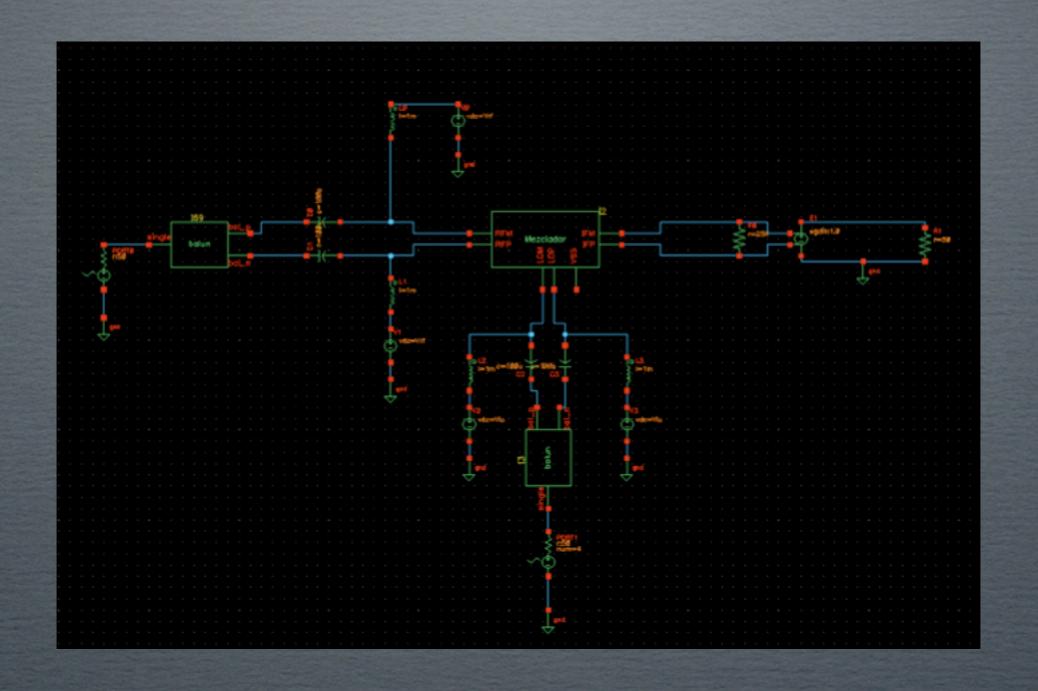

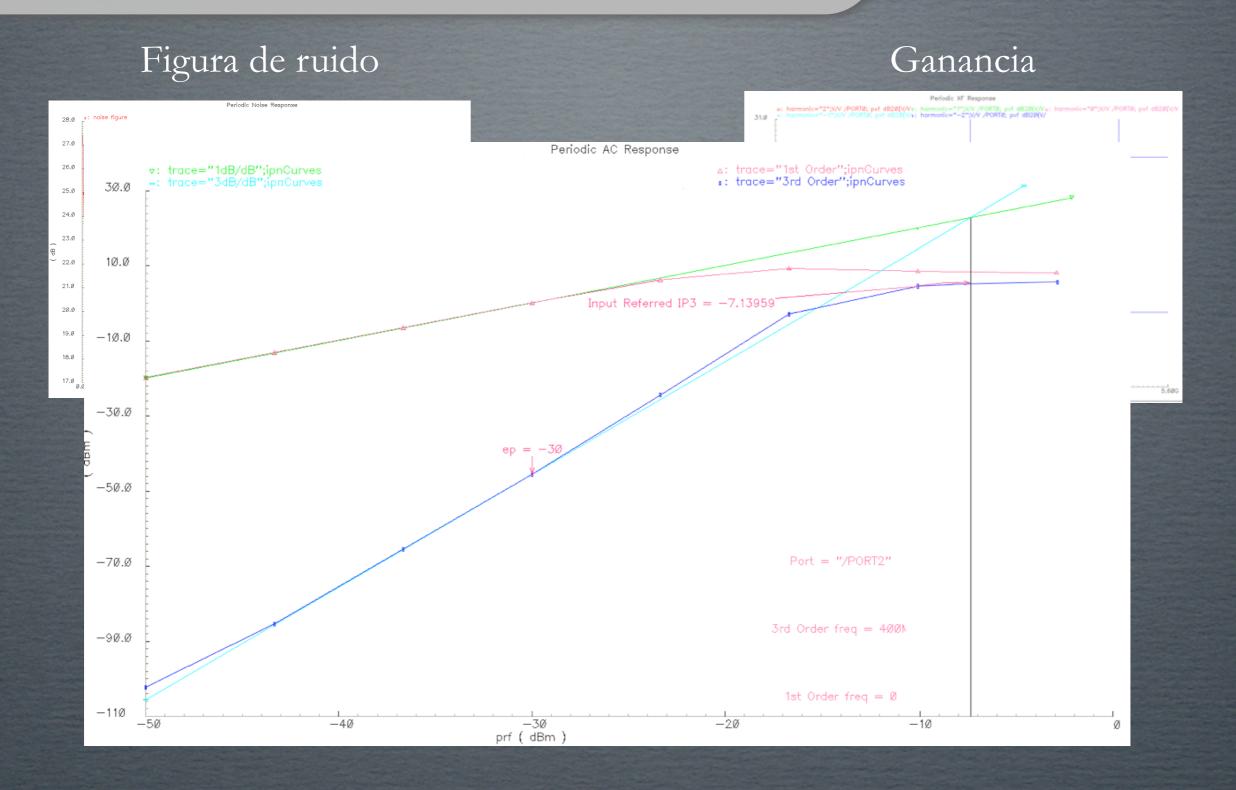

#### Diseño del mezclador

- Ganancia

- Figura de ruido

- IIP3

Diseño a nivel esquemático Diseño a nivel layout

| $V_{LO}(V)/V_{RF}(V)$ | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|-----------------------|---------------|------------|------------|

| 0;0,4                 | -2,8          | 8,9        | -0,15      |

| 0,6;1,6               | -14,7         | 14,42      | 12,66      |

#### Bloque 2 Diseño a nivel esquemátic

#### Diseño a nivel esquemático Diseño a nivel layout

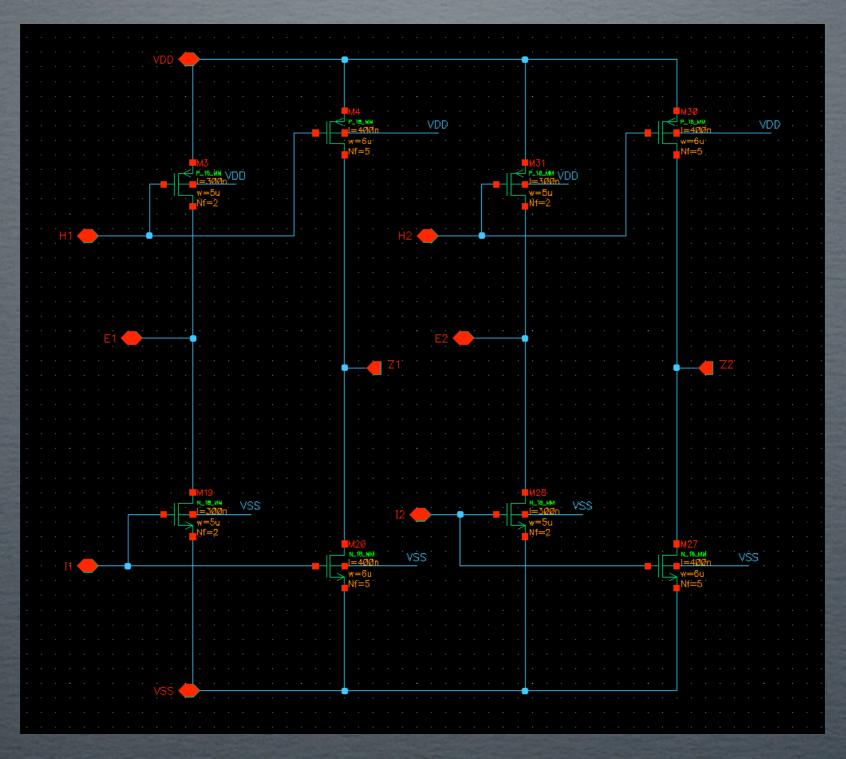

### Diseño del current conveyor

#### - Primer CCII

#### - Segundo CCII

#### Bloque 2 Diseño a nivel esquemátic

#### Diseño a nivel esquemático Diseño a nivel layout

### Diseño del current conveyor

#### - Primer CCII

#### - Segundo CCII

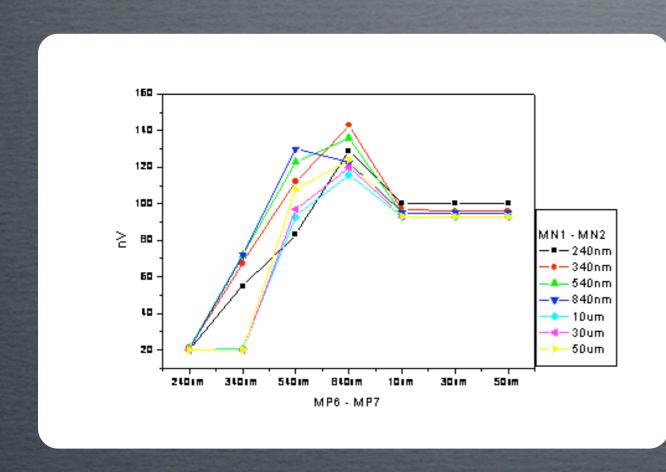

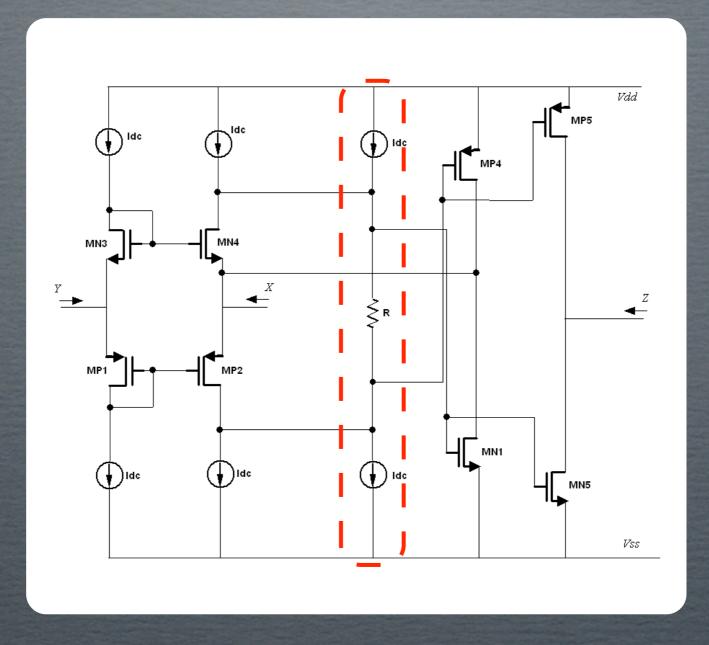

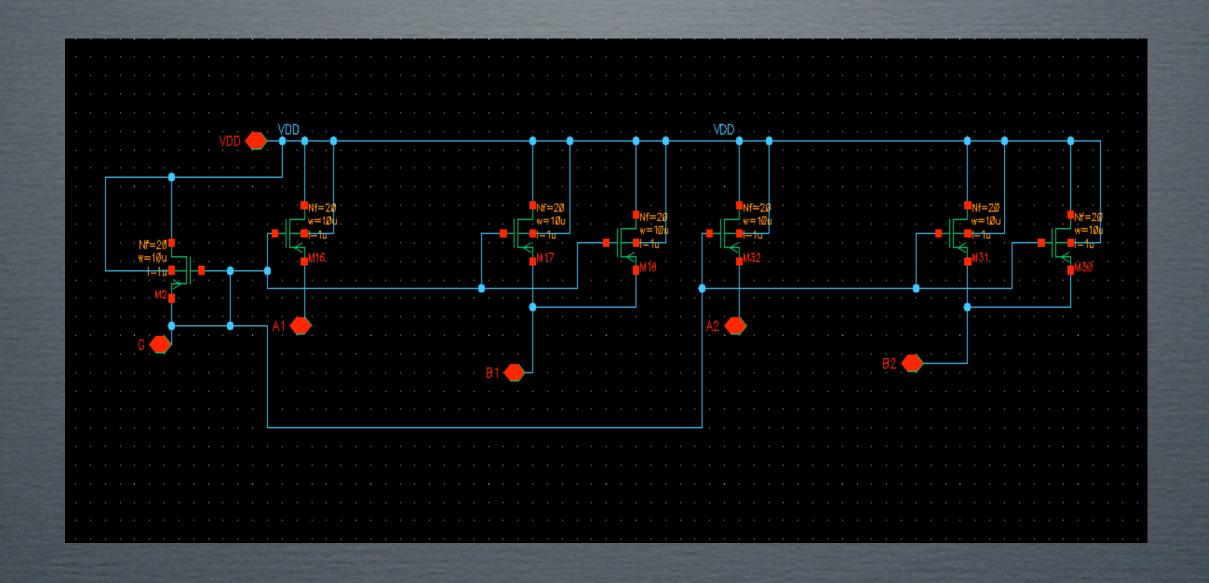

# Optimización del núcleo del current conveyor

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

# Optimización del núcleo del current conveyor

# Optimización del núcleo del current conveyor

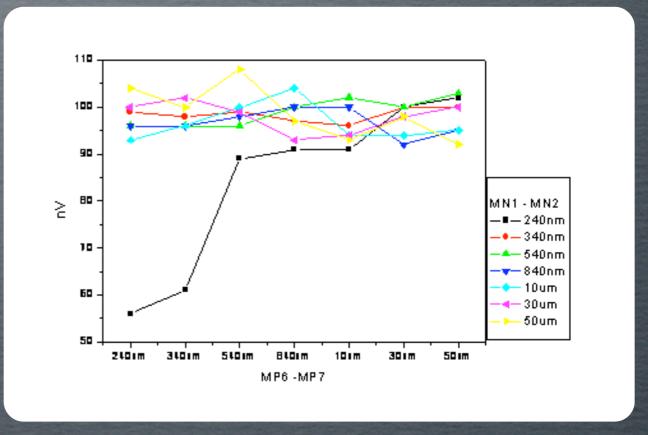

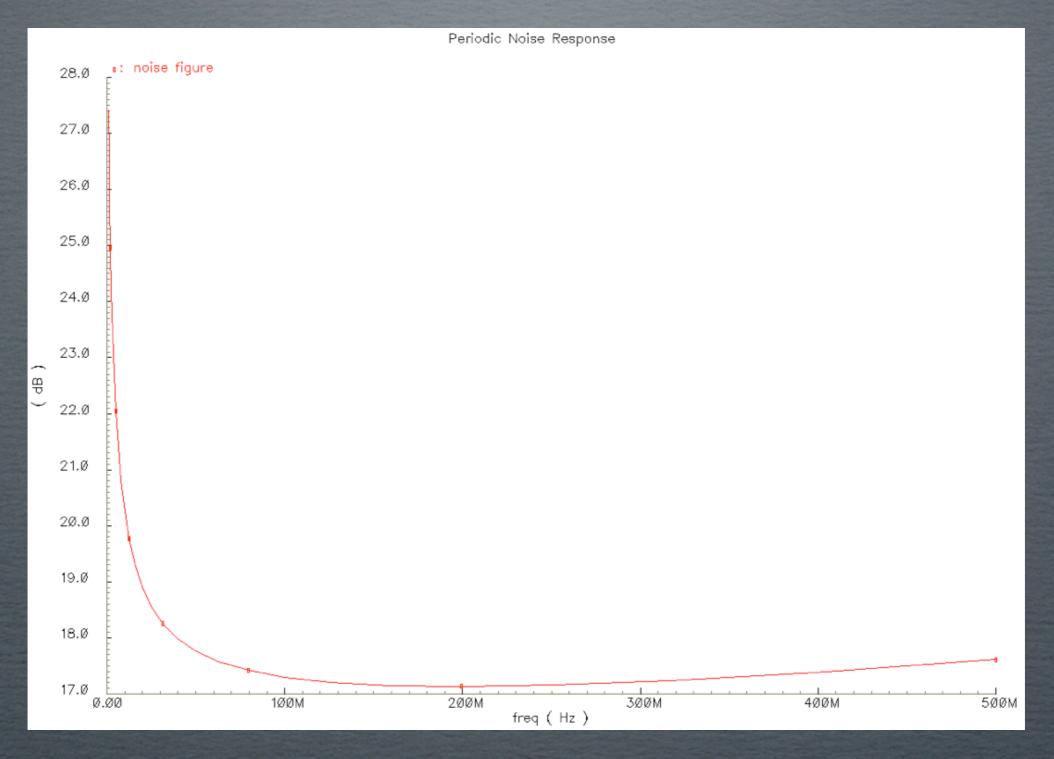

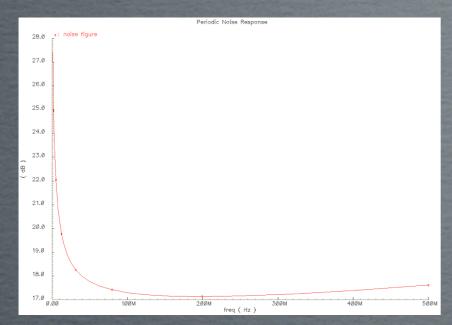

#### Valores para output noise figure

Primer CCII

Segundo CCII

Diseño a nivel esquemático Diseño a nivel lavout

# Optimización del núcleo del current conveyor

comentar que aquí se llegó a la conclusión de 240 arriba y 340 abajo

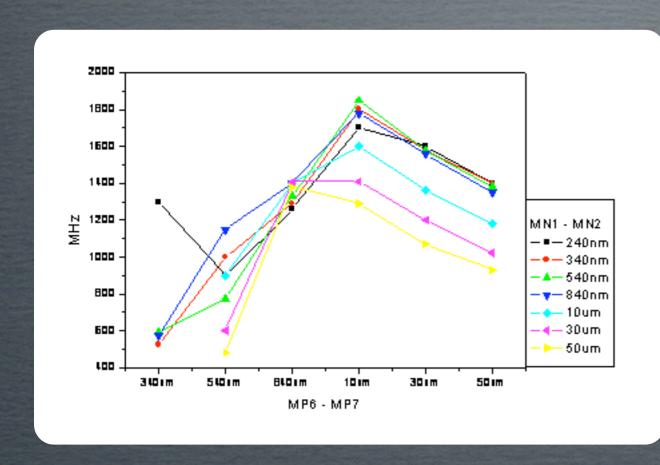

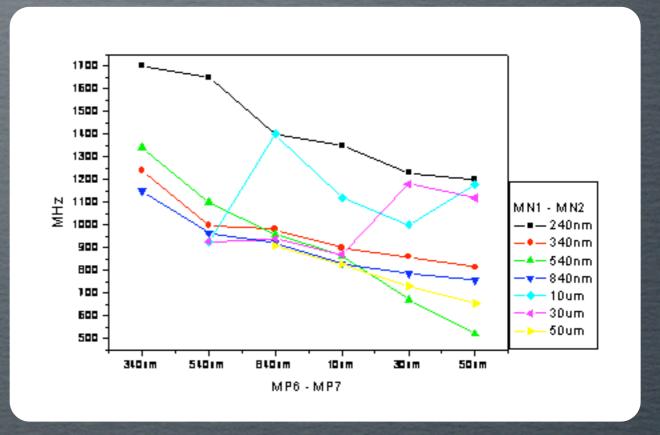

#### Valores de ancho de banda

Primer CCII

Segundo CCII

# Optimización del núcleo del current conveyor

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

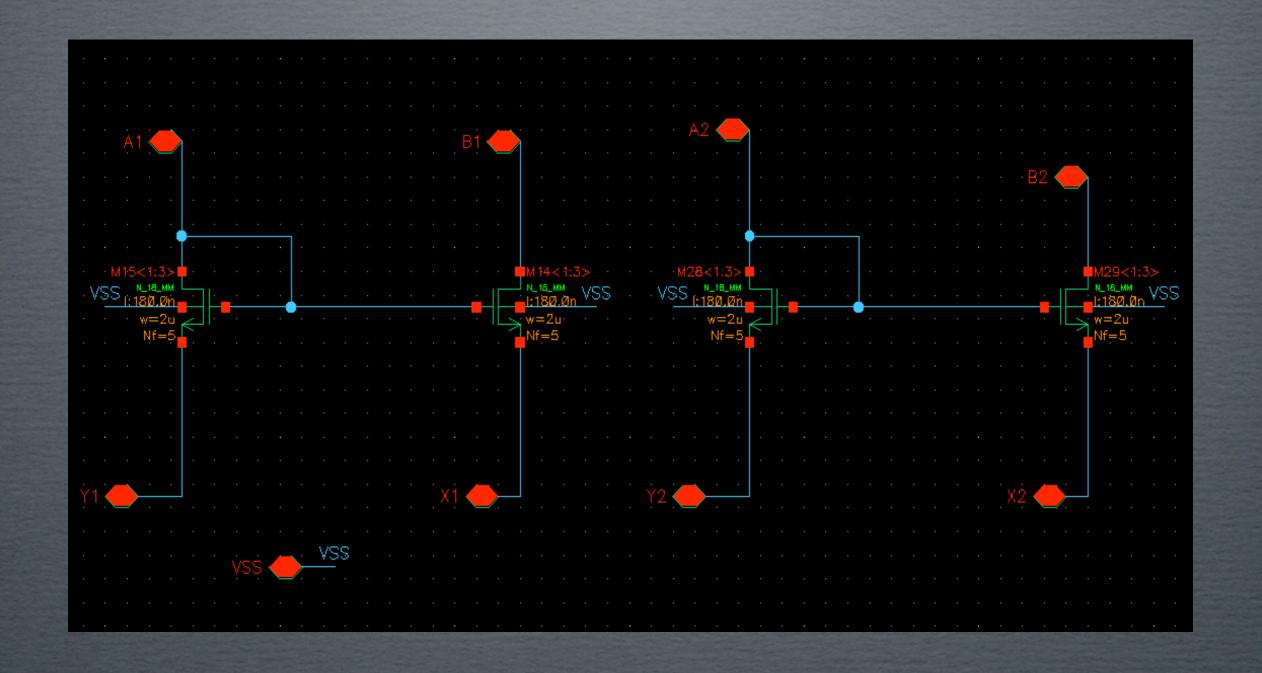

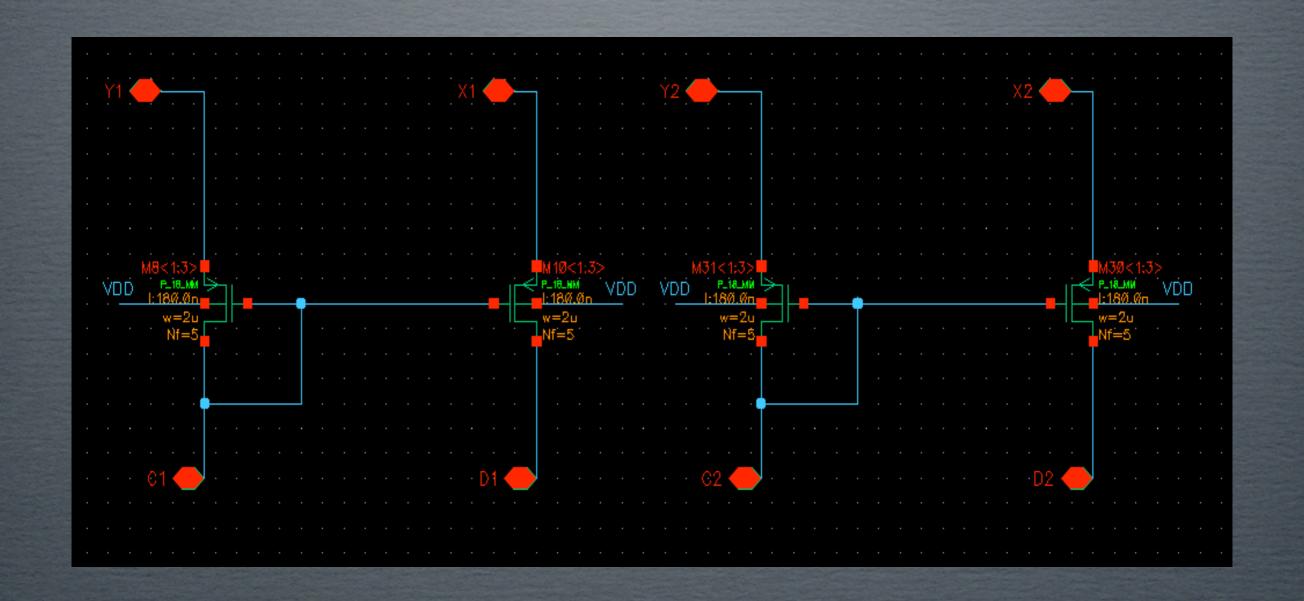

Transistores N

Transistores P

240 nm

340 nm

Diseño a nivel esquemático Diseño a nivel layout

# Optimización del núcleo del current conveyor

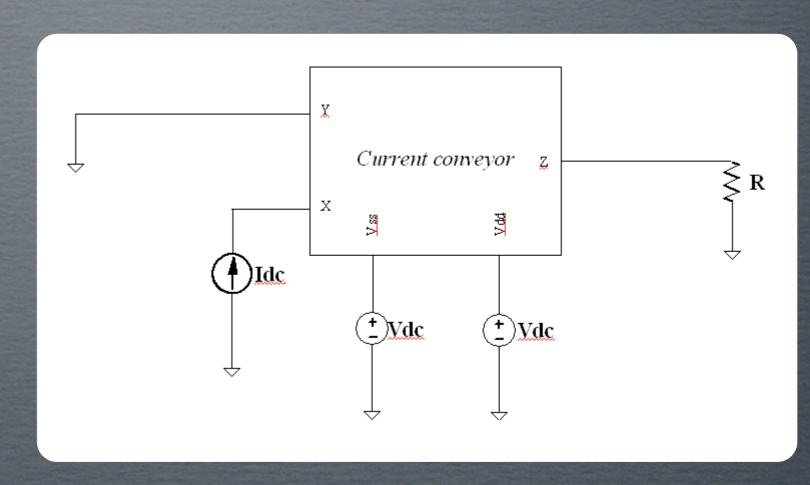

#### Modelo de simulación

Diseño a nivel esquemático Diseño a nivel layout

## Optimización del núcleo del current conveyor

#### Modelo de simulación

Diseño a nivel esquemático Diseño a nivel layout

## Optimización del núcleo del current conveyor

#### Modelo de simulación

Diseño a nivel esquemático Diseño a nivel layout

## Optimización del núcleo del current conveyor

#### Modelo de simulación

## Bloque 2 Diseño a nivel esquemático

## Optimización del núcleo del current conveyor

|                      | Primer CCII | Segundo CCII |  |  |

|----------------------|-------------|--------------|--|--|

| Figura de ruido (dB) | 35,3        | 31,7         |  |  |

| Ganancia (dB)        | 9,14        | 12           |  |  |

| IIP3 (dBm)           | 1,52 -2,4   |              |  |  |

| Consumo (mA)         | > 30        |              |  |  |

## Bloque 2 Diseño a nivel esquemático

## Optimización del núcleo del current conveyor

| Dimensionado t | ransistores | Figura de ruido (dB) |              |  |

|----------------|-------------|----------------------|--------------|--|

| Tipo N         | Tipo P      | Primer CCII          | Segundo CCII |  |

| 340 nm         | 340 nm      | 36                   | 31           |  |

| 540 nm         | 340 nm      | 32                   | 29           |  |

| 10 μm          | 540 nm      | 33                   | 29           |  |

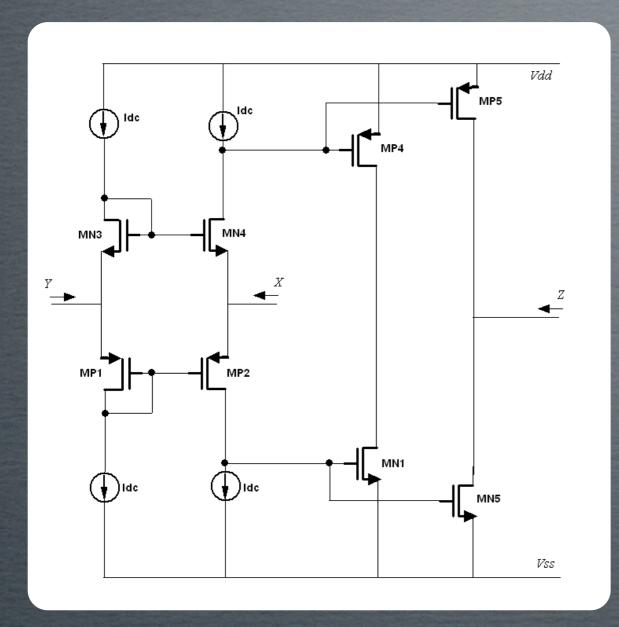

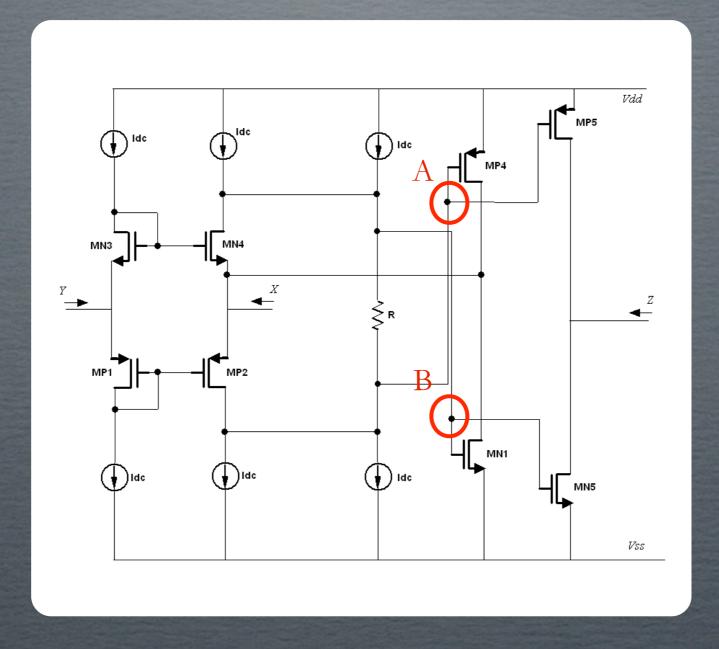

## Optimización de la etapa de salida (Objetivos)

Bloque 2

Diseño a nivel lavout

Bajo consumo

## Optimización de la etapa de salida (Objetivos)

## Bloque 2 Diseño a nivel esquemático

Bajo consumo

Diseño a nivel esquemático Diseño a nivel layout

## Optimización de la etapa de salida (Objetivos)

Bajo consumo

Figura de ruido

Ganancia

Linealidad

## Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

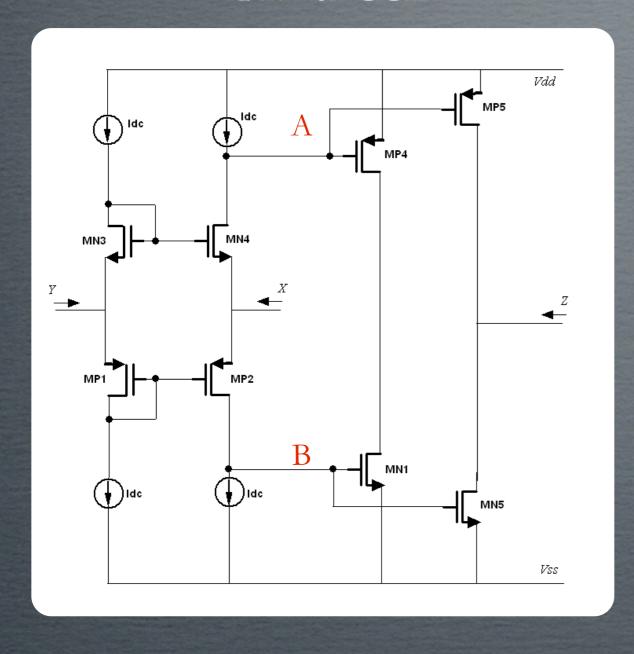

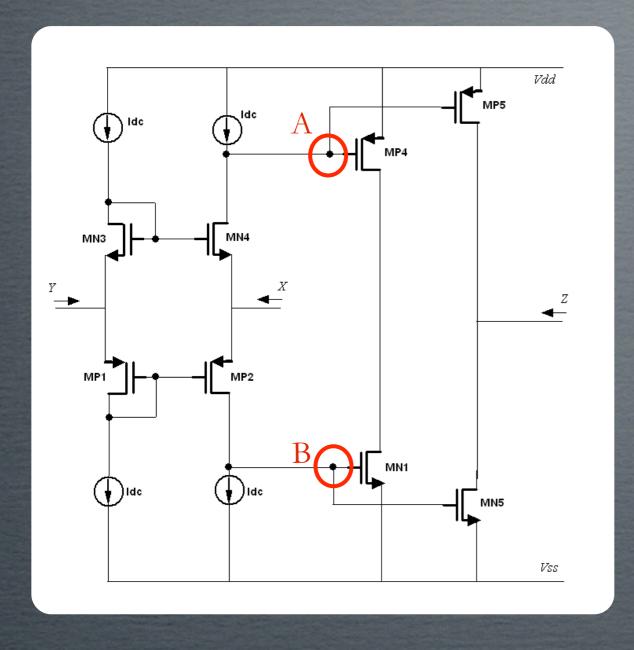

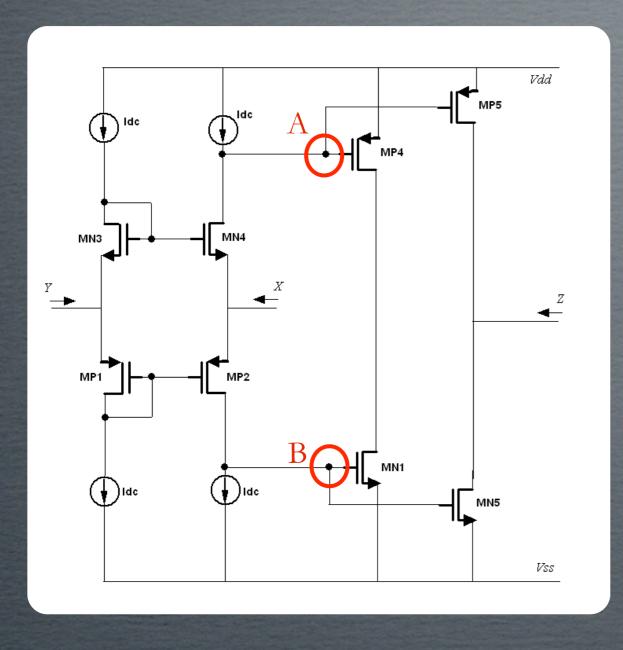

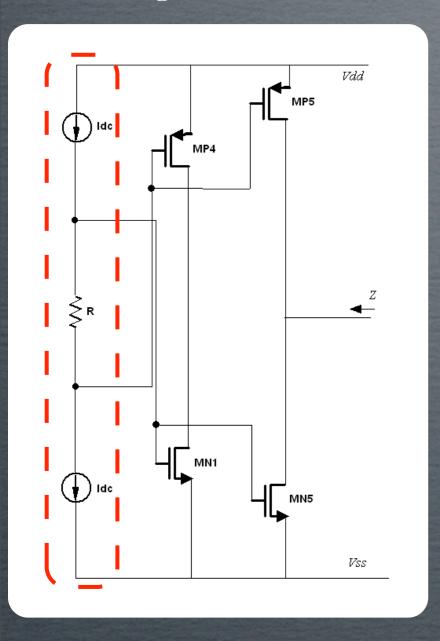

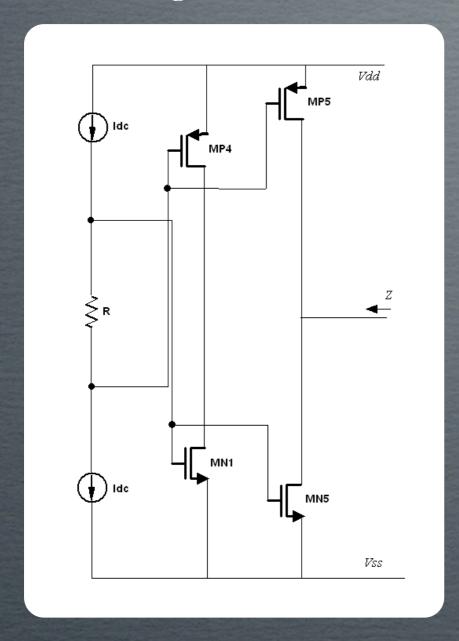

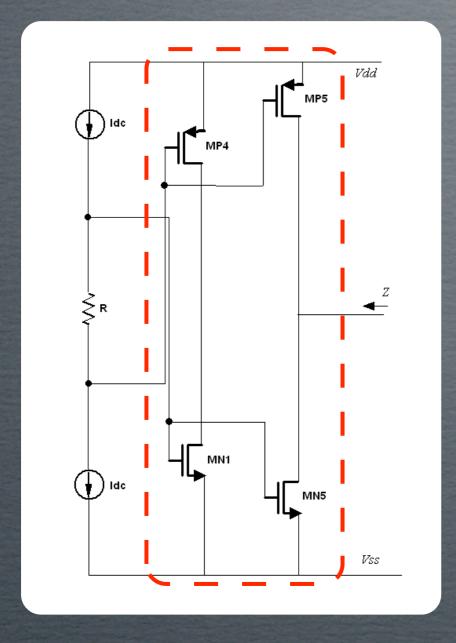

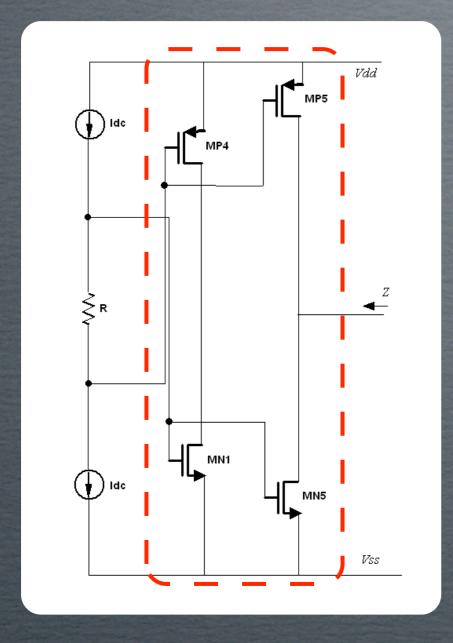

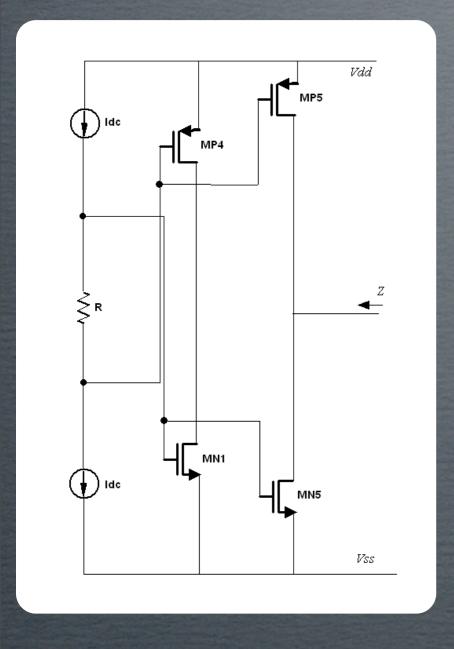

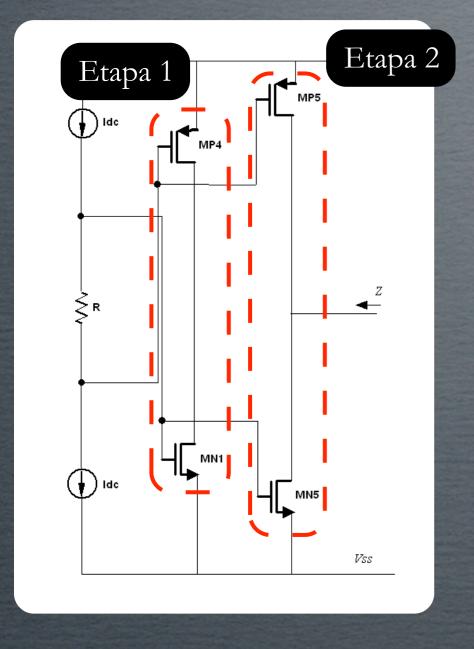

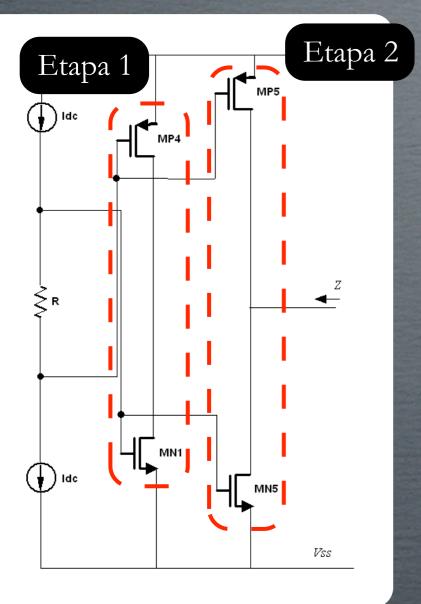

## Optimización de la etapa de salida

#### - Primer CCII

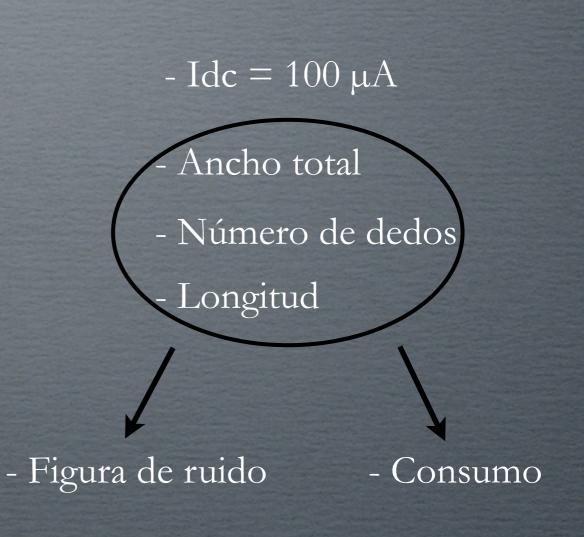

$- Idc = 100 \,\mu A$

Diseño a nivel esquemático Diseño a nivel layout

### Optimización de la etapa de salida

- $Idc = 100 \,\mu A$

- Ancho total

- Número de dedos

- Longitud

## Bloque 2 iseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

### Optimización de la etapa de salida

# Bloque 2 Diseño a nivel esquemático Diseño a nivel lavout

## Optimización de la etapa de salida

| Transistores         | Ancho total<br>(µm) | Número de<br>dedos | Lontigud<br>(µm) | Figura de ruido<br>(dB) | Consumo<br>(mA) |

|----------------------|---------------------|--------------------|------------------|-------------------------|-----------------|

| MP4, MP5<br>MN1, MN5 | 100<br>100          | 1<br>1             | 0,18<br>0,18     | 35                      | 9,5             |

| MP4, MP5<br>MN1, MN5 | 50<br>100           | 1<br>1             | 0,18<br>0,18     | 31                      | 44              |

| MP4, MP5<br>MN1, MN5 | 100<br>100          | 1<br>1             | 1<br>1           | 23                      | 4               |

| MP4, MP5<br>MN1, MN5 | 200<br>200          | 10<br>10           | 0,5<br>0,5       | 25,8                    | 3,4             |

| MP4, MP5<br>MN1, MN5 | 50<br>50            | 5<br>5             | 1 1              | 22                      | 4               |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1 1                | 1 1              | 17,15                   | 2,8             |

# Bloque 2 Diseño a nivel esquemático Diseño a nivel lavout

## Optimización de la etapa de salida

| Transistores         | Ancho total<br>(µm) | Número de<br>dedos | Lontigud<br>(µm)             | Figura de ruido<br>(dB) | Consumo<br>(mA) |

|----------------------|---------------------|--------------------|------------------------------|-------------------------|-----------------|

| MP4, MP5<br>MN1, MN5 | 100<br>100          | 1<br>1             | 0,18<br>0,18                 | 35                      | 9,5             |

| MP4, MP5<br>MN1, MN5 | 50<br>100           | 1<br>1             | 0,18<br>0,18                 | 31                      | 44              |

| MP4, MP5<br>MN1, MN5 | 100<br>100          | 1<br>1             | 1<br>1                       | 23                      | 4               |

| MP4, MP5<br>MN1, MN5 | 200<br>200          | 10<br>10           | 0 <b>,</b> 5<br>0 <b>,</b> 5 | 25,8                    | 3,4             |

| MP4, MP5<br>MN1, MN5 | 50<br>50            | 5<br>5             | 1<br>1                       | 22                      | 4               |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1                       | 17,15                   | 2,8             |

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

- Linealidad

- Ganancia

## Bloque 2 Diseño a nivel esquemático

## Optimización de la etapa de salida

| Transistores         | Ancho total<br>(µm) | Número de<br>dedos | Lontigud<br>(µm) | Fuentes Idc<br>(µm) | Ganancia<br>(dB) |

|----------------------|---------------------|--------------------|------------------|---------------------|------------------|

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 100                 | -74              |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 20                  | -7               |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 10                  | -9               |

## Bloque 2 Diseño a nivel esquemático

## Optimización de la etapa de salida

| Transistores         | Ancho total<br>(µm) | Número de<br>dedos | Lontigud<br>(µm) | Fuentes Idc<br>(µm) | Ganancia<br>(dB) |

|----------------------|---------------------|--------------------|------------------|---------------------|------------------|

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 100                 | -74              |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 20                  | -7               |

| MP4, MP5<br>MN1, MN5 | 100<br>50           | 1<br>1             | 1<br>1           | 10                  | -9               |

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

#### Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

## Optimización de la etapa de salida

| Fuentes Idc<br>(µA) | $ ho =  ho \left( oldsymbol{\Omega}  ight)$ | Figura de ruido<br>(dB) | Ganancia<br>(dB) | IIP3<br>(dBm) |

|---------------------|---------------------------------------------|-------------------------|------------------|---------------|

| 100                 | 1000                                        | 18,2                    | 14               | 1,3           |

| 100                 | 500                                         | 18                      | 14               | 2,2           |

| 50                  | 500                                         | 17,9                    | 13,4             | 1,8           |

| 20                  | 1000                                        | 18,3                    | 7                | 1             |

| 10                  | 500                                         | 22                      | 28               | 0,5           |

#### Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

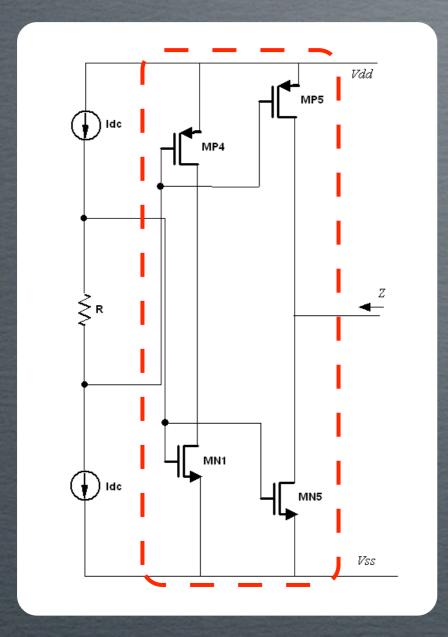

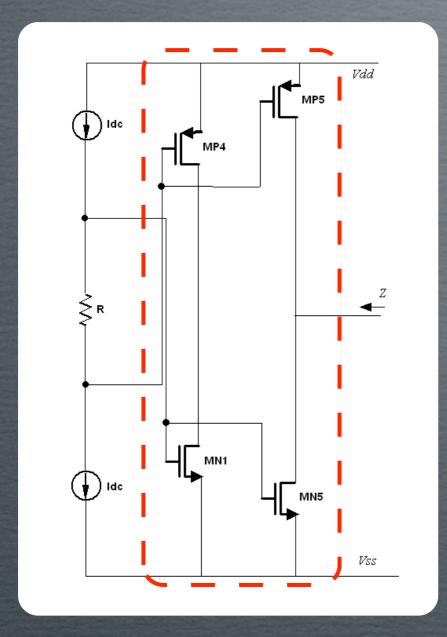

## Optimización de la etapa de salida

### - Segundo CCII

Ancho total: 150 um

Diseño a nivel esquemático Diseño a nivel layout

## Optimización de la etapa de salida

- Segundo CCII

Ancho total: 150 um

Ganancia

IIP3

Diseño a nivel esquemático Diseño a nivel layout

### Optimización de la etapa de salida

- Segundo CCII

Ancho total: 150 um

Ganancia

IIP3

Figura de ruido Consumo = 9 mA

Diseño a nivel esquemático Diseño a nivel layout

### Optimización de la etapa de salida

### - Segundo CCII

Ancho total: 150 um

Ganancia

IIP3

Figura de zuido Consumo = 9 mA

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

## Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel lavout

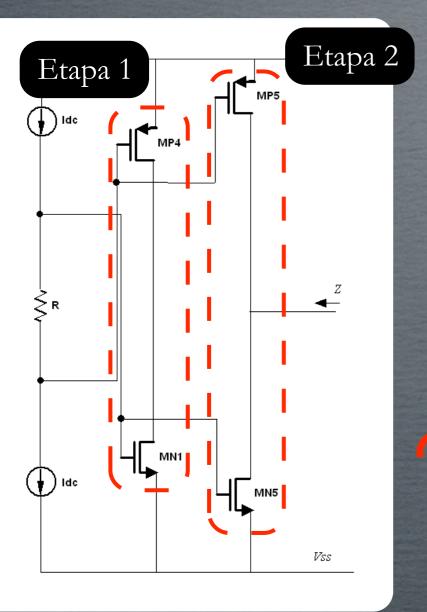

### Optimización de la etapa de salida

| Etapa 1 (µm) | Etapa 2<br>(µm) | Fuentes Idc<br>(µA) | Figura de ruido<br>(dB) | Ganancia<br>(dB) | IIP3<br>(dBm) | Consumo<br>(mA) |

|--------------|-----------------|---------------------|-------------------------|------------------|---------------|-----------------|

| 10           | 10              | 10                  | 18,71                   | 25               | -8            | 0,7             |

| 10           | 10              | 100                 | 18,27                   | 14               | no            | 3,6             |

| 5            | 10              | 10                  | 18,8                    | 25,9             | -4,5          | 1               |

| 10           | 20              | 10                  | 17,37                   | 27,3             | -7            | 1               |

| 10           | 20              | 40                  | 18                      | 13               | 1,8           | 2,6             |

| 10           | 30              | 20                  | 16,52                   | 30               | -7            | 1,7             |

| 1            | 20              | 10                  | 16,37                   | 29               | -10           | 0,8             |

Diseño a nivel esquemático Diseño a nivel layout

## Optimización de la etapa de salida

| Etapa 1<br>(µm) | Etapa 2<br>(µm) | Fuentes Idc<br>(µA) | Figura de ruido<br>(dB) | Ganancia<br>(dB) | IIP3<br>(dBm) | Consumo<br>(mA) |

|-----------------|-----------------|---------------------|-------------------------|------------------|---------------|-----------------|

| 10              | 10              | 10                  | 18,71                   | 25               | -8            | 0,7             |

| 10              | 10              | 100                 | 18,27                   | 14               | no            | 3,6             |

| 5               | 10              | 10                  | 18,8                    | 25,9             | -4,5          | 1               |

| 10              | 20              | 10                  | 17,37                   | 27,3             | -7            | 1               |

| 10              | 20              | 40                  | 18                      | 13               | 1,8           | 2,6             |

| 10              | 30              | 20                  | 16,52                   | 30               | -7            | 1,7             |

| 1               | 20              | 10                  | 16,37                   | 29               | -10           | 0,8             |

## Bloque 2 Diseño a nivel esquemático

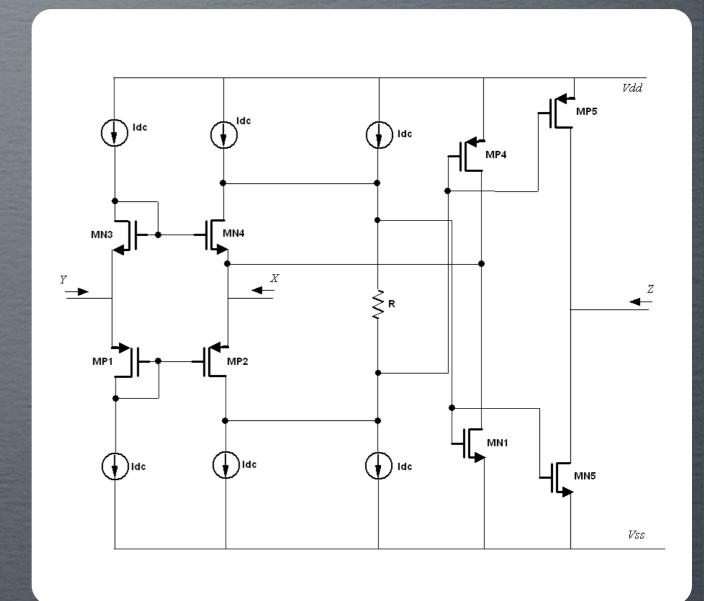

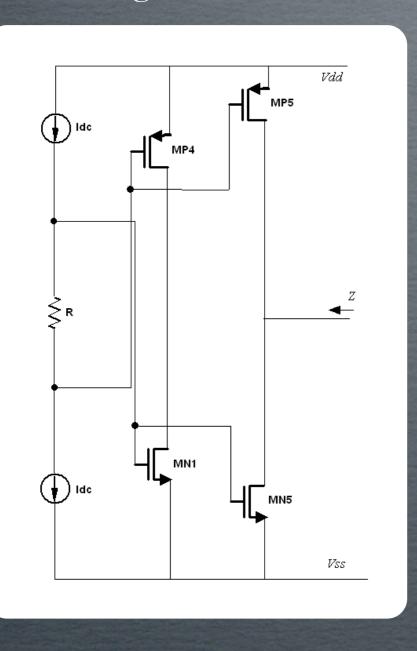

### Diseño completo y simulaciones finales

## Bloque 2 Diseño a nivel esquemático

### Diseño completo y simulaciones finales

## Diseño completo y simulaciones finales

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

|                         | Fuentes de corriente reales |

|-------------------------|-----------------------------|

| Ancho total (μm)        | 200                         |

| Ancho de los dedos (μm) | 10                          |

| Longitud (µm)           | 1                           |

| Número de dedos         | 20                          |

## Diseño completo y simulaciones finales

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

|                         | Fuentes de corriente reales |

|-------------------------|-----------------------------|

| Ancho total (μm)        | 200                         |

| Ancho de los dedos (μm) | 10                          |

| Longitud (µm)           | 1                           |

| Número de dedos         | 20                          |

18 dB

| Etapa 1<br>(µm) | Etapa 2<br>(µm) | $rac{	ext{R}}{(oldsymbol{\Omega})}$ | Figura de ruido<br>(dB) | Ganancia<br>(dB) | IIP3<br>(dBm) | Consumo<br>(mA) |

|-----------------|-----------------|--------------------------------------|-------------------------|------------------|---------------|-----------------|

| 10              | 300             | 1000                                 | 19                      | 25               | -1,9          | 11,5            |

| 10              | 30              | 250                                  | 18                      | 30               | -7,8          | 1,8             |

| 10              | 30              | 600                                  | 18,4                    | 30               | -6,7          | 1,8             |

| 10              | 30              | 1000                                 | 18                      | 30               | -5,6          | 1,9             |

| 10              | 30              | 500                                  | 18,4                    | 30               | -7,6          | 2,1             |

| Etapa 1<br>(µm) | Etapa 2<br>(µm) | $rac{	ext{R}}{(oldsymbol{\Omega})}$ | Figura de ruido<br>(dB) | Ganancia<br>(dB) | IIP3<br>(dBm) | Consumo (mA) |

|-----------------|-----------------|--------------------------------------|-------------------------|------------------|---------------|--------------|

| 10              | 300             | 1000                                 | 19                      | 25               | -1,9          | 11,5         |

| 10              | 30              | 250                                  | 18                      | 30               | -7,8          | 1,8          |

| 10              | 30              | 600                                  | 18,4                    | 30               | -6,7          | 1,8          |

| 10              | 30              | 1000                                 | 18                      | 30               | -5,6          | 1,9          |

| 10              | 30              | 500                                  | 18,4                    | 30               | -7,6          | 2,1          |

| Factor de<br>multiplicidad | Figura de ruido<br>(dB)         | Ganancia<br>(dB) | IIP3<br>(dBm) |  |

|----------------------------|---------------------------------|------------------|---------------|--|

| x 2                        | 17,2                            | 31               | -7,8          |  |

| x 3                        | 16                              | 30               | -7,67         |  |

| x 4                        | No realizable por la tecnología |                  |               |  |

|                         | Núcleo del CCII | Etapa 1 | Etapa 2 |

|-------------------------|-----------------|---------|---------|

| Ancho total (μm)        | 10              | 10      | 30      |

| Ancho de los dedos (µm) | 2               | 5       | 6       |

| Longitud (µm)           | 180             | 300     | 400     |

| Número de dedos         | 5               | 2       | 5       |

| Multiplicidad           | x 3             | x 1     | x 1     |

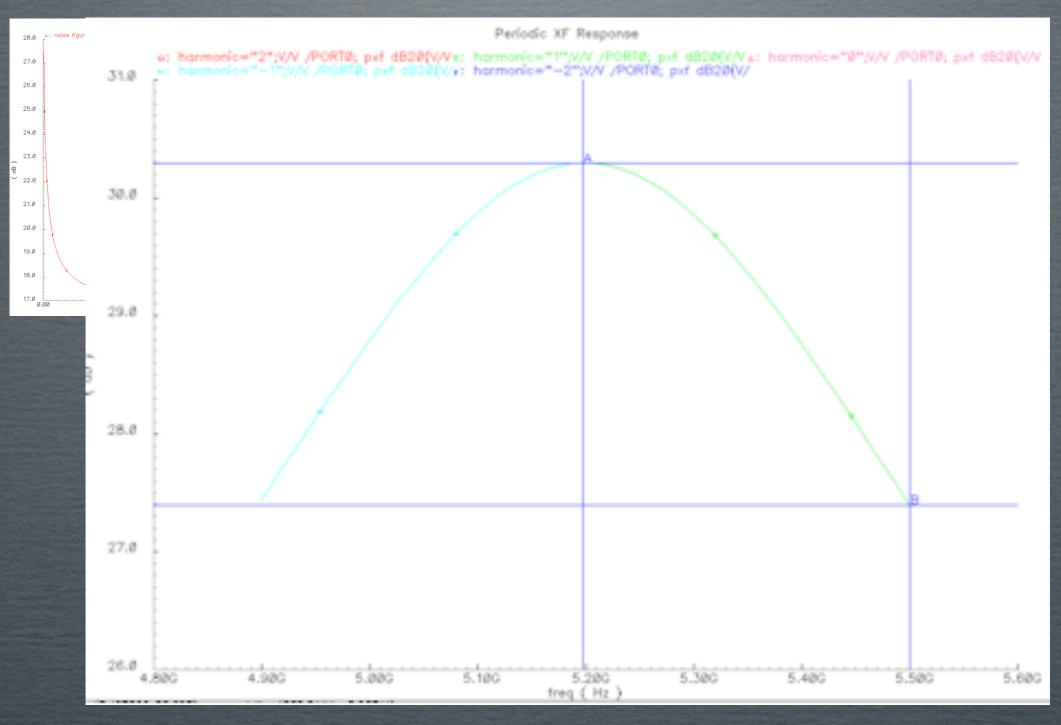

Diseño a nivel esquemático Diseño a nivel lavout

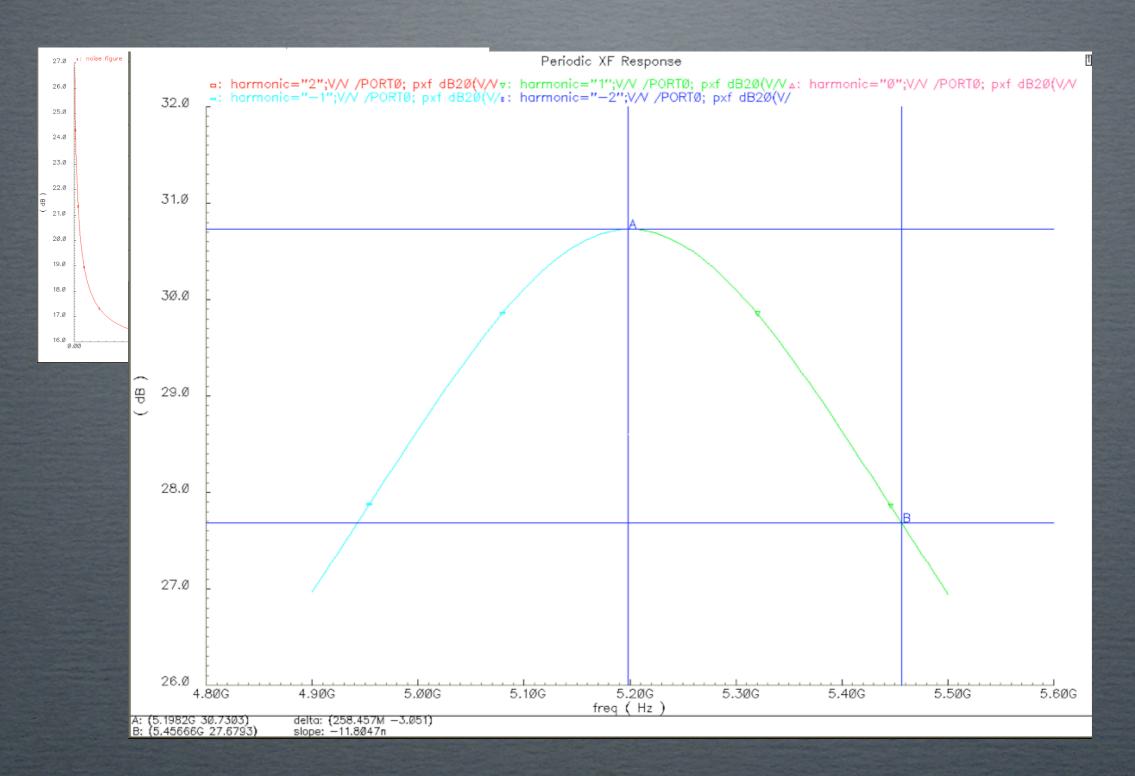

## Diseño completo y simulaciones finales

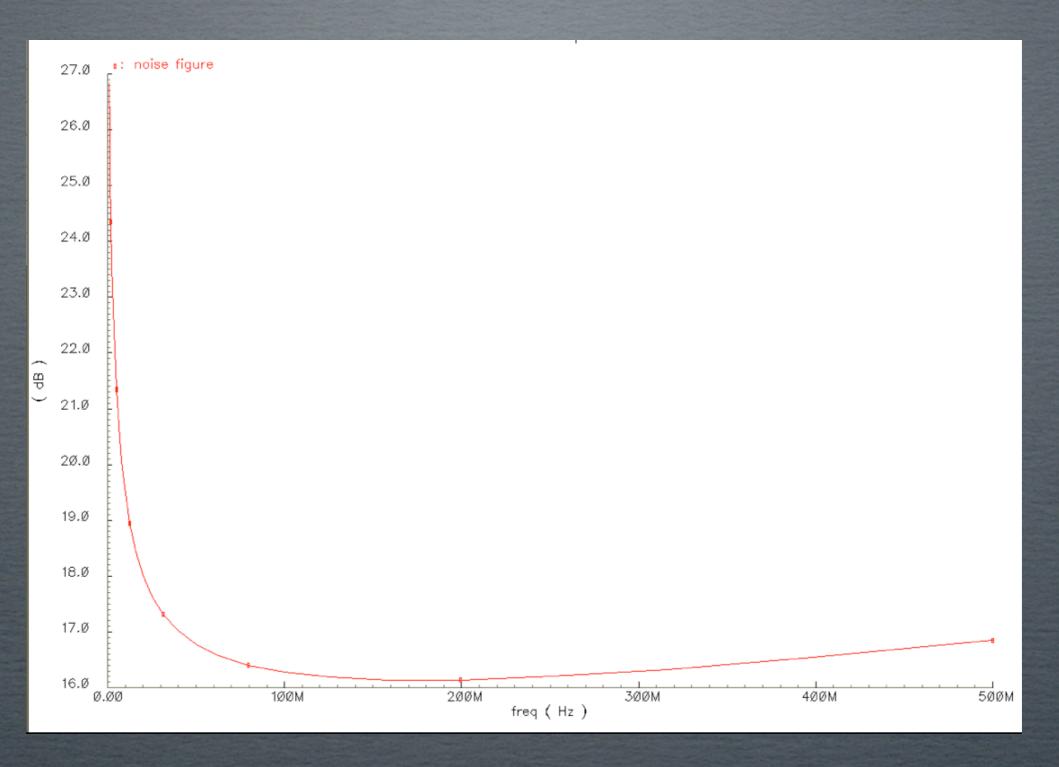

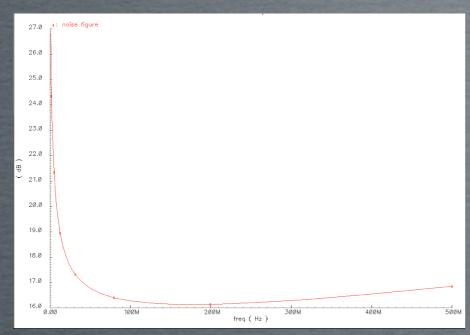

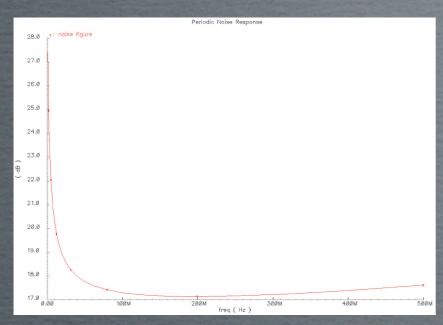

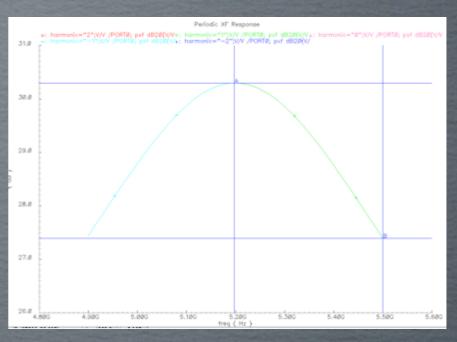

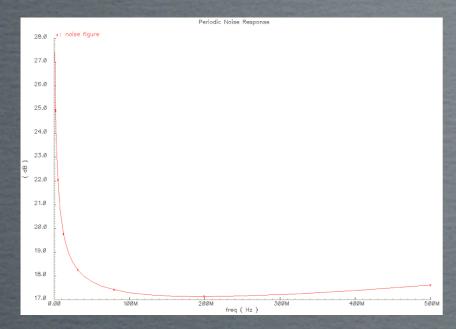

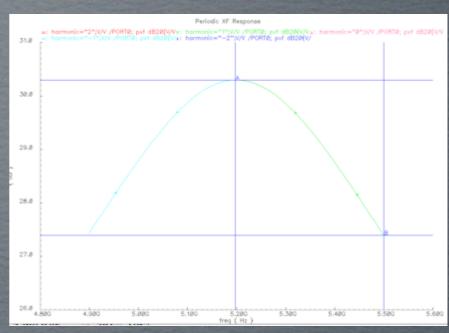

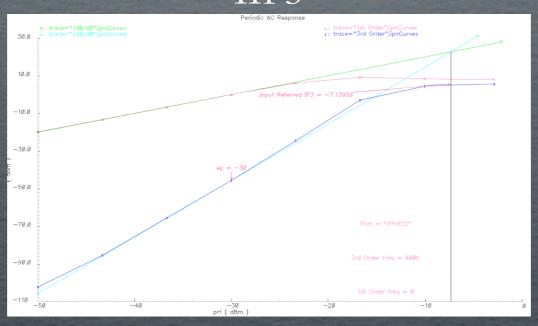

#### Figura de ruido

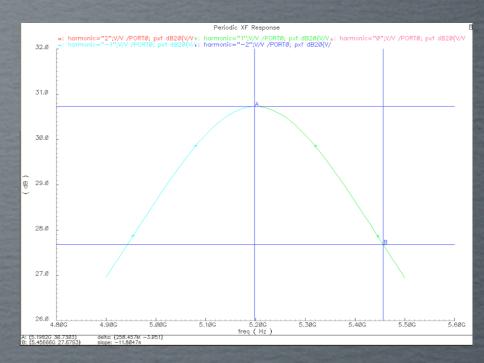

#### Ganancia

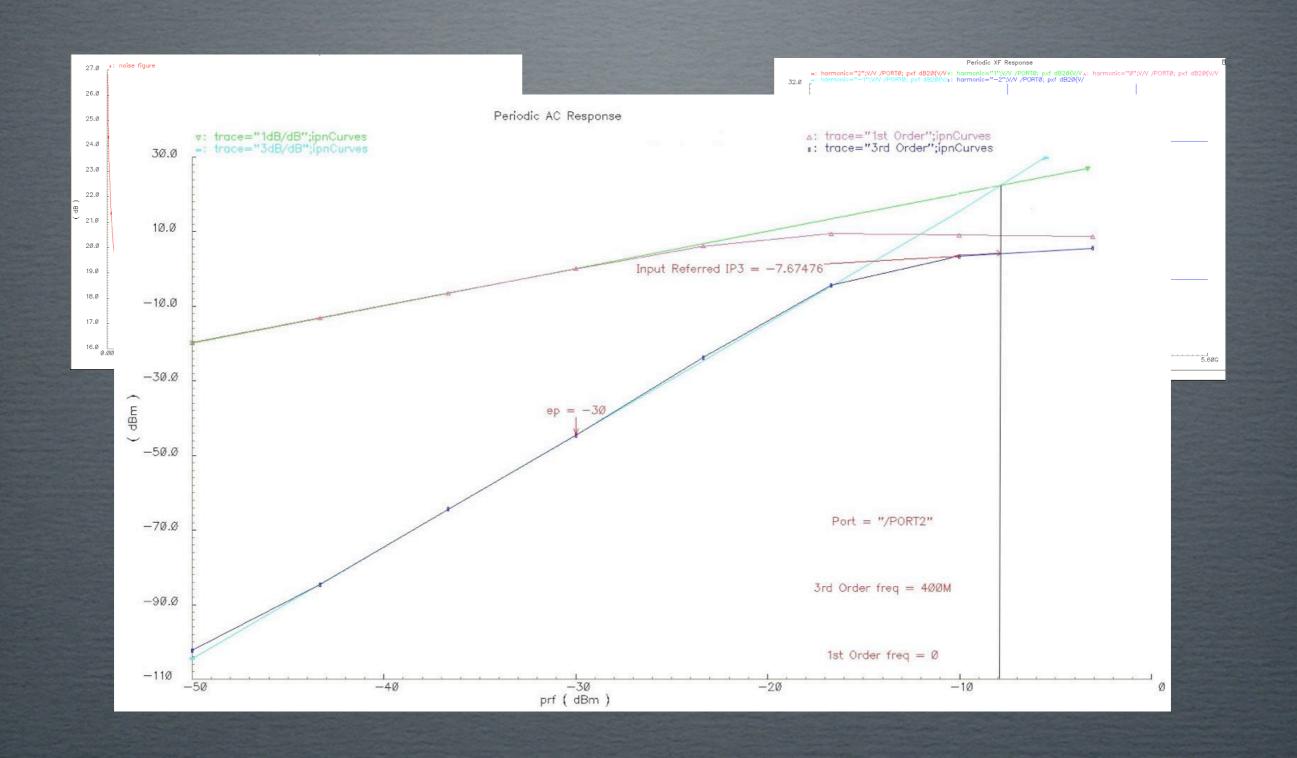

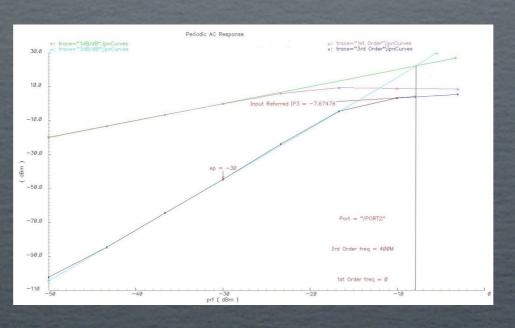

#### IIP3

| Figura de ruido (dB)           | 16,27 |

|--------------------------------|-------|

| Ganancia (dB)                  | 30,7  |

| Ancho de banda de salida (MHz) | 259   |

| IIP3 (dBm)                     | -7,67 |

| Consumo (mA)                   | 2,33  |

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

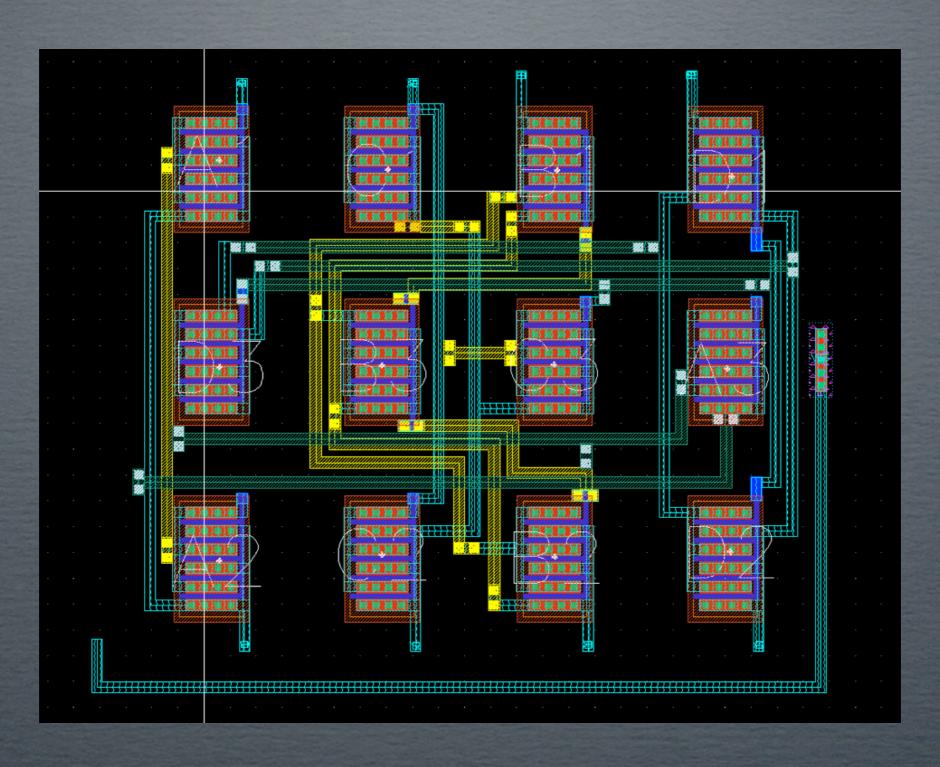

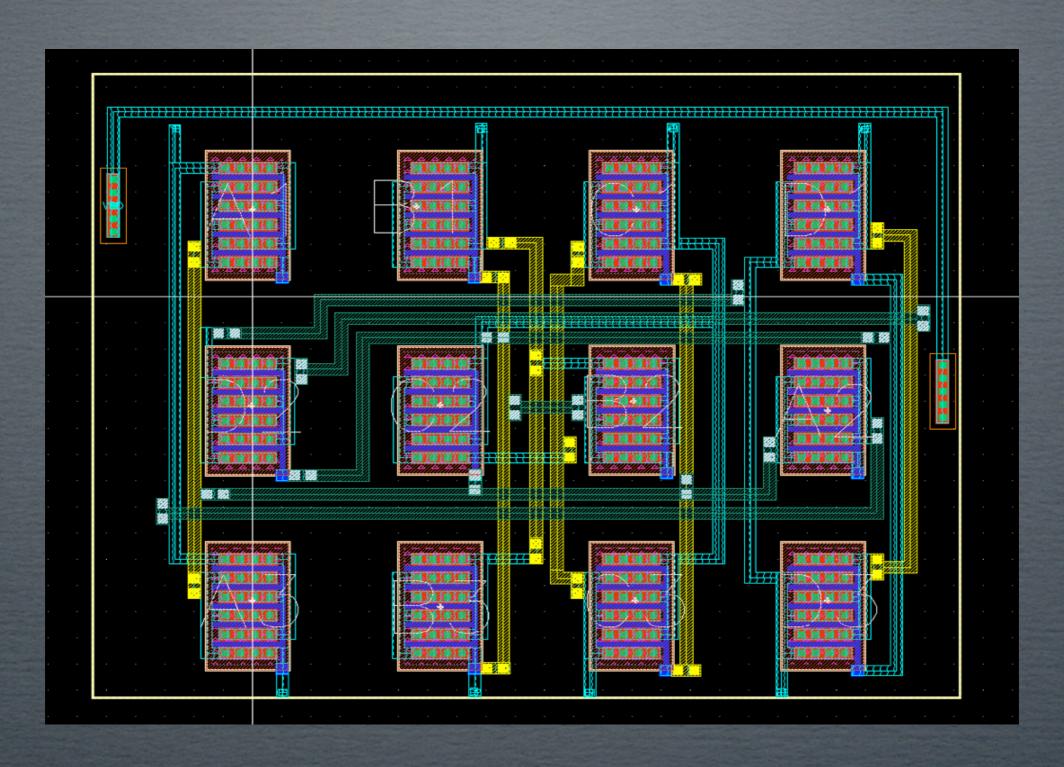

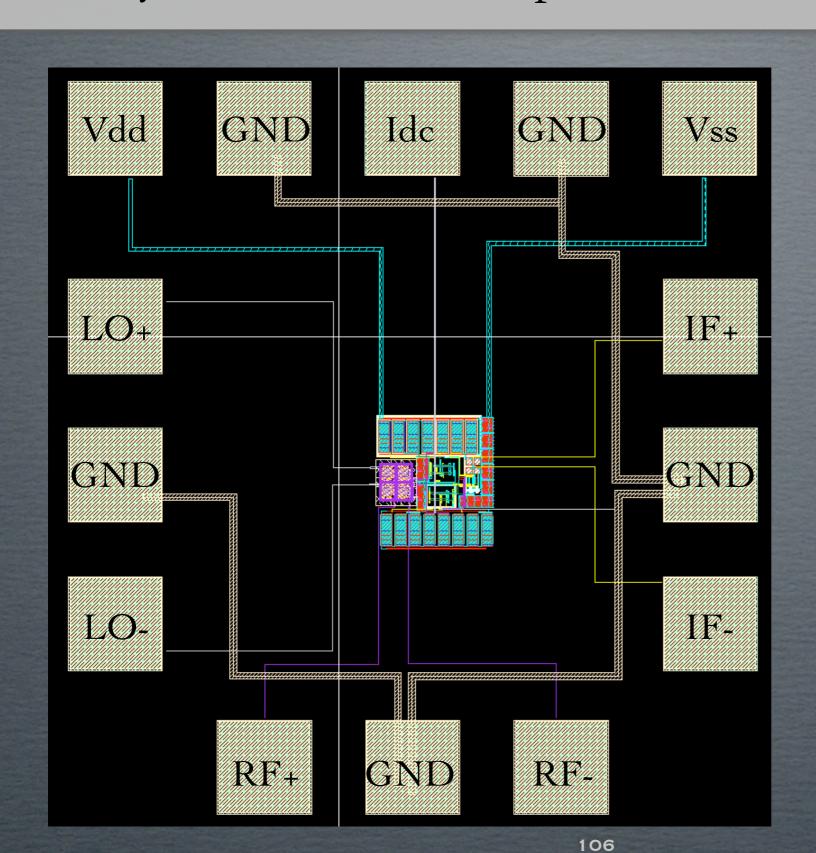

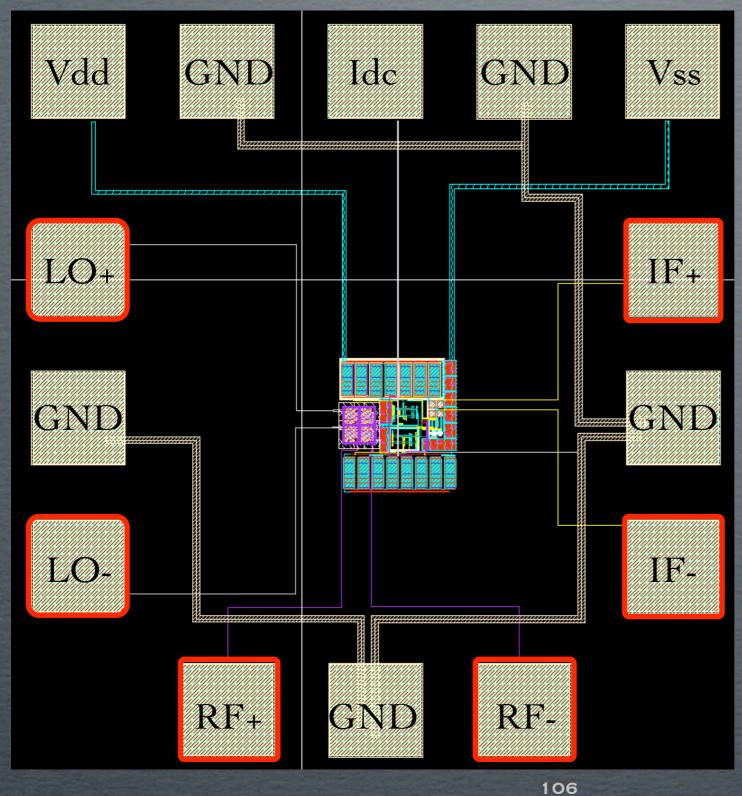

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

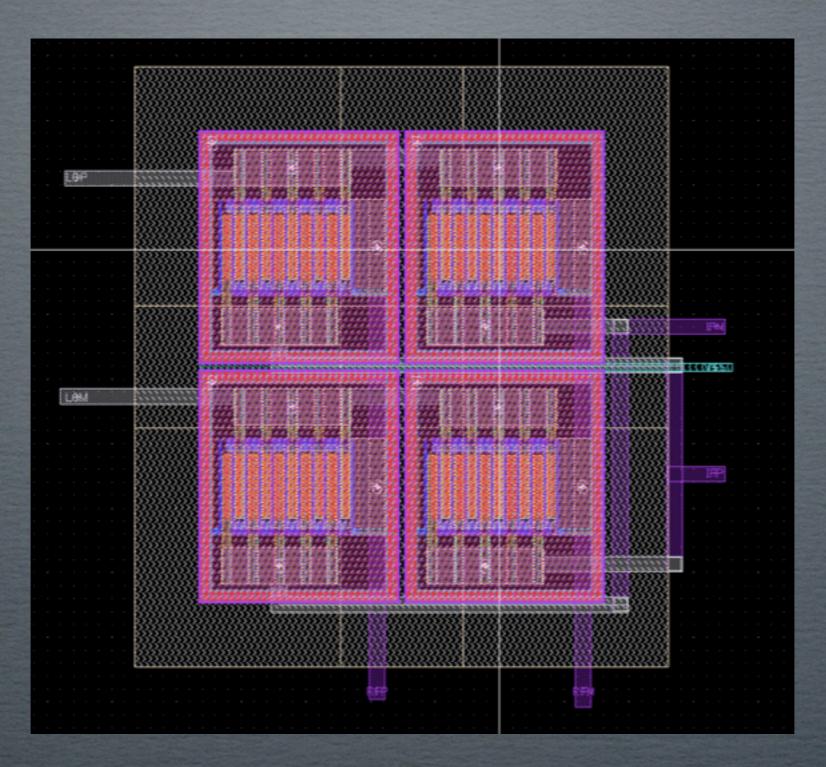

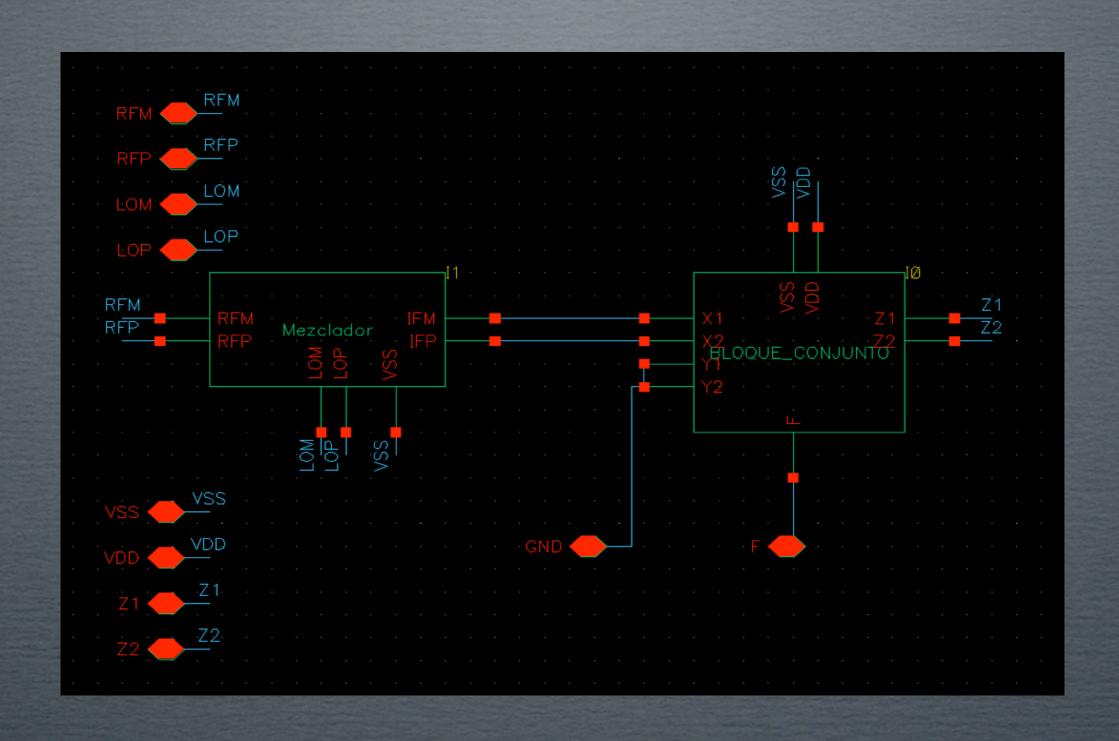

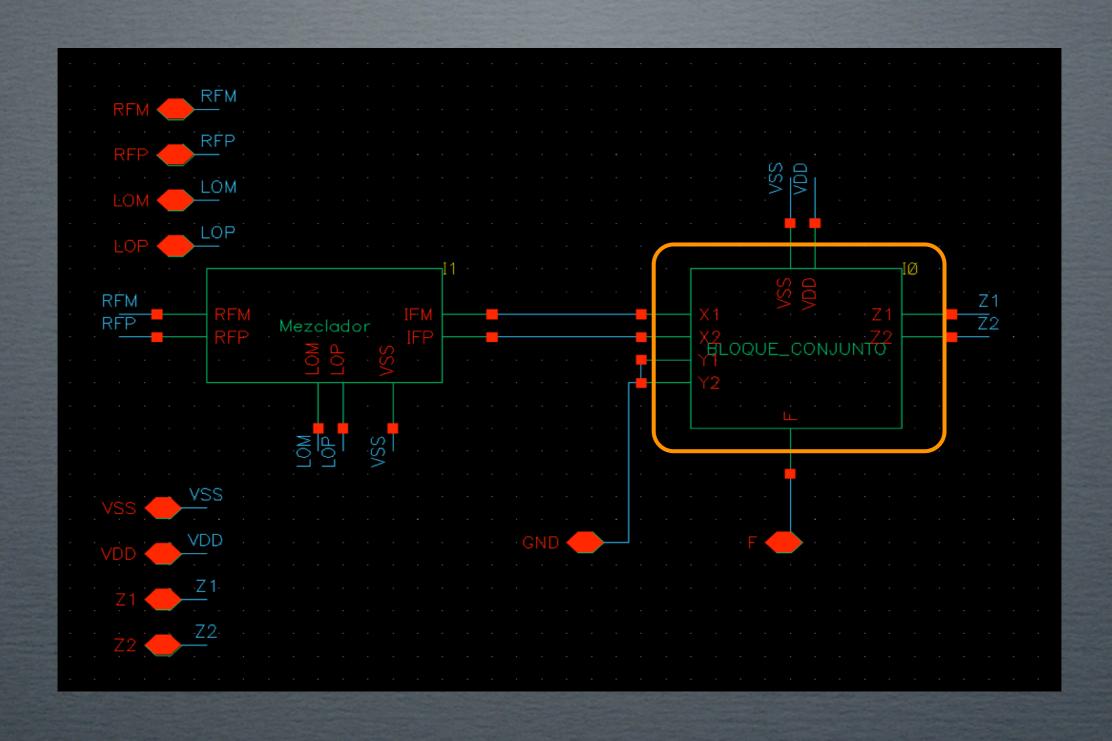

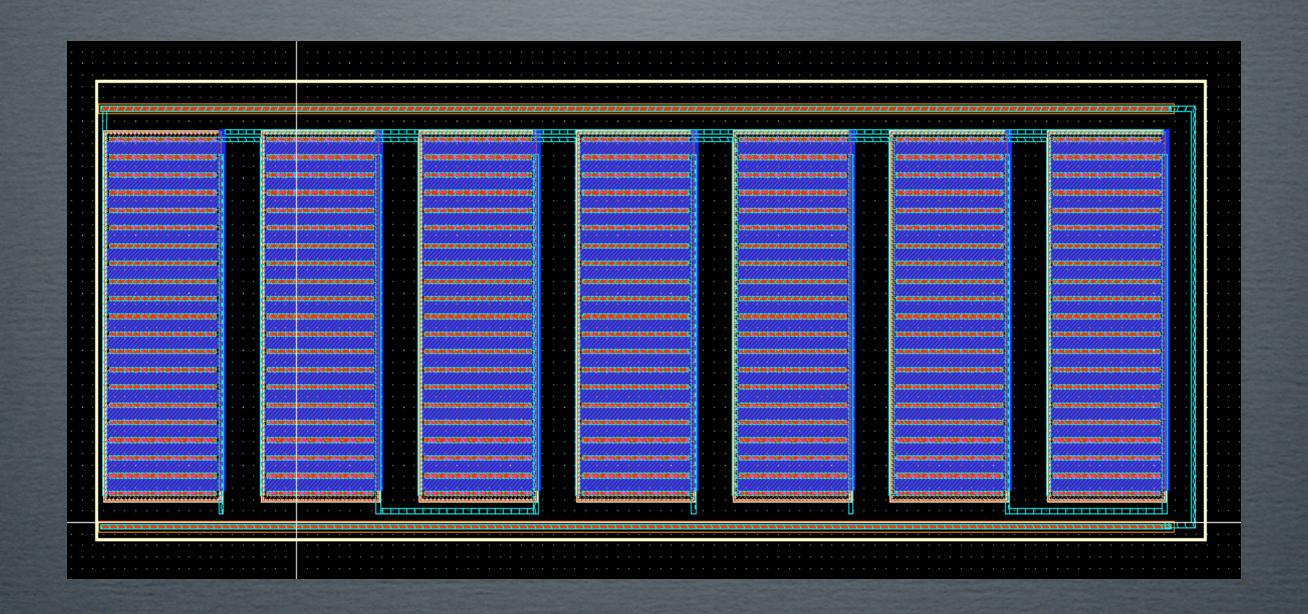

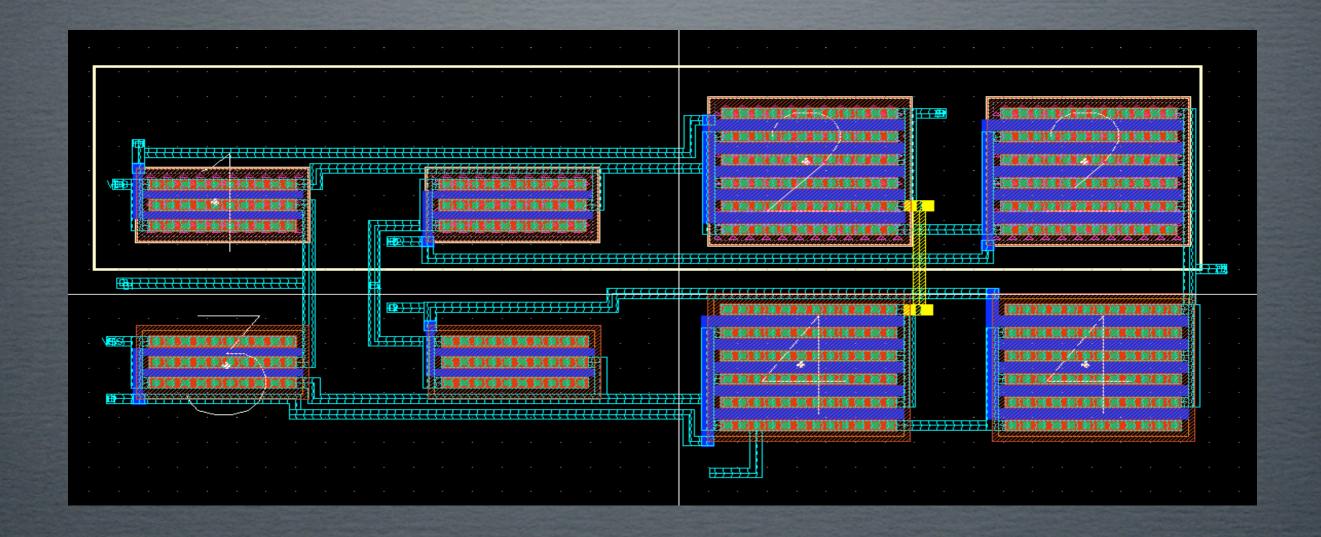

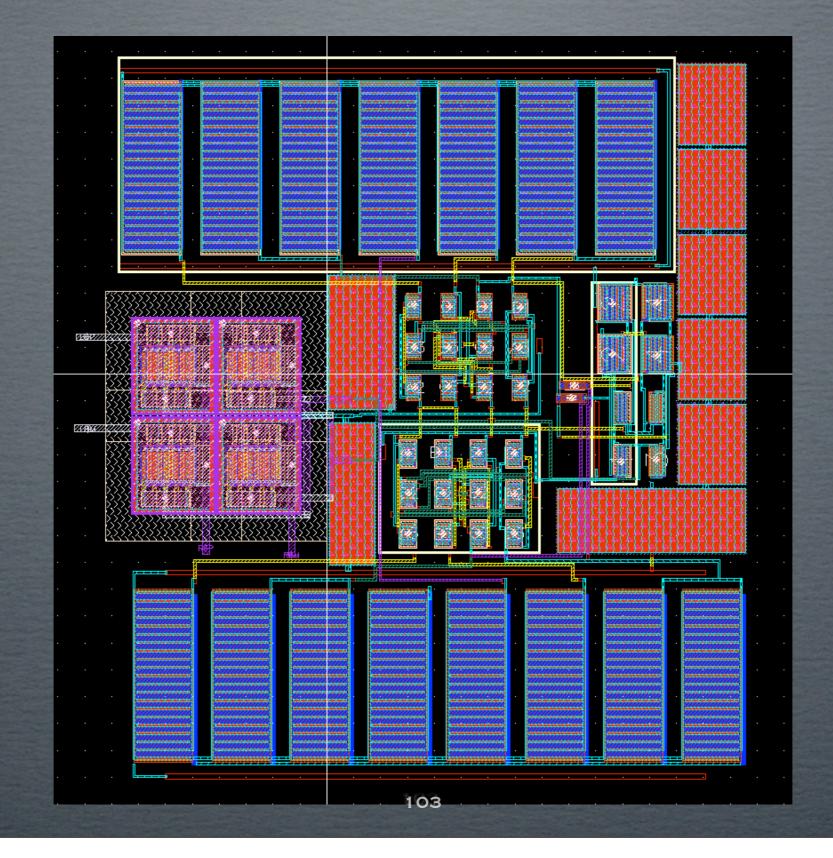

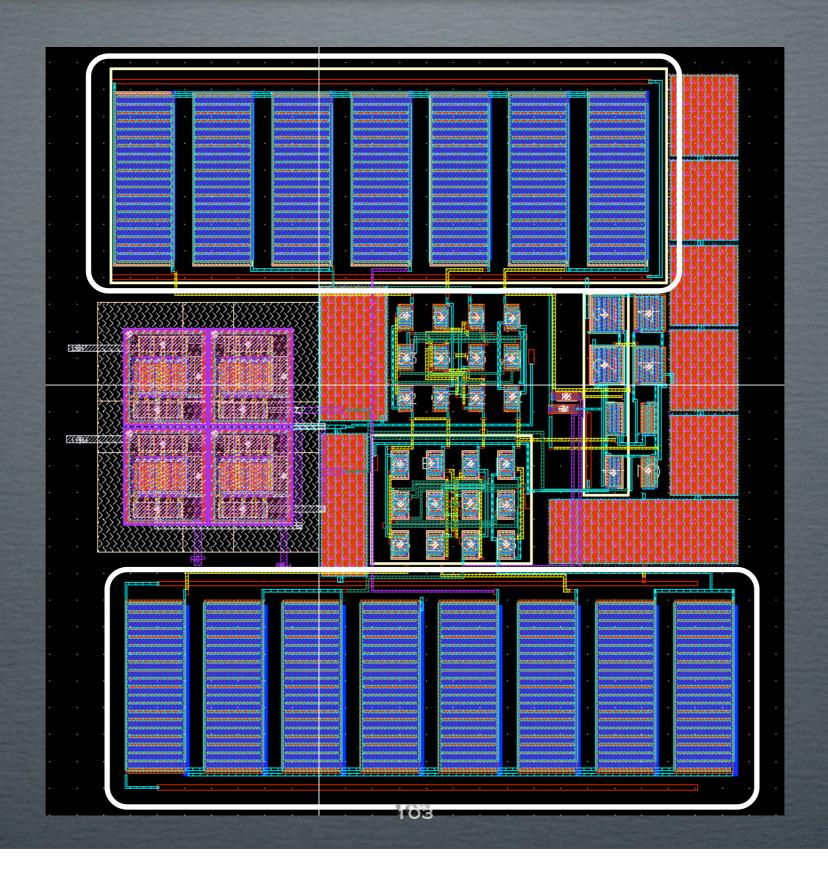

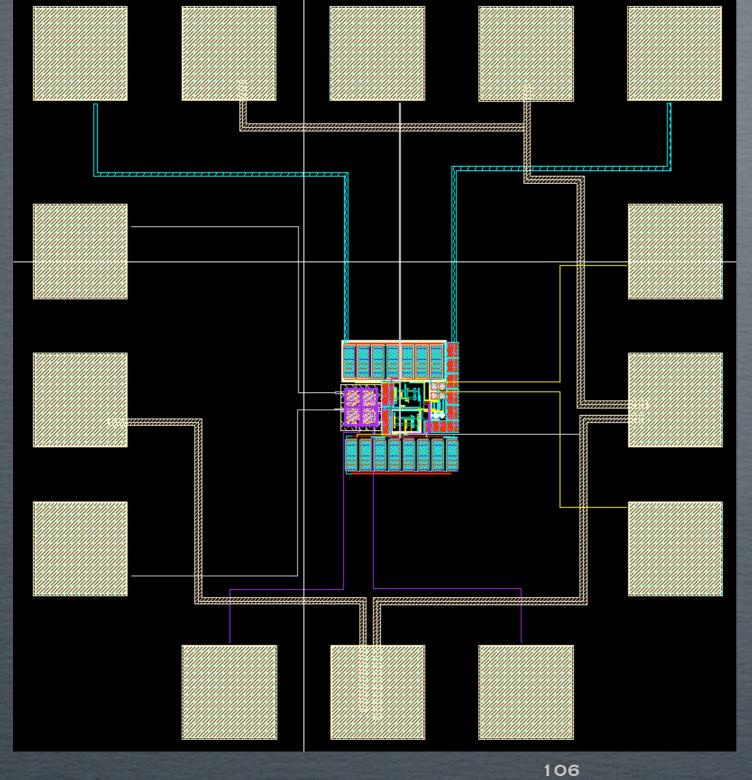

## Layout del mezclador

Diseño a nivel esquemático Diseño a nivel layout

## Layout del mezclador

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

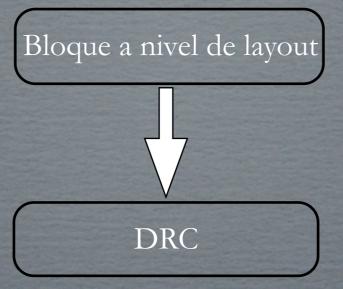

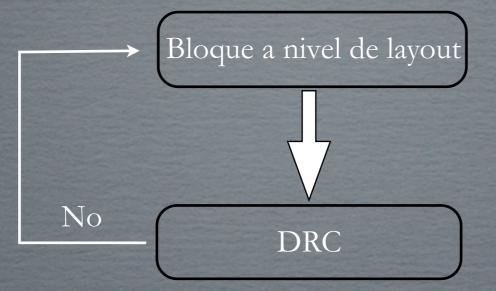

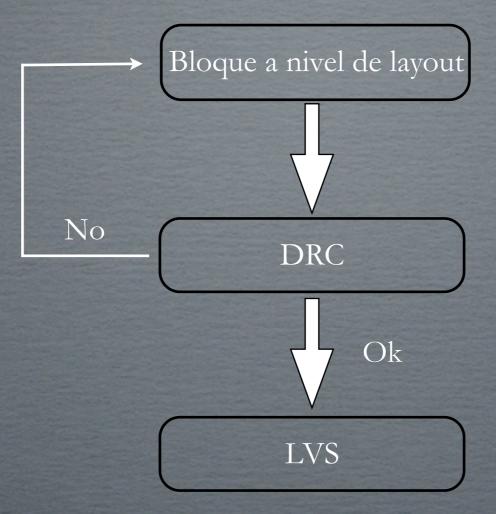

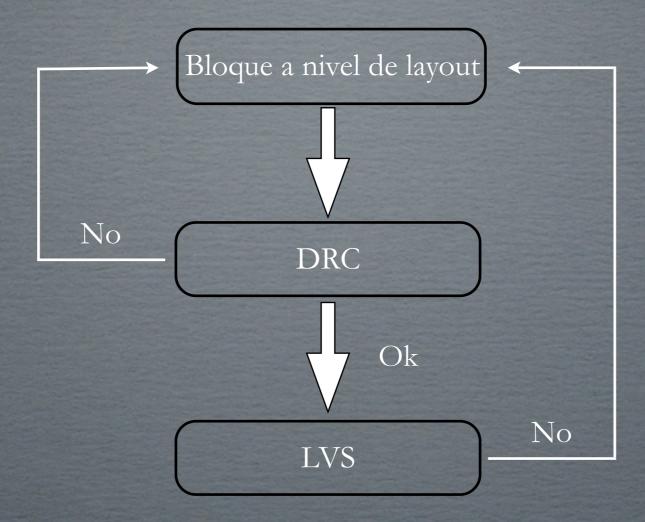

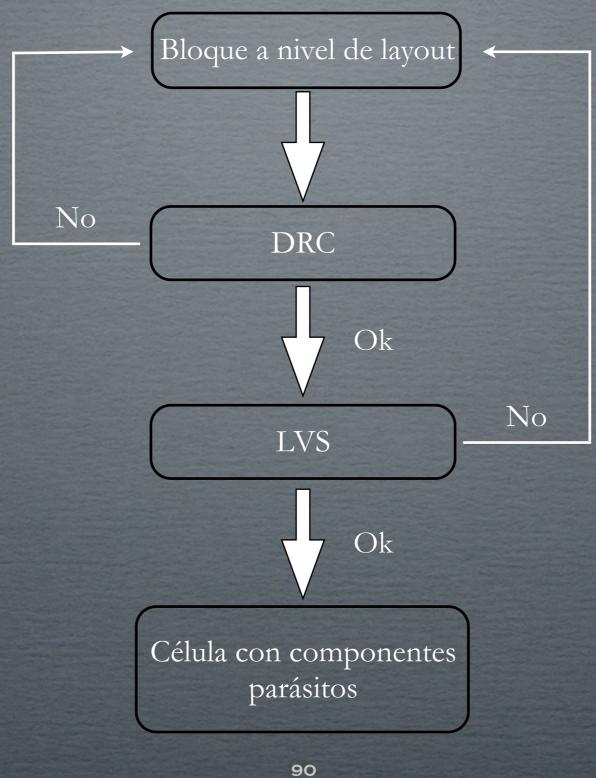

Bloque a nivel de layout

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

## Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

#### Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

## Layout del mezclador

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 254      | 30,73         | 16,27      | -7,67      |

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

## Layout del mezclador

#### Simulaciones bloque extraído del mezclador

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 254      | 30,73         | 16,27      | -7,67      |

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

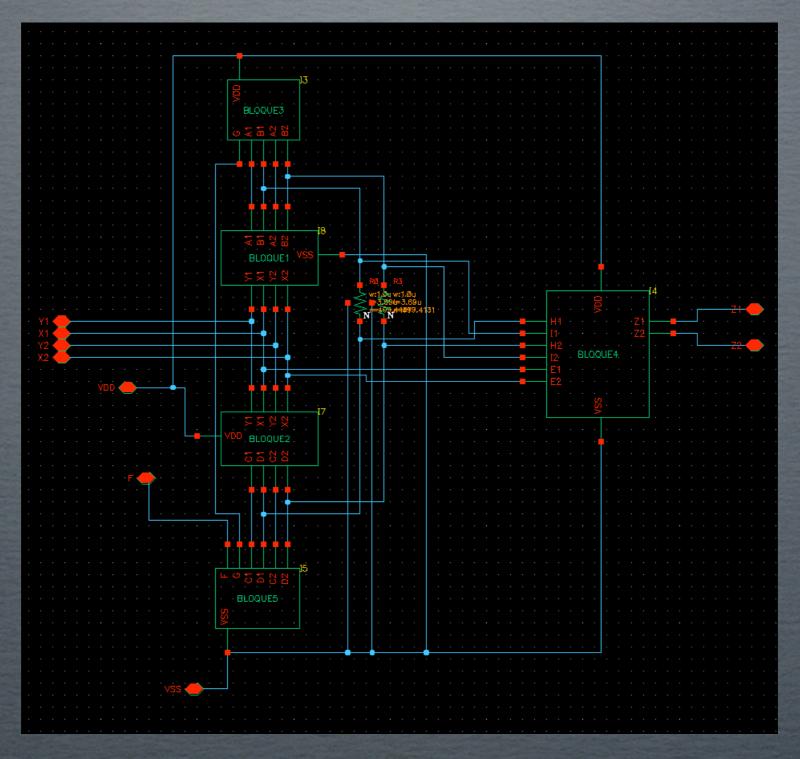

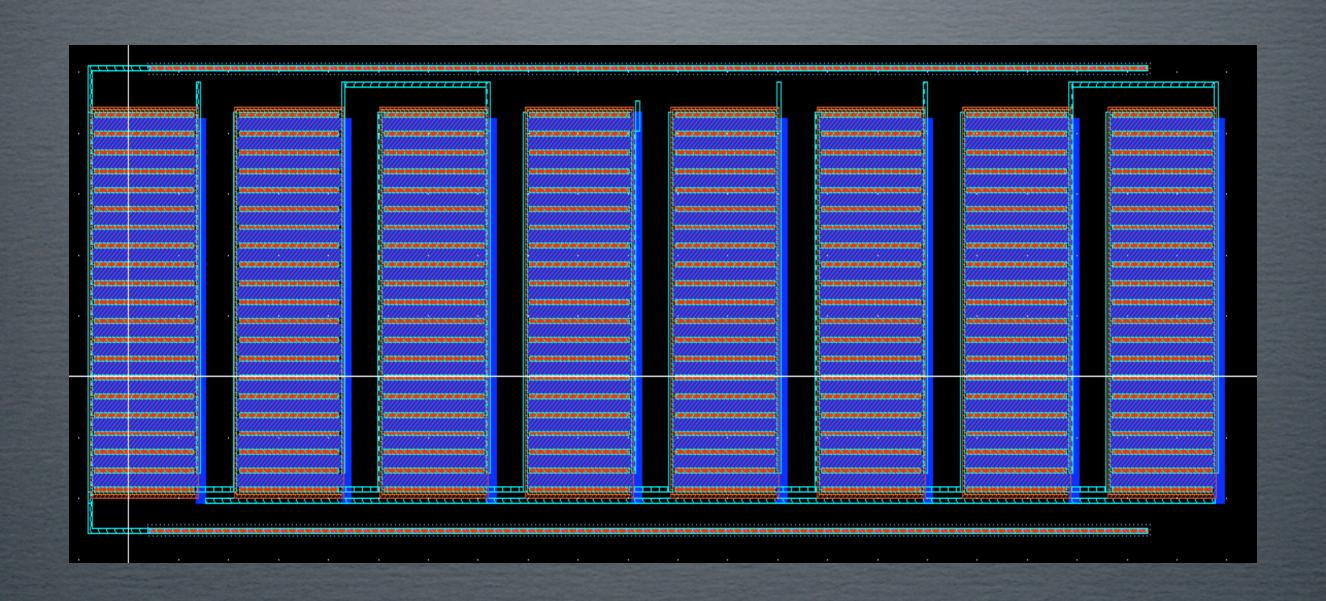

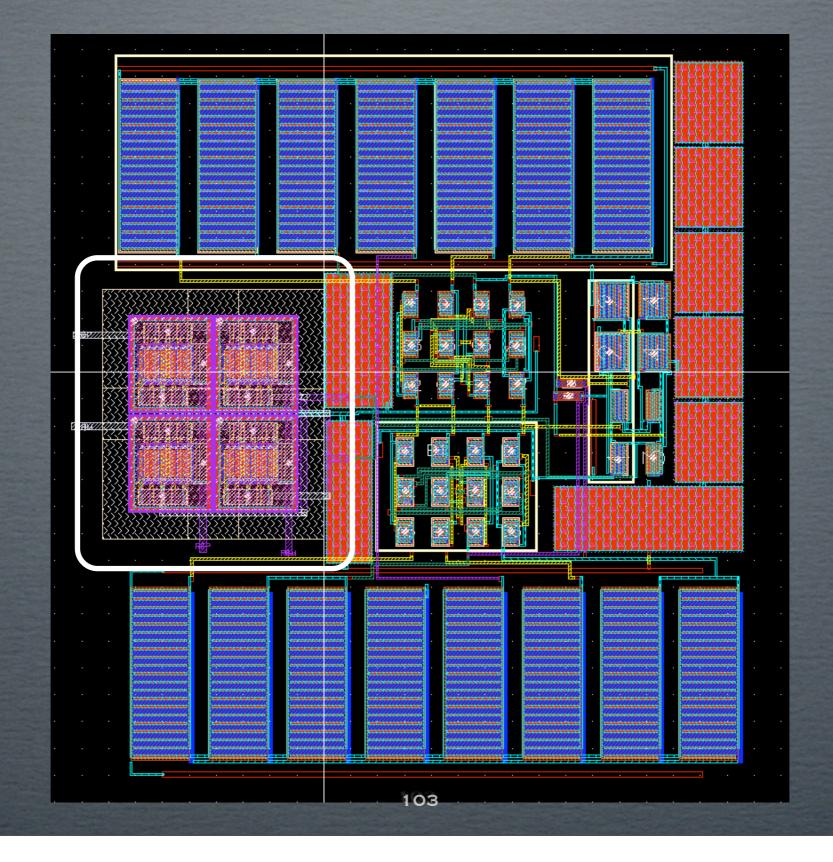

## Layout del current conveyor

Diseño a nivel esquemático Diseño a nivel layout

### Layout del current conveyor

## Layout del current conveyor

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

## Layout del current conveyor

## Layout del current conveyor

Bloque 2

Diseño a nivel esquemático

Diseño a nivel layout

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 250      | 30,7          | 16,36      | -7,15      |

Diseño a nivel esquemático Diseño a nivel layout

## Layout del current conveyor

#### Simulaciones bloque extraído del núcleo del CCII

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 250      | 30,7          | 16,36      | -7,15      |

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

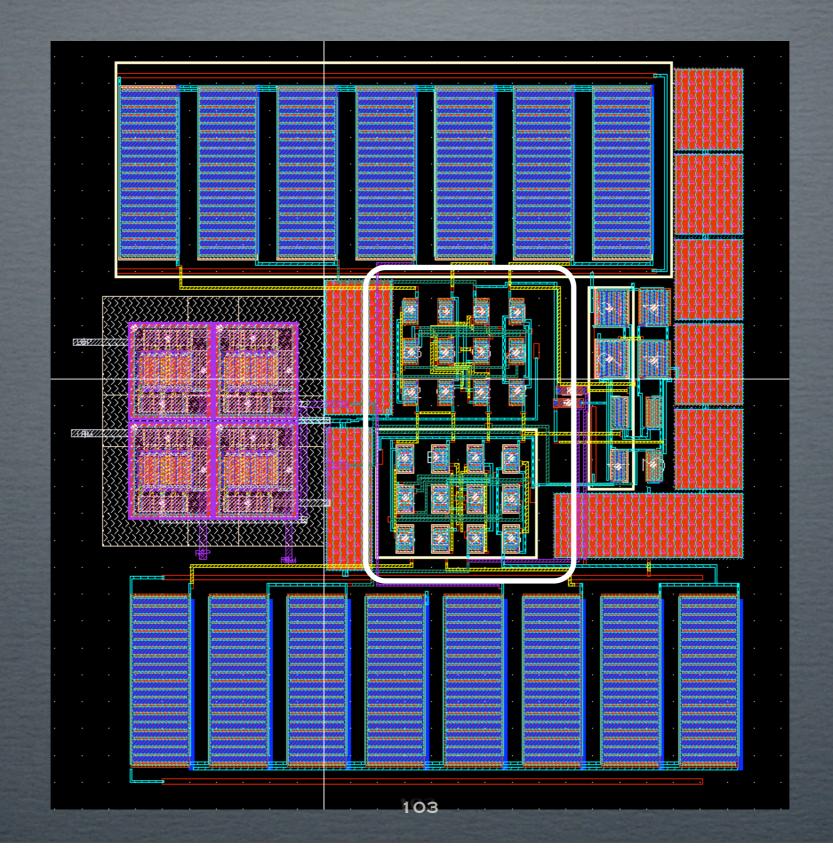

## Layout del current conveyor

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 260      | 30,7          | 16,80      | -7,46      |

#### Layout del current conveyor

## Simulaciones bloque extraído del núcleo del CCII y fuentes de corriente reales

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 260      | 30,7          | 16,80      | -7,46      |

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

#### Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 320      | 30,6          | 16,88      | -6,98      |

#### Layout del current conveyor

## Simulaciones bloque extraído del núcleo del CCII, fuentes de corriente reales y etapa de salida

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 320      | 30,6          | 16,88      | -6,98      |

Diseño a nivel esquemático Diseño a nivel layout

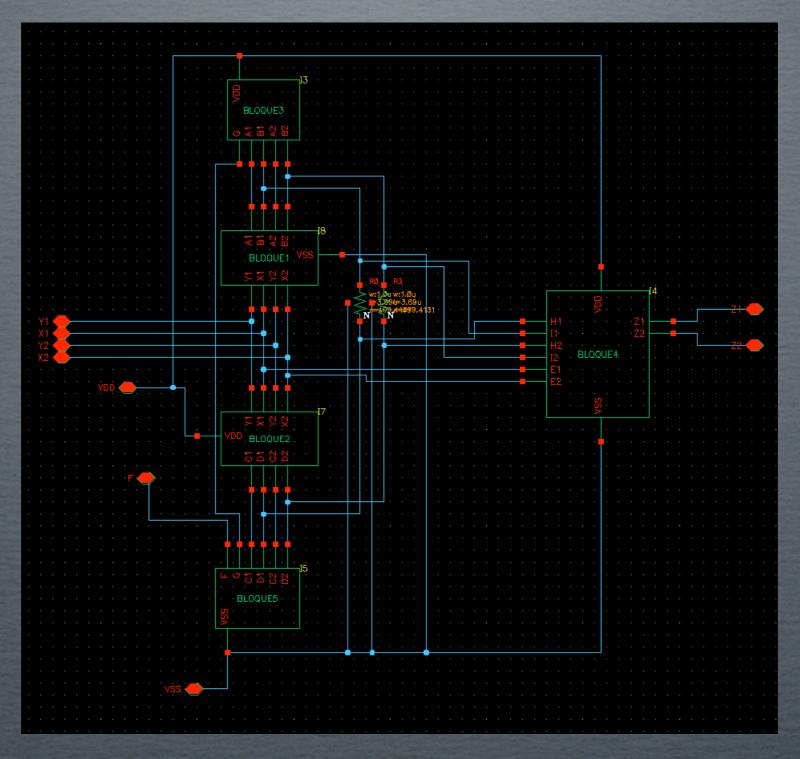

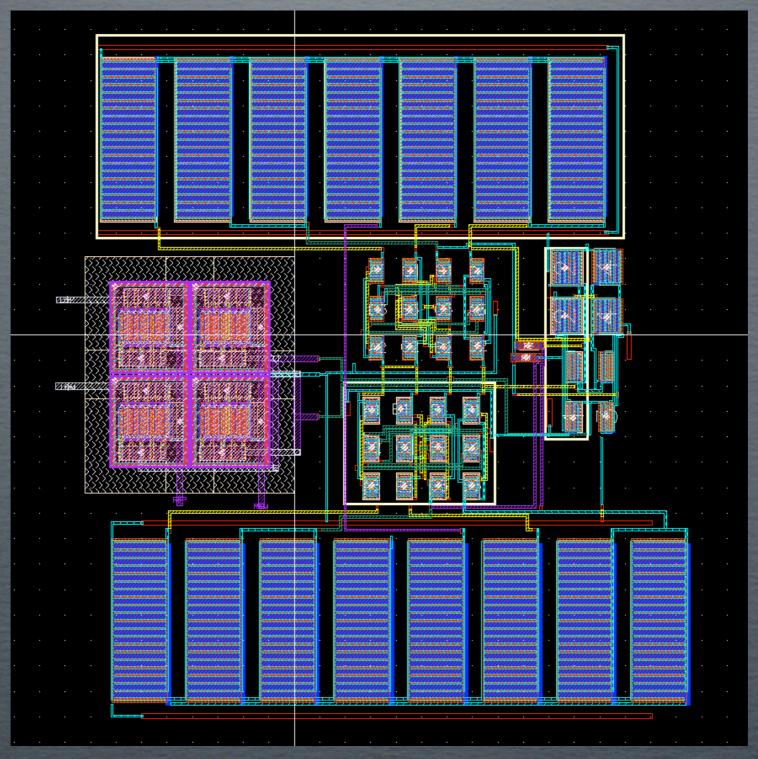

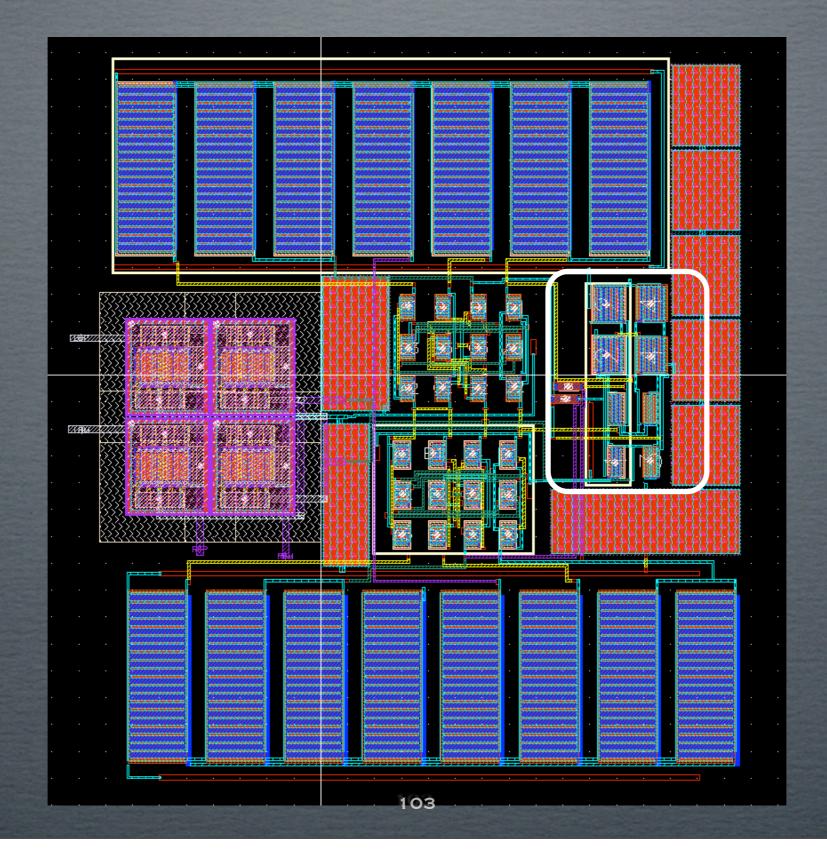

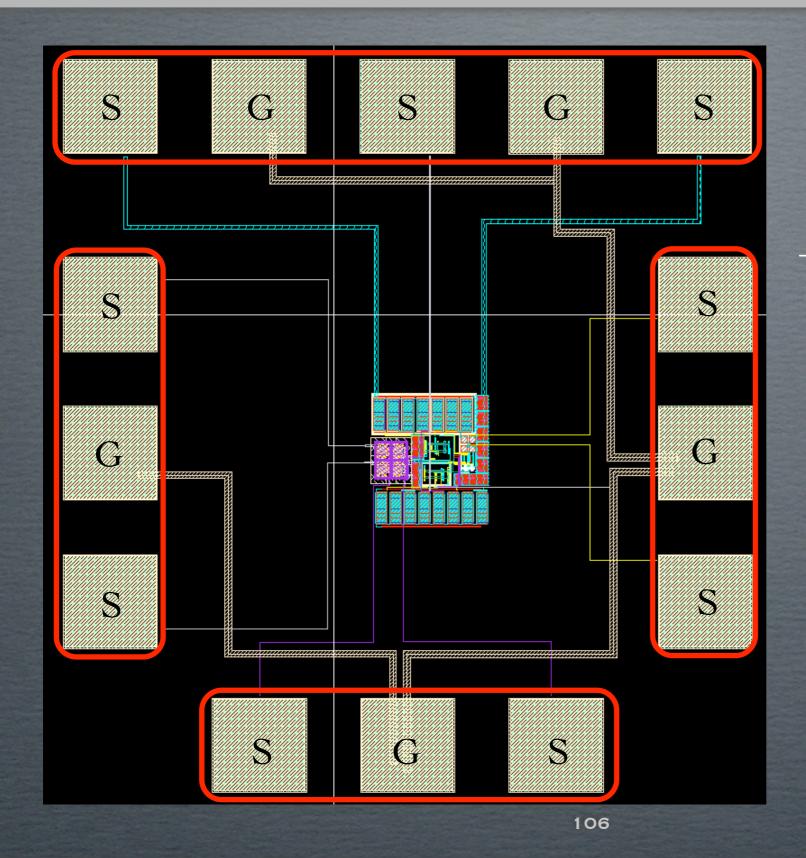

### Layout del diseño completo

# Bloque 2 Diseño a nivel esquemático Diseño a nivel layout

## Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemation

Diseño a nivel layout

## Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemátic Diseño a nivel layout

## Bloque 2 Diseño a nivel esquemático

Diseño a nivel esquemati

Diseño a nivel layout

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

#### Layout del diseño completo

#### Figura de ruido

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

#### Layout del diseño completo

#### Figura de ruido

#### Layout del diseño completo

#### Figura de ruido

#### Ganancia

#### Layout del diseño completo

### Layout del diseño completo

#### Figura de ruido

#### Ganancia

#### IID2

### Layout del diseño completo

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 300      | 30,3          | 17,21      | -7,14      |

#### Bloque 2 Diseño a nivel esquemátic

Diseño a nivel esquemático Diseño a nivel layout

#### Layout del diseño completo

#### Simulaciones bloque completo

| BW (MHz) | Ganancia (dB) | Ruido (dB) | IIP3 (dBm) |

|----------|---------------|------------|------------|

| 300      | 30,3          | 17,21      | -7,14      |

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

## Bloque 2 iseño a nivel esquemátic

Diseño a nivel esquemático Diseño a nivel layout

#### Layout del diseño completo

- Signal Ground Signal (SGS)

#### Bloque 2

Diseño a nivel esquemático Diseño a nivel layout

Diseño a nivel esquemático Diseño a nivel layout

#### Layout del diseño completo

- Simetrías LO y RF

- Señal IF

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

#### Conclusiones

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

#### Conclusiones

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

| Referencia           | Este proyecto | [6]       |

|----------------------|---------------|-----------|

| Tecnología           | CMOS 0,18     | CMOS 0,35 |

| Vdd (V)              | 1,8           | 3,3       |

| Consumo (mW)         | 4,14          | 1,913     |

| Frec. RF (GHz)       | 5,2           | 5,525     |

| Frec. IF (MHz)       | 200           | 25        |

| LO (dB)              | 0             | 0         |

| Ganancia (dB)        | 30,3          | 13,79     |

| IIP3 (dBm)           | -7,14         | 4,5       |

| Figura de ruido (dB) | 17,21         | 33,26     |

| Fecha                | 2010          | 2009      |

| Referencia     | Este proyecto | [6]          | [34]         | [33]          | [32]         | [31]         |

|----------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Tecnología     | CMOS 0,18     | CMOS<br>0,35 | CMOS<br>0,25 | CMOS<br>65 nm | CMOS<br>0,35 | CMOS<br>0,35 |

| Vdd (V)        | 1,8           | 3,3          | 1,8          | 1,2           | 3            | 3            |

| Consumo (mW)   | 4,14          | 1,913        | 13,3         | 9             | 45           | 18           |

| Frec. RF (GHz) | 5,2           | 5,525        | 2,44         | 5,15-5,35     | 1,1          | 4,488        |

| Frec. IF (MHz) | 200           | 25           | 0            | 0             | 10           | 45           |

| LO (dB)        | 0             | -70 dBm      | -            | -             | 5 dBm        | 2,5 (V)      |

| Ganancia (dB)  | 30,3          | 13,79        | -2,688       | 11            | -1           | 14,3         |

| IIP3 (dBm)     | -7,14         | 4,5          | 12,81        | 3             | 10           | -0,7         |

| NF (dB)        | 17,21         | 33,26        | 13,6         | -             | 20,3         | 4,8          |

| Fecha          | 2010          | 2009         | 2006         | 2008          | 2006         | 2007         |

| Tipo           | Mezclador p   | pasivo       |              | Mezclador     | activo       |              |

| Referencia     | Este proyecto | [6]          | [34]         | [33]          | [32]         | [31]         |

|----------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Tecnología     | CMOS 0,18     | CMOS<br>0,35 | CMOS<br>0,25 | CMOS<br>65 nm | CMOS<br>0,35 | CMOS<br>0,35 |

| Vdd (V)        | 1,8           | 3,3          | 1,8          | 1,2           | 3            | 3            |

| Consumo (mW)   | 4,14          | 1,913        | 13,3         | 9             | 45           | 18           |

| Frec. RF (GHz) | 5,2           | 5,525        | 2,44         | 5,15-5,35     | 1,1          | 4,488        |

| Frec. IF (MHz) | 200           | 25           | 0            | 0             | 10           | 45           |

| LO (dB)        | 0             | -70 dBm      |              | _             | 5 dBm        | 2,5 (V)      |

| Ganancia (dB)  | 30,3          | 13,79        | -2,688       | 11            | -1           | 14,3         |

| IIP3 (dBm)     | -7,14         | 4,5          | 12,81        | 3             | 10           | -0,7         |

| NF (dB)        | 17,21         | 33,26        | 13,6         | -             | 20,3         | 4,8          |

| Fecha          | 2010          | 2009         | 2006         | 2008          | 2006         | 2007         |

| Tipo           | Mezclador p   | pasivo       |              | Mezclador     | activo       |              |

| Referencia     | Este proyecto | [6]          | [34]         | [33]          | [32]         | [31]         |

|----------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Tecnología     | CMOS 0,18     | CMOS<br>0,35 | CMOS<br>0,25 | CMOS<br>65 nm | CMOS<br>0,35 | CMOS<br>0,35 |

| Vdd (V)        | 1,8           | 3,3          | 1,8          | 1,2           | 3            | 3            |

| Consumo (mW)   | 4,14          | 1,913        | 13,3         | 9             | 45           | 18           |

| Frec. RF (GHz) | 5,2           | 5,525        | 2,44         | 5,15-5,35     | 1,1          | 4,488        |

| Frec. IF (MHz) | 200           | 25           | 0            | 0             | 10           | 45           |

| LO (dB)        | 0             | -70 dBm      | -            | -             | 5 dBm        | 2,5 (V)      |

| Ganancia (dB)  | 30,3          | 13,79        | -2,688       | 11            | -1           | 14,3         |

| IIP3 (dBm)     | -7,14         | 4,5          | 12,81        | 3             | 10           | -0,7         |

| NF (dB)        | 17,21         | 33,26        | 13,6         |               | 20,3         | 4,8          |

| Fecha          | 2010          | 2009         | 2006         | 2008          | 2006         | 2007         |

| Tipo           | Mezclador p   | pasivo       |              | Mezclador     | activo       |              |

| Referencia     | Este proyecto | [6]          | [34]         | [33]          | [32]         | [31]         |

|----------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Tecnología     | CMOS 0,18     | CMOS<br>0,35 | CMOS<br>0,25 | CMOS<br>65 nm | CMOS<br>0,35 | CMOS<br>0,35 |

| Vdd (V)        | 1,8           | 3,3          | 1,8          | 1,2           | 3            | 3            |

| Consumo (mW)   | 4,14          | 1,913        | 13,3         | 9             | 45           | 18           |

| Frec. RF (GHz) | 5,2           | 5,525        | 2,44         | 5,15-5,35     | 1,1          | 4,488        |

| Frec. IF (MHz) | 200           | 25           | 0            | 0             | 10           | 45           |

| LO (dB)        | 0             | -70 dBm      | -            | -             | 5 dBm        | 2,5 (V)      |

| Ganancia (dB)  | 30,3          | 13,79        | -2,688       | 11            | -1           | 14,3         |

| IIP3 (dBm)     | -7,14         | 4,5          | 12,81        | 3             | 10           | -0,7         |

| NF (dB)        | 17,21         | 33,26        | 13,6         | -             | 20,3         | 4,8          |

| Fecha          | 2010          | 2009         | 2006         | 2008          | 2006         | 2007         |

| Tipo           | Mezclador p   | pasivo       |              | Mezclador     | activo       |              |

| Referencia     | Este proyecto | [6]          | [34]         | [33]          | [32]         | [31]         |

|----------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Tecnología     | CMOS 0,18     | CMOS<br>0,35 | CMOS<br>0,25 | CMOS<br>65 nm | CMOS<br>0,35 | CMOS<br>0,35 |

| Vdd (V)        | 1,8           | 3,3          | 1,8          | 1,2           | 3            | 3            |

| Consumo (mW)   | 4,14          | 1,913        | 13,3         | 9             | 45           | 18           |

| Frec. RF (GHz) | 5,2           | 5,525        | 2,44         | 5,15-5,35     | 1,1          | 4,488        |

| Frec. IF (MHz) | 200           | 25           | 0            | 0             | 10           | 45           |

| LO (dB)        | 0             | -70 dBm      | -            | -             | 5 dBm        | 2,5 (V)      |

| Ganancia (dB)  | 30,3          | 13,79        | -2,688       | 11            | -1           | 14,3         |

| IIP3 (dBm)     | -7,14         | 4,5          | 12,81        | 3             | 10           | -0,7         |

| NF (dB)        | 17,21         | 33,26        | 13,6         |               | 20,3         | 4,8          |

| Fecha          | 2010          | 2009         | 2006         | 2008          | 2006         | 2007         |

| Tipo           | Mezclador p   | pasivo       |              | Mezclador     | activo       |              |

Bloque 3

Conclusiones

Presupuesto

Bloque 3

Conclusiones

Presupuesto

#### Conclusiones

- Líneas futuras

- Realizar las simulaciones del circuito sobre oblea

- Realizar las simulaciones del circuito sobre oblea

- Integrar el circuito en una cadena de recepción

- Realizar las simulaciones del circuito sobre oblea

- Integrar el circuito en una cadena de recepción

- Comprobar el correcto funcionamiento

Estructura de la memoria

Bloque 1

Introducción

Objetivos

Características de los sistemas RF

Estándar WiMedia

Teoría de los mezcladores

Teoría de los current conveyor

Bloque 2

Diseño a nivel esquemático Diseño a nivel de layout

Bloque 3

Conclusiones Presupuesto

# Presupuesto

| Descripción                        | Gastos (€) |

|------------------------------------|------------|

| Costes de recursos humanos         | 25.870     |

| Costes de herramientas de software | 69,05      |

| Costes de equipos informáticos     | 216,1      |

| Costes de fabricación              | 993,6      |

| Otros costes                       | 455        |

| Subtotal                           | 27.603,75  |

| I.G.I.C. (5%)                      | 1.380,19   |

| Presupuesto total                  | 28.983,9   |

# Diseño de un mezclador basado en convertidores de corriente en tecnología CMOS 0.18

Escuela de Ingeniería de Telecomunicación y Electrónica

Titulación: Sistemas electrónicos

Tutores: Dr. Francisco Javier del Pino Suárez D. Roberto Díaz Ortega Autor: D. Guillermo García Saavedra

Fecha: Abril 2010