## UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA UNIVERSITARIA DE INGENIERÍA TÉCNICA DE TELECOMUNICACIÓN

# Proyecto Fin de Carrera

DISEÑO DE UN MEZCLADOR PASIVO EN CMOS  $0.35~\mu m$  PARA UN RECEPTOR BASADO EN EL ESTÁNDAR IEEE 802.11a

TITULACIÓN: SISTEMAS ELECTRÓNICOS.

TUTORES: FRANCISCO JAVIER DEL PINO SUÁREZ.

AMAYA GOÑI ITURRI.

**AUTOR:** ROBERTO DÍAZ ORTEGA.

FECHA: ABRIL 2004.

# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA UNIVERSITARIA DE INGENIERÍA TÉCNICA DE TELECOMUNICACIÓN

# Proyecto Fin de Carrera

# DISEÑO DE UN MEZCLADOR PASIVO EN CMOS $0.35~\mu m$ PARA UN RECEPTOR BASADO EN EL ESTÁNDAR IEEE 802.11a

| Presidente: | Secretario: | Vocal: |

|-------------|-------------|--------|

|             |             |        |

| Tutores:    |             | Autor: |

|             | NOTA:       |        |

TITULACIÓN: SISTEMAS ELECTRÓNICOS.

TUTORES: FRANCISCO JAVIER DEL PINO SUÁREZ.

AMAYA GOÑI ITURRI.

**AUTOR:** ROBERTO DÍAZ ORTEGA.

FECHA: ABRIL 2004.

# **Agradecimientos**

Quiero empezar dándole mi agradecimiento más sincero a mi familia y en especial a mis padres, por darme durante todo este tiempo su apoyo y comprensión. Gracias a ellos he podido avanzar firme durante todo este tiempo, porque siempre han estado ahí para darme consejos a la hora de tomar mis propias decisiones.

Por otro lado quisiera agradecerle a Javier el estar en todo momento asesorándome y encauzando el desarrollo del proyecto. Sin lugar a dudas, sin su ayuda este proyecto no sería más que una mera ilusión. También quiero agradecer a Amaya y a Sunil los consejos que me han ido dando a lo largo del proyecto, enseñándome esos trucos que no vienen en ningún libro y que se aprenden tras años de experiencia y peleas diarias con el ordenador.

Y como no agradecer a todos mis compañeros de carrera y amigos, en especial a Rubén, que siempre han estado ahí, al pie del cañón, pendientes del desarrollo del proyecto y haciendo que llevara el proyecto de la manera más grata posible.

Sé que me queda gente en el tintero, pero es imposible en pocas líneas resumir tantos momentos pasados durante estos tres cortos pero intensos años. De corazón a todos MUCHAS GRACIAS.

# Indice General

| 1 Introducción                                       |    |

|------------------------------------------------------|----|

| 1.1 Introducción                                     | 1  |

| 1.2 Objetivos                                        | 3  |

| 1.3 Estructura de la memoria                         | 3  |

| 1.4 Peticionario                                     | 5  |

| 2 Sistemas de Radiofrecuencia                        |    |

| 2.1 Introducción                                     | 7  |

| 2.2 Características de los sistemas de RF            | 7  |

| 2.2.1 Ganancia (G)                                   | 8  |

| 2.2.2 Figura de ruido (NF)                           |    |

| 2.2.3 Punto de intercepción de tercer orden          |    |

| 2.2.4 Coeficiente de onda estacionaria               | 12 |

| 2.3 Características del estándar 802.11a             | 12 |

| 2.3.1 Canalización                                   | _  |

| 2.3.2 Modulación OFDM                                |    |

| 2.4 Especificaciones Técnicas                        | 19 |

| 2.4.1 Impedancia de la antena en emisión y recepción |    |

| 2.4.2 Rangos de temperatura en emisión y recepción   |    |

| 2.4.3 Nivel de potencia en transmisión               | 20 |

| 2.4.4 Mascara de espectro de salida                  |    |

| 2.4.5 Variación de la frecuencia de salida           | 21 |

| 2.4.6 Sensibilidad a la entrada                      |    |

| 2.4.7 Figura de ruido                                | 21 |

| 2.5 Tipos de receptores                              |    |

| 2.5.1 Receptor de conversión directa                 |    |

| 2.5.2 Receptor superheterodino de doble conversión   |    |

| 2.5.3 Receptor arquitectura Weaver modificada        | 24 |

| 3 M | lezclador de frecuencias                                      |    |

|-----|---------------------------------------------------------------|----|

|     | 3.1 Introducción                                              | 27 |

|     | 3.2 Teoría básica                                             | 27 |

|     | 3.3 Parámetros del mezclador                                  | 30 |

|     | 3.3.1 Ganancia de conversión                                  | 30 |

|     | 3.3.2 Figura de ruido                                         | 31 |

|     | 3.3.3 Linealidad                                              |    |

|     | 3.3.3.1 Rango dinámico                                        | 32 |

|     | 3.3.3.2 Punto de compresión                                   |    |

|     | 3.3.3.3 Distorsión de intermodulación de tercer orden         | 32 |

|     | 3.3.4 Aislamiento                                             |    |

|     | 3.4 Sistemas no lineales como mezcladores lineales            | 34 |

|     | 3.4.1 Mezclador de dos puertos: Dispositivo de ley cuadrática |    |

|     | 3.4.2 Ganancia de un mezclador de un solo transistor bipolar  |    |

|     | 3.5 Mezcladores basados en multiplicadores                    |    |

|     | 3.5.1 Mezclador simple balanceado                             | 39 |

|     | 3.5.2 Mezclador activo doble balanceado. Célula de Gilbert    |    |

|     | 3.5.3 Mezclador CMOS pasivo                                   |    |

| 4 E |                                                               |    |

| 4 E | studio de la tecnología                                       |    |

|     | 4.1 Introducción                                              |    |

|     | 4.2 Resistencias                                              |    |

|     | 4.2.1 Construcción                                            |    |

|     | 4.2.2 Resistencias en la tecnología S35D4 de AMS              |    |

|     | 4.3 Condensadores                                             |    |

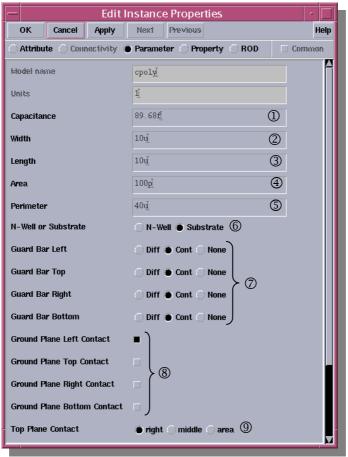

|     | 4.3.1 Construcción                                            |    |

|     | 4.3.2 Condensadores en la tecnología S35D4 de AMS             |    |

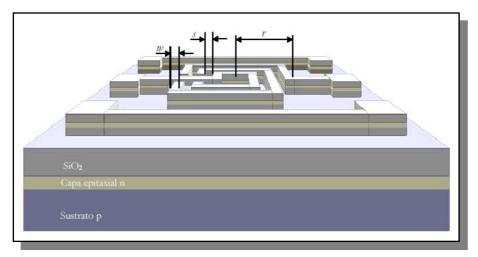

|     | 4.4 Bobinas                                                   |    |

|     | 4.4.1 Construcción                                            |    |

|     | 4.4.2 Funcionamiento                                          |    |

|     | 4.4.3 Modelo de la bobina                                     |    |

|     | 4.4.4 Bobinas en la tecnología S35D4 de AMS                   |    |

|     | 4.5 El transistor MOSFET                                      |    |

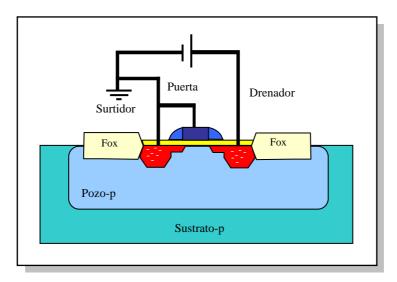

|     | 4.5.1 Construcción                                            |    |

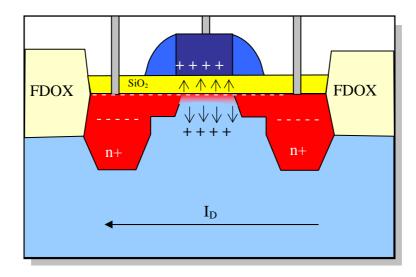

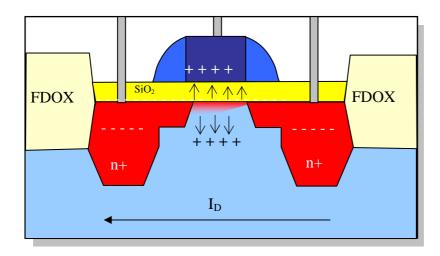

|     | 4.5.2 Funcionamiento                                          |    |

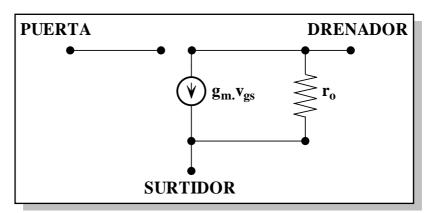

|     | 4.5.3 Modelo de baja frecuencia                               |    |

|     | 4.5.4 Modelo de alta frecuencia                               |    |

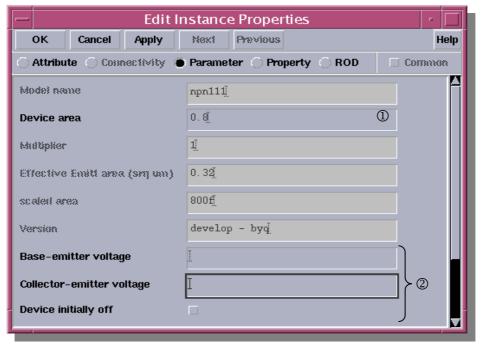

|     | 4.5.5 Transistores MOSFET en la tecnología S35D4 de AMS       |    |

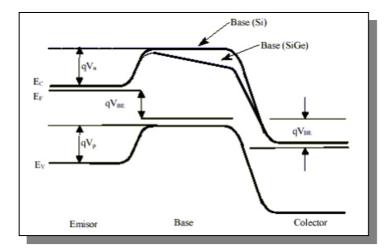

|     | 4.6 HBTs de SiGe                                              |    |

|     | 4.6.1 Estructura y principio de funcionamiento de los HBTs    |    |

| 5 D |                                                               |    |

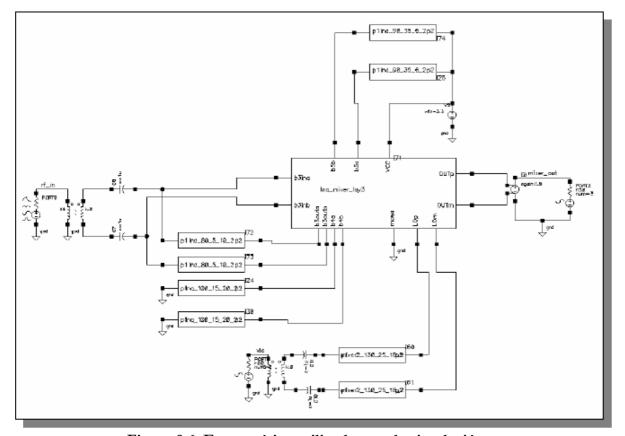

| J D | iseño del mezclador pasivo 5.1 Introducción                   | 75 |

|     | 5.1 Introducción 5.2 Topología del circuito                   |    |

|     |                                                               |    |

|     | 5.3 Polarización del circuito                                 |    |

|     | 5.4 Dimensionado del circuito                                 |    |

|     | 5.5 Adaptación de impedancia en las entradas                  |    |

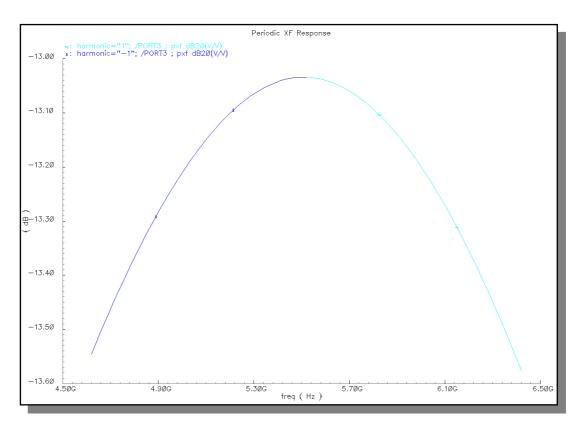

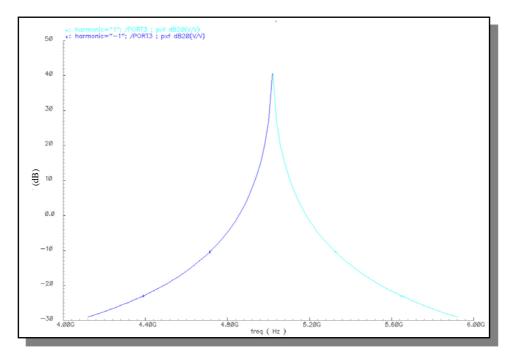

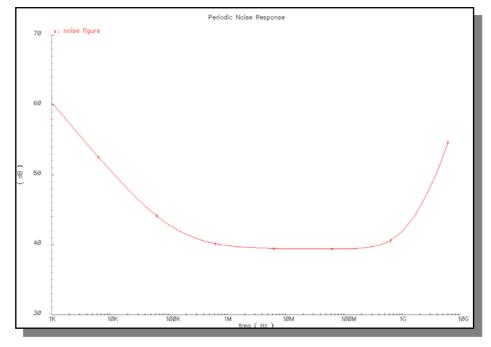

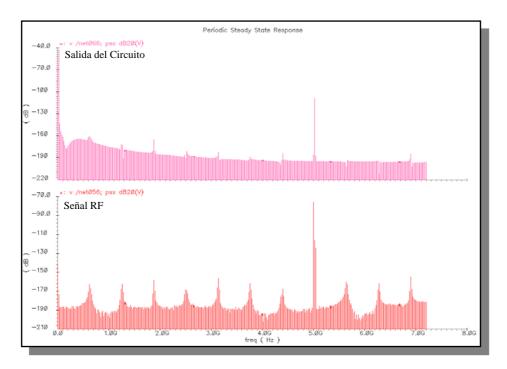

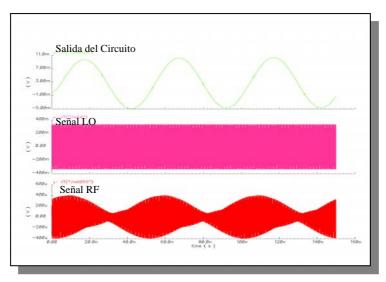

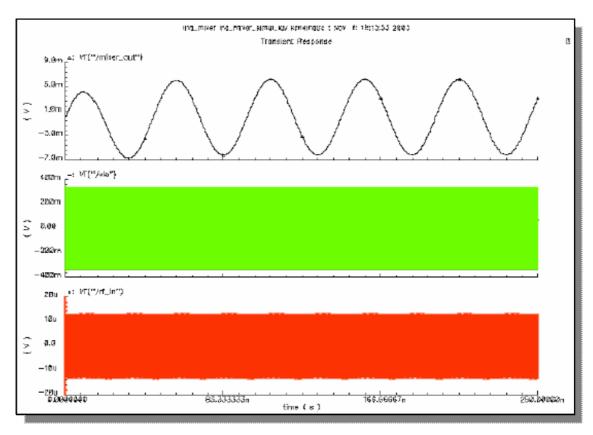

|     | 5.6 Simulación del diseño                                     | 82 |

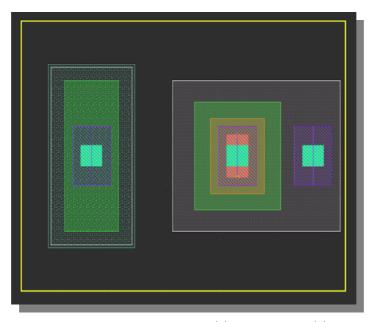

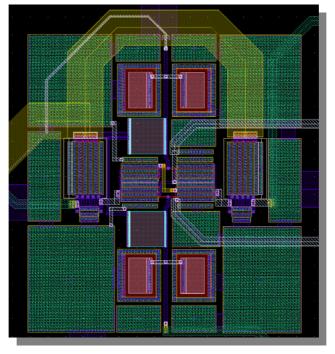

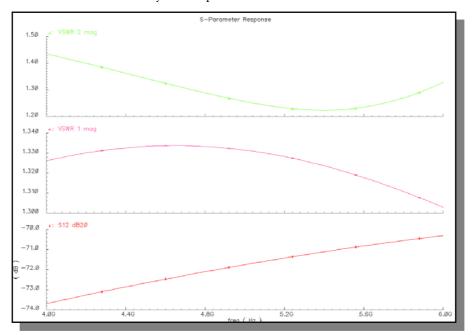

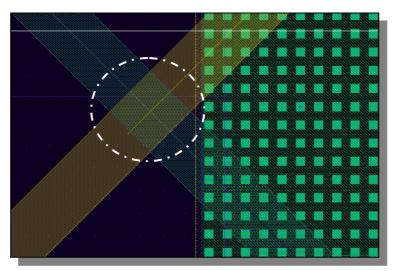

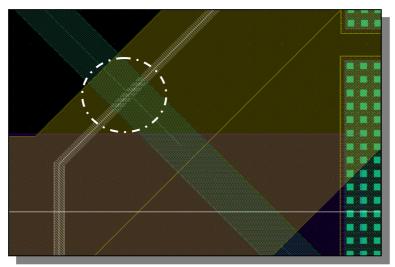

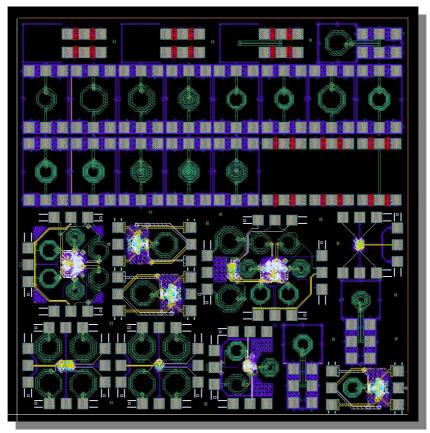

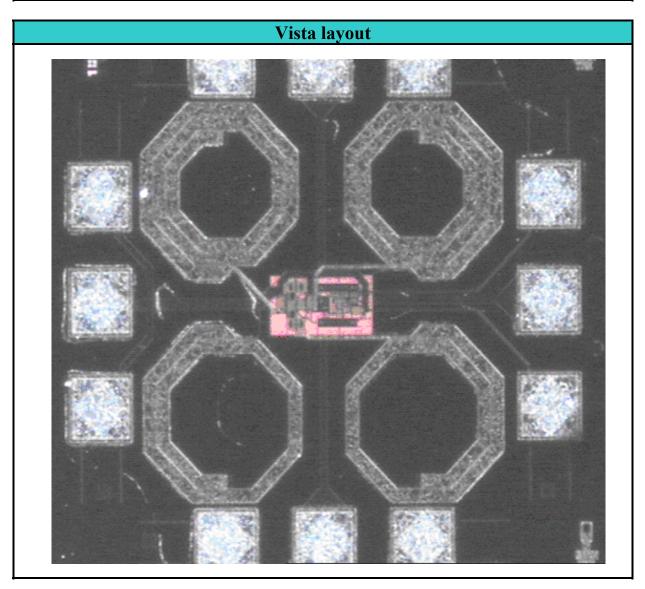

| 5.7 Layout del mezclador                 | 84  |

|------------------------------------------|-----|

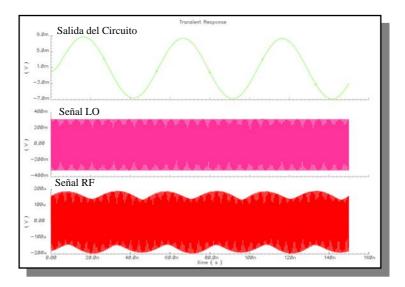

| 5.8 Simulaciones post-layout             | 85  |

| 6 Diseño del amplificador operacional    |     |

| 6.1 Introducción                         | 89  |

| 6.2 Etapa de entrada del amplificador    |     |

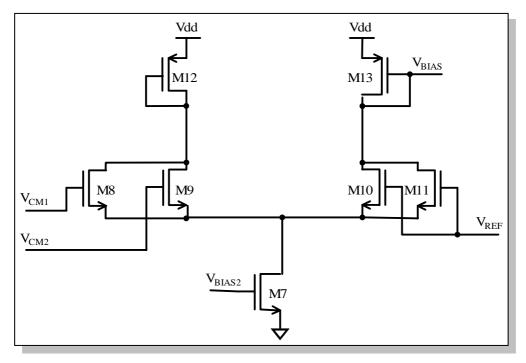

| 6.3 Diseño del CMFB                      |     |

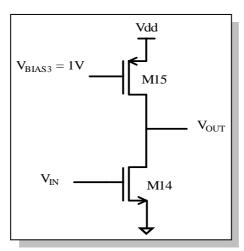

| 6.4 Diseño de la etapa de salida         |     |

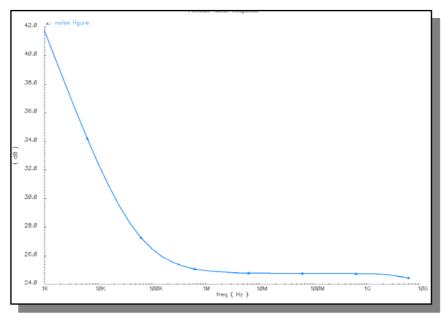

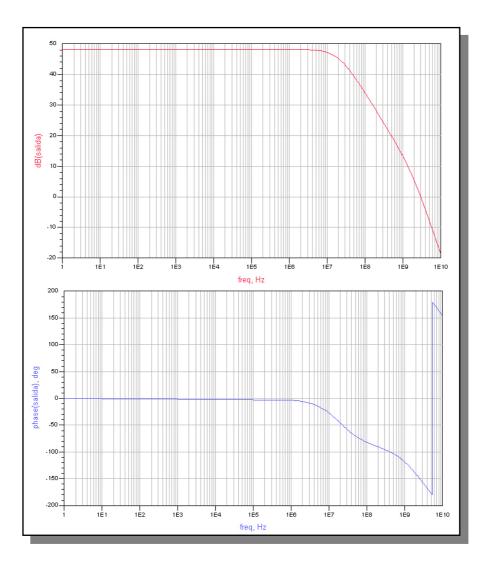

| 6.5 Simulación del amplificador          |     |

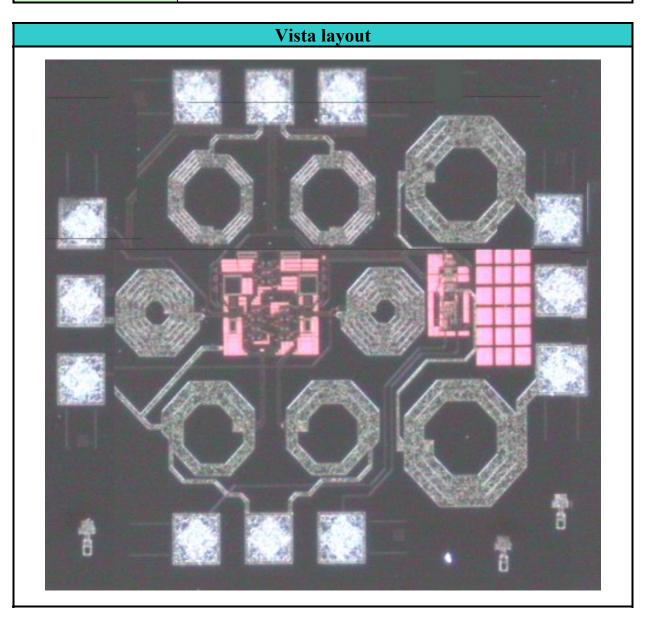

| 6.6 Layout del amplificador              |     |

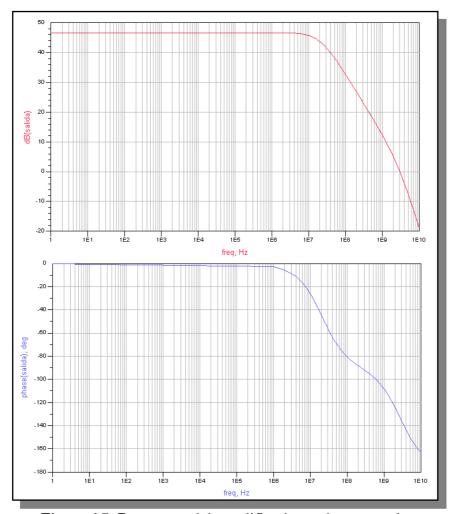

| 6.7 Simulaciones post-layout             |     |

| 7 Mezclador con etapa de amplificación   |     |

| 7.1 Introducción                         | 101 |

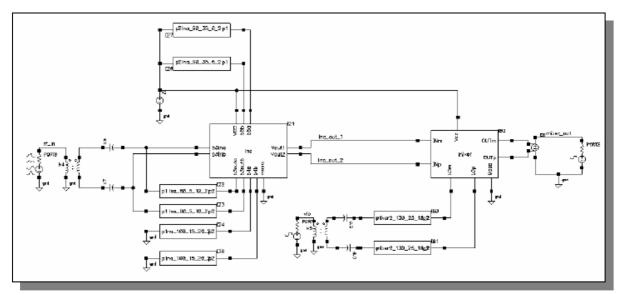

| 7.2 Simulación del conjunto              |     |

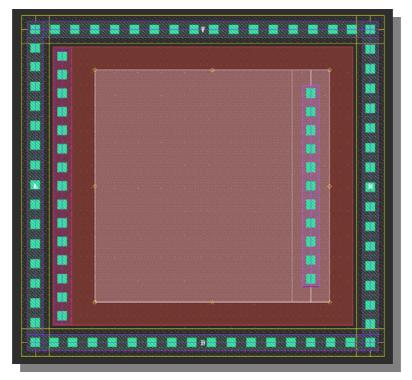

| 7.3 Layout del conjunto                  |     |

| 7.4 Simulaciones Post-layout             |     |

| 7.5 Acoplamiento de señales              |     |

| 0 I na a na ai i na ann ai i n           |     |

| 8 Integración en una cadena de recepción | 111 |

| 8.1 Introducción                         |     |

| 8.2 Consideraciones previas              |     |

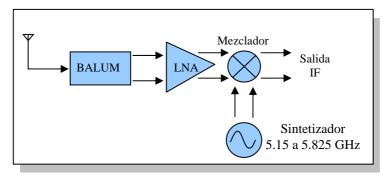

| 8.3 Amplificador de bajo ruido (LNA)     |     |

| 8.3.1 Especificaciones de LNAs           |     |

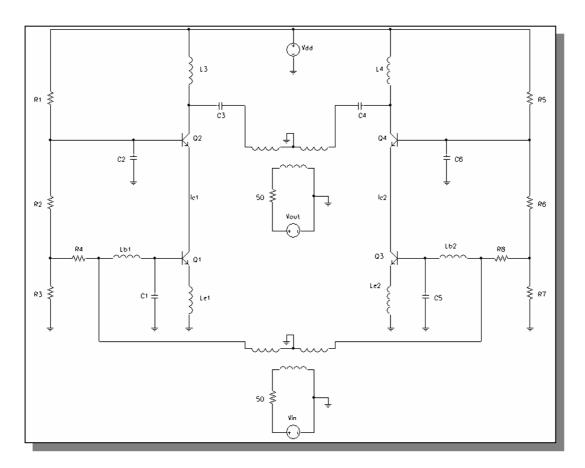

| 8.3.2 Esquemático del LNA                |     |

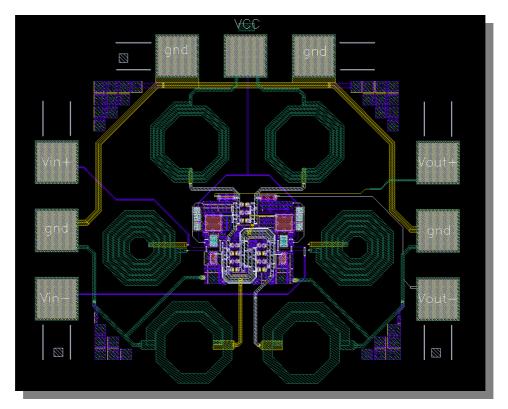

| 8.3.3 Layout del LNA                     |     |

| 8.3.4 Prestaciones del LNA               |     |

| 8.4 Conexionado LNA-Mezclador            |     |

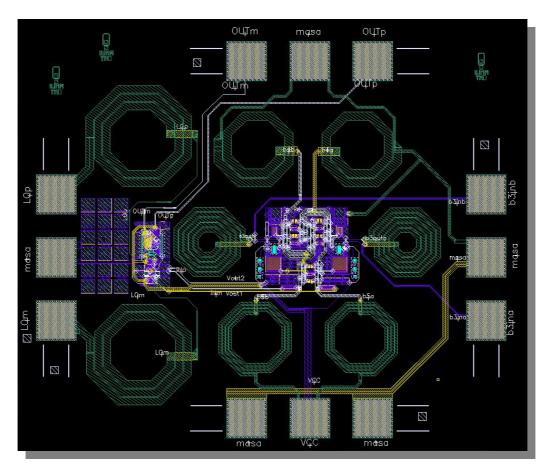

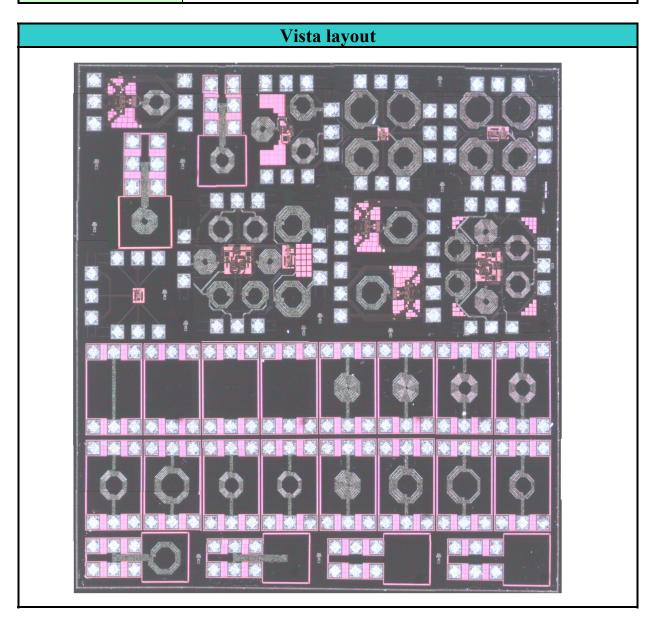

| 8.5 Layout del sistema                   |     |

| 8.6 Simulaciones post-layout             |     |

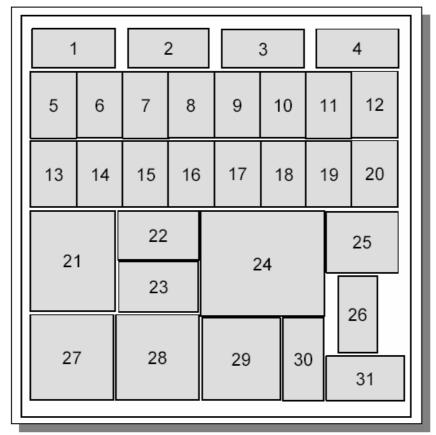

| 8.7 RUN de fabricación                   | 119 |

| 9 Conclusiones                           |     |

| 9.1 Introducción                         |     |

| 9.2 Mezclador pasivo                     |     |

| 9.3 Mezclador con etapa de amplificación |     |

| 9.4 Conclusiones                         | 126 |

| Presupuesto                              |     |

| Introducción                             | 129 |

| Costes debidos a recursos humanos        | 129 |

| Costes de Ingeniería                     | 130 |

| Costes de Amortización                   |     |

| Costes de Fabricación                    | 131 |

| Otros costes                             | 131 |

| Coste Total                              | 132 |

| Bibliografia                             | 133 |

| Anexo: Fotografías de los diseños        | 137 |

# **CAPITULO 1**

# Introducción

## 1.1 Introducción

En los últimos años las redes inalámbricas (WLAN, Wireless Local Area Network) han ganado muchos adeptos y popularidad en mercados como hospitales, fábricas, tiendas de autoservicio, pequeños negocios, universidades, etc. Las redes inalámbricas permiten a los usuarios el acceso a información y recursos en tiempo real sin necesidad de estar físicamente en un determinado lugar. Con WLANs la red por sí misma es móvil y elimina la necesidad de usar cables y establece nuevas aplicaciones añadiendo flexibilidad a la red y, lo que es más importante, incrementa la productividad y eficiencia en las actividades diarias de la empresa. Un usuario dentro de una red inalámbrica puede transmitir y recibir voz, datos y video dentro de edificios, entre edificios o campus universitarios e inclusive sobre áreas metropolitanas.

Muchos de los fabricantes de ordenadores y equipos de comunicaciones como PDAs (Personal Digital Assistants), módems, microprocesadores inalámbricos, lectores de punto de venta y otros dispositivos están introduciendo aplicaciones en soporte a las comunicaciones

inalámbricas. Las nuevas posibilidades que ofrecen las WLANs son permitir una fácil incorporación de nuevos usuarios a la red, ofrecer una alternativa de bajo coste a los sistemas cableados, y posibilitar el acceso a cualquier base de datos o cualquier aplicación localizada dentro de la red.

Figura 1.1. Ejemplo de sistemas WLAN.

Las ventajas de las WLANs sobre las redes cableadas se pueden resumir en los siguientes términos:

- Movilidad: Las redes inalámbricas pueden proporcionar a los usuarios de una LAN acceso a la información en tiempo real en cualquier lugar dentro de la organización. Esta movilidad incluye oportunidades de productividad y servicio que no es posible con una red cableada.

- Simplicidad y rapidez en la instalación: La instalación de una red inalámbrica es rápida y fácil. Además elimina la necesidad de tirar cable a través de paredes y techos.

- Flexibilidad en la instalación: La tecnología inalámbrica permite a la red ir donde la cableada no puede ir.

- Coste de propiedad reducido: Mientras que la inversión inicial requerida para una red inalámbrica puede ser más alta que el coste en hardware de una LAN cableada, la inversión de toda la instalación y el coste del ciclo de vida puede ser significativamente inferior. Los beneficios y costes a largo plazo son superiores en ambientes dinámicos que requieren acciones y movimientos frecuentes.

- Escalabilidad: Los sistemas de WLANs pueden ser configurados en una variedad de topologías para satisfacer las necesidades de las instalaciones y aplicaciones específicas. Las configuraciones son muy fáciles de cambiar y además es muy fácil la incorporación de nuevos usuarios a la red.

Como se ha comentado las redes inalámbricas están sufriendo un gran auge dentro de las tecnologías de la información, por está razón, es un campo donde se está invirtiendo gran cantidad de fondos en procesos de investigación y desarrollo.

# 1.2 Objetivos

El principal objetivo de este proyecto fin de carrera es el desarrollo de un mezclador pasivo en tecnología SiGe 0.35 µm para el estándar de comunicaciones IEEE802.11a. Este proyecto se engloba dentro de otro proyecto de mayor envergadura desarrollado por el Instituto Universitario de Microelectrónica Aplicada (IUMA), en el que se pretende diseñar un receptor de conversión directa para el estándar 802.11a.

Para el diseño del mezclador inicialmente se llevará a cabo un estudio teórico para comprender los parámetros básicos de los sistemas de radiofrecuencia, el funcionamiento de los mezcladores y el estudio de la tecnología a emplear.

Una vez completado el estudio teórico se procede a la elaboración del diseño. Para la elaboración del mismo se seguirá el flujo de diseño tipico en un sistema integrado, es decir, se partirá del diseño a nivel de esquemático realizado con ADS (*Advanced design System*) y una vez completado el diseño a nivel de esquemático se procederá al diseño a nivel de *layuot* en Cadence. Es digno de mención que al tratarse de un sistema analógico el diseño a nivel de *layout* debe realizarse enteramente a mano ya que no se dispone de células estándar que faciliten el diseño del mismo (diseño *full-custom*).

#### 1.3 Estructura de la memoria

La memoria de este proyecto está dividida de la siguiente forma:

En el **Capítulo 2** se comienza realizando un estudio teórico de los parámetros más importantes que caracterizan a los sistemas de radiofrecuencia. En este capítulo quedarán definidos términos como ganancia, linealidad,... etc. Por otro lado en el Capítulo 2 se realiza también un estudio general del estándar IEEE802.11a para conocer el marco en el que se englobará el mezclador diseñado. Finalmente en este capítulo se compararán las diferentes

arquitecturas de receptores que se utilizan en sistemas de radiofrecuencia, exponiendo tanto las ventajas como inconvenientes de las mismas.

Conocidos ya los fundamentos de los sistemas de radiofrecuencia, en el **Capítulo 3** se realizará un estudio en profundidad de los mezcladores de frecuencia. El capítulo comienza con la definición de los parámetros que caracterizan a los mezcladores para proceder después al estudio de las diferentes topologías de mezcladores típicamente usadas en sistemas de de radiofrecuencia integrados.

Llegados a este punto ya el objetivo del proyecto puede considerarse englobado dentro de su marco de trabajo. Por esta razón, en el **Capítulo 4** se procederá al estudio de la tecnología SiGe 0,35 µm de la fundidora AMS. Para ello se realizará un pequeño estudio a nivel tanto de construcción como de funcionamiento de cada uno de los componentes que proporciona la tecnología. Así mismo se analizarán las diferentes opciones que proporciona el Kit de diseño de la tecnología en la herramienta de diseño Cadence.

En el **Capítulo 5** se procede a abordar el diseño del mezclador pasivo. El trabajo comienza con el diseño del mezclador pasivo tanto a nivel de esquemático como a nivel de *layout*. El diseño del mismo será realizado de una forma metódica, partiendo de un esquema genérico para luego ir ajustando los valores hasta obtener los resultados óptimos.

Debido a que se ha diseñado un mezclador pasivo y este presenta pérdidas en la conversión, en el **Capítulo 6** se realizará el diseño de un amplificador operacional totalmente diferencial que será colocado en la salida del mezclador. Al igual que en el caso del mezclador pasivo, en el diseño del amplificador se partirá del esquemático para terminar con el diseño a nivel de *layout*.

En este punto del proyecto, ya se encuentran los dos bloques diseñados independientemente (el mezclador pasivo y el amplificador operacional). En el **Capítulo 7** se procede a la unión de ambos circuitos para comprobar que el sistema funciona de acuerdo a las especificaciones esperadas inicialmente. La comprobación del funcionamiento de la unión de ambos bloques se realizará inicialmente a nivel de esquemático para luego proceder a la implementación del *layout* y comprobar su correcto funcionamiento.

Concluido el diseño del mezclador, en el **Capítulo 8** se procederá a la integración del bloque diseñado dentro de la cadena de recepción. El mezclador será integrado junto con un amplificador de bajo ruido diseñado por Jesús Rubén Pulido Medina [1], formando ambos sistemas la etapa analógica del receptor de conversión directa para el estándar 802.11a. Como los sistemas desarrollados serán fabricados, en el capítulo 8 también se podrá apreciar el proceso de preparación de los sistemas para su envío a fábrica, dando con esto por finalizado el proceso de diseño.

Por último, en el **Capítulo 9** se analizarán los resultados obtenidos a lo largo del proyecto, comparando el sistema desarrollado con otros sistemas de características similares y evaluando como se han ido alcanzando una serie de metas y objetivos a lo largo de todo el proyecto.

Finalizadas las conclusiones se realizará el **Presupuesto**, donde se detallarán los gastos derivados del proyecto tanto de los sistemas *hardware / software* como gastos tanto de fabricación y de recursos humanos.

Finalmente al final del proyecto se recoge un **Anexo** con las fotografías de los circuitos fabricados.

## 1.4 Peticionario

Actúa como peticionario para este proyecto fin de carrera, la división de Tecnología Microelectrónica (TME) del Instituto Universitario de Microelectrónica Aplicada (IUMA).

# **CAPITULO 2**

# Sistemas de radiofrecuencia

#### 2.1 Introducción

Conocidos los objetivos generales del proyecto y el marco de trabajo donde será englobado, en este capítulo se pretende profundizar en los sistemas de radiofrecuencia y en el estándar de comunicaciones IEEE802.11a.

La comprensión de los diversos parámetros expuestos en este capítulo es fundamental para el desarrollo del proyecto, ya que, sin ello es imposible determinar y valorar las características de los sistemas de radiofrecuencia.

# 2.2 Características de los sistemas de RF

Los conceptos tratados en este apartado son comunes a la mayoría de los bloques que componen un sistema de RF y, por tanto, serán de utilidad más adelante para el estudio del sistema donde irá incluido el mezclador.

## 2.2.1 Ganancia (G)

La ganancia de un circuito determina la relación entre las amplitudes de la señal de salida y la de entrada. La ganancia en tensión se puede expresar mediante la ecuación 2.1.

$$G = \frac{V_{salida}}{V_{entrada}}$$

(Ec. 2.1)

Siendo su valor en decibelios el mostrado en la ecuación 2.2.

$$G(dB) = 20 \log \left( \frac{V_{salida}}{V_{entrada}} \right)$$

(Ec. 2.2)

Cuando se trabaja con sistemas de radiofrecuencia no se suele hablar en términos de tensión sino en términos de potencia. Por tanto, de ahora en adelante se hablará de la ganancia en potencia de una etapa. Para medir la ganancia en potencia de un circuito se utilizan los parámetros S, más concretamente el parámetro  $S_{21}$ .

## 2.2.2 Figura de ruido (NF)

En un sistema de RF, incluso cuando no hay señal a la entrada, a la salida se puede medir una pequeña tensión. A esta pequeña cantidad de potencia de salida se la suele denominar potencia de ruido. La potencia de ruido total a la salida es la suma de la potencia de ruido a la entrada amplificada más la potencia de ruido a la salida producida por el sistema. La figura de ruido describe cuantitativamente la respuesta frente al ruido de un sistema. Se define como la relación entre la potencia total de ruido disponible a la salida del sistema y la potencia de ruido disponible a la salida debido al ruido térmico, siendo éste la única señal a la entrada. La figura de ruido se expresa como muestra la ecuación 2.3.

$$NF = \frac{P_{N0}}{P_{Ni} \cdot G_A}$$

(Ec. 2.3)

donde  $P_{N_0}$  es la potencia total de ruido disponible a la salida del sistema,  $P_{N_i}=k\ T\ B$  es la potencia de ruido disponible en un ancho de banda B (k y T son respectivamente la constante de Boltzmann y la temperatura absoluta) y  $G_A$  es la ganancia de potencia disponible definida

como la relación entre la potencia de señal disponible a la salida  $(P_{So})$  y la potencia de señal disponible a la entrada  $(P_{Si})$ . Sustituyendo  $G_A$  por dicha relación obtenemos que la figura de ruido viene dada por:

$$NF = \frac{P_{Si} / P_{Ni}}{P_{S0} / P_{N0}} = \frac{SNR_i}{SNR_0}$$

(Ec. 2.4)

donde  $SNR_i$  y  $SNR_o$  son, respectivamente, las relaciones señal a ruido medidas a la entrada y a la salida. De esta forma, la figura de ruido es una medida de cuanto se degrada la SNR al pasar la señal a través del circuito. Si el circuito no añadiese ruido, entonces  $SNR_i = SNR_o$ , independientemente del valor de la ganancia del mismo. Esto es debido a que tanto la señal como el ruido son amplificadas (o atenuadas) por el mismo factor. Por lo tanto, la figura de ruido de un circuito sin ruido es igual a 1 aunque por lo general la figura de ruido suele ser mayor que la unidad.

Para dos etapas en cascada la figura de ruido viene dada por la ecuación 2.5.

$$NF = NF_1 + \frac{NF_2 - 1}{G_{A1}}$$

(Ec. 2.5)

donde  $NF_1$  y  $NF_2$  son las figuras de ruido de ambas etapas por separado y  $G_{A1}$  es la ganancia de la primera etapa. La ecuación 2.5 muestra que la primera etapa es la que más contribuye al ruido total ya que su figura de ruido se suma directamente a la del sistema y la de la segunda etapa es atenuada por la ganancia de la primera etapa. En consecuencia, la primera etapa de un sistema de radiofrecuencia (LNA) debe tener una baja figura de ruido y una alta ganancia.

# 2.2.3 Punto de Intercepción de Tercer orden (IP3)

El punto de intercepción de tercer orden es una medida de la linealidad de un circuito. Cuando dos señales con diferentes frecuencias ( $\omega_1$  y  $\omega_2$ ) son aplicadas a un sistema no lineal, la salida exhibe, en general, términos armónicos de  $\omega_1$  y  $\omega_2$ , y también términos de frecuencias que siguen la ley  $m\omega_1\pm n\omega_2$  los cuales se producen por mezcla de los anteriores. A estos se les denomina productos de intermodulación (IM). Se define el orden de cada producto como la suma de m+n. Los productos de intermodulación se pueden dar referidos a la salida (OIM) o a la entrada (IIM) y se suelen expresar en dBm. Ambos valores están relacionados a través de la

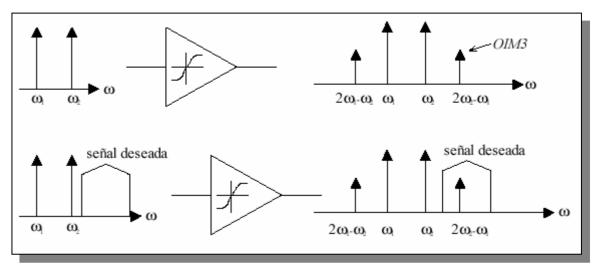

ganancia del circuito (OIM = IIM + G dB). Los productos de intermodulación más importantes son los de tercer orden ( $2\omega_1 - \omega_2$  y  $2\omega_2 - \omega_1$ ), desechando el término de continua que normalmente no condiciona la información y los términos superiores por considerarlos de magnitud muy pequeña o estar alejados de la frecuencia de la portadora. En la Figura 2.1 se muestra como los productos de intermodulación pueden caer dentro del canal deseado produciendo fuertes interferencias.

Figura 2.1. Efecto de la intermodulación.

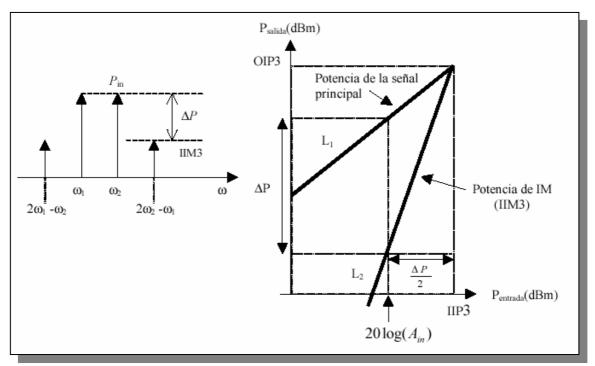

La corrupción de las señales debido a la intermodulación de tercer orden de dos interferencias cercanas es algo común y perjudicial. Para determinar cuánto es esta degradación se define una figura de mérito llamada punto de intercepción de tercer orden *IP3* (third intercept point) el cual se puede dar referido a la entrada (*IIP3*) o a la salida (*OIP3*). El *IIP3* se calcula como:

$$IIP3_{dBm} = \frac{\Delta P_{dB}}{2} + Pin_{dBm}$$

(Ec. 2.6)

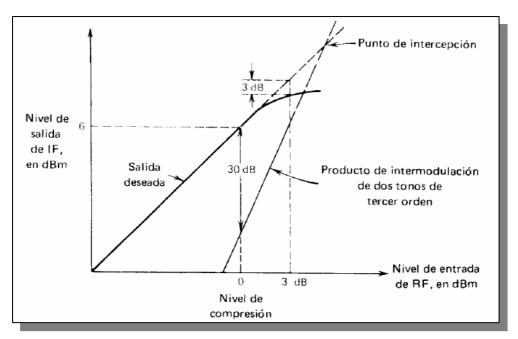

donde  $P_{in}$  es la potencia de la señal interferente (tono) y  $\Delta P_{dB}$  es la diferencia de potencia entre la señal interferente y el IIM3. En la Figura 2.2 se muestra la interpretación gráfica de ambas cantidades así como del IP3. Para determinar gráficamente el IP3 se representa la salida deseada y la salida del producto de intermodulación de tercer orden en función del nivel RF a la entrada. El IP3 es la intercepción extrapolada de esas dos curvas. En general cuanto mayor sea el IP3 más lineal será el circuito.

Figura 2.2. Medida del IP3 referido a la entrada.

Así, el IIP3 lo se puede determinar a partir de la ecuación 2.6 mediante la expresión 2.7.

$$IIP3_{dBm} = \frac{Pin_{dBm} - IIM3}{2} + Pin_{dBm}$$

(Ec.2.7)

Por lo que el IIM3 viene dado por la ecuación 2.8.

$$IIM \, 3_{dBm} = Pin_{dBm} - 2(IIP \, 3_{dBm} - Pin_{dBm})$$

$IIM \, 3_{dBm} = 3Pin_{dBm} - 2IIP \, 3_{dBm}$

(Ec. 2.8)

Es digno de mención que el representar la linealidad de un componente mediante el uso del *IM3* presenta el inconveniente que debe ser especificada la potencia de entrada. Con el *IP3* se salva este problema. El *IIM3* y el *OIM3* son medidas absolutas de la potencia de los productos de intermodulación referidos a la entrada y a la salida, mientras que el *IIP3* y el *OIP3* son medidas relativas a los valores de los tonos de *test* utilizados. De esta forma, haciendo uso del *IIP3* o el *OIP3* se pueden comparar distintos sistemas cuyas medidas se hayan hecho con diferentes tonos y por ello es la forma más habitual de caracterizar los efectos de la intermodulación.

#### 2.2.4 Coeficiente de onda estacionario (VSWR)

Está relacionado con el coeficiente de reflexión ( $\Gamma_L$ , relación entre la onda incidente y la reflejada) según la ecuación 2.9 e indica una medida cuantitativa de la adaptación del circuito a la entrada ( $VSWR_1$ ) o a la salida ( $VSWR_2$ ). En la ecuación 2.9,  $Z_0$  es la impedancia característica de una línea de transmisión y  $Z_L$  es la impedancia de carga. Como se puede observar, si terminamos la línea de transmisión con una impedancia igual a su impedancia característica, el coeficiente de reflexión será cero, lo cual equivale a un VSWR de valor 1. El hecho de que se utilice más el coeficiente de onda estacionario que el coeficiente de reflexión se debe a que es más fácil de medir (no es más que la relación entre la tensión de pico máxima y mínima a lo largo de una línea sin pérdidas).

$$|\Gamma_L| = \left| \frac{Z_L - Z_0}{Z_L + Z_0} \right| = \frac{VSWR - 1}{VSWR + 1}$$

(Ec. 2.9)

## 2.3 Características del Estándar IEEE 802.11a

Este estándar se define para redes inalámbricas en la banda de 5 GHz. En la Tabla 2.1 se puede ver las especificaciones básicas de diferentes estándares de WLANs.

Para reducir errores el estándar permite la reducción de la tasa de transferencia de información. Así el 802.11a tiene 7 velocidades de transferencia de datos posibles (48, 36, 24, 18, 12, 9 y 6 Mbps). La velocidad máxima permisible de 54 Mbits/s sólo es disponible en un ambiente libre de interferencias y a muy corta distancia.

Tabla 2.1. Distintas especificaciones para WLANs

| Estándar  | Velocidad<br>máxima | Modulación | Ancho de banda de canal | Frecuencia |

|-----------|---------------------|------------|-------------------------|------------|

| 802.11a   | 54 Mbps             | OFDM       | 20 MHz                  | 5.0 GHz    |

| 802.11b   | 11 Mbps             | DSSS       | 25 MHz                  | 2.4 GHz    |

| 802.11g   | 54 Mbps             | OFDM/DSSS  | 25 MHz                  | 2.4 GHz    |

| HomeRF2   | 10 Mbps             | FHSS       | 5 MHz                   | 2.4 GHz    |

| HiperLAN2 | 54 Mbps             | OFDM       | 25 MHz                  | 5.0 GHz    |

| 5-UP      | 108 Mbps            | OFDM       | 50 MHz                  | 5.0 GHz    |

#### 2.3.1 Canalización

La frecuencia central de canal es múltiplo de 5 MHz. La relación entre la frecuencia central y el número del canal viene dada por la ecuación 2.10.

Frecuencia central del cada canal =  $5 \text{ GHz} + 5 \text{ MHz} \cdot n_{ch}$  (Ec. 2.10)

Existen 12 canales, los cuales se puede observar en la Tabla 2.2.

Tabla 2.2 Plan de frecuencias para IEEE 802.11a

| Banda (GHz)            | Número de canales operativos (nch) | Frecuencia central del cada canal (MHz) |

|------------------------|------------------------------------|-----------------------------------------|

|                        | 36                                 | 5180                                    |

| U-NII Banda            | 40                                 | 5200                                    |

| inferior (5.15-5-25)   | 44                                 | 5220                                    |

|                        | 48                                 | 5240                                    |

|                        | 52                                 | 5260                                    |

| U-NII Banda            | 56                                 | 5280                                    |

| media (5.25-5.35)      | 60                                 | 5300                                    |

|                        | 64                                 | 5320                                    |

|                        | 149                                | 5745                                    |

| U-NII Banda            | 153                                | 5765                                    |

| superior (5.725-5.825) | 157                                | 5785                                    |

|                        | 161                                | 5805                                    |

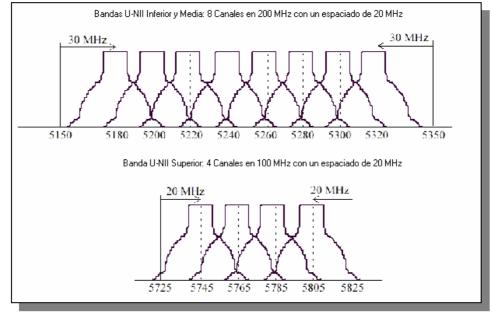

El ancho de banda total es de 300 MHz divididos en tres bloques de 100 MHz (5.15 a 5.25 GHz, 5.25 a 5.35 GHz y 5.725 a 5.825 GHz). En la Figura 2.3 se puede observar el plan de frecuencias.

Figura 2.3. Canalización para IEEE 802.11a.

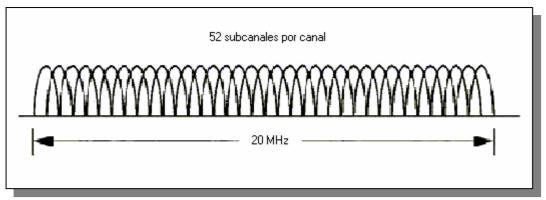

Cada canal tiene un ancho de 20 MHz, y ésta a su vez está divido en 52 sub-canales, cada uno de 300 KHz. 48 de esos canales son para datos y 4 son canales para frecuencias piloto. Esta subdivisión de canales es útil para adaptar diferentes tasas de bits tal como se verá en el siguiente apartado.

Figura 2.4. 52 subcanales del IEEE.802a.

#### 2.3.2 Modulación OFDM

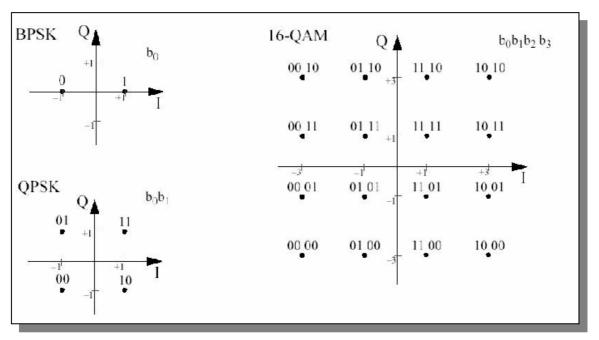

La versión de OFDM que utiliza el estándar 802.11a combina las modulaciones BPSK, QPSK y QAM en función de la tasa de bits elegida, tal como se ve en la Tabla 2.3.

Tabla 2.3 Tipos de Modulaciones del estándar 802.11a

| Tasa de bits<br>transmitida<br>(Mbits/s) | Tasa de bits transmitida por cada subcanal (kbits/s) | Modulación |

|------------------------------------------|------------------------------------------------------|------------|

| 6                                        | 125                                                  | BPSK       |

| 9                                        | 188                                                  | BPSK       |

| 12                                       | 250                                                  | QPSK       |

| 18                                       | 375                                                  | QPSK       |

| 24                                       | 500                                                  | 16-QAM     |

| 36                                       | 750                                                  | 16-QAM     |

| 48                                       | 1000                                                 | 64-QAM     |

| 54                                       | 1125                                                 | 64-QAM     |

La OFDM es una FDM (multiplexación por división en frecuencia) en la que los canales contiguos se solapan pero no se interfieren los unos a los otros debido a la ortogonalidad de las portadoras.

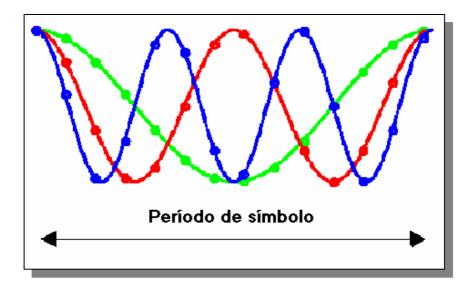

La OFDM divide una cadena de datos de alta velocidad en 48 sub-cadenas de baja velocidad que se transmiten en paralelo. Cada sub-cadena se modula (BPSK, QPSK, 16-QAM ó 64 QAM) con una sub-portadora con frecuencia diferente. Las frecuencias de las sub-portadoras son elegidas de manera que sean ortogonales, es decir, que en un periodo de símbolo quepan un número entero de ciclos. En la Figura 2.8 se puede observar este caso para tres sub-portadoras.

Figura 2.5. Ejemplo de tres portadoras ortogonales.

Las tres señales son ortogonales entre sí, es decir cumplen la ecuación 2.11.

$$\int_{0}^{T} \sin\left(\frac{2\pi kt}{T}\right) \sin\left(\frac{-2\pi lt}{T}\right) dt = 0, \qquad k \neq 1$$

(Ec. 2.11)

Los datos se modular variando la fase o la amplitud de cada sub-portadora dependiendo del tipo de modulación (BPSQ, QPSK, 4QAM y 16QAM). Cada sub-portadora se puede modular con un tipo de modulación distinta.

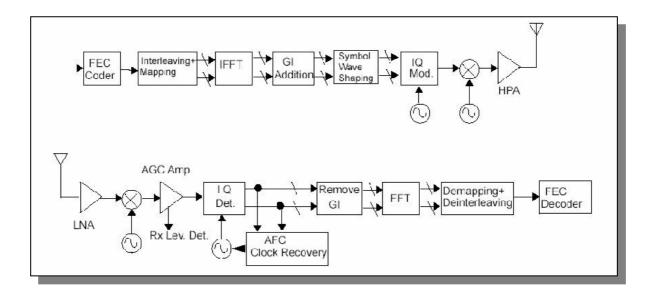

En la Figura 2.6 se puede observar un esquema de bloques genérico para el transmisor y para el receptor.

Figura 2.6. Esquema de bloques del transmisor y receptor para la capa física de OFDM.

El codificador FEC (Forward Error Correction) expande los bits sobre el ancho de banda del canal y aumenta la redundancia de la información a transmitir para poder corregir errores en el receptor. Se suele utilizar para éste propósito un codificador convolucional.

El *interleaving* modifica la cadena de datos para evitar secuencias de "1" o "0" seguidas (evita errores debidos al *burst*), para ello la cadena de datos se divide en grupos de  $N_{CBPS}$  bits, dentro de cada grupo se produce un intercambio en los bits en dos permutaciones.

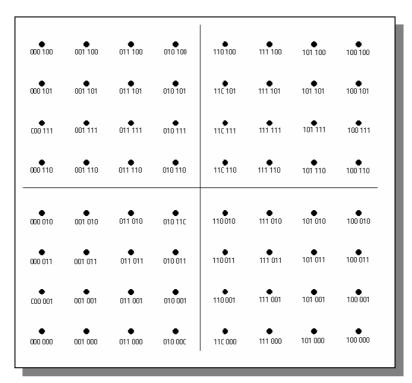

En el mapeo (*mapping*) la cadena de datos se divide en grupos de N<sub>BPSC</sub> bits (1, 2, 4 o 6) y se convierten en números complejos dependiendo de la tasa de bits elegida. Cada grupo se convierte en un número complejo acorde a la modulación (Figuras 2.7 y 2.8). Por ejemplo, si se elige una tasa de bits de 24 Mbits/s se mapean los datos con una constelación 16-QAM. La cadena de números complejos se divide en grupos de 48 números complejos. Cada grupo se mapea a cada una de las subportadoras (48).

A las 52 (48+4) sub-portadoras se le aplica la *IFFT* (transformada inversa de Fourier rápida). La *IFFT* suma todas las cadenas de datos y realiza la modulación y el multiplexado en un paso. Este procesado de señal sustituye los bancos de moduladores *I/Q* que hubieran sido necesarios de haberlas realizado de forma tradicional. Esta señal pasa por un convertidor paralelo-serie.

Figura 2.7. Constelaciones para BPSK, QPSK y 16-QAM.

Figura 2.8. Constelación para 64-QAM.

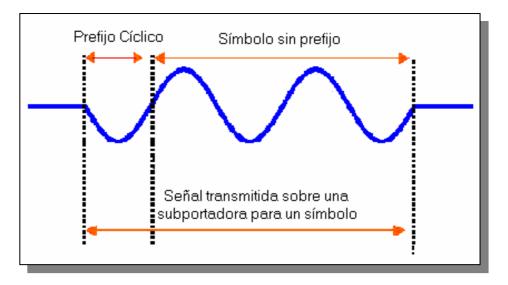

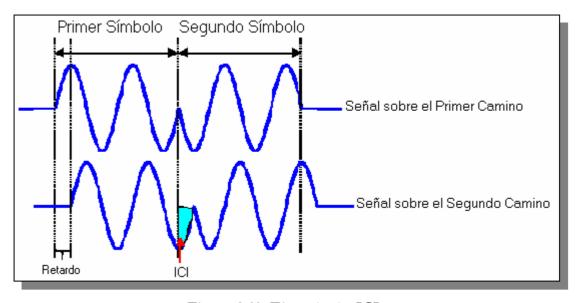

Una vez pasada la señal anterior por el convertidor paralelo serie se le añade el GI (guard interval) o también llamado cyclic prefix. En este paso se añade una banda de guarda sobre cada símbolo para reducir la interferencia entre símbolos (ISI) y entre portadoras (ICI). En la figura 2.9 se ve un ejemplo de agregación del GI o Cyclic Prefix en un símbolo, por otro lado, en la figura 2.10 se observa como aparece la ICI si no se tiene en cuenta el retardo introducido con el GI

Figura 2.9. Ejemplo de agregación de GI o Cyclic Prefix en cada símbolo.

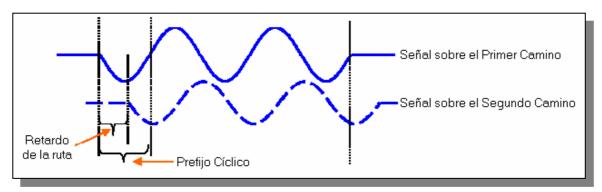

Cuando la misma señal llega al receptor por diferentes caminos y el retardo de la señal es menor que el GI no se produce ISI ni ICI tal como se ve en la Figura 2.11

Figura 2.10. Ejemplo de ICI.

Figura 2.11. Efecto del GI o Cyclic Prefix cuando la señal viene por varios caminos.

Seguidamente hay que realizar a la señal el *symbol wave shaping*. Este paso se realiza para disminuir el ancho de banda de los pulsos filtrando la señal con un filtro de coseno alzado. Este filtro sirve para reducir el nivel de los lóbulos laterales del espectro de la señal, reduciendo de esta manera la potencia transmitida.

La señal (I/Q) resultante se pasa por un convertidor digital analógico y un filtro para poder ser modulada.

El proceso de recepción es el inverso y los bloques realizan la operación inversa que en el proceso de transmisión.

# 2.4 Especificaciones técnicas

A continuación se va a enumerar las especificaciones técnicas de un transceptor para IEEE802.11a [2].

## 2.4.1 Impedancia de la antena de emisión y recepción

La impedancia del puerto de la antena de emisión y la de recepción es de 50 Ohmios [3].

## 2.4.2 Rangos de temperatura para la transmisión y la recepción

Se han definido tres rangos de temperatura de funcionamiento que se pueden ver en la Tabla 2.4.

| Tipo 1 | 0 °C a 40 °C   | Entorno doméstico  |

|--------|----------------|--------------------|

| Tipo 2 | -20 °C a 50 °C | Entorno industrial |

| Tipo 3 | -30 °C a 70 °C | Entorno industrial |

Tabla 2.4. Rangos de temperatura de funcionamiento

#### 2.4.3 Nivel de potencia en la transmisión

La potencia máxima transmitida de la señal se puede ver en la Tabla 2.5.

Banda de frecuencias (GHz)

Potencia máxima de salida con antena de 6 dBi de ganancia

5.15 – 5.25

40 mW (2.5 mW/MHz)

5.25 – 5.35

200 mW (12.5 mW/MHz)

5.725 – 5.825

800 mW (50 mW/MHz)

Tabla 2.5. Potencia de salida

#### 2.4.4 Máscara del espectro de salida

El espectro de la señal emitida debe tener 0 dBr (dB relativos a la máxima densidad espectral de la señal) en un ancho de banda no superior a 18 MHz, -20 dBr en una desviación de frecuencia de 20 MHz y -40 dBr en una desviación de frecuencia de 30 MHz. Las mediciones deben realizarse utilizando una resolución de 100 KHz de ancho de banda sobre una señal de video de 30 KHz. Esto se muestra en la Figura 2.12.

Figura 2.12. Máscara del espectro de salida.

#### 2.4.5 Variación de la frecuencia a la salida

La variación máxima de la frecuencia de salida y de los símbolos transmitidos debe ser como máximo de  $\pm$  20 ppm [2].

#### 2.4.6 Sensibilidad a la entrada

El PER (packet error rate) debe ser menor que del 10% para una SDU (sublayer service data Units) de 1000 bytes para los valores de sensibilidad mínima según la tasa de bits transmitida.

Se supone una NF de 10 dB con 5 dB de margen. En la Tabla 2.6 se observa la sensibilidad mínima a la entrada en función de la tasa de bits.

Tasa de bits Sensibilidad mínima Rechazo de canales Rechazo alternativo de (Mbits/s) (dBm) adyacentes (dB) canales adyacentes (dB) 6 -82 16 32 9 -81 15 31 12 -79 29 13 -77 18 11 27 24 -74 8 24 36 -70 4 20 48 -66 0 16 54 -65 -1 15

Tabla 2.6 Sensibilidad mínima a la entrada

La potencia máxima a la entrada para un PER del 10% para una PSDU de 1000 bytes debe ser de -30 dBm (medidos en la antena para cualquier tipo de señal de banda base modulada).

## 2.4.7 Figura de ruido

El receptor debe tener una sensibilidad suficiente para detectar señales de -148 dBm/Hz (para un ancho de banda de 24 MHz). Para tener una SNR de 12 dB como mínimo, el ruido total del receptor debe ser:

$$NF=-148dBm/Hz-12dB-(-174dBm/Hz)=14dB$$

(Ec. 2.12)

Donde -174 dBm/Hz (&T) es la potencia de ruido de la fuente debido al umbral de ruido (noise floor) para T=290°K.

# 2.5 Tipos de Receptores

En este apartado se realizará un breve resumen de las características de los receptores más utilizados para el estándar IEEE802.11a. Este estudio es fundamental para la determinación de las prestaciones que debe cumplir el mezclador. Los tres tipos de receptores que se suelen utilizar para este estándar son:

- Receptor de conversión directa.

- Receptor superheterodino de doble conversión.

- Receptor basado en arquitectura Weaver.

A continuación se detallarán las principales características de cada arquitectura.

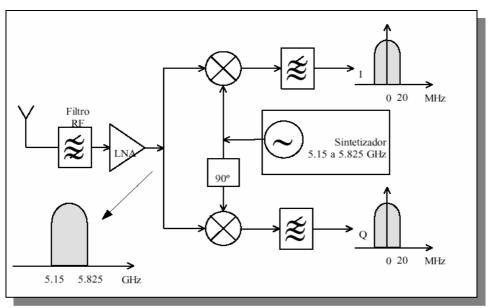

#### 2.5.1 Receptor de conversión directa

El esquema de bloques de este receptor se puede observar en la Figura 2.13. Este esquema es el ideal para ser integrado debido a su reducido número de componentes. Las ventajas de este esquema son:

- No hay problemas con la frecuencia intermedia ni con la imagen ya que  $w_{if}$ =0. No es necesario el filtro de la frecuencia imagen, el cual suele ser externo (SAW).

- Debido al reducido número de componentes y a la eliminación de los filtros de IF el receptor es apto para ser integrado en un chip.

Por el contrario, las desventajas de este esquema se pueden resumir en los siguientes puntos:

• Aparece un *offset* en *DC* a la salida del filtro pasobajo que disminuye el rango dinámico de la señal. Este *offset* se debe a que parte de señal proveniente del oscilador local se cuela al mezclador por la entrada de RF sumándose a al señal proveniente del LNA. Esto es debido a que el aislamiento entre los puertos del mezclador no es infinito. Esta señal se mezcla con la del oscilador local la cual al ser filtrada aparece

como componente continua. A este efecto se le conoce como automezclado (self-mixing).

- El oscilador local hay que desfasarlo 90° para poder realizar la demodulación I/Q. Este desplazamiento provoca un cambio en la amplitud de la señal desfasada, lo cual produce una variación de amplitud entre el oscilador local utilizado para el canal Q y el utilizado para el canal I apareciendo un error en la constelación en la señal demodulada (I/Q Mismatch).

- Realizar un sintetizador a esa frecuencia es dificultoso.

Figura 2.13. Arquitectura de conversión directa.

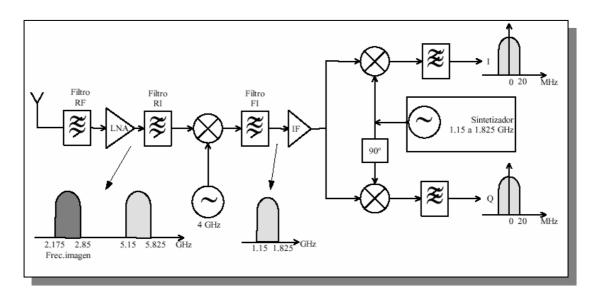

## 2.5.2 Receptor superheterodino de doble conversión

El esquema de bloques de este conversor se puede observar en la Figura 2.14. Las ventajas de este esquema son:

- Se eliminan los problemas de auto-mezclado e *I/Q mismatch*.

- Se mejora la selectividad.

- El sintetizador se hace a baja frecuencia.

Por otro lado, las desventajas que presenta este esquema son:

•Elevado número de componentes a integrar por lo que el consumo aumenta considerablemente.

• Hay que utilizar un filtro de rechazo de la frecuencia imagen, el cual no se puede integrar.

Figura 2.14. Arquitectura del receptor superheterodino de doble conversión.

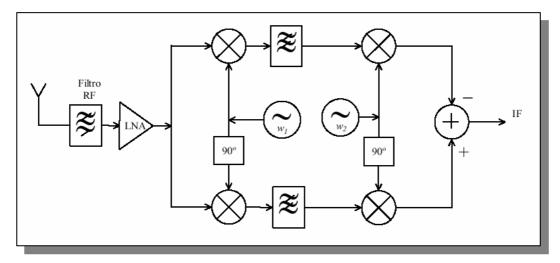

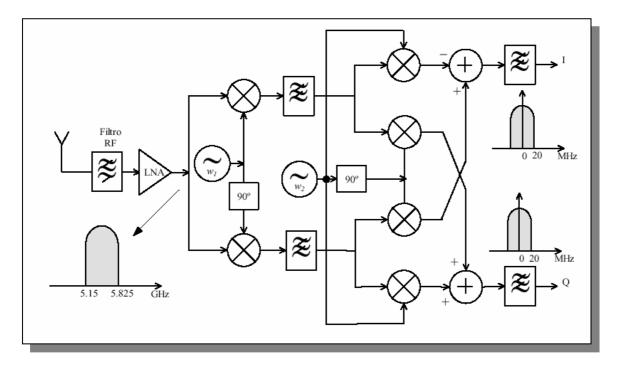

#### 2.5.3 Receptor de arquitectura Weaver modificada

El esquema de bloques de este conversor se puede observar en la Figura 2.15. En la Figura 2.16 se muestra su homónimo para demodulación I/Q. Las principales ventajas de esta arquitectura son:

- Gran selectividad.

- No es necesario utilizar filtros de rechazo de la frecuencia imagen, ya que en esta arquitectura se utilizan las bandas laterales y su traslación para obtener el espectro requerido anulándose dicha frecuencia imagen.

Sin embargo, sus principales desventajas son:

- Elevado número de componentes.

- Pueden aparecer desajustes entre las señales I/Q debido al desfase de  $90^{\rm o}$  de los osciladores.

Figura 2.15. Esquema de bloques del receptor Weaver.

Figura 2.16. Arquitectura del receptor Weaver para demodulación I/Q.

## 2.5 Elección de la arquitectura

Dado que el receptor se va a implementar utilizando transistores bipolares, el consumo de potencia juega un papel importante en la elección de la arquitectura. Dichos transistores pertenecen a la tecnología SiGe de 0.35 µm, y consumen más que los transistores CMOS.

Por otro lado, los receptores Weaver y superheterodino poseen un elevado número de componentes. Como ya sabemos, esto nos dificultará la integración y el obtener bajos consumos de potencia. Además, un receptor superheterodino nos obliga a implementar filtros de rechazo de la frecuencia imagen, los cuales no son integrables.

Sin embargo, un receptor de conversión directa emplea pocos componentes, siendo todos ellos de fácil integración. De la misma forma, los problemas de *self-mixing* que presenta este receptor pueden ser solventados mediante diversas técnicas, tales como el empleo de anillos de guarda.

Como se puede apreciar, estas últimas características constituyen el punto de inflexión que hace que el diseño se decante por el receptor de conversión directa.

A lo largo de este capítulo se han visto las principales características de los sistemas de RF. Igualmente, se ha dado una descripción detallada del Estándar IEEE802.11a, además de establecer las características de los tipos de receptores existentes actualmente. Finalmente, se ha procedido a la elección del receptor. En el próximo capítulo se profundizará en los mezcladores de frecuencia, desarrollando en profundidad los parámetros que los caracterizan y las diferentes topologías existentes.

# CAPITULO 3

# Mezclador de frecuencias

## 3.1 Introducción

Una vez conocidos algunos aspectos fundamentales de las comunicaciones inalámbricas en el capítulo 2, en este capítulo, profundizaremos un poco más dentro del campo de los mezcladores. Para ello realizaremos un estudio teórico de la función de los mezcladores dentro de los sistemas de comunicaciones, así como un estudio de las topologías más empleadas.

# 3.2 Teoría Básica

Un mezclador de frecuencias tiene la función de convertir o trasladar la señal presente a su entrada a un rango de frecuencias diferente, sin modificar las características de frecuencia de la señal a trasladar (ancho de banda, relación de amplitudes, etc.).

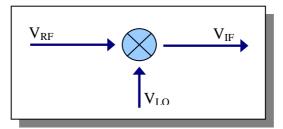

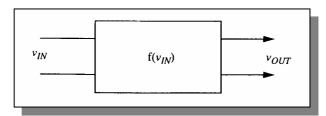

Un mezclador de frecuencias le suma o le resta a la banda de frecuencias de la señal de entrada  $V_{RF}$ , centrada en la frecuencia  $f_{RF}$ , un valor de frecuencia constante de valor  $f_{LO}$  denominado frecuencia del oscilador local, para obtener una señal centrada en la frecuencia  $f_{IF}$ , denominada frecuencia intermedia. Un diagrama básico sería el mostrado en la figura 3.1.

Figura 3.1 Diagrama básico de un mezclador.

La señal de entrada puede estar localizada en cualquier rango de frecuencias, es decir, ser una señal en banda base o una señal pasobanda, y el mezclado puede realizarse tanto para subir en frecuencia la señal de entrada (*up-conversion*), como para bajarla (*down-conversion*).

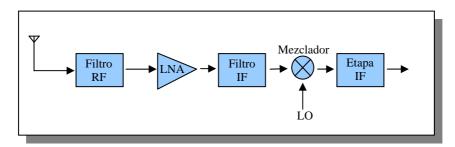

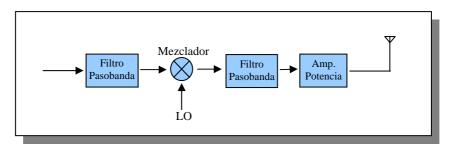

La figura 3.2 representa el esquema de un receptor que utiliza un mezclador *down-conversion* para convertir la señal RF en una señal intermedia IF, mezclando la señal RF con la señal LO procedente de un oscilador local. La figura 3.3 muestra un transmisor, en el que se convierte una señal de baja frecuencia en una de alta frecuencia.

Figura 3.2 Esquema de un receptor.

Figura 3.3 Esquema de un transmisor.

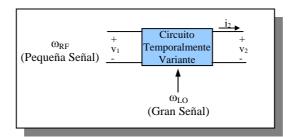

La figura 3.4 ilustra un mezclador sencillo formado por un dispositivo no lineal con una tensión de entrada  $v_1$ . Si el dispositivo fuese perfectamente lineal, la tensión o corriente de salida contendría sólo las frecuencias  $f_1$ . La naturaleza no lineal del mismo determina que se generen otras frecuencias.

Figura 3.4 Dispositivo no lineal usado como mezclador.

En general, la relación entrada-salida en el dominio del tiempo se puede expresar por la serie de Taylor

$$i_2(t) = I_2 + a \cdot v_1(t) + b \cdot [v_1(t)]^2 + c \cdot [v_1(t)]^3 + \dots$$

(Ec. 3.1)

donde  $I_2$  es la corriente de salida en reposo y  $v_1(t)$  representa la suma de los efectos de todas las señales de entrada. Si la entrada contiene sólo una frecuencia, la no-linealidad generará armónicos de esta frecuencia y alterará la componente continua.

Si se tienen varias frecuencias de entrada, se generarán frecuencias suma y diferencia, así como armónicas. Las frecuencias de suma y diferencia generadas por el término cuadrático en ecuación 3.1 se llaman productos de intermodulación de segundo orden; las originadas por el término cúbico, productos de tercer orden.

Un dispositivo de ley cuadrática es ideal para ser utilizado como de mezclador, pues se produce el número mínimo de frecuencias indeseables. Si el dispositivo tiene la característica de transferencia

$$i_2(t) = a \cdot v_1(t) + b \cdot [v_1(t)]^2$$

(Ec. 3.2)

y la entrada es:

$$V_1(t) = V_{RF} \cdot \cos(w_{RF}t) + V_{LO} \cdot \cos(w_{LO}t)$$

(Ec. 3.3)

la corriente de salida se hace

$$i_2(t) = a \cdot (V_{RF} \cdot \cos(w_{RF}t) + V_{LO} \cdot \cos(w_{LO}t)) + b \cdot (V_{RF} \cdot \cos(w_{RF}t) + V_{LO} \cdot \cos(w_{LO}t))^2 \quad \text{(Ec. 3.4)}$$

$$i_{2}(t) = a \cdot V_{RF} \cdot \cos(w_{RF}t) + a \cdot V_{LO} \cdot \cos(w_{LO}t) + (\text{Ec. 3.5})$$

$$+ b \cdot V_{RF}^{2} \cdot \cos^{2}(w_{RF}t) + b \cdot V_{LO}^{2} \cdot \cos^{2}(w_{LO}t) + 2b \cdot V_{RF} \cdot V_{LO} \cdot \cos(w_{RF}t) \cdot \cos(w_{LO}t)$$

Los dos primeros términos en la ecuación 3.5 carecen de interés para la acción del mezclador, salvo que en un circuito práctico puede ser necesario filtrarlos. Mediante la igualdad trigonométrica expresada en la ecuación 3.6 se llega a la conclusión de que los términos tercero y cuarto representan una componente continua y segundos armónicos de las frecuencias de entrada. El término final de la ecuación 3.5 determina el producto deseado  $(2b \cdot V_{RF} \cdot V_{LO} \cdot \cos(w_{RF}t) \cdot \cos(w_{LO}t))$ .

$$aV^2\cos^2 wt = \frac{a}{2}V^2(1+\cos^2 wt)$$

(Ec. 3.6)

$$2bV_{RF}V_{LO}\cos w_{RF}t\cos w_{LO}t = bV_{RF}V_{LO}\left[\cos(w_{LO} - w_{RF})t + \cos(w_{LO} + w_{RF})t\right]$$

(Ec. 3.7)

Obsérvese que las amplitudes de las componentes de frecuencias suma y diferencia, son proporcionales al producto de las amplitudes de las señales de entrada ( $V_{RF}$ • $V_{LO}$ ).

Por lo general, en mezcladores de recepción, sólo se desea la componente de salida de frecuencia diferencia, por lo que deben eliminarse las frecuencias originales, las armónicas y su suma, mediante filtrado o por otros medios.

## 3.3 Parámetros del mezclador

En los siguientes apartados se definen los parámetros más importantes que describen el funcionamiento del mezclador.

#### 3.3.1 Ganancia de Conversión

Una característica importante de un mezclador es la ganancia (o pérdida) de conversión, que se define como la relación entre la señal de salida (IF) y el valor de la señal de entrada (RF). Para un mezclador caracterizado con la ecuación 3.8:

$$(A\cos w_1 t)(B\cos w_2 t) = \frac{AB}{2} \left[\cos(w_1 - w_2)t + \cos(w_1 + w_2)t\right]$$

(Ec. 3.8)

la ganancia de conversión es la salida IF, AB/2, dividido entre la amplitud de la señal de entrada RF, A. Por lo que en este ejemplo, la ganancia de conversión sería B/2, es decir, la mitad de la amplitud LO.

La ganancia de conversión, si se expresa como una relación de potencia, puede ser mayor que la unidad en mezcladores activos, mientras que los mezcladores pasivos sólo son capaces de lograr ganancias superiores a la unidad en tensión o corriente.

Normalmente es conveniente obtener una ganancia de conversión alta, ya que esto implica que los mezcladores proporcionan amplificación a la frecuencia de traslación.

#### 3.3.2 Figura de ruido

La figura de ruido se define como la relación la SNR en el puerto de entrada RF y la SNR a la salida IF.

En un mezclador existen dos frecuencias de entrada que generan una frecuencia intermedia, una es la señal RF y la otra se denomina señal imagen. Estas dos señales se denominan bandas laterales.

La razón de la existencia de estas dos frecuencias es que la señal IF es la magnitud de la diferencia entre las frecuencias RF y LO. Por lo tanto, señales que están por debajo y por encima de IF, con una diferencia igual (2ω<sub>IF</sub>), producirán salidas IF de la misma frecuencia. Por ejemplo si suponemos que la frecuencia IF es 100 MHz y queremos sintonizar una señal a 900 MHz seleccionando una frecuencia LO de 1 GHz, además de la señal de entrada RF deseada a 900 MHz, la señal imagen de 1.1 GHz también producirá una señal de salida IF de 100 MHz.

La existencia de una frecuencia imagen empeora la figura de ruido debido a que el ruido originado en la frecuencia deseada RF y en la frecuencia imagen se convierten en ruido IF.

En el caso en que la señal deseada exista sólo a una frecuencia, la figura de ruido que se mide se denomina figura de ruido de banda lateral única (SSB\_NF). En el caso de que ambas señales, RF y la señal imagen, contengan información útil, se utiliza la figura de ruido de doble banda lateral (DSB\_NF).

Obviamente, la SSB\_NF será mayor que la DSB\_NF, debido a que ambas tienen el mismo ruido IF, pero la SSB\_NF tiene potencia de señal sólo en una banda lateral. Por lo tanto, la SSB\_NF será normalmente 3dB mayor que la DSB\_NF.

#### 3.3.3 Linealidad

Existen diferentes formas de definir la linealidad de un mezclador. En los siguientes apartados veremos las más utilizadas.

#### 3.3.3.1 Rango dinámico

El rango dinámico se define como la diferencia entre los valores mínimos y máximos de señal que se pueden aplicar a un circuito.

El valor mínimo del rango dinámico se establece con la figura de ruido, que indica la mínima señal que se puede procesar. El máximo se establece en el principio de las no-linealidades que acompañan a las grandes señales.

#### 3.3.3.2 Punto de compresión

Como en los amplificadores y, prácticamente en todos los dispositivos físicos, los mezcladores reales tienen un límite por encima del cual la salida no es lineal con la entrada. El punto de compresión es el valor de la señal RF en el que se produce una desviación de la curva lineal ideal. Normalmente se especifica un valor de compresión de 1 dB (o más raramente 3 dB). Sobre este nivel, un aumento adicional en el nivel de entrada RF no se traduce en un aumento proporcional en el nivel de salida. Cuantitativamente, la compresión de ganancia es la reducción del nivel de salida en dB por debajo de la característica lineal.

#### 3.3.3.3 Distorsión de intermodulación de tercer orden

Para caracterizar la linealidad también se usa el punto de intercepción de tercer orden. Tal y como vimos en el capítulo 2 el punto de intercepción es el lugar en el que la curva de respuesta fundamental y la de respuesta espuria de tercer orden se interceptan (ver figura 3.5). A menudo se usa para especificar la supresión de los armónicos de tercer orden generados por el mezclador cuando a la entrada del mismo están presentes dos tonos. Mientras más alto esté el punto de intercepción, mejor será la supresión de los armónicos de tercer orden.

Un *test* de intermodulación de tercer orden es una forma eficaz para evaluar el rendimiento de un mezclador debido a que imita un escenario real en el que hay presente a la entrada una señal deseada RF y una potencial interferencia.

Idealmente, ambas señales presentes en la entrada RF serían trasladadas en frecuencia sin interaccionar unas con otras. Un mezclador real muestra algunos efectos de intermodulación y, por lo tanto, la salida contendrá versiones trasladadas en frecuencia de los componentes de intermodulación de tercer orden cuyas frecuencias serán  $2\omega_{RF1}\pm\omega_{RF2}$  y  $2\omega_{RF2}\pm\omega_{RF2}$ .

La distorsión de intermodulación de tercer orden en dos tonos es la cantidad de distorsión de tercer orden causada por la presencia de una señal secundaria recibida en el puerto de RF. Matemáticamente, la distorsión de tercer orden se define en términos de la componente de frecuencia en  $2f_2$ -f± $f_o$ , donde f, es la señal de entrada deseada y  $f_2$  es la señal de entrada secundaria. Por lo general, mientras más alto sea el punto de interceptación del mezclador, más baja será la amplitud de este producto.

Figura 3.5 Definiciones de terminología de operación de mezcladores.

En la figura 3.5, se muestra la característica de un mezclador hipotético, así como la representación gráfica de las definiciones anteriores. Para una entrada de 0 dBm la salida es de 6 dBm, indicando una ganancia de conversión de 6 dB. En este nivel de entrada, el producto de intermodulación de dos tonos y tercer orden está 30 dB por debajo de la salida deseada. En

un valor de entrada más alto aparece el punto de compresión de 3 dB (3 dB de salida deseada abajo del valor de línea recta); y a un nivel de entrada aun más alto se encuentra el punto de interceptación que es donde se interceptan las curvas proyectadas de la salida deseada y las del producto de intermodulación de tercer orden.

#### 3.3.4 Aislamiento

El aislamiento representa la cantidad de "fuga" o "paso de señal" entre los puertos del mezclador. Se supone que en cada terminal debe estar presente únicamente la señal correspondiente al puerto. Si el aislamiento es grande esto ocurre, si no lo es, aparecerá en el puerto parte de señal que pertenece al otro puerto. Por ejemplo, el aislamiento en el puerto de RF de la señal LO, es la cantidad en que se atenúa la señal LO en el puerto de RF, respecto del nivel que ésta tenía en su propio puerto. El aislamiento depende de la configuración física del mezclador.

# 3.4 Sistemas no lineales como mezcladores lineales

Algunos mezcladores implementan directamente una multiplicación, mientras que otros la producen mediante una no-linealidad.

Primero se estudiará un sistema no-lineal de 2 puertos, debido a que los mezcladores de este tipo preceden a los designados específicamente para actuar como multiplicadores. Si la no-linealidad está bien definida (en sentido matemático), podemos describir la relación entrada/salida como:

$$V_{OUT} = \sum_{n=0}^{N} C_n (v_{IN})^n$$

(Ec. 3.9)

El uso de una no-linealidad de orden N requiere que la señal  $v_{\rm IN}$  sea la suma de la entrada RF y la señal del oscilador local. En general, la salida se compondrá de 3 tipos de productos: términos DC, armónicos de las entradas y productos de intermodulación (IM) de esos armónicos. No todos esos componentes espectrales son deseables, por lo que parte de la labor de diseño consistirá en el uso de topologías que generen los mínimos términos posibles.

Los factores no-lineales de orden par de la ecuación 3.9 forman los términos DC, éstos son fácilmente filtrables mediante un acople AC, si es necesario. Los términos armónicos ( $m\omega_{LO}$  y  $m\omega_{RF}$ ), que van desde m>1 hasta N, son fácilmente filtrables debido a que sus frecuencias suelen estar lo suficientemente separadas de la frecuencia IF. Los productos de

intermodulación tienen frecuencias de la forma  $p\omega_{RF}\pm q\omega_{LO}$ , donde p y q son enteros entre 0 y N. Sólo el término de intermodulación de 2° orden (p=q=1) es el que normalmente se desea obtener. Desgraciadamente, otros productos IM pueden tener frecuencias cercanas a la IF, haciendo que sean más difíciles de eliminar.

Debido a que los sistemas no-lineales de alto orden tienden a generar un mayor número de términos no-deseados, los mezcladores deberían aproximar un comportamiento de ley cuadrática (la no-linealidad de orden menor) si sólo tienen un puerto de entrada, como en la figura 3.6.

Figura 3.6. Sistema general de dos puertos no-lineal.

## 3.4.1 Mezclador de dos puertos: Dispositivo de ley cuadrática

Consideremos las propiedades específicas de un mezclador de ley cuadrática para poder mostrar sus ventajas sobre los mezcladores no-lineales de órdenes mayores.

Para ver cómo aparece la multiplicación en un mezclador de ley cuadrática hay que observar que los únicos términos distintos de cero en la serie son los términos  $C_1$ ,  $C_2$  y  $C_0$ , pero éste último se elimina fácilmente ya que es la componente DC, por lo que se ignorará para simplificar la ecuación.

Si v<sub>IN</sub> es la suma de 2 sinusoides:

$$v_{IN} = v_{RF} \cos(w_{RF}t) + v_{IO} \cos(w_{IO}t)$$

(Ec. 3.10)

entonces la salida de este mezclador se puede expresar como suma de 3 componentes:

$$v_{OUT} = v_{FUN} + v_{SOUARE} + v_{CROSS}$$

(Ec. 3.11)

donde

$$v_{FUN} = C_1(v_{RF}\cos(w_{RF}t) + v_{LO}\cos(w_{LO}t))$$

(Ec. 3.12)

$$v_{SQUARE} = C_2(v_{RF}\cos(w_{RF}t)^2 + v_{LO}\cos(w_{LO}t)^2$$

(Ec. 3.13)

$$v_{CROSS} = 2C_2 v_{RF} v_{LO} (\cos(w_{RF}t).\cos(w_{LO}t))$$

(Ec. 3.14)

Los términos fundamentales son versiones escaladas de las entradas originales y no representan una salida útil para el mezclador. Estos términos pueden ser eliminados mediante filtrado. Los componentes  $v_{SQUARE}$  tampoco proporcionan información útil, como se observa en el siguiente caso obtenido de la ecuación 3.6

$$(\cos wt)^2 = \frac{1}{2}(1 + \cos 2wt)$$

(Ec. 3.15)

Obsérvese como los componentes v<sub>SQUARE</sub> producen un *offset* DC, así como segundos armónicos de las señales de entrada. Esto también se puede eliminar mediante filtrado.

La salida útil la forman los componentes  $v_{CROSS}$  debido a que se observa una multiplicación en la ecuación 3.14. Usando la ecuación 3.6, se puede rescribir  $v_{CROSS}$  de forma que muestre la acción del mezclador más claramente:

$$v_{CROSS} = C_2 v_{RF} v_{LO} [\cos(w_{RF} - w_{LO})t + \cos(w_{RF} + w_{LO})t]$$

(Ec. 3.16)

Para una amplitud de LO fijada, la salida IF es linealmente proporcional a la amplitud de la entrada RF. Esta no-linealidad implementa un mezclador lineal, debido a que la salida es proporcional a la entrada.

La ganancia de conversión de este circuito se obtiene a partir de la ecuación 3.16:

$$G_C = \frac{C_2.v_{RF}v_{LO}}{v_{RF}} = C_2.v_{LO}$$

(Ec. 3.17)

Como cualquier otro parámetro de ganancia, la ganancia de conversión es adimensional. En diseños discretos se debe expresar como relación de potencia (o su equivalente en dB), pero los distintos niveles de impedancia en los mezcladores integrados hacen apropiado el uso de la ganancia de conversión de tensión o corriente.

La ventaja del mezclador de ley cuadrática es que los componentes espectrales no deseados normalmente están en una frecuencia bastante separada de IF, por lo que se pueden eliminar fácilmente.

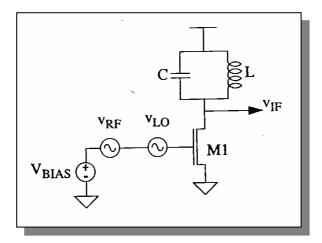

En la figura 3.7 se muestra un mezclador de ley cuadrática realizado con MOSFETs. En este esquemático simplificado, las tensiones de polarización, RF y LO se representan en serie con la puerta del transistor. La suma de las señales RF y LO puede realizarse en circuitos prácticos con sumadores resistivos o reactivos. Debido a que estas señales están en serie, existe poco aislamiento entre ellas.

Figura 3.7. Mezclador MOSFET de ley cuadrática (Simplificado).

En la figura 3.8 se muestra una solución alternativa (pero funcionalmente equivalente) que reduce el efecto de la señal LO relativamente grande en el puerto RF.

Figura 3.8. Mezclador MOSFET de ley cuadrática (Configuración alternativa).

La señal RF ataca directamente a la puerta (a través de un condensador para el bloqueo DC), mientras que la señal LO ataca al terminal de Surtidor. De esta manera, la tensión Puerta-Surtidor ( $V_{GS}$ ) es la suma de las señales LO y RF referenciadas a tierra.

# 3.4.2 Ganancia de conversión en un mezclador de un solo transistor bipolar

Debido a que en un mezclador no es necesario un perfecto comportamiento de ley cuadrática,  $M_1$  puede ser un transistor bipolar. En este caso el efecto cuadrático en la representación en serie para la relación exponencial iv- $V_{BE}$ , domina en un rango limitado de amplitudes de entrada. Ignorando los efectos dinámicos esta relación viene dada por:

$$ic = Is.e^{\frac{V_{BE}}{V_T}}$$

(Ec. 3.18)

expandiendo esta relación a un sistema de segundo orden:

$$ic = Ic \left[ 1 + \frac{V_{BE}}{V_T} + \frac{1}{2} \left( \frac{V_{BE}}{V_T} \right)^2 \right]$$

(Ec. 3.19)

haciendo que:

$$C_2 = \frac{gm}{2V_T}$$

(Ec. 3.20)

donde gm=I<sub>C</sub>/V<sub>T</sub> se obtiene que la ganancia de conversión viene dada por:

$$G_C = C_2.v_{LO} = gm \frac{v_{LO}}{2V_T}$$

(Ec. 3.21)

Se observa como la ganancia de conversión es proporcional a la transconductancia y a la relación entre la amplitud del oscilador local y la  $V_T$ . En otras palabras, la ganancia de conversión en un transistor bipolar depende de la corriente de polarización, de la amplitud del oscilador local y de la temperatura.

En este análisis se han ignorado las resistencias parásitas de base y emisor. Estas resistencias pueden linealizar el transistor y, por lo tanto, empeorar la acción del mezclador.

# 3.5 Mezcladores basados en multiplicadores

Los mezcladores basados en sistemas no-lineales generan un número elevado de componentes espectrales. Además, debido a que los mezcladores de dos puertos tienen una sola entrada, las señales de RF y LO no suelen estar lo suficientemente aisladas entre ellas. Esta falta de aislamiento puede provocar la aparición de *offset* de DC en la etapa de IF o la radiación de la señal de LO (o sus armónicos) a través de la antena.

Los mezcladores basados en multiplicadores presentan por lo general un rendimiento mayor debido a que (idealmente) sólo generan el producto de intermodulación deseado. Además, debido a que las entradas del multiplicador se encuentran en puertos separados, puede haber un alto grado de aislamiento entre las tres señales (RF, LO, IF).

Los mezcladores basados en multiplicadores se catalogan como, simple balanceado y doble balanceado. A continuación se presenta cada uno de ellos. Empezaremos por las topologías más simples hasta llegar al doble balanceado. Por último estudiaremos en mayor profundidad el mezclador pasivo pues es el tipo de estructura elegida para la realización de este proyecto.

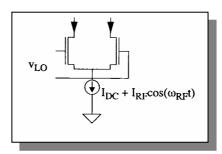

# 3.5.1 Mezclador simple balanceado

Este tipo de multiplicadores primero convierte la tensión de entrada RF en una corriente y después realiza la multiplicación en el dominio de la corriente. La célula más sencilla de este tipo se representa en la figura 3.9.

Figura 3.9. Mezclador simple-balanceado.

En este mezclador,  $v_{LO}$  se elige lo suficientemente grande para que los transistores puedan conmutar alternativamente la corriente de polarización de un lado al otro a la frecuencia LO. De esta forma la corriente de polarización se multiplica por una onda cuadrada cuya frecuencia es la del oscilador local.

$$i_{out}(t) = \text{sgn}\{\cos(w_{LO}t)(I_{BIAS} + I_{RF}\cos(w_{RF}t))\}$$

(Ec. 3.22)

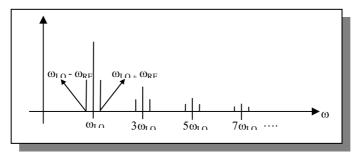

Debido a que una onda cuadrada consiste en los armónicos impares del fundamental, la multiplicación de la corriente de polarización por una onda cuadrada produce un espectro de salida como el mostrado en la figura 3.10 ( $\omega_{RF}$  se ha tomado muy pequeño para una representación más clara).

Figura 3.10. Espectro de salida de un mezclador simple-balanceado.

La salida consiste en componentes suma y resta, cada uno resultado de un armónico impar de LO mezclado con la señal RF. Los armónicos impares de LO aparecen directamente a la salida como consecuencia de la multiplicación de la señal de polarización (DC) con la señal LO. Debido a la presencia de LO en el espectro de salida, este tipo de mezcladores se denominan simple-balanceados. Los mezcladores doble-balanceados aprovechan la simetría para eliminar la salida no deseada LO.

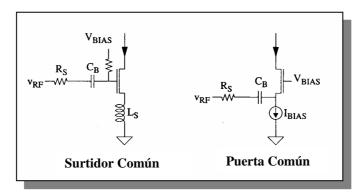

A pesar de que la fuente de corriente de la figura 3.9 incluye un componente que es perfectamente proporcional a la señal de entrada RF, los convertidores V-I de los mezcladores reales son imperfectos. Un importante reto de diseño es maximizar la linealidad de la transconductancia RF. Ésta se puede mejorar mediante degeneración de la Surtidor, tanto para puerta como para Surtidor común; (ver figura 3.11).

Figura 3.11 Transconductores RF para mezcladores.

Ambos circuitos usan una resistencia  $R_s$  para linealizar la característica de transferencia. Para el caso del circuito puerta común esta linealización es más efectiva si la admitancia desde el terminal de Surtidor del transistor es mucho mayor que la conductancia de  $R_s$ . En este caso, la transconductancia de la etapa se aproxima a  $1/R_s$ .

Normalmente se prefiere una degeneración inductiva a una resistiva debido a varios motivos. Una inductancia no introduce ruido térmico que degrade la figura de ruido ni caída de tensión que disminuya el nivel de alimentación. Esta última consideración es particularmente importante para aplicaciones de baja tensión y baja potencia. Finalmente, un aumento de la reactancia ayuda a atenuar los armónicos de alta frecuencia y los componentes de intermodulación.

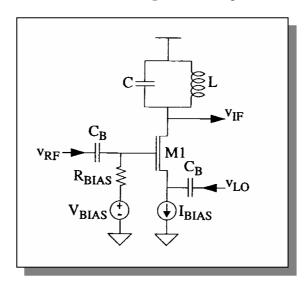

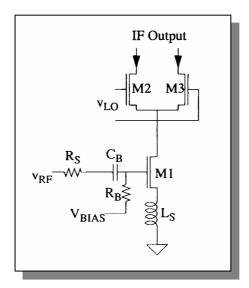

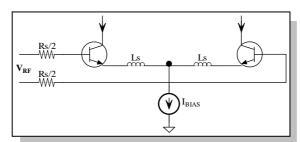

En la figura 3.12 se muestra un mezclador simple-balanceado de forma más completa, que incorpora una transconductancia linealizada.

Figura 3.12. Mezclador simple-balanceado con transconductancia linealizada.

El valor de  $V_{BIAS}$  establece la polarización,  $R_B$  se escoge lo suficientemente grande para no despolarizar la puerta del circuito y reducir su contribución al ruido. La señal RF se aplica a la puerta a través de un condensador de bloqueo DC ( $C_B$ ). En la práctica se usa un filtro para eliminar los componentes espectrales de LO de la salida.

La ganancia de conversión de un mezclador se puede calcular sabiendo que los transistores de LO se comportan como interruptores perfectos. Entonces, la corriente de salida diferencial puede ser considerada como el resultado de multiplicar la corriente de drenador de M1 por una onda cuadrada de amplitud unitaria. Debido a que el componente fundamental de la onda cuadrada es  $4/\pi$  veces la amplitud de la onda cuadrada, se puede escribir:

$$G_C = \frac{2}{\pi} gm \tag{Ec. 3.23}$$

$$g_m = \frac{di_c}{dv_{be}} = \frac{i_c}{V_T}$$

(Ec. 3.24)

donde gm es la transconductancia del conversor V-I y  $G_C$  es una transconductancia. El coeficiente es  $2/\pi$  en vez de  $4/\pi$  debido a que la señal IF se divide entre los componentes suma y diferencia.

#### 3.5.2 Mezclador activo doble balanceado. Célula de Gilbert.

Para evitar la llegada de productos de LO a la salida, se pueden combinar dos circuitos simplebalanceados para conseguir un mezclador doble balanceado.

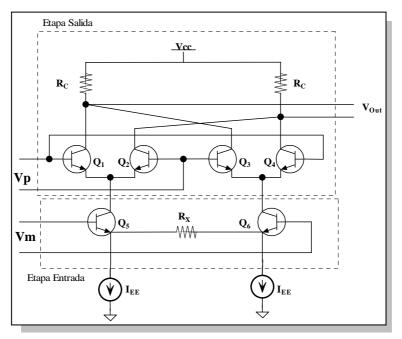

Figura 3.13. Mezclador activo doble balanceado.

La célula de Gilbert está compuesta por dos etapas: la etapa de entrada o de radio frecuencia y la etapa de salida o de frecuencia intermedia. La etapa de entrada compuesta por un par diferencial, es un amplificador de transconductancia. Su función es la de conversión con ganancia de tensión a corriente. La etapa de salida compuesta por dos pares diferenciales con salidas cruzadas, es el núcleo del mezclador ya que se encarga de la realización de la multiplicación.

Para el análisis del circuito se supone que todos los transistores son idénticos y que la resistencia de salida de los transistores y de la fuente de corriente de polarización, así como las corrientes de base se pueden despreciar. Además, se supondrá que los transistores están bien polarizados y se encuentran siempre en la región activa.

Del modelo de Ebers-Moll y suponiendo  $V_{BE1}$ ,  $V_{BE2} >> V_{T}$

$$V_{BEx} = V_{T} \ln \frac{I_{CX}}{I_{SX}}$$

$$(Ec. 3.25)$$

$$I_{C1} = \frac{I_{C5}}{1 + e^{\frac{V_{P}}{V_{T}}}}$$

$$(Ec. 3.26)$$

$$I_{C2} = \frac{I_{C5}}{1 + e^{\frac{V_{P}}{V_{T}}}}$$

$$(Ec. 3.28)$$

$$I_{C4} = \frac{I_{C6}}{\frac{V_{P}}{V_{P}}}$$

$$1 + e^{\frac{V_{T}}{V_{T}}}$$

$$(Ec. 3.29)$$

$$I_{C5} = I_{EE} + \frac{V_{x}}{R_{x}}$$

$$(Ec. 3.30)$$

$$(Ec. 3.31)$$

Combinando las expresiones anteriores:

$$I_{1} = \frac{I_{EE} + \frac{V_{x}}{R_{x}}}{1 + e^{\frac{V_{x}}{V_{T}}}} + \frac{I_{EE} - \frac{V_{x}}{R_{x}}}{1 + e^{\frac{V_{x}}{V_{T}}}}$$

$$I_{2} = \frac{I_{EE} + \frac{V_{x}}{R_{x}}}{1 + e^{\frac{V_{x}}{V_{T}}}} + \frac{I_{EE} - \frac{V_{x}}{R_{x}}}{1 + e^{\frac{V_{x}}{V_{T}}}}$$

(Ec. 3.32)

(Ec. 3.33)

Por lo que la salida en corriente diferencial es:

$$\Delta I = I_2 - I_1 = \frac{2\frac{V_x}{V_x}}{1 + e^{\frac{V_p}{V_T}}} + \frac{-2\frac{V_x}{V_x}}{-2\frac{V_x}{R_x}}$$

$$\Delta I = I_2 - I_1 = \frac{I'}{1 + e^{\frac{V_P}{V_T}}} - \frac{I'}{1 + e^{\frac{-V_P}{V_T}}} = I' \frac{e^{\frac{V_P}{V_T}} - e^{\frac{V_P}{V_T}}}{2 + e^{\frac{V_P}{V_T}} + e^{\frac{V_P}{V_T}}} = I' \cdot \tanh\left(-\frac{V_P}{2V_T}\right)$$

$$\tanh\left(-\frac{V_P}{2V_T}\right)$$

(Ec. 3.35)

La salida en tensión es:

$$V_{o1} = Vcc - I_1RC$$

$V_{o2} = Vcc - I_2RC$  (Ec. 3.36)

$$V_o = V_{o1} - V_{o2} = R_C (I_2 - I_1)$$

(Ec. 3.37)

$$V_o = -R_C \frac{2V_m}{R_x} \tanh\left(\frac{V_P}{2V_T}\right)$$

(Ec. 3.38)

Para ciertos valores de x, se puede hacer la aproximación:  $\tanh x = x \leftarrow -0.5 < x < 0.5$

Es decir, si  $|V_P| < 2V_T$ , la salida en tensión de la célula de Gilbert se puede expresar como se muestra en la siguiente expresión:

$$V_o \approx -R_C \frac{2V_m}{R_x} \frac{V_P}{2V_T} \approx \underbrace{-\frac{R_C}{R_x V_T}}_{cte} V_m V_P$$

(Ec. 3.39)

Es decir, la característica de transferencia en continua, es el producto de las dos tensiones de entrada.

Esta célula multiplicadora se puede usar en diferentes aplicaciones dependiendo de la magnitud de  $V_m$  y  $V_p$  con respecto a  $V_T$ :

- a)  $V_m$  y  $V_p$  <<  $V_T$ : En este caso, la tangente hiperbólica se puede considerar como una recta, con lo que se obtiene el producto linear  $V_m \cdot V_p$ .

- b)  $V_m$  o  $V_p > V_T$ : Con estos niveles, el transistor al que se le aplica dicha señal se comporta como un conmutador antes que como un dispositivo lineal. Es como multiplicar una pequeña señal por un tren de pulsos.

c) V<sub>m</sub> y V<sub>p</sub> > V<sub>T</sub>: Este modo de operación es útil para la detección de diferencia de fases entre dos señales de amplitud limitada. Ambos transistores se comportan como conmutadores.

Normalmente, se asume la opción b de forma que la amplitud de la señal LO es lo suficientemente grande para hacer actuar al par diferencial como interruptores controlados por tensión. Los dos mezcladores simple balaceado están conectados en antiparalelo para la señal LO, pero en paralelo para la señal RF. Por lo tanto, los términos de LO se anulan a la salida y la señal de RF se dobla.

Este mezclador tiene un alto grado de aislamiento LO-IF. De hecho, si se tiene cuidado en el *layout*, se puede conseguir un aislamiento de entre 40 dB y 60 dB.

Al igual que en el mezclador simple-balanceado, el rango dinámico está limitado en parte por la linealidad del conversor V-I en el puerto IF. Por lo tanto, parte del proceso de diseño será conseguir una mejor conversión V-I. Las técnicas básicas de linealización usadas en el mezclador simple-balanceado deben ser adaptadas al caso del mezclador doble-balanceado, como se muestra en la figura 3.14.

Figura 3.14. Transconductor RF diferencial linealizado en mezclador doble balanceado.

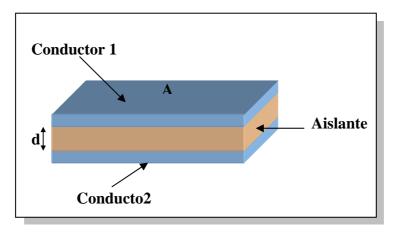

Figura 3.15. Mezclador doble balanceado con mínimo consumo DC.

En aplicaciones de baja tensión, la fuente de corriente DC se puede reemplazar por un tanque paralelo LC para crear una fuente de corriente que no consuma tensión DC. La frecuencia de resonancia del tanque debe elegirse para proporcionar rechazo del componente en modo común. Si existen varios componentes en modo común, se deben usar varios tanques LC en serie. En la figura 3.15 se muestra un circuito de un mezclador doble-balaceado en el que se utiliza un tanque LC.

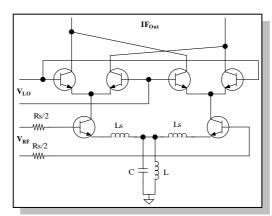

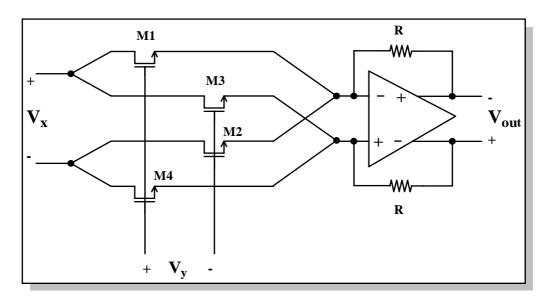

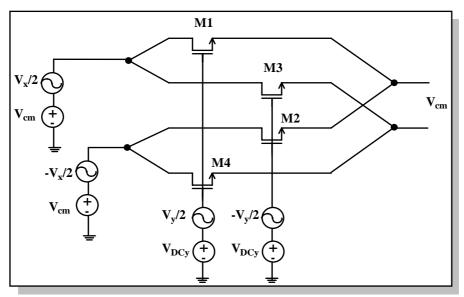

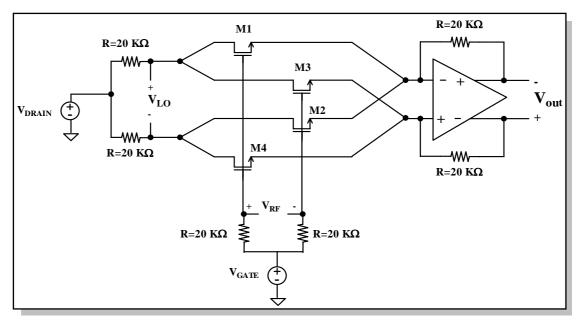

# 3.5.3 El mezclador CMOS pasivo

El multiplicador CMOS pasivo emplea un puente multiplicador (M1 – M4) tal como se muestra en la figura 3.16, así como una etapa de amplificación compuesta por un amplificador operacional totalmente diferencial. El puente multiplicador opera en la región de triodo y en consecuencia los MOSFET pueden ser considerados como resistencias. Inicialmente sin considerar la polarización del puente, la tensión en el terminal negativo de salida viene dada como:

$$V_{o-} = -R.(I_{D1} + I_{D2})$$

(Ec. 3.40)

Mientras que la tensión positiva viene dada como:

$$V_{o+} = -R.(I_{D3} + I_{D4})$$

(Ec. 3.41)

En consecuencia la tensión de salida tiene la siguiente expresión:

$$V_{out} = V_{o+} - V_{o-} = -R.(I_{D1} + I_{D2} - I_{D3} - I_{D4})$$

(Ec. 3.42)

Figura 3.16. Multiplicador Analógico CMOS.

En la figura 3.17 se muestra un esquema simplificado del multiplicador con la polarización de las entradas. En la entrada X, se ha establecido un nivel de tensión para polarizar el sistema, mientras que el nivel de polarización de la entrada Y, es establecido a un nivel suficiente para mantener al puente en la región de triodo.

Figura 3.17. Polarización del multiplicador.

Usando la ecuación correspondiente a la región de triodo de los transistores (ver apartado 4.5):

$$I_D = \mu . C_{OX} \left[ (V_{GS} - V_T) V_{DS} - \left( \frac{V_{DS}^2}{2} \right) \right]$$

(Ec. 3.43)

y teniendo en cuenta que la tensión en DC Puerta – Surtidor para todos los MOSFET es la misma, las corrientes de Drenador se pueden poner como:

$$I_{D1} = \mu . C_{OX_1} \left[ \left( V_{GS} + \frac{V_y}{2} - V_{T1} \right) \left( \frac{V_x}{2} \right) - \frac{1}{2} \left( \frac{V_x}{2} \right)^2 \right]$$

(Ec. 3.44)

$$I_{D2} = \mu C_{OX2} \left[ \left( V_{GS} - \frac{V_y}{2} - V_{T2} \right) \left( -\frac{V_x}{2} \right) - \frac{1}{2} \left( -\frac{V_x}{2} \right)^2 \right]$$

(Ec. 3.45)

$$I_{D3} = \mu . C_{OX3} \left[ \left( V_{GS} - \frac{V_{y}}{2} - V_{T3} \right) \left( \frac{V_{x}}{2} \right) - \frac{1}{2} \left( \frac{V_{x}}{2} \right)^{2} \right]$$

(Ec. 3.46)

$$I_{D4} = \mu . C_{OX4} \left[ \left( V_{GS} + \frac{V_y}{2} - V_{T4} \right) \left( -\frac{V_x}{2} \right) - \frac{1}{2} \left( -\frac{V_x}{2} \right)^2 \right]$$

(Ec. 3.47)

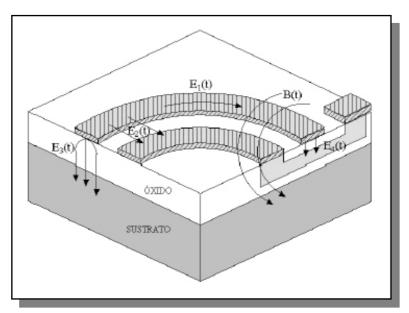

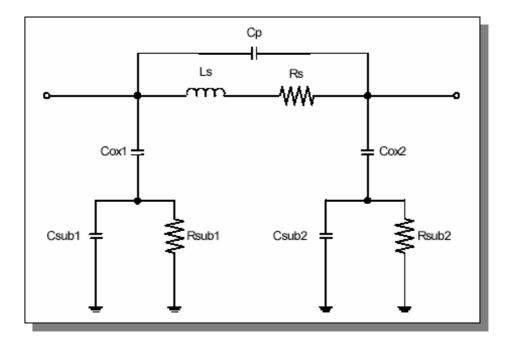

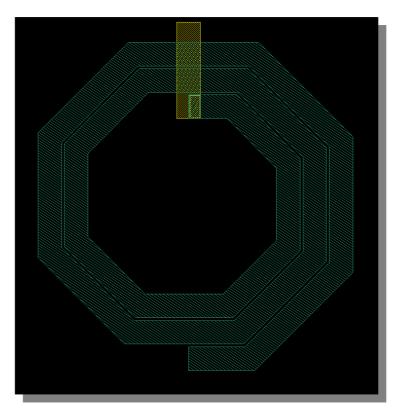

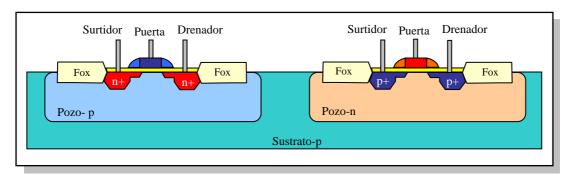

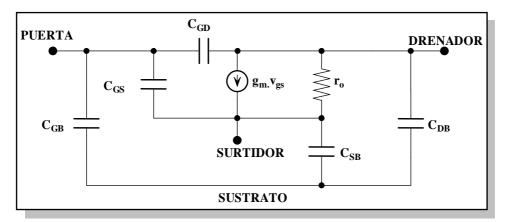

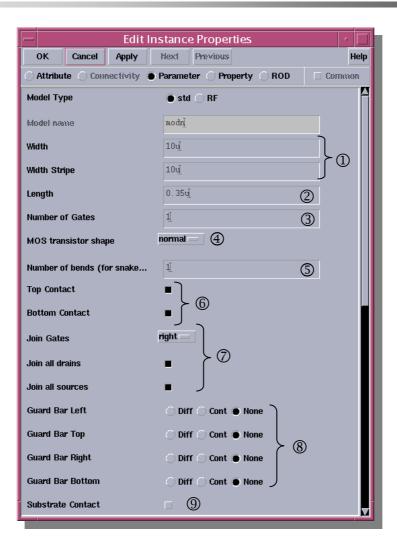

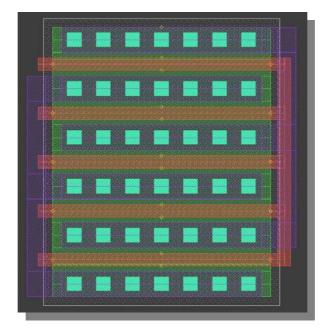

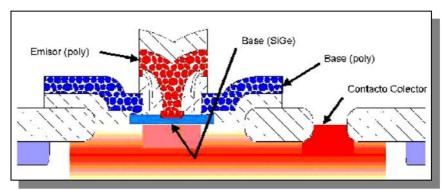

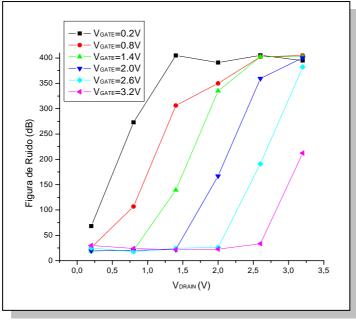

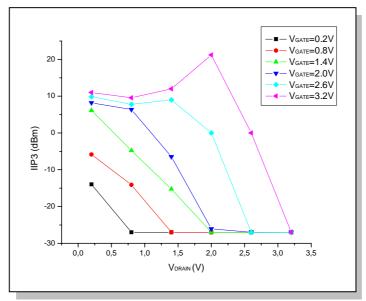

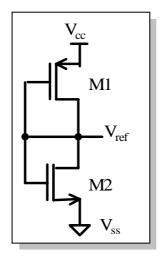

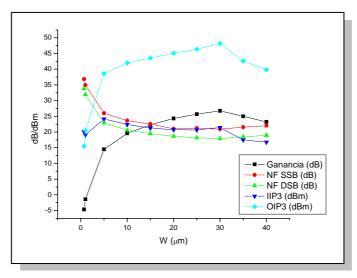

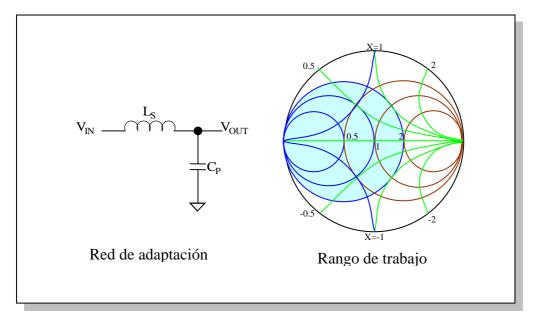

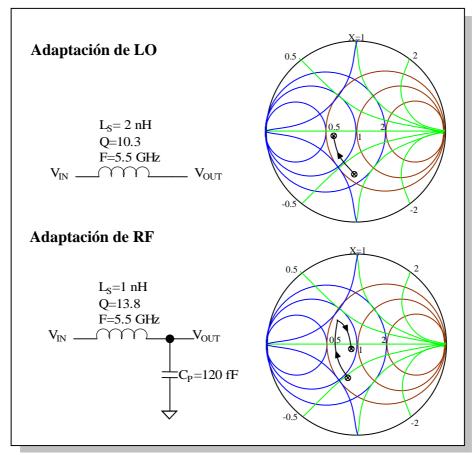

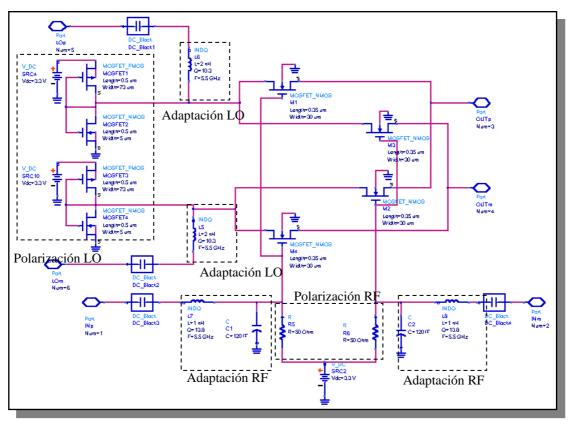

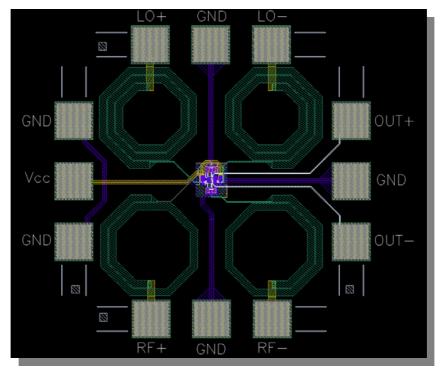

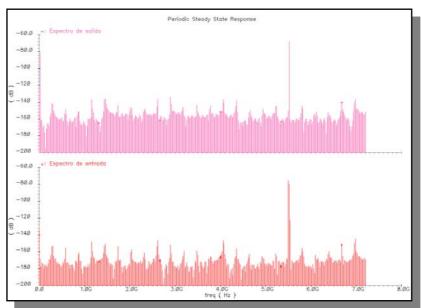

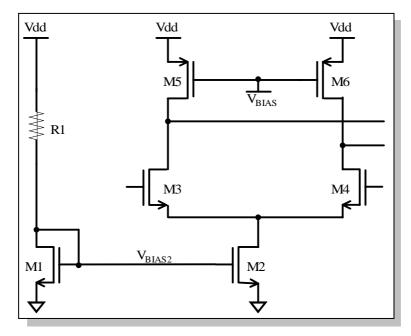

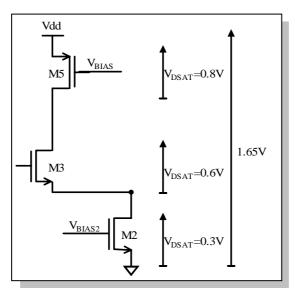

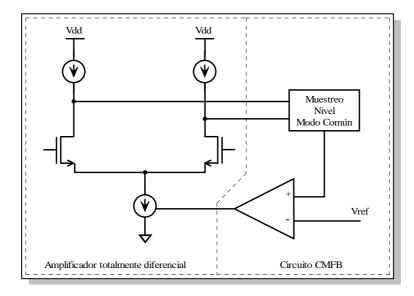

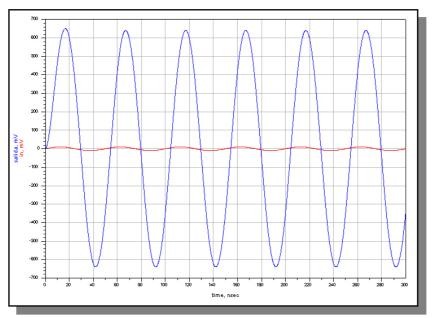

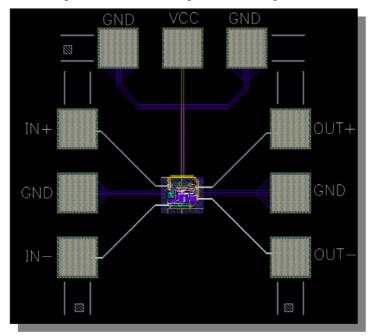

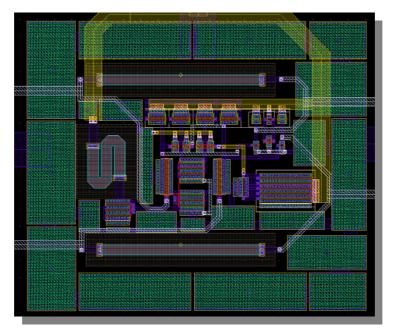

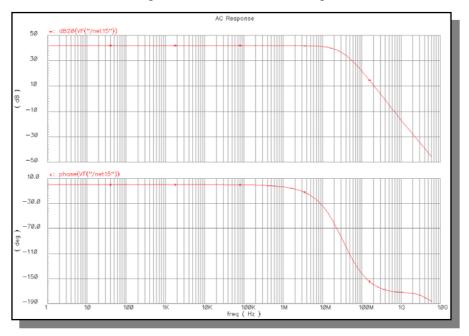

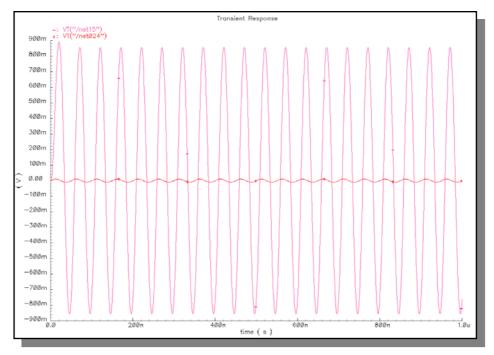

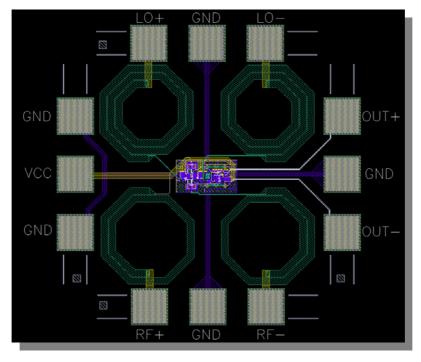

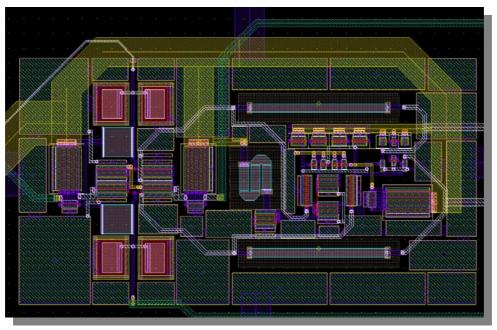

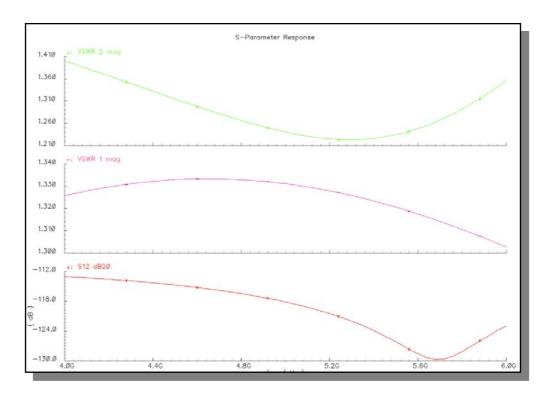

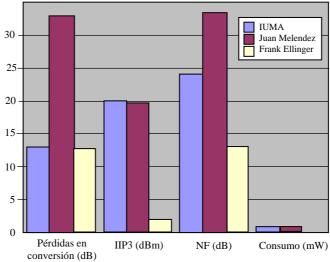

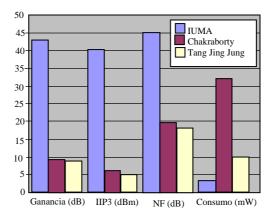

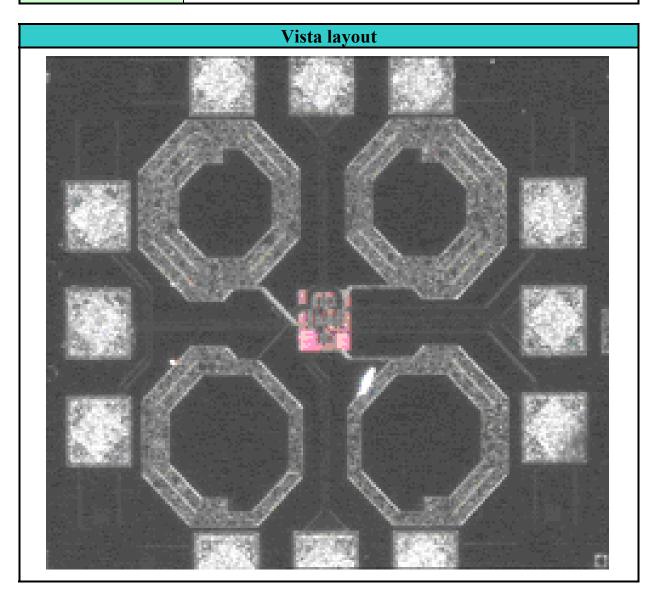

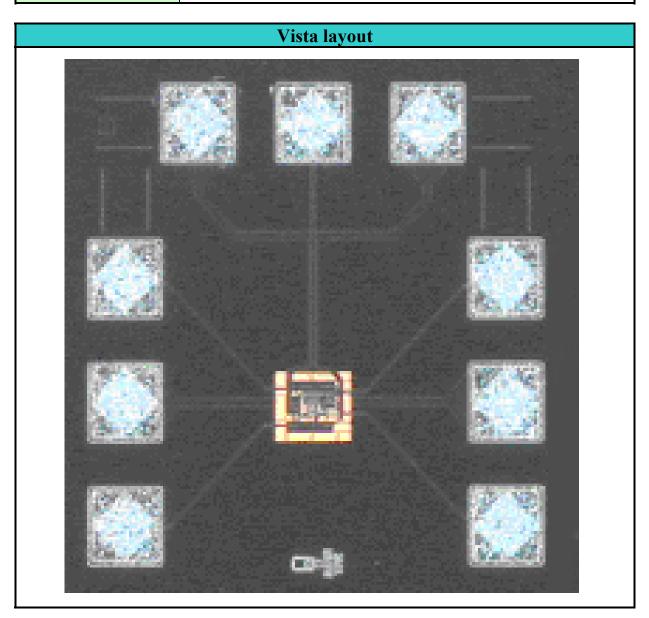

Considerando que  $C_{OX} = C_{OX1} = C_{OX2} = C_{OX3} = C_{OX4}$  y sustituyendo las ecuaciones 3.44 a 3.47 en la ecuación 3.42 se obtiene que la tensión de salida viene dada por la siguiente ecuación: