# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

### DESARROLLO DEL FIRMWARE DE CONTROL DE LOS NODOS DE UNA PLATAFORMA EXPERIMENTAL DE WSN

Titulación: Grado en Ingeniería en Tecnologías de la Telecomunicación

Mención: Sistemas Electrónicos

Autor: Ricardo Antonio Rios Peña

Tutores: Dr. Roberto Esper-Chain Falcón

Dr. Félix B. Tobajas Guerrero

Fecha: Julio 2015

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

### DESARROLLO DEL FIRMWARE DE CONTROL DE LOS NODOS DE UNA PLATAFORMA EXPERIMENTAL DE WSN

### **HOJA DE FIRMAS**

### Alumno

Fdo.: Ricardo Antonio Rios Peña

Tutor Tutor

Fdo.: Dr. Roberto Esper-Chaín Falcón Fdo.: Dr. Félix B. Tobajas Guerrero

Fecha: Julio 2015

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

### DESARROLLO DEL FIRMWARE DE CONTROL DE LOS NODOS DE UNA PLATAFORMA EXPERIMENTAL DE WSN

### **HOJA DE EVALUACIÓN**

| Calificación:    |                  |

|------------------|------------------|

| Presidente       |                  |

| Fdo.: Presidente |                  |

| Vocal            | Secretario/a     |

| Fdo.: Vocal      | Fdo.: Secretario |

Fecha: Julio 2015

## Índice de Contenidos

| CAPÍTULO 1: | INTRODUCCIÓN                                          | 1          |

|-------------|-------------------------------------------------------|------------|

| 1.1 ANTEG   | CEDENTES                                              | 1          |

| 1.2 Овјет   | IVOS                                                  | 5          |

| 1.3 Soluc   | CIÓN ADOPTADA                                         | 7          |

| 1.4 ESTRU   | ICTURA DE LA MEMORIA                                  | 8          |

| CAPÍTULO 2: | DESCRIPCIÓN HARDWARE                                  | 11         |

| 2.1 INTRO   | DUCCIÓN                                               | 11         |

|             |                                                       |            |

|             | JLOS SENSORES INALÁMBRICOS.                           |            |

| 2.3 MICRO   | DCONTROLADOR ATMEL AT90CAN.                           |            |

| 2.3.1       | Descripción general.                                  | 15         |

| 2.3.2       | La arquitectura AVR                                   | 17         |

| 2.3.3       | Diagrama de bloques del microcontrolador AT90CAN128   | 19         |

| 2.4 Func    | ONALIDADES DEL MICROCONTROLADOR AT90CAN128.           | 22         |

| 2.4.1       | Puertos de entrada/salida de propósito general (GPIO) | 23         |

| 2.4.1.      | 1 Configuración del Pin                               | 25         |

| 2.4.2       | USART                                                 | 27         |

| 2.4.2.      | 1 Generación de Reloj                                 | <b>2</b> 9 |

| 2.4.2.      | 2 Formato de la trama                                 | 31         |

| 2.4.2.      | 3 Transmisor                                          | 32         |

| 2.4.2.      | 4 Receptor                                            | 34         |

| 2.4.2.      | 5 Descripción de registros                            | 35         |

| 2.4.3       | CAN                                                   | 40         |

| 2.4.3.      | 1 Protocolo CAN                                       | 41         |

| 2.4.3.      | 2 Controlador CAN                                     | 44         |

| 2.4.3.      | 3 Objetos de mensajes (MOb)                           | 45         |

| 2.4.3.      | 4 Interrupciones                                      | 48         |

| 2.4.3.      | 5 Descripción de los registros generales              | 48         |

| 2.4.3.      | 6 Descripción de los registros MOb                    | 52         |

| 2.4.4       | Bootloader                                            | 57         |

| CAPÍTULO 3: | DESARROLLO SOFTWARE                                   | 63         |

| 3.1 INTRO   | DUCCIÓN                                               | 63         |

| 3.2     | DESCI  | RIPCIÓN GENERAL.                           | 63    |

|---------|--------|--------------------------------------------|-------|

| 3.3     | Siste  | MA DE INTERRUPCIONES.                      | 66    |

| 3.      | 3.1    | Vector de interrupción CAN                 | 66    |

| 3.      | 3.2    | Vector de interrupción USART: transmisión. | 68    |

| 3.      | 3.3    | Vector de interrupción USART: recepción.   | 71    |

| 3.4     | Biblio | OTECA CAN                                  | 74    |

| 3.      | 4.1    | Configuración previa.                      | 75    |

| 3.      | 4.2    | Funciones públicas: configuración del bus. | 75    |

| 3.      | 4.3    | Funciones públicas: transmisión.           | 76    |

| 3.      | 4.4    | Funciones públicas: recepción.             | 77    |

| 3.5     | APLIC  | ACIÓN ROUTER.                              | 78    |

| 3.6     | APLIC  | ACIÓN BOOTLOADER                           | 83    |

| CAPÍTUI | LO 4:  | RESULTADOS                                 | 91    |

| CAPÍTUI | LO 5:  | CONCLUSIONES Y LÍNEAS FUTURAS              | 101   |

| 5.1     | Conc   | LUSIONES                                   | 101   |

| 5.2     | LÍNEA  | S FUTURAS.                                 | . 103 |

| REFERE  | NCIAS  | BIBLIOGRÁFICAS                             | .105  |

| PLIEGO  | DE CO  | NDICIONES                                  | . 107 |

| PL.1    | Co     | ONDICIONES HARDWARE                        | 107   |

| PL.2    | Co     | ONDICIONES SOFTWARE                        | .107  |

| PRESUP  | UESTO  | )                                          | 109   |

| P.1     | RECU   | RSOS MATERIALES                            | 109   |

| P.      | 1.1    | Recursos Hardware.                         | .109  |

| P.      | 1.2    | Recursos Software.                         | .110  |

| P.2     | TRABA  | AJO TARIFADO POR TIEMPO EMPLEADO.          | .111  |

| P.3     | Мате   | RIAL FUNGIBLE.                             | .112  |

| P.4     | Costi  | ES DE REDACCIÓN DEL TRABAJO FIN DE GRADO.  | .113  |

| P.5     | Dere   | CHOS DE VISADO DEL COITT                   | .114  |

| P.6     | Costi  | ES DE TRAMITACIÓN Y ENVÍO                  | .114  |

| P.7     | APLIC  | ación de impuestos.                        | 115   |

| ANEXO   | I. CO  | ONTENIDO DEL CD-ROM                        | .117  |

| A.I.I I | Estruc | TURA DEL CD-ROM.                           | 117   |

# Índice de Figuras

| FIGURA 1.1. WIRELESS SENSOR NETWORK                                          | 2  |

|------------------------------------------------------------------------------|----|

| Figura 1.2. Configuración en bus                                             | 5  |

| Figura 1.3. Estructura de la plataforma                                      | 7  |

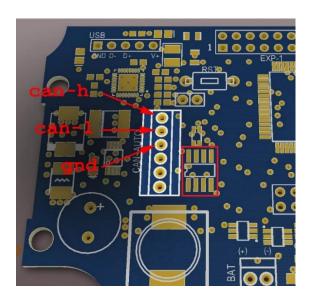

| Figura 2.1. PCB de los módulos sensores inalámbricos                         | 12 |

| FIGURA 2.2. CHIP FT232R                                                      | 13 |

| Figura 2.3. Esquemático del circuito USB a UART                              | 13 |

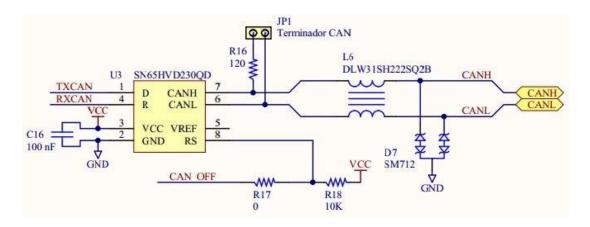

| Figura 2.4. Chip SN65HVD255                                                  | 14 |

| Figura 2.5. Conector CAN                                                     | 14 |

| Figura 2.6. Esquemático del circuito transceptor del CAN                     | 15 |

| FIGURA 2.7. ATMEL AT90CAN128 MICROCONTROLLER                                 | 17 |

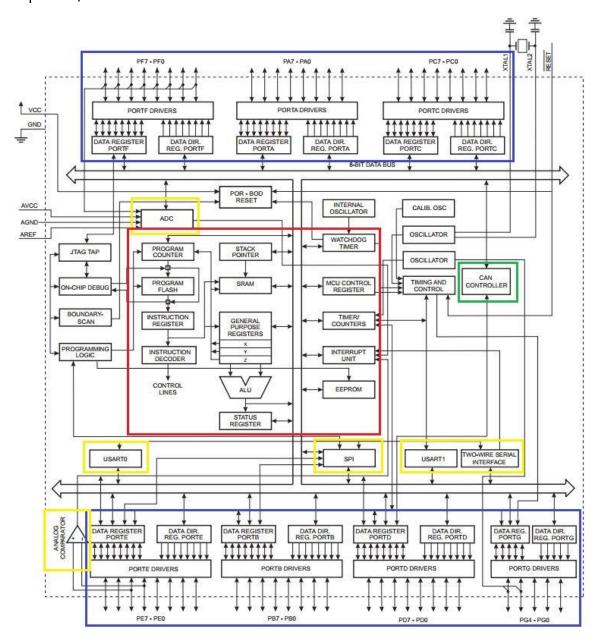

| Figura 2.8. Diagrama de Bloques del microcontrolador AT90CAN128              | 20 |

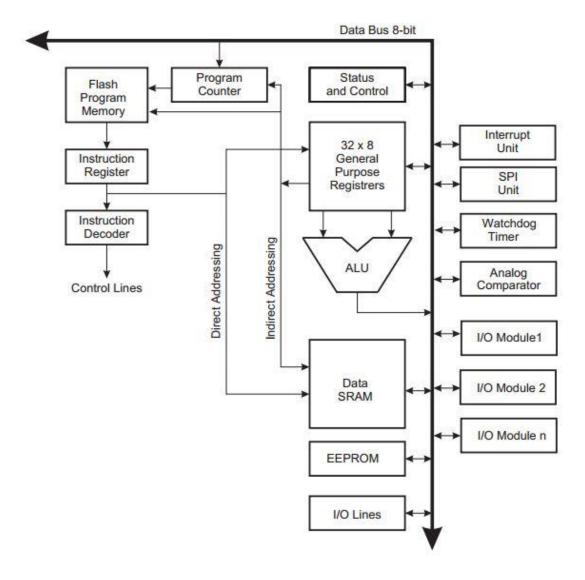

| Figura 2.9. Arquitectura AVR                                                 | 22 |

| FIGURA 2.10. ESQUEMÁTICO EQUIVALENTE DE UN PIN I/O                           | 23 |

| Figura 2.11. I/O Digital General                                             | 25 |

| Figura 2.12. Descripción de registros de los Puertos I/O                     | 26 |

| Figura 2.13. Diagrama de bloques de la USART                                 | 28 |

| Figura 2.14. Lógica de generación de la señal de reloj de la USART           | 30 |

| Figura 2.15. Ecuaciones para calcular la configuración de la tasa de baudios | 31 |

| Figura 2.16. Formato de trama                                                | 31 |

| Figura 2.17. Registro de datos I/O de la USART                               | 35 |

| Figura 2.18. Registro de Estado y de Control A                               | 36 |

| Figura 2.19. Registro de Estado y de Control B                               | 37 |

| Figura 2.20. Registro de Estado y de Control C                               | 38 |

| Figura 2.21. Configuración del bit UMSELn                                    | 38 |

| Figura 2.22. Configuración de los bits UPMn                                  | 39 |

| Figura 2.23. Configuración del bit USBSn                                     | 39 |

| Figura 2.24. Configuración de los bits UCSZn                                 | 40 |

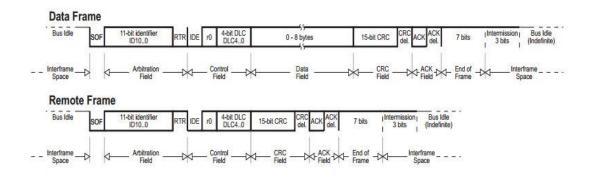

| Figura 2.25. Trama CAN estándar                                              | 42 |

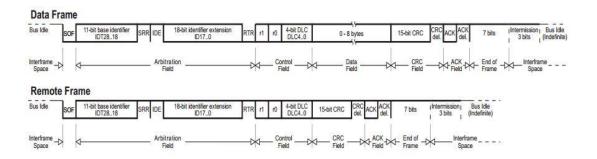

| Figura 2.26. Trama CAN extendida                                             | 43 |

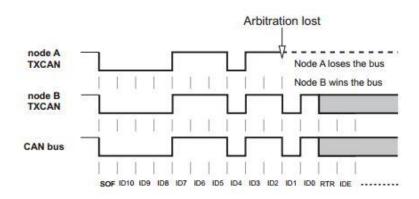

| Figura 2.27. Arbitraje del bus                                               | 44 |

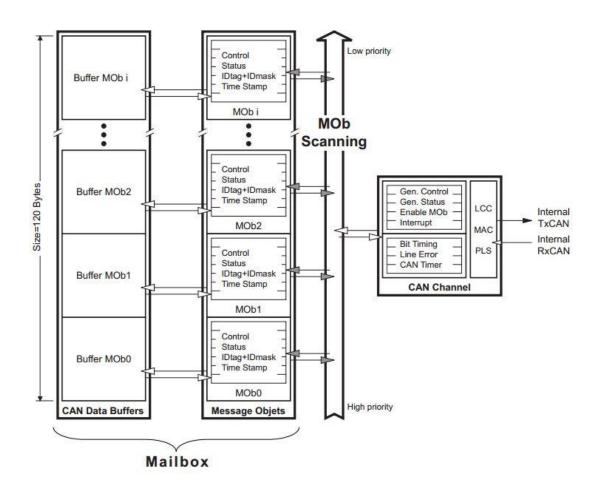

| Figura 2.28. Estructura del controlador CAN                                  | 45 |

| FIGURA 2.29. CONFIGURACIÓN DE LOS MOBS                                    | 46         |

|---------------------------------------------------------------------------|------------|

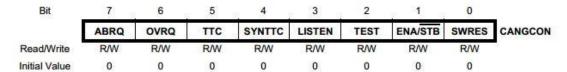

| Figura 2.30. Registro de control general                                  | 49         |

| FIGURA 2.31. REGISTRO DE INTERRUPCIONES GENERALES                         | 49         |

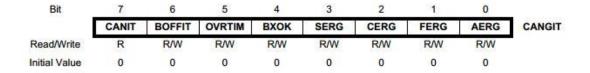

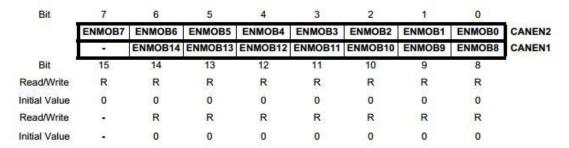

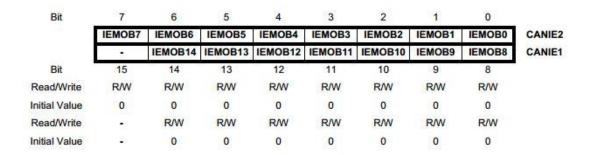

| Figura 2.32. Registro de habilitación de interrupciones generales         | 50         |

| Figura 2.33. Registros de habilitación de los MObs.                       | 51         |

| Figura 2.34. Registros de habilitación de las interrupciones de los MObs  | 51         |

| Figura 2.35. Registro de página MOb                                       | 52         |

| Figura 2.36. Registro de estado del MOb                                   | 53         |

| FIGURA 2.37. REGISTRO DE CONTROL Y DLC DEL MOB                            | 53         |

| Figura 2.38. Registro de identificador                                    | 54         |

| Figura 2.39. Registro de máscara del identificador                        | 56         |

| Figura 2.40. Ejemplo de máscara                                           | 57         |

| Figura 2.41. Registro de datos del mensaje                                | 57         |

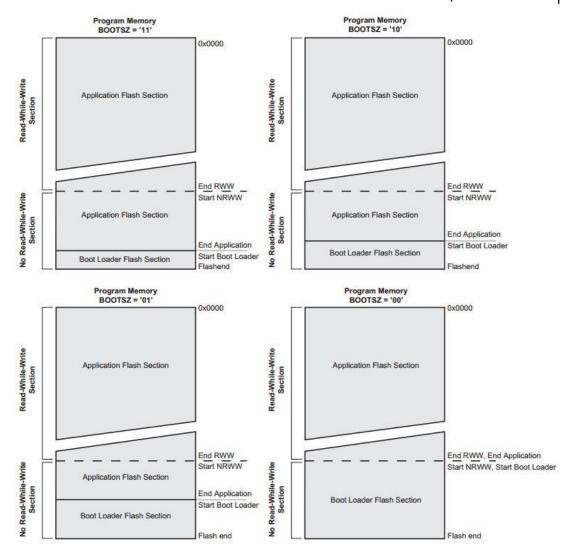

| FIGURA 2.42. SECCIONES DE LA MEMORIA FLASH                                | 59         |

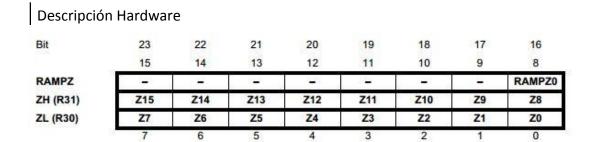

| Figura 2.43. Puntero Z                                                    | 60         |

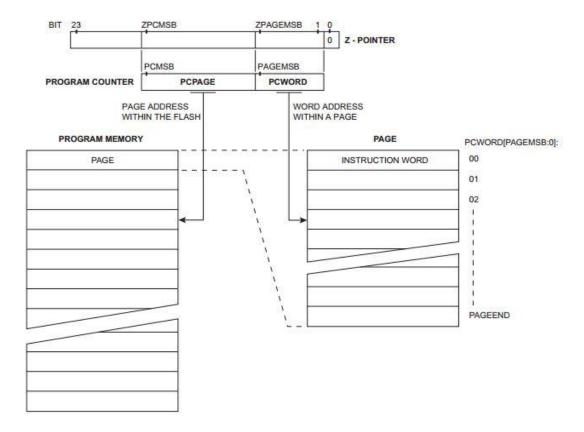

| Figura 2.44. Páginas de la memoria Flash                                  | 60         |

| FIGURA 2.45. DIRECCIONAMIENTO DE LA MEMORIA FLASH DURANTE SPM             | 61         |

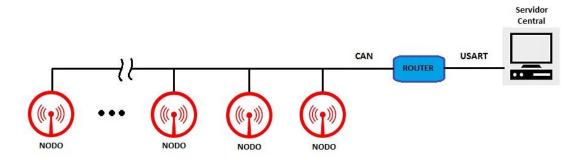

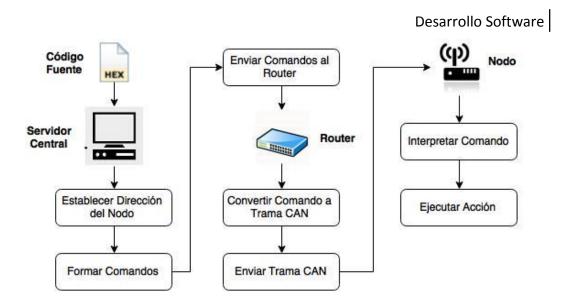

| FIGURA 3.1. ESTRUCTURA DE LA PLATAFORMA                                   | 64         |

| Figura 3.2. Diagrama de flujo de la programación de un nodo               | 65         |

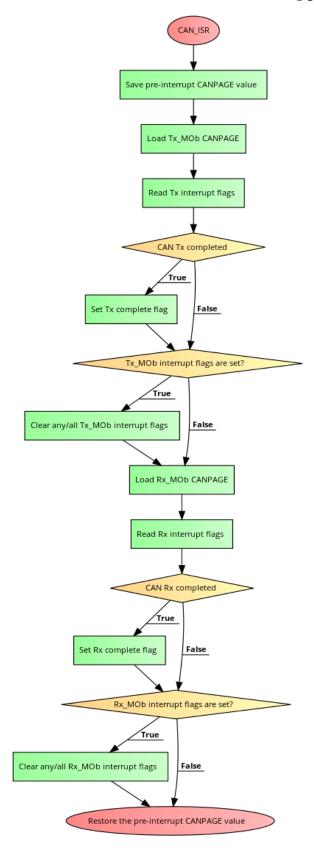

| Figura 3.3. Diagrama de flujo de la rutina de servicio CAN                | 67         |

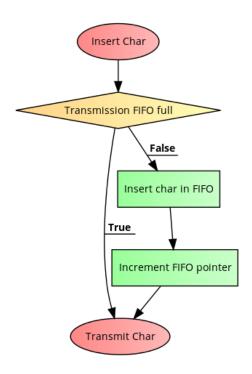

| Figura 3.4. Diagrama de flujo de la función insertTxFIFO                  | 69         |

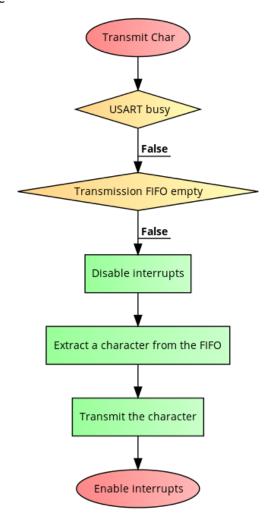

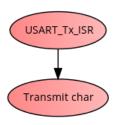

| Figura 3.5. Diagrama de flujo de la función TxChar                        | 70         |

| Figura 3.6. Diagrama de flujo de la rutina de servicio USART: transmisión | 71         |

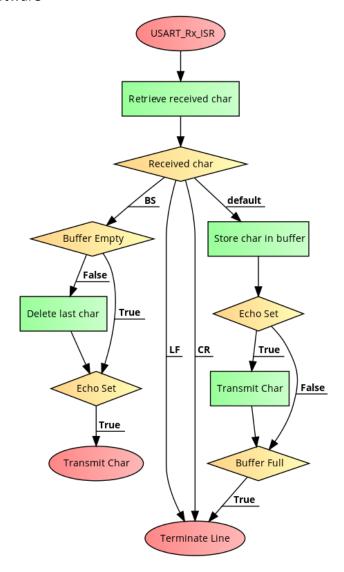

| FIGURA 3.7. DIAGRAMA DE FLUJO DE LA RUTINA DE SERVICIO USART: RECEPCIÓN   | 72         |

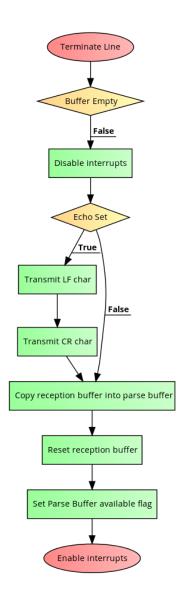

| Figura 3.8. Diagrama de flujo de la función terminateRx                   | 73         |

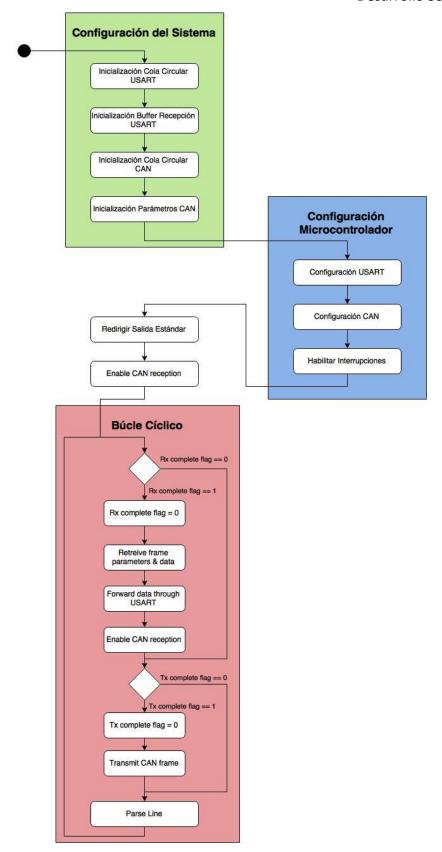

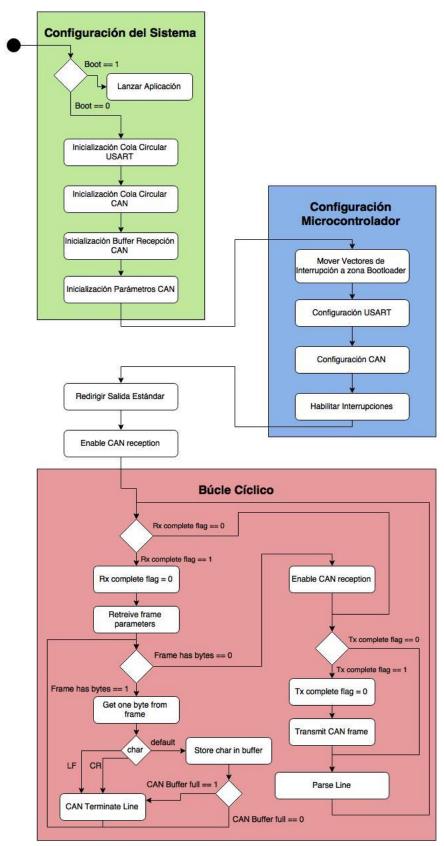

| Figura 3.9. Diagrama de flujo de la aplicación router                     | <b>7</b> 9 |

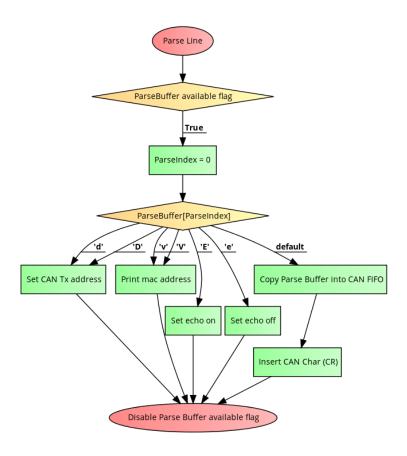

| Figura 3.10. Diagrama de flujo de la función parseLine                    | 82         |

| FIGURA 3.11. DIAGRAMA DE FLUJO DE LA APLICACIÓN BOOTLOADER                | 84         |

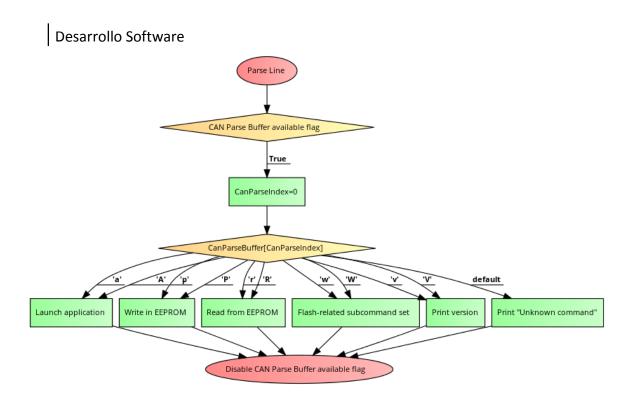

| Figura 3.12. Diagrama de flujo de la función parseLine                    | 88         |

| FIGURA 4.1. MONTAJE PRÁCTICO DE LA PLATAFORMA EXPERIMENTAL                | 91         |

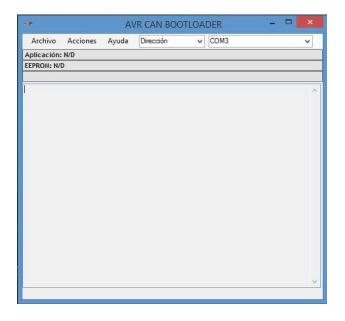

| Figura 4.2. Interfaz aplicación Servidor                                  | 93         |

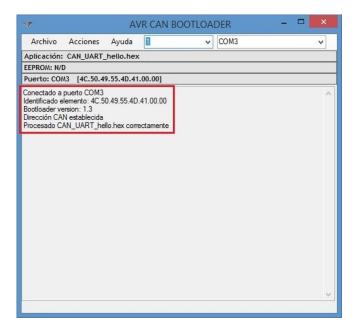

| FIGURA 4.3. CONEXIÓN CON EL ROUTER                                        | 93         |

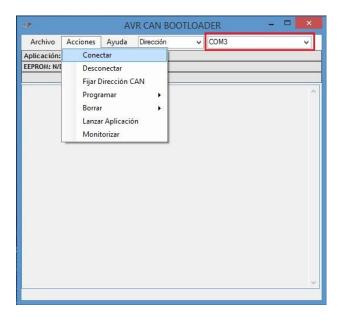

| FIGURA 4.4. ESTABLECER DIRECCIÓN CAN DEL NODO                             | 94         |

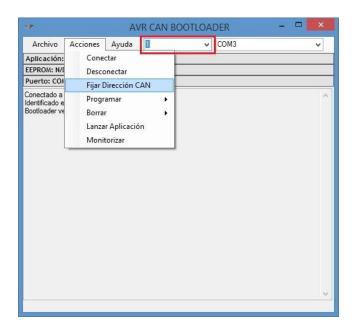

| FIGURA 4.5. CARGAR CÓDIGO FUENTE                                          | 95         |

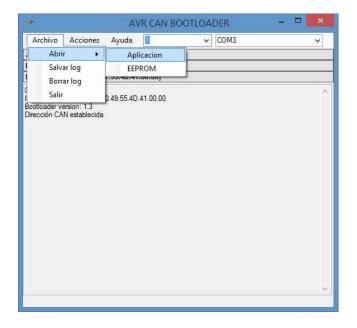

| FIGURA 4.6. FICHERO .HEX GENERADO POR EL COMPILADOR                       | 95         |

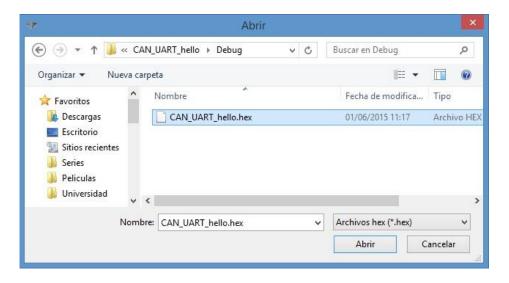

| Figura 4.7. Mensajes de estado de la aplicación Servidor       | 96 |

|----------------------------------------------------------------|----|

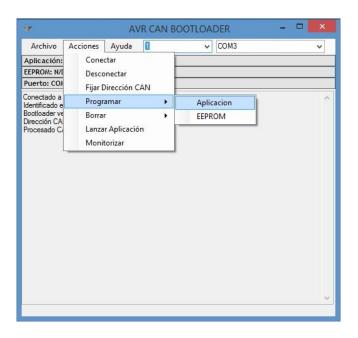

| Figura 4.8. Ejecutar programación del nodo                     | 96 |

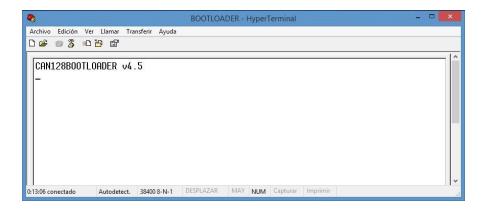

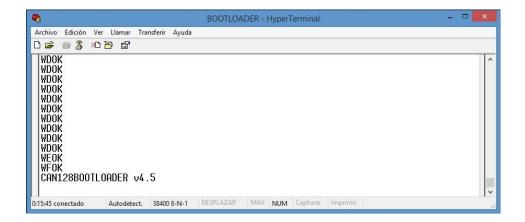

| FIGURA 4.9. MENSAJE INICIAL DE LA APLICACIÓN BOOTLOADER        | 97 |

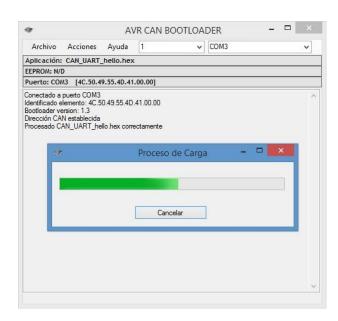

| Figura 4.10. Porcentaje completado de la programación del nodo | 97 |

| Figura 4.11. Mensajes de confirmación del nodo                 | 98 |

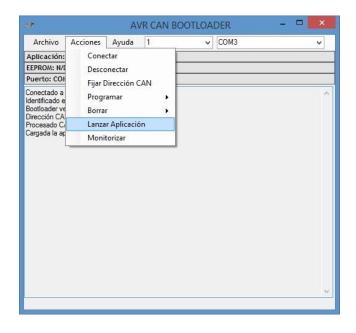

| Figura 4.12. Lanzar aplicación de usuario                      | 98 |

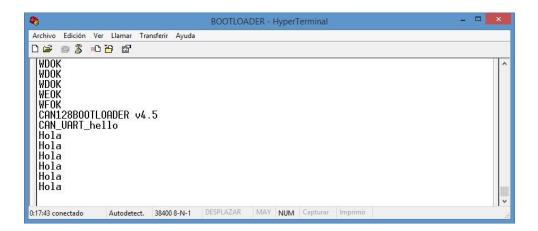

| Figura 4.13. Aplicación de ejemplo en el nodo                  | 99 |

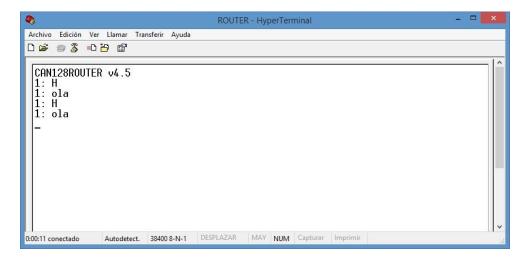

| FIGURA 4.14. MENSAJES RECIBIDOS EN EL ROUTER                   | 99 |

# Índice de Tablas

| Tabla PL.1. Elementos hardware                             | . 107 |

|------------------------------------------------------------|-------|

| Tabla PL.2. Elementos software                             | . 107 |

| Tabla P.1. Recursos hardware                               | 110   |

| Tabla P.2. Recursos software                               | 110   |

| Tabla P.3. Factor de corrección según las horas trabajadas | . 111 |

| Tabla P.4. Costes material fungible                        | . 112 |

| Tabla P.5. Presupuesto acumulado                           | . 113 |

| TABLA P.6. COSTE TOTAL DEL TRABAJO FIN DE GRADO            | . 115 |

### Resumen

En los últimos años, las redes de sensores inalámbricas han ganado mucha popularidad, experimentando un gran desarrollo y despliegue. La base de este auge proviene de maximizar la utilización de una de sus principales ventajas: la movilidad. Las redes de sensores inalámbricos presentan un gran potencial para aplicaciones en escenarios como el seguimiento y la vigilancia de objetivos militares, atenuación de desastres naturales, monitorización biomédica de la salud, exploración en entornos peligrosos y detección de seísmos, etc.

No obstante, este tipo de redes también presentan una serie de desventajas, siendo una de ellas el que, a pesar de que emplean tecnología inalámbrica, la programación y configuración de los nodos por lo general debe realizarse con el dispositivo físicamente conectado. También se hace muy difícil la depuración y el control de la red, ya que cuando se detecta que ocurre algún fallo en alguno de los nodos, la única forma que habría de comprobar qué es lo que está pasando, es desplazarse al lugar donde se encuentra dicho nodo y realizar una depuración *in situ*. Las desventajas que esto trae consigo son evidentes, ya que tener que ir de nodo en nodo verificando su funcionamiento puede representar un trabajo muy engorroso.

El objetivo principal del presente Trabajo Fin de Grado consiste en realizar una infraestructura que facilite la experimentación en el desarrollo de redes de sensores inalámbricos. La estructura estará conformada por una serie de nodos inalámbricos, los cuales estarán conectados a un bus CAN común, por un *router* y un servidor central. De esta forma, se dispondrá de un servidor desde el cual será posible programar todos los nodos conectados al bus, haciendo uso de un *router* que permitirá direccionar cada uno de ellos, además de poder recibir mensajes provenientes de dichos nodos. Para ello se desarrollará el firmware correspondiente a la aplicación *router* y a la aplicación *bootloader* de los nodos inalámbricos. Con ello se creará una infraestructura que permitirá programar y depurar los nodos de forma remota, concentrando los datos en un servidor central.

### **Abstract**

In recent years, wireless sensor networks have gained much popularity, experiencing a great development and deployment. The key to this growth comes from maximizing the use of one of its main advantages: mobility. Wireless sensor networks have great potential for applications in scenarios such as monitoring and surveillance of military targets, mitigation of natural disasters, biomedical health monitoring, exploration in hazardous environments, earthquakes detection, etc.

However, these kind of networks also have a number of disadvantages, one of which is that despite employing wireless technology, programming and configuration of the nodes generally has to be performed physically connected to the device. It is also very difficult to debug and control the network, because when a failure in one of the nodes is detected, the only way to check what is going on would be to go to the place where the node is located and start debugging it *in-situ*. The disadvantages this entails are obvious, as it might be a very cumbersome job to go from node to node checking their operation.

The main goal of this work is to develop an infrastructure that facilitates experimentation in the development of wireless sensor networks. The structure will consist of a series of wireless nodes which are connected to a common CAN bus, a router and a central server. Thereby a server will be available from which it will be possible to program all nodes connected to the bus, using a router that will address each of one of them, also the server can receive messages coming from these nodes. For this purpose the firmware corresponding to the router application and the wireless nodes bootloader application will be developed. This will create an infrastructure that will allow to program and debug nodes remotely, concentrating the data on a central server.

### **Acrónimos**

ACK ACKnowledge

ADC Analog-to-Digital Converter

ALU Arithmetic Logic Unit

AS Application Section

ASIC Aplication-Specific Integrated Circuit

BLS Bootloader Section

BS Back Space

CAN Controller Area Network

CD-ROM Compact Disc Read-Only Memory

CMOS Complementary Metal Oxide Semiconductor

COITT Colegio Oficial de Ingenieros Técnicos de Telecomunicación

CPU Central Processing Unit

CR Carry Return

CRC Cyclic Redundant Check

DLC Data Length Code

DSP Digital Signal Processor

EEPROM Electrically Erasable Programmable Read-Only Memory

EITE Escuela de Ingeniería de Telecomunicación y Electrónica

EOF End Of Frame

FIFO First In First Out

FPGA Field Programmable Gate Array

GPIO General Purpose Input Output

I2C Inter-Integrated Circuit

IDE IDentifier Extension

IEEE Institute of Electrical and Electronics Engineers

IFS Intermission Frame Space

IGIC Impuesto General Indirecto Canario

ISO International Organization for Standardization

JTAG Joint Test Action Group

LF Line Feed

LLC Logical Link Control

MAC Medium Access Control

MCU MicroController Unit

MIPS Million Instructions Per Second

MOb Message Object

OSI Open Systems Interconnection

PC Program Counter

PCB Printed Circuit Board

PLS Physical Signalling

PWM Pulse Width Modulation

QFN Quad Flat No Leads

RAM Random Access Memory

RF Radio Frecuencia

RISC Reduced Instruction Set Computer

RTC Real Time Counter

RTR Remote Transmission Request

SOF Start Of Frame

SPI Serial Peripheral Interface

SPM Store Program Memory

SRAM Static Random Access Memory

TFG Trabajo Fin de Grado

TQFP Thin Quad Flat Pack

ULPGC Universidad de Las Palmas de Gran Canaria

USB Universal Serial Bus

USART Universal Synchronous Asynchronous serial Receiver and Transmitter

WSN Wireless Sensor Network

# Capítulo 1: Introducción

### 1.1 Antecedentes.

Los avances en la tecnología de sistemas micro-electrónicos, comunicaciones inalámbricas, y electrónica digital han posibilitado el desarrollo de nodos sensores de bajo coste, reducido consumo de potencia y mínimo tamaño, que se comunican a distancia. Estos pequeños nodos sensores inalámbricos se fundamentan en la idea de redes de sensores basadas en el esfuerzo conjunto de un gran número de nodos [1, 2].

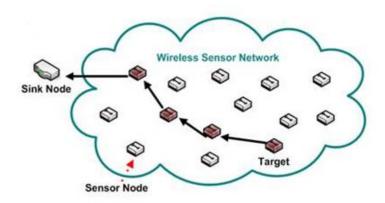

Una red de sensores inalámbricos (*Wireless Sensor Network*, WSN) consiste en una serie de nodos sensores distribuidos espacialmente con el objetivo de medir magnitudes físicas, como pueden ser sonido, temperatura, presión, etc. Dichos nodos sensores se comunican entre sí de forma inalámbrica con el fin de transmitir la información medida, por lo general a una unidad de procesamiento central, o bien para llevar a cabo algunas tareas de coordinación, como se representa en la Figura 1.1. Los componentes hardware más usuales en un nodo sensor incluyen un procesador empotrado, un transceptor de radio, fuente de alimentación y uno o más sensores [1, 2].

Figura 1.1. Wireless Sensor Network

En un nodo sensor, la funcionalidad del procesador empotrado es la de programar tareas, procesar datos y controlar el funcionamiento de los otros componentes hardware. Los tipos de procesadores empotrados que pueden ser usados en un nodo sensor incluyen Microcontroladores (MicroController Unit, MCU), Digital Signal Processor (DSP), Field Programmable Gate Array (FPGA) y Aplication-Specific Integrated Circuit (ASIC). De entre todas estas alternativas, los Microcontroladores han sido los más usados en la práctica debido a su flexibilidad para conectar con otros dispositivos, así como su reducido precio [3].

El transceptor es el responsable de la comunicación inalámbrica del nodo sensor. Las opciones disponibles como medio de comunicación inalámbrico son Radio Frecuencia (RF), Láser, e Infrarrojo. De ellas las comunicaciones basadas en RF encajan mejor en la mayoría de aplicaciones de WSN [3].

En un nodo sensor, el consumo de energía se produce principalmente debido a las tareas de detección, comunicación y procesamiento de los datos. Así, se requiere mayor energía para la comunicación que para el resto de las tareas, siendo las baterías la principal fuente de energía para los nodos sensores, por lo que, debido a su limitada capacidad,

minimizar el consumo de energía siempre es un aspecto clave durante las operaciones de los nodos en las WSNs [3].

Un sensor es un dispositivo hardware que ante un cambio en una magnitud física, como pueden ser temperatura, presión o humedad, genera como respuesta una señal eléctrica medible. La señal eléctrica analógica detectada por los sensores es digitalizada por un conversor analógico-digital (*Analog-to-Digital Converter*, ADC) y enviada al procesador empotrado para un procesamiento posterior. Debido a que un nodo sensor es un dispositivo micro-electrónico alimentado por una fuente de energía limitada, los sensores acoplados deben ser igualmente de reducido tamaño y tener muy poco consumo de energía. Un nodo sensor puede tener varios tipos de sensores integrados dentro, o conectados al nodo [3].

En los últimos años, las redes de sensores inalámbricos han ganado mucha popularidad, experimentando un gran desarrollo y despliegue acrecentado conforme al aumento de las capacidades tecnológicas de fabricación de sistemas integrados y al desarrollo de nuevos estándares y estructuras de comunicación. La base de este auge proviene de maximizar la utilización de una de sus principales ventajas: la movilidad. Haciendo uso de este tipo de redes, se elimina la necesidad de usar cables para la transferencia de datos entre dispositivos, dotando de una gran flexibilidad a la red, y por tanto, incrementando su eficiencia y productividad, independientemente del lugar donde ésta se encuentre instalada. La flexibilidad en el despliegue es una propiedad fundamental de los dispositivos que empleen este tipo de redes, y que está cada vez más presente en la sociedad actual [1-3].

Las redes de sensores inalámbricos presentan un gran potencial para aplicaciones en escenarios como el seguimiento y la vigilancia de objetivos militares, atenuación de desastres naturales, monitorización biomédica de la salud, exploración en entornos

#### Introducción

peligrosos y detección de seísmos. En el seguimiento y vigilancia de objetivos militares, una WSN puede ayudar en la detección de intrusos e identificación. En desastres naturales, los nodos sensores pueden detectar el entorno para predecir desastres con antelación a que ocurran. En aplicaciones biomédicas, la implantación quirúrgica de sensores ayudan a monitorizar la salud del paciente. Para la detección de seísmos, el despliegue de sensores ad-hoc a lo largo del área volcánica puede detectar el desarrollo de terremotos y erupciones [2].

Sin embargo, este tipo de redes también presentan una serie de desventajas, siendo una de ellas el que, a pesar de que emplean tecnología inalámbrica, la programación y configuración de los nodos debe realizarse por lo general con el dispositivo físicamente conectado. Esto implica que en redes que sean relativamente extensas puede resultar muy costoso en tiempo el ir programando nodo por nodo, sin tener en cuenta que la red puede estar desplegada en una superficie de gran tamaño, por lo que se requerirá estar desplazándose de un nodo a otro para realizar dicha programación [4, 5].

De modo similar, se hace muy difícil la depuración y el control de la WSN, ya que cuando se detecta que ocurre algún fallo en alguno de los nodos, la única forma que habría de comprobar qué es lo que está pasando, es desplazarse al lugar donde se encuentra dicho nodo y realizar una depuración *in situ*. Las desventajas que esto trae consigo son evidentes, ya que puede representar un trabajo muy engorroso tener que ir de nodo en nodo verificando su funcionamiento. Si además se dispone de una red ya desplegada, el proceso de detectar el error, corregirlo y verificar nuevamente el funcionamiento, lo que seguramente será necesario realizar varias veces, se puede fácilmente estimar que consumirá un tiempo significativo [4, 5].

Actualmente existen alternativas que permiten programar los nodos de forma inalámbrica, si bien esta solución no es demasiado eficaz, ya que si ocurre algún problema

con la transmisión, dicha programación no se llevará a cabo y no será posible saber qué es lo que ha pasado. En este trabajo se pretende dar una solución a los problemas comentados anteriormente con el desarrollo de una red experimental de sensores inalámbricos [4, 5].

### 1.2 Objetivos.

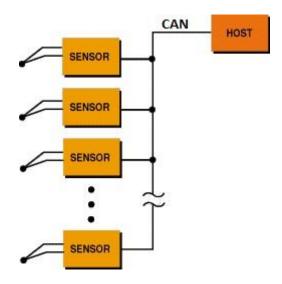

El objetivo principal del presente Trabajo Fin de Grado (TFG) consiste en desarrollar una infraestructura que facilite la experimentación en el desarrollo de redes de sensores inalámbricos. Una de las principales características de la red experimental de sensores inalámbricos relacionada con este trabajo será que estos sensores estarán conectados mediante un bus común a un Servidor central (*Host*), siendo el bus utilizado CAN (*Controller Area Network*) (Figura 1.2).

Figura 1.2. Configuración en bus

Los sensores proporcionarán constantemente información de su estado al servidor, con lo cual se busca facilitar las tareas de depuración y control que pueden resultar complejas en caso de que la red no esté cableada, ya que habría que ir nodo por nodo verificando su funcionamiento. Además, dichos informes de los nodos se almacenarán en

Introducción

el Servidor, permitiendo así verificar su funcionamiento en el momento en el que se desee, no necesariamente en tiempo real.

El tener la red cableada a través del bus permite programar cada nodo con un *firmware* de forma remota desde el Servidor, pudiendo desarrollar distintas versiones del mismo, y probarlas en diferentes nodos. Esto permite también que más de un usuario utilice la red al mismo tiempo, ya que al tener cada nodo un identificador, estos se pueden programar individualmente.

Por otro lado, al estar todos los datos concentrados en un servidor, es posible conectar dicho servidor a Internet, de tal forma que los usuarios de la red puedan acceder a ella de forma remota a través de un navegador web. Esta característica permite que cualquier usuario pueda acceder a la red sin estar físicamente en la misma ubicación, programe los sensores con el *firmware* que haya desarrollado, y finalmente analice los resultados obtenidos en el momento que desee, todo esto sin tener que desplazarse.

Así, en este TFG se van a implementar las funciones básicas de programación y monitorización que permitan crear una plataforma experimental que facilitará la realización de pruebas en redes de sensores inalámbricos de una manera mucho más práctica de cara al usuario. Facilitará la tarea del programador, ya que éste sólo tendrá que centrarse en el desarrollo del *firmware* y no en la implementación de la red de prueba. Además, ofrecerá varias ventajas frente a las redes completamente inalámbricas a la hora de programar los nodos, realizar la depuración, recoger los resultados, y facilidad de acceso a la red. También será muy escalable, ya que será posible realizar pruebas iniciales en unos pocos nodos y luego pasar a una red masiva de elementos sin ninguna dificultad. Otro objetivo con el que se ha pensado este TFG es de cara a la docencia y las prácticas de los estudiantes de la Escuela de Ingeniería de Telecomunicación y Electrónica (EITE) de la Universidad de Las Palmas de Gran Canaria (ULPGC), ya que permitirá al profesor asignarle

unos determinados nodos a cada alumno. Estos podrán realizar sus prácticas en dichos nodos y el profesor podrá analizar los resultados obtenidos por cada alumno, dado que estarán almacenados en el Servidor, permitiendo así una evaluación más precisa de las prácticas.

Para el desarrollo de este TFG se parte de unos módulos sensores inalámbricos que han sido desarrollados previamente por los profesores tutores en su labor de investigación, siendo estos los nodos sobre los cuales se trabajará. Una característica de estos módulos es que están basados en el microcontrolador AT90CAN128 de Atmel, el cual posee una interfaz CAN, además de una sección de memoria y funcionalidades destinadas especialmente a la implementación del *bootloader*, características convenientes para llevar a cabo el presente TFG.

### 1.3 Solución adoptada.

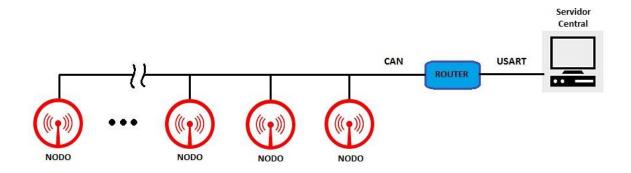

En la Figura 1.3 se puede ver un diagrama de bloques de la solución adoptada. En él se representan los diferentes elementos que componen el sistema y en los cuales se basa este Trabajo Fin de Grado.

Figura 1.3. Estructura de la plataforma

#### Introducción

En primer lugar, en el Servidor central se toma el código fuente desarrollado, se analiza y se divide en pequeños fragmentos de código. En segundo lugar se selecciona la dirección del nodo que se desea programar y se envía al *router* un comando que fija esa dirección. El tercer paso consiste en tomar los fragmentos de código, formar con ellos los distintos comandos que posteriormente deben interpretar los nodos, y enviarlos al *router*. En cuarto lugar el *router* recibe los comandos del servidor a través de la USART (*Universal Synchronous Asynchronous serial Receiver and Transmitter*), los convierte en tramas CAN, y los envía por este bus a la dirección previamente establecida. En quinto lugar los nodos, una vez hayan recibido un comando, lo interpretan y llevan a cabo la tarea correspondiente. Por último, cualquiera de los nodos puede enviar mensajes al Servidor a través del *router*; si este es el caso el *router* toma la trama CAN recibida, la convierte en un mensaje serie, y lo envía al servidor a través de la USART.

### 1.4 Estructura de la memoria.

La memoria de este Trabajo Fin de Grado está estructurada en cinco capítulos. Aparte se encuentra incluida una lista de Acrónimos, situada al comienzo del documento, así como una lista de Referencias Bibliográficas, Pliego de Condiciones, el Presupuesto y los Anexos que se encuentran localizados al final de la memoria.

El primer capítulo presenta una introducción a las redes de sensores inalámbricos, incluyendo una descripción general de los elementos que la componen, así como de sus principales ventajas, campos de aplicación y problemas relativos al desarrollo de *firmware* para este tipo de redes. A continuación se plantean los objetivos de este Trabajo Fin de Grado, describiendo brevemente la plataforma experimental en la que se engloba el desarrollo a realizar.

En el segundo capítulo se realiza una descripción del hardware utilizado, haciendo especial hincapié en el microcontrolador Atmel AT90CAN128, elemento principal en la realización de este Trabajo Fin de Grado. De él se describen sus características más importantes, prestando especial atención a aquellas que se han utilizado durante el desarrollo del proyecto, y que básicamente son el controlador CAN, la USART, la zona de Bootloader, y los pines GPIO (General Purpose Input Output).

En el tercer capítulo se comienza con una breve descripción general de la plataforma. A continuación se explica detalladamente el sistema de interrupciones empleado. Además también se introduce la biblioteca CAN desarrollada como parte de este Trabajo Fin de Grado, que será puesta a disposición de los usuarios. Por último, se describe el funcionamiento de la aplicación *router* y la aplicación *bootloader* implementadas, explicando detalladamente cada una de las partes en las que se divide el programa ejecutado por el microcontrolador.

En el cuarto capítulo, tras haber completado el desarrollo *firmware*, se describen las pruebas realizadas para comprobar el correcto funcionamiento de la plataforma.

El quinto capítulo está dedicado a las conclusiones obtenidas tras haber completado los objetivos propuestos para el presente Trabajo Fin de Grado, así como a las líneas futuras.

Introducción

# Capítulo 2:

# Descripción Hardware

### 2.1 Introducción.

En este capítulo se pretenden introducir los distintos elementos hardware que componen la plataforma experimental sobre la que se basa el presente TFG. Se comienza con una descripción general de los módulos sensores inalámbricos, haciéndose hincapié en las partes relativas a este TFG. A continuación se presenta una introducción del microcontrolador Atmel AT90CAN128, el cual ha sido empleado en este Trabajo Fin de Grado, realizándose en primer lugar una descripción general del mismo para finalmente, centrarse en los bloques de los cuales se ha hecho uso.

### 2.2 Módulos sensores inalámbricos.

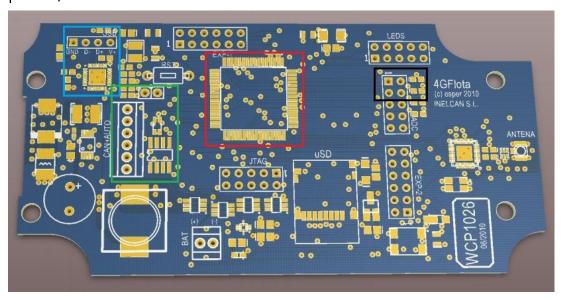

Para el desarrollo de este TFG se han utilizado unos módulos sensores inalámbricos que han sido desarrollados previamente por los profesores tutores en su labor de investigación, siendo los dispositivos sobre los cuales se trabajará. Una característica de estos módulos es que están basados en el microcontrolador AT90CAN128 de Atmel. En la Figura 2.1 se puede observar la placa de circuito impreso (*Printed Circuit Board*, PCB) de estos módulos.

Figura 2.1. PCB de los módulos sensores inalámbricos

Enmarcados con los distintos bloques de colores se han señalado los elementos que intervienen directamente en este TFG. En color rojo se ha señalado la zona donde va colocado el microcontrolador AT90CAN128. El color negro señala el pin con el cual se indica al microcontrolador que se debe iniciar en modo *bootloader*. El color azul corresponde a la conexión USB (*Universal Serial Bus*) con su correspondiente interfaz hacia la USART. Por último en color verde están los elementos relacionados con el CAN.

El pin para seleccionar el modo *bootloader* se encuentra ubicado en uno de los puertos de expansión de la placa. Colocando un *jumper* entre este pin y masa, se le indica al microcontrolador que se debe iniciar en modo *bootloader*, en caso contrario saltará directamente a la aplicación de usuario.

El conector USB está compuesto por cuatro pines. Uno correspondiente a la alimentación, otro para masa y los dos restantes corresponden al par diferencial de datos. A través de este conector se puede alimentar a toda la placa. La señal de datos se lleva a un chip que hace de interfaz entre USB y la USART. El FT232R es un chip que simplifica los

diseños USB a serie, reduce el número de componentes externos necesarios al integrar en el dispositivo una EEPROM, resistencias de terminación USB y un circuito integrado de reloj que no requiere de cristal externo. En la Figura 2.2 se presenta una imagen del chip FT232R en su formato QFN (*Quad Flat No Leads*) [6].

Figura 2.2. Chip FT232R

En la Figura 2.3 se puede observar el esquemático de cómo está conectado este chip con el microcontrolador y con el conector USB. Por un lado se tiene la señal de datos USB (USBDP, USBDM), que una vez pasa por la interfaz se convierte en las señales del transmisor y receptor de la USART (TXD, RXD).

Figura 2.3. Esquemático del circuito USB a UART

#### Descripción Hardware

El microcontrolador AT90CAN128 dispone de un controlador pero no de un transceptor CAN, por lo tanto es necesario añadirlo de forma externa. El dispositivo utilizado en este caso es el chip SN65HVD255, del cual se puede observar una imagen en la Figura 2.4. Este es un chip que cumple con los requerimientos del estándar ISO 11898, pudiendo soportar hasta 1Mbps de velocidad en buses altamente cargados y proporciona varias características de protección que permiten aumentar la robustez del bus [7].

Figura 2.4. Chip SN65HVD255

En la Figura 2.5 se puede observar la posición del transceptor externo que se ha añadido en los módulos, así como la de los pines correspondientes a las conexiones de CAN\_H y CAN\_L, en los cuales se ha colocado una clema para facilitar su conexionado.

Figura 2.5. Conector CAN

Por último, se incluye en la Figura 2.6 el esquemático de cómo se ha realizado el conexionado del transceptor. En ella se puede observar cómo por un lado se tienen las señales de transmisión y recepción CAN del microcontrolador que una vez pasan por el transceptor se convierten en CAN\_H y CAN\_L como establece el estándar. Destacar también que se dispone de un *jumper* con el cual se establece si se añade o se quita la terminación resistiva, dependiendo si se trata de un nodo final o uno intermedio respectivamente.

Figura 2.6. Esquemático del circuito transceptor del CAN

### 2.3 Microcontrolador Atmel AT90CAN.

### 2.3.1 Descripción general.

El microcontrolador Atmel AT90CAN32/64/128 es un microcontrolador CMOS de 8 bits de propósito general y bajo consumo [8]. El diseño de su núcleo está basado en la arquitectura RISC (*Reduced Instruction Set Computer*) de AVR. La arquitectura del núcleo AVR combina la utilización de un amplio repertorio de instrucciones con un banco de 32 registros de propósito general. Estos 32 registros están directamente conectados a la ALU (*Arithmetic Logic Unit*), permitiendo realizar operaciones entre dos registros independientes en un sólo ciclo de reloj.

En este TFG se hará uso de la versión AT90CAN128, la cual consta de 128KBytes de memoria de programa, implementados en una memoria tipo *Flash*, 4KBytes de memoria tipo *EEPROM* (*Electrically Erasable Programmable Read-Only Memory*), 4KBytes de memoria SRAM (*Static Random Access Memory*). Además cuenta con 53 líneas de entrada/salida de propósito general (*General Purpose Input Output*, GPIO), 32 registros de propósito general, un controlador CAN, contador de tiempo real (*Real Time Counter*, RTC), 4 Timers/Contadores flexibles con modo de comparación y PWM (*Pulse Width Modulation*). También cuenta con hardware USART (*Universal Synchronous Asynchronous serial Receiver and Transmitter*), hardware SPI (*Serial Peripheral Interface*), una interfaz serie de dos cables (*Inter-Integrated Circuit*, I2C), conversor analógico-digital (*Analog to Digital Converter*, ADC) de 8 canales y resolución de 10 bits con la opción de incluir una etapa de entrada diferencial con ganancia programable, *Watchdog* programable con oscilador interno, interfaz JTAG (*Joint Test Action Group*) para test conforme al estándar IEEE 1149.1, también usada para acceder al sistema de depuración en chip y la programación.

El sistema está dotado con 5 modos distintos de ahorro de energía. El modo *Idle* detiene la CPU (*Central Processing Unit*) mientras permite que la RAM, *timer/counters*, puertos SPI/CAN y el sistema de interrupciones siga funcionando. El modo *Power-down* almacena el contenido de los registros pero detiene el oscilador, deshabilitando el resto de funciones del chip hasta la próxima interrupción o *reset*. En el modo *Power-save*, el *timer* asíncrono continua contando, permitiendo al usuario mantener un *timer* de referencia, mientras que el resto del dispositivo está inactivo. El bloque conversor analógico-digital dispone de un modo especial de operación, *ADC Noise Reduction*, que desconecta todo el hardware del sistema, excepto el contador asíncrono, con el fin de realizar una conversión fiable, aportando el mínimo ruido posible a la medida realizada. El último modo es el *Standby*, en el que el oscilador, ya sea basado en cristal o un resonador, continúa operando mientras que el resto del dispositivo está inactivo, lo que permite un arranque muy rápido del dispositivo a la vez que un bajo consumo de potencia.

En la Figura 2.7 se puede observar una imagen del microcontrolador Atmel AT90CAN128 en el formato TQFP (*Thin Quad Flat Pack*), que es el que ha sido utilizado, el cual consta de 64 pines.

Figura 2.7. Atmel AT90CAN128 Microcontroller

# 2.3.2 La arquitectura AVR.

La arquitectura AVR es una modificación de la arquitectura RISC de 8 bits existente para microcontroladores. Fue desarrollada por Atmel en 1996; concretamente, fue inventada por dos estudiantes del *Norwegian Institute of Technology*, y posteriormente refinada y desarrollada en Atmel Norway, la empresa subsidiaria de Atmel, fundada entonces por los dos diseñadores del chip. Los de AVR fueron los primeros microcontroladores que empleaban una memoria *Flash* integrada para almacenar el programa [9-11].

AVR es una CPU de arquitectura Harvard, en la que la memoria de programa y la memoria de datos se encuentran separadas físicamente. Sin embargo, existen una serie de instrucciones especiales que permite el acceso a la memoria de programa durante la ejecución del mismo.

La arquitectura AVR está diseñada para soportar frecuencias de reloj de hasta 20MHz, pudiendo llegar algunos dispositivos hasta los 32MHz. Sin embargo, las aplicaciones que requieran un bajo consumo requerirán menores frecuencias de reloj. Algunas series de microcontroladores AVR integran un oscilador en el chip, eliminando así la necesidad de utilizar una fuente de reloj externa, o un circuito resonador. Con el fin de incrementar las posibilidades del sistema, también se incluye un *prescaler* para la señal de reloj, de forma que es posible dividir la frecuencia de reloj principal por un valor máximo de 256. El valor del *prescaler* puede ser configurado en el momento de la programación o durante la ejecución de la aplicación, aportando máxima flexibilidad. Casi todas las instrucciones ejecutadas en el AVR duran 1 ciclo de reloj, lo que permite realizar 1 MIPS (*Million Instructions Per Second*) por MHz.

En cuanto a memoria, tanto *Flash* como EEPROM y SRAM, se encuentran integradas en el hardware disponible en el chip. De este modo se elimina la necesidad de emplear memorias externas. Sin embargo, algunos dispositivos disponen de un bus, que permite hacer uso de una memoria externa, estando ésta mapeada en la memoria del chip.

En la mayoría de las variantes de la arquitectura AVR, los 32 registros de uso general se encuentran mapeados en las primeras 32 direcciones de memoria, y los 64 registros de entrada-salida se encuentran mapeados consecutivamente a los de uso general. De este modo, la concatenación de los 32 registros de uso general con los registros de entrada-salida y la memoria de datos conforman un espacio de direcciones unificado, accesible mediante operaciones de carga/almacenamiento.

Las CPU AVR poseen un *pipeline* simple de 2 etapas (cargar y ejecutar), haciendo posible que la mayor parte de las instrucciones se ejecuten en un solo ciclo de reloj. Esta característica particular hace que esta arquitectura resulte significativamente más rápida frente a otros microcontroladores de 8 bits con otras arquitecturas.

AVR fue diseñado desde un comienzo para la ejecución eficiente de código C compilado. Como este lenguaje utiliza punteros para el manejo de variables en memoria, los tres últimos pares de registros internos del procesador AVR se usan como punteros de 16 bits al espacio de memoria externa, bajo los nombres X, Y y Z. Este compromiso se aplica en arquitecturas de ocho bits debido a que el tamaño de palabra de 8 bits tan solo puede direccionar 256 registros.

# 2.3.3 Diagrama de bloques del microcontrolador AT90CAN128.

En la Figura 2.8 se muestra el diagrama de bloques completo del microcontrolador Atmel AT90CAN128. En él se pueden diferenciar los distintos bloques funcionales, englobados mediante cuadros coloreados atendiendo a la función que desempeñan.

Figura 2.8. Diagrama de Bloques del microcontrolador AT90CAN128

Los bloques encuadrados en azul se encuentran formados por los puertos de entrada y salida del dispositivo. El Atmel AT90CAN128 posee 53 líneas de entrada/salida que pueden ser utilizadas para propósito general, y que se encuentran organizadas en 6 puertos de 8 bits y un puerto de 5 bits, denotados como PORTA, PORTB, PORTC, PORTD, PORTE, PORTF y PORTG, respectivamente. Las líneas de uso general comparten conexión

con los diferentes bloques funcionales implementados en el hardware del dispositivo, de forma que éstos poseen conexión con el exterior.

Los bloques resaltados en color amarillo son algunos de los distintos bloques funcionales implementados en el chip. Dichos bloques poseen una variada funcionalidad, que va desde la USART, SPI, bloque de conversor analógico-digital (ADC), timers, etc. Por otro lado el bloque resaltado en color verde se corresponde con el controlador CAN, siendo este el bloque más importante para nuestro TFG.

En la Figura 2.9 se muestra el diagrama de bloques del núcleo del microcontrolador, que se corresponde con el bloque resaltado en rojo en la Figura 2.8.

Figura 2.9. Arquitectura AVR

# 2.4 Funcionalidades del microcontrolador AT90CAN128.

En este apartado se describen las características principales de los bloques funcionales más significativos del microcontrolador Atmel AT90CAN128, y que han sido empleados en el desarrollo de este Trabajo Fin de Grado.

# 2.4.1 Puertos de entrada/salida de propósito general (GPIO).

Como se ha mencionado anteriormente, el microcontrolador AT90CAN128 cuenta con 53 líneas de entrada/salida de propósito general (GPIO). Dichas líneas se encuentran agrupadas en 6 puertos de 8 bits y un puerto de 5 bits, denotados como PORTA, PORTB, PORTC, PORTD, PORTE, PORTF y PORTG, respectivamente. Además cada una de ellas cuenta con una resistencia de *pull-up* que brinda mayor capacidad de control sobre las líneas GPIO [8].

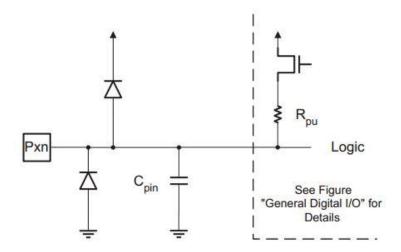

Todos los puertos tienen la funcionalidad *Read-Modify-Write* cuando se utilizan como puertos de entrada/salida de propósito general. Esto quiere decir que la dirección de uno de los pines del puerto puede ser cambiada sin modificar accidentalmente la del resto de los pines del puerto. Lo mismo ocurre al habilitar o deshabilitar las resistencias de *pull-up*. En la Figura 2.10 se puede observar el esquema simplificado de un pin.

Figura 2.10. Esquemático equivalente de un Pin I/O

Cada puerto tiene reservadas tres posiciones de la memoria de entrada/salida. Una para *Data Register* (PORTx), otra para *Data Direction Register* (DDRx), y otra para *Port Input Pins* (PINx). La letra minúscula "x" representa la letra correspondiente al puerto (A, B, C, D,

E, F y G). El registro *Port Input Pins* es de sólo lectura, mientras que *Data Register* y *Data Direction Register* son de lectura/escritura. Sin embargo, escribir un "1" lógico en uno de los bits del registro PINx resultará en una conmutación en el bit correspondiente en el *Data Register*.

La mayoría de los pines están multiplexados con funciones alternativas de los periféricos implementados en el dispositivo. Aclarar que habilitar en uno de los pines de un puerto la función alternativa, no interfiere con el uso del resto de los pines como entradas-salidas de propósito general.

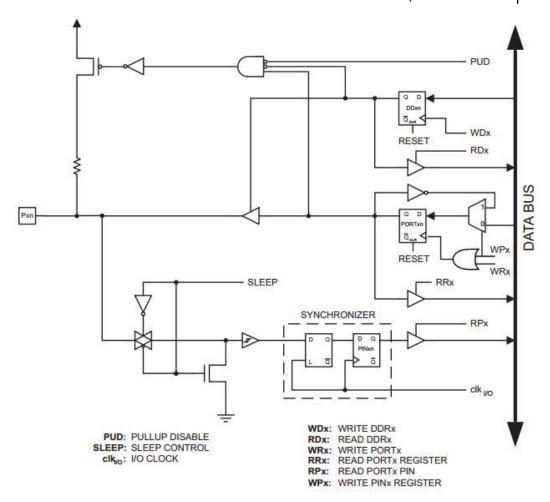

A continuación, en la Figura 2.11 se presenta el esquema general de un pin cuando éste está actuando como entrada/salida. En él se puede observar que tanto la entrada como la salida se pasan a través de un *latch*, y además que la dirección del pin, ya sea entrada o salida, se controla mediante *buffers* tri-estado.

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports.

Figura 2.11. I/O Digital General

# 2.4.1.1 Configuración del Pin.

Cada pin de los puertos consiste en un bit de tres registros distintos: DDxn, PORTxn, y PINxn, siendo la letra minúscula "n" el número correspondiente del pin. Como se muestra en el ejemplo de la Figura 2.12, los bits DDxn se acceden en la dirección DDRx del espacio de direcciones de entrada/salida, los bits PORTxn en la dirección PORTx, y los bits PINxn en la dirección PINx.

#### Port G Data Register - PORTG PORTG4 PORTG3 PORTG2 PORTG0 PORTG1 R/W R/W R/W R R/W R/W Read/Write R R Initial Value 0 0 0 0 0 0 0 0 Port G Data Direction Register - DDRG Bit 2 DDG3 DDG2 DDG1 DDG0 DDRG R/W Initial Value 0 0 0 0 0 Port G Input Pins Address - PING Bit 6 3 2 PING4 PING3 PING2 PING1 PING0 PING Read/Write R R/W R/W Initial Value 0 0 0 N/A N/A N/A N/A N/A

Figura 2.12. Descripción de registros de los Puertos I/O

El bit DDxn en el registro DDRx selecciona la dirección del pin. Si en DDxn se escribe un "1" lógico, Pxn es configurado como un pin de salida. Mientras que si se escribe un "0" lógico, Pxn se configura como un pin de entrada.

Si en el bit PORTxn del registro PORTx se escribe un "1" lógico cuando el pin se encuentra configurado como entrada, se activa la resistencia de *pull-up*. Para desactivar dicha resistencia, se debe escribir un "0" lógico en PORTxn o el pin debe ser configurado como salida.

Si en el bit PORTxn se escribe un "1" lógico cuando el pin se encuentra configurado como salida, dicho pin se lleva a nivel alto, mientras que si se escribe un "0" lógico el pin se lleva a nivel bajo.

Escribir un "1" lógico en el bit PINxn conmuta el valor de PORTxn, independientemente del valor de DDRxn, mientras que la lectura de este registro indica el estado del pin.

# 2.4.2 USART.

El microcontrolador AT90CAN128 dispone de dos USART (*Universal Synchronous Asynchronous serial Receiver and Transmitter*), que es un dispositivo de comunicación serie altamente flexible [8, 11]. Los diferentes registros que se explican a continuación se han descrito de forma general, siendo la letra minúscula "n" el número de la USART correspondiente, en este caso 0 o 1. Sus principales características son:

- Modo de operación Full-Duplex. (Registros independientes para la transmisión y recepción)

- Funcionamiento síncrono o asíncrono.

- Generador de la tasa de transferencia de alta resolución.

- Soporta tramas serie con 5, 6, 7, 8 y 9 bits de datos, y 1 o 2 bits de stop.

- Generación de la paridad y chequeo de paridad soportado por hardware.

- Filtrado de ruido que incluye detección de falsos bits de start y filtro digital paso bajo.

- Tres vectores de interrupción independientes para transmisión completada,

buffer de transmisión vacío y recepción completada.

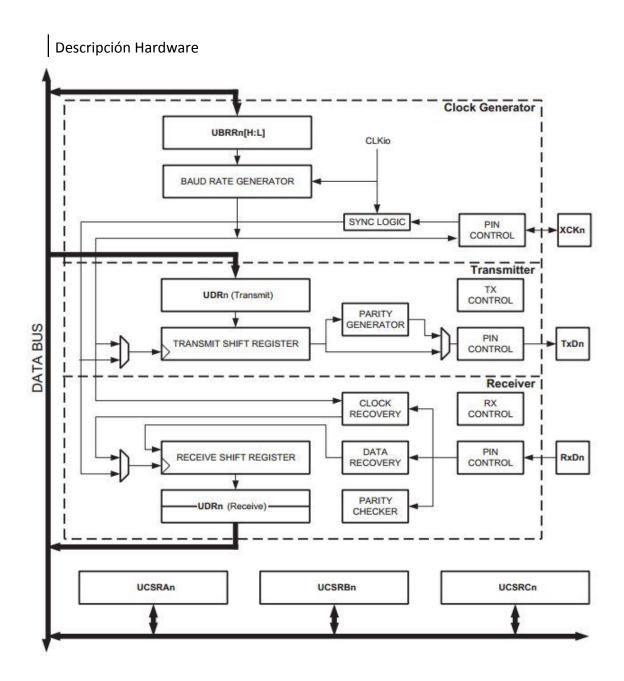

En la Figura 2.13 se presenta un diagrama de bloques simplificado de la USART. Los registros y pines accesibles por la CPU se muestran en negrita.

Figura 2.13. Diagrama de bloques de la USART

Los cuadros señalados con líneas discontinuas separan los tres bloques principales de la USART, mencionándolos desde arriba hacia abajo: Generador de Reloj, Transmisor y Receptor. Los registros de control son compartidos por todas las unidades. La lógica del Generador de Reloj (*Clock Generator*) consiste en lógica de sincronización para la entrada de señal de reloj externa utilizada como esclavo en modo síncrono, y el generador de la tasa de baudios. El pin XCKn (Reloj de transferencia) se usa sólo en el modo de transferencia

síncrono. El Transmisor (*Transmitter*) consiste en un único buffer de escritura (UDRn), un registro de desplazamiento serie (*Shift Register*), un generador de paridad (*Parity Generator*) y lógica de control (*TX Control*) para gestionar diferentes formatos de trama. El buffer de escritura permite una transferencia continua de datos sin retardo entre tramas. El Receptor (*Receiver*) es el bloque más complejo de la USART debido a sus unidades de recuperación de reloj (*Clock Recovery*) y de datos (*Data Recovery*). Estas unidades se utilizan para la recepción asíncrona de datos. El Receptor además incluye un comprobador de paridad (*Parity Checker*), lógica de control (*RX Control*), un registro de desplazamiento (*Shift Register*) y un buffer de recepción (UDRn). El Receptor soporta el mismo formato de tramas que el Transmisor, además puede detectar errores de trama (*Frame Error*), desbordamiento de datos (*Data OverRun*) y errores de paridad (*Parity Errors*).

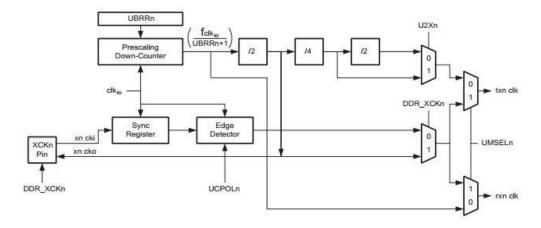

# 2.4.2.1 Generación de Reloj.

La lógica de generación de la señal de reloj genera el reloj de referencia para el Transmisor y el Receptor. La USART soporta cuatro modos de operación: Normal asíncrono, Asíncrono a doble velocidad, Maestro síncrono y Esclavo síncrono. El bit UMSELn en el registro de estado y control C de la USART (*Control and Status Register*, UCSRnC) selecciona entre los modos de operación síncrono y asíncrono. En la Figura 2.14 se muestra el diagrama de bloques del generador de reloj de la USART.

Figura 2.14. Lógica de generación de la señal de reloj de la USART

Cuando se utiliza el modo síncrono (UMSELn = 1), el registro DDR para el pin XCKn (DDR\_XCKn) controla si la señal de reloj es interna (Maestro) o externa (Esclavo). El pin XCKn sólo está activo cuando se utiliza el modo de operación síncrono. La generación interna del reloj se utiliza para los modos de operación asíncrono y maestro síncrono.

El registro de tasa de baudios (*Baud Rate Register*, UBRRn) y el contador regresivo conectado a él funcionan como un *prescaler* programable. El contador regresivo, ejecutándose a la velocidad del reloj del sistema (f<sub>clkio</sub>), se carga con el valor de UBRRn cada vez que el contador llega a cero, o bien cuando se escribe en el registro UBRRn. Se genera un pulso de reloj cada vez que contador llega al valor cero. Este reloj es la salida del generador de la tasa de baudios (= f<sub>clkio</sub>/(UBRRn+1)). El Transmisor divide la salida de este reloj por 2, 8 o 16 dependiendo del modo de operación. Por otro lado este reloj es usado directamente por las unidades de recuperación de datos y reloj del Receptor. Sin embargo, las unidades de recuperación utilizan una máquina de estados que usa 2, 8 o 16 estados en función del modo de operación establecido. En la Figura 2.15 se muestran las distintas ecuaciones para calcular tanto la tasa de baudios como el valor del registro UBRRn.

| Operating Mode                            | Equation for Calculating Baud<br>Rate <sup>(1)</sup> | Equation for Calculating<br>UBRRn Value |  |  |

|-------------------------------------------|------------------------------------------------------|-----------------------------------------|--|--|

| Asynchronous Normal mode (U2Xn = 0)       | $BAUD = \frac{f_{CLKio}}{16(UBRRn + 1)}$             | $UBRRn = \frac{f_{CLKio}}{16BAUD} - 1$  |  |  |

| Asynchronous Double Speed mode (U2Xn = 1) | $BAUD = \frac{f_{CLKio}}{8(UBRRn + 1)}$              | $UBRRn = \frac{f_{CLKio}}{8BAUD} - 1$   |  |  |

| Synchronous Master mode                   | $BAUD = \frac{f_{CLKio}}{2(UBRRn + 1)}$              | $UBRRn = \frac{f_{CLKio}}{2BAUD} - 1$   |  |  |

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps)

BAUD Baud rate (in bits per second, bps).

fclk<sub>io</sub> System I/O Clock frequency.

UBRRn Contents of the UBRRnH and UBRRnL Registers, (0-4095).

Figura 2.15. Ecuaciones para calcular la configuración de la tasa de baudios

# 2.4.2.2 Formato de la trama.

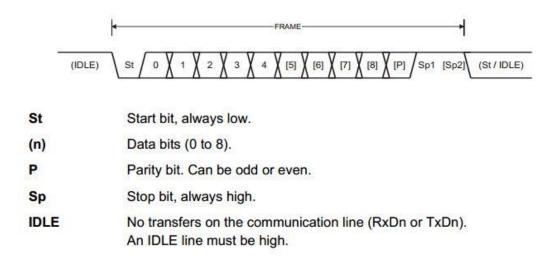

Una trama serie se define como una serie de bits de datos en conjunto con bits de sincronización (bits de *start* y *stop*). Opcionalmente se puede incluir un bit de paridad para comprobación de errores. En la Figura 2.16 se observa gráficamente este formato, donde los bits dentro de corchetes son opcionales.

Figura 2.16. Formato de trama

La USART acepta las 30 combinaciones de los siguientes formatos de trama válidos:

- 1 bit de start.

- 5, 6, 7, 8 o 9 bits de datos.

- Bit de paridad par, impar o sin paridad.

- 1 o 2 bits de stop.

Una trama comienza con el bit de *start* seguido del bit de datos menos significativo. A continuación se encuentran los siguientes bits de datos, hasta un máximo de 9, terminando con el bit más significativo. Si está habilitado, el bit de paridad se inserta justo después de los bits de datos, antes de los bits de *stop*. Cuando una trama es transmitida completamente, se puede transmitir directamente una nueva trama, o la línea de comunicación se puede llevar a un estado desocupado (nivel alto).

#### 2.4.2.3 Transmisor.

La USART debe ser inicializada antes de que pueda tener lugar cualquier comunicación. El proceso de inicialización normalmente consiste en el establecimiento de la tasa de baudios, el formato de la trama, y en la habilitación del Transmisor o del Receptor dependiendo del uso que se le vaya a dar. Si la USART va a ser gestionada mediante interrupciones, el *flag* de interrupciones globales (*Global Interrupt Flag*) debe estar desactivado, y las interrupciones globales deshabilitadas, en el momento de hacer la inicialización.

El Transmisor de la USART se habilita al establecer el bit de habilitar transmisión (*Transmit Enable*, TXENn) en el registro UCSRnB a nivel alto. Una vez habilitado, el modo de operación normal del puerto en el pin TxDn es ignorado por la USART y se le asigna la función de salida serie del Transmisor. La tasa de baudios, el modo de operación y el formato de la trama deben ser establecidos antes de hacer ninguna transmisión.

Una transmisión se inicia cargando los datos a transmitir en el buffer de transmisión. Los datos que se encuentran en el buffer serán movidos al Registro de Desplazamiento cuando éste se encuentre listo para enviar una nueva trama. El Registro de Desplazamiento se carga con los nuevos datos si se encuentra en un estado inactivo (no hay transmisiones en curso), o inmediatamente después de que se haya transmitido el último bit de *stop* de la trama anterior.

El Transmisor de la USART cuenta con dos *flags* que indican su estado: registro de datos vacío (*USART Data Register Empty*, UDREn) y transmisión completada (*Transmit Complete*, TXCn). Ambos *flags* pueden ser utilizados para generar interrupciones.

El *flag* de registro de datos vacío (UDREn) indica si el buffer de transmisión está listo para recibir nuevos datos. Este bit se activa cuando el buffer está vacío, y se desactiva cuando contiene datos para transmitir que no han sido pasados aún al Registro de Desplazamiento.

El flag de transmisión completada (TXCn) se activa cuando en el Registro de Desplazamiento la trama completa ha sido desplazada hacia la salida y no hay datos nuevos en el buffer de transmisión. El flag TXCn es automáticamente desactivado cuando la interrupción de transmisión completada se ejecuta, si bien también puede ser desactivado escribiendo un "1" lógico en el bit correspondiente al flag. Cuando el bit de habilitación de la interrupción por transmisión completada (*Transmit Complete Interrupt Enable*, TXCIEn) en el registro UCSRnB se pone a nivel lógico alto, se ejecutará dicha interrupción siempre que el flag TXCn se active, asumiendo que las interrupciones globales está habilitadas.

La acción de deshabilitar el Transmisor (establecer el bit TXENn a nivel bajo) no será efectiva hasta que la transmisión en curso y las pendientes se completen, por ejemplo

cuando el Registro de Desplazamiento y el buffer de transmisión no contengan datos para transmitir. Una vez deshabilitado, el Transmisor no continuará sobrescribiendo la función del pin TxDn.

# 2.4.2.4 Receptor.

El Receptor de la USART se habilita al establecer el bit de habilitar recepción (*Receive Enable*, RXENn) en el registro UCSRnB a "1" lógico. Una vez habilitado, el modo de operación normal del puerto en el pin RxDn es ignorado por la USART y se le asigna la función de entrada serie del Receptor. La tasa de baudios, el modo de operación y el formato de la trama deben ser establecidos antes de realizar ninguna transmisión.

El Receptor comienza la recepción de datos cuando detecta un bit de *start* válido en el bus. Cada bit que le sigue al bit de *start* será muestreado a la velocidad de la tasa de baudios, y luego será desplazado hacia el Registro de Desplazamiento de recepción hasta que se reciba el primer bit de *stop* de la trama. Un segundo bit de *stop* será ignorado por el receptor. Cuando se recibe el primer bit de *stop*, el Registro de Desplazamiento contiene una trama completa, la cual será trasladada al buffer de recepción. El buffer de recepción puede ser leído en la dirección UDRn.

El Receptor de la USART cuenta con un *flag* que indica su estado: recepción completada (*Receive Complete*, RXCn), el cual puede generar una interrupción.

El *flag* recepción completada (RXCn) es un indicador de si hay datos sin leer en el buffer de recepción. El *flag* se encuentra activado cuando se dispone de datos no leídos en el buffer de recepción, y desactivado cuando dicho buffer se encuentra vacío. Si el Receptor es deshabilitado (RXENn = 0) el contenido del buffer de recepción será borrado, y en consecuencia el *flag* RXCn se desactivará.

Cuando el bit de habilitación de la interrupción por recepción completada (*Receive Complete Interrupt Enable*, TXCIEn) en el registro UCSRnB se pone a "1" lógico, se ejecutará dicha interrupción siempre que el *flag* TXCn se active, asumiendo que las interrupciones globales están habilitadas. Cuando la recepción es gestionada mediante interrupciones, la rutina de servicio debe leer los datos recibidos en UDRn con el fin de desactivar el *flag* RXCn, de lo contrario se volverá a generar una nueva interrupción una vez finalice la rutina de servicio.

Al contrario del Transmisor, deshabilitar el Receptor tiene efecto inmediatamente. Por tanto se perderán los datos de cualquier recepción en curso. Una vez deshabilitado, el Receptor no continuará sobrescribiendo la función del pin RxDn y los datos que queden en el buffer de recepción se perderán.

# 2.4.2.5 Descripción de registros.

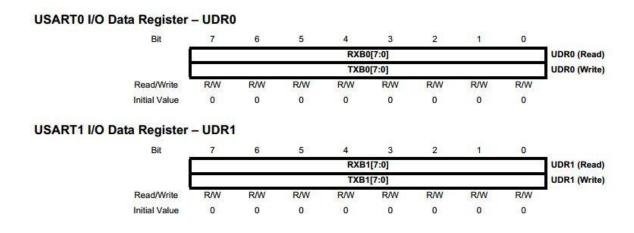

En este apartado se explicarán cada uno de los registros utilizados en la configuración y la gestión de la USART, así como la descripción del significado de los bits dentro de cada registro. Únicamente se explicarán los registros y bits relevantes a este TFG. En primer lugar se pueden observar los registros de datos en la Figura 2.17.

Figura 2.17. Registro de datos I/O de la USART

Initial Value

- Bit 7:0 RxBn7:0: Receive Data Buffer.

- Bit 7:0 TxBn7:0: Transmit Data Buffer.

Los buffers de recepción y transmisión de la USART comparten la misma dirección en el espacio de memoria, referido como USARTn Data Register o UDRn. El buffer de transmisión (TXBn) será el destino de los datos escritos en la dirección del registro UDRn, mientras que leer del registro UDRn devolverá el contenido del buffer de recepción (RXBn).

En las figuras que siguen a continuación se pueden observar los registros de estado y de control de la USART.

#### USART0 Control and Status Register A - UCSR0A UDRE0 DOR0 UPE0 RXC0 TXC0 FE0 U2X0 MPCMO **UCSR0A** Read/Write R/W R/W Initial Value 0 0 0 0 0 0 USART1 Control and Status Register A - UCSR1A Bit DOR1 TXC1 UDRE1 FE1 MPCM1 UCSR1A RXC1 UPE1 U2X1 R/W R/W Read/Write R R R R R R/W 0 0 0

Figura 2.18. Registro de Estado y de Control A

1

#### Bit 7 - RXCn: USARTn Receive Complete.

0

0

Este bit se activa cuando hay datos en el buffer de recepción que no han sido leídos, y se desactiva cuando el buffer de recepción se vacía. Si el Receptor se deshabilita, los datos que hayan en el buffer de recepción son descartados y por tanto el flag RXCn se desactiva. Este *flag* puede ser utilizado para generar una interrupción.

#### Bit 6 – TXCn: USARTn *Transmit Complete*.

Este bit se activa cuando la trama completa del Registro de Desplazamiento se ha desplazado hacia la salida y no hay nuevos datos en el buffer de transmisión. El flag TXCn

0

0

se desactiva automáticamente cuando la interrupción de transmisión completada se ejecuta, o bien escribiendo un "1" lógico en el bit correspondiente al *flag*. Este *flag* puede ser utilizado para generar una interrupción.

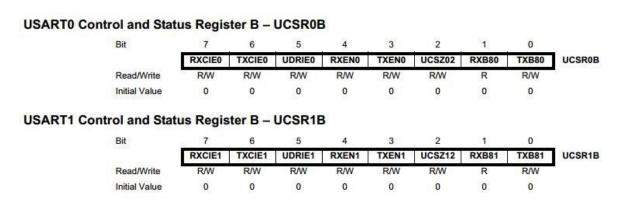

Figura 2.19. Registro de Estado y de Control B

#### • Bit 7 – RXCIEn: RX Complete Interrupt Enable.

Escribir un "1" lógico en este bit habilita la interrupción del *flag* RXCn. Se generará una interrupción de recepción completada sólo si el bit RXCIEn está a nivel alto, las interrupciones globales están habilitadas y el *flag* RXCn se encuentra activo.

#### • Bit 6 – TXCIEn: TX Complete Interrupt Enable.

Escribir un "1" lógico en este bit habilita la interrupción del flag TXCn. Se generará una interrupción de transmisión completada sólo si el bit TXCIEn está a nivel alto, las interrupciones globales están habilitadas y el *flag* TXCn se encuentra activo.

#### • Bit 4 - RXENn: Receiver Enable.

Escribir un "1" lógico en este bit habilita el Receptor de la USART. El Receptor ignorará el modo de operación normal del pin RxDn cuando está habilitado. Deshabilitar el Receptor descartará el contenido del buffer de recepción.

#### • Bit 3 – TXENn: Transmitter Enable.

Escribir un "1" lógico en este bit habilita el Transmisor de la USART. El Transmisor ignorará el modo de operación normal del pin TxDn cuando está habilitado. Deshabilitar el Transmisor no se hará efectivo hasta que se completen todas las transmisiones pendientes.

#### • Bit 2 - UCSZn2: Character Size.

Los bits UCSZn2 combinados con los bits UCSZn1:0 en el registro UCSRnC establecen el número de bits de datos para las tramas, tanto del Receptor como del Transmisor.

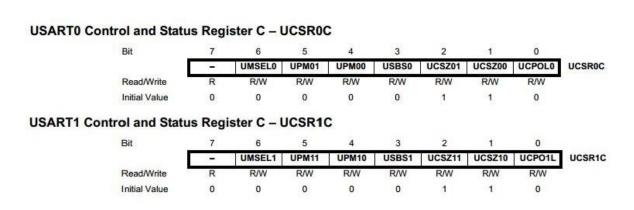

Figura 2.20. Registro de Estado y de Control C

#### • Bit 6 – UMSELn: USARTn Mode Select.

Este bit permite seleccionar entre los modos de operación síncrono y asíncrono.

| 4      | T.                     |

|--------|------------------------|

| UMSELn | Mode                   |

| 0      | Asynchronous Operation |

| 1      | Synchronous Operation  |

Figura 2.21. Configuración del bit UMSELn

#### • Bit 5:4 – UPMn1:0: Parity Mode.

Estos bits habilitan y establecen el tipo de generación y chequeo de paridad. Si está habilitada, el Transmisor automáticamente generará y enviará el bit de paridad correspondiente a los bits de datos enviados en cada trama. El Receptor por su parte genera la paridad de los datos recibidos y lo compara con el valor establecido en UPMn.

| UPMn1 | UPMn0 | Parity Mode          |  |

|-------|-------|----------------------|--|

| 0     | 0     | Disabled             |  |

| 0     | 1     | Reserved             |  |

| 1     | 0     | Enabled, Even Parity |  |

| 1     | 1     | Enabled, Odd Parity  |  |

Figura 2.22. Configuración de los bits UPMn

#### • Bit 3 – USBSn: Stop Bit Select.

Este bit selecciona el número de bits de *stop* a ser insertados por el Transmisor. El Receptor ignora esta configuración, ya que solamente utiliza el primer bit de *stop*.

| USBSn | Stop Bit(s) |

|-------|-------------|

| 0     | 1-bit       |

| 1     | 2-bit       |

Figura 2.23. Configuración del bit USBSn

# • Bit 2:1 – UCSZn1:0: Character Size.

Los bits UCSZn1:0, combinados con el bit UCSZn2 en el registro UCSRnB, establecen el número de bits de datos para las tramas, tanto del Receptor como del Transmisor.

| UCSZn2 | UCSZn1 | UCSZn0     | Character Size |  |

|--------|--------|------------|----------------|--|

| 0      | 0      | 0          | 5-bit          |  |

| 0      | 0      | 1          | 6-bit          |  |

| 0      | 1      | 0          | 7-bit          |  |

| 0      | 1      | 1          | 8-bit          |  |

| 1      | 0      | 0 Reserved |                |  |

| 1      | 0      | 1          | Reserved       |  |

| 1      | 1      | 0          | Reserved       |  |

| 1      | 1      | 1 9-bit    |                |  |

Figura 2.24. Configuración de los bits UCSZn

## 2.4.3 CAN.

El protocolo CAN (*Controller Area Network*) es un protocolo de tipo *broadcast*, serie y de tiempo real con un alto nivel de seguridad. El controlador CAN del AT90CAN128 es completamente compatible con la Especificación CAN 2.0 en sus versiones A y B [8]. Además proporciona las características necesarias para implementar el protocolo CAN de acuerdo con el modelo de referencia OSI de la ISO:

#### Capa de Enlace de Datos:

- Subcapa de control de enlace lógico (Logical Link Control, LLC).

- Subcapa de control de acceso al medio (*Medium Access Control*, MAC).

#### Capa Física:

• Subcapa de señalización física (*Physical Signalling*, PLS).

Este controlador CAN es capaz de gestionar todo tipo de tramas (*Data, Remote, Error* y *Overload*), además de una serie de características que se mencionan a continuación:

- Controlador CAN completo.

- Completamente compatible con el Estándar CAN rev 2.0 A y rev 2.0 B.

- 15 MOb (*Message Object*) con sus propios:

- o 11 bits de identificador (rev 2.0 A) y 29 bits de identificador (rev 2.0 B).

- o 11 bits de máscara (rev 2.0 A) y 29 bits de máscara (rev 2.0 B).

- Buffer de datos de 8 bytes.

- o Configuraciones de Tx, Rx, Buffer y Respuesta Automática.

- Máxima tasa de transferencia de 1Mbit/s a 8MHz.

### 2.4.3.1 Protocolo CAN.

El protocolo CAN es un estándar internacional definido en el ISO 11898 para alta velocidad y en el ISO 11519-2 para baja velocidad. CAN está basado en un mecanismo de comunicación *broadcast*. Esta comunicación *broadcast* se alcanza usando un protocolo de transmisión orientado a mensaje. Estos mensajes son identificados por un identificador, el cual debe ser único dentro de toda la red, y define, no sólo el contenido, sino también la prioridad del mensaje [12, 13].

La prioridad con la que se transmite un mensaje comparado con otro mensaje de menor prioridad se especifica mediante el identificador. Las prioridades se definen durante el diseño del sistema en forma de los correspondientes valores binarios y no puede ser cambiada dinámicamente. El identificador con el número binario más bajo posee la prioridad más alta.

Los conflictos en el acceso al bus se resuelven mediante un arbitraje bit a bit de los identificadores involucrados. Esto sucede de acuerdo con el mecanismo de AND cableada, a través del cual el estado dominante anula al estado recesivo. Todos los nodos con una transmisión recesiva pierden la competencia por el reparto del bus. Los perdedores automáticamente se convierten en receptores del mensaje con la prioridad más alta, y no vuelven a intentar transmitir hasta que el bus haya sido liberado.

El protocolo CAN soporta dos formatos de trama de los mensajes, que se diferencian básicamente en la longitud del identificador. La trama CAN estándar, también conocida como CAN 2.0 A, soporta una longitud de 11 bits para el identificador, mientras que la trama CAN extendida, también conocida como CAN 2.0 B, soporta una longitud de 29 bits para el identificador.

Figura 2.25. Trama CAN estándar

Un mensaje en el formato CAN estándar comienza con el "inicio de trama" (Start Of Frame, SOF). A esto le sigue el "campo de arbitraje" (Arbitration Field) que consiste en el identificador y el bit de "petición de transmisión remota" (Remote Transmission Request, RTR), utilizado para distinguir entre una trama de datos y una trama de petición de datos, llamada trama remota. A continuación está el "campo de control" (Control Field) el cual contiene el bit de "extensión de identificador" (IDentifier Extension, IDE) y el "código de longitud de datos" (Data Length Code, DLC), que se usa para indicar el número de bytes que siguen a continuación en el "campo de datos" (Data Field), el cual puede contener hasta un máximo de 8 bytes. La integridad de la trama se garantiza con el "código de redundancia cíclica" (Cyclic Redundant Check, CRC) que le sigue. El "campo de reconocimiento" (ACKnowledge Field, ACK) está compuesto por el bit de ACK y el delimitador de ACK. El bit de ACK se envía como un bit recesivo y es sobrescrito como un bit dominante por los receptores que hayan recibido la trama correctamente. Los mensajes correctos son reconocidos por los receptores sin importar la configuración del filtro de

aceptación de los mismos. El fin del mensaje es indicado por el "fin de trama" (*End Of Frame*, EOF). El "espacio de intervalo entre tramas" (*Intermission Frame Space*, IFS) es el número de bits mínimo que separa dos mensajes consecutivos. Si a continuación ningún nodo accede al bus, éste permanece inactivo.

Figura 2.26. Trama CAN extendida

Un mensaje en el formato CAN extendido es prácticamente igual al formato CAN estándar. La diferencia está en la longitud del identificador. El identificador se compone del identificador de 11 bits existente (base identifier) y una extensión de 18 bits (identifier extension). La distinción entre el formato estándar y el extendido se hace a través del bit IDE, el cual se transmite como dominante en caso de tratarse de una trama CAN estándar, y como recesivo en el otro caso.

Como los dos formatos tienen que coexistir en un mismo bus, se establece el mensaje que tiene la prioridad más alta en caso de colisión en el acceso al bus de dos formatos diferentes con el mismo identificador: El mensaje en formato CAN estándar siempre tiene prioridad sobre los mensajes en formato extendido.

Durante la transmisión, el arbitraje del bus se puede perder en favor de otro dispositivo con un identificador de mayor prioridad. Este concepto de arbitraje evita las colisiones de mensajes cuya transmisión comenzó de forma simultánea en varios nodos.

Por lo general, los conflictos de acceso al bus se resuelven en el campo de arbitraje a partir del valor del identificador. Si una trama de datos y una trama remota con el mismo identificador se envían al mismo tiempo, la trama de datos prevalece sobre la trama remota.

Figura 2.27. Arbitraje del bus

#### 2.4.3.2 Controlador CAN.

El controlador CAN implementado en el AT90CAN128 soporta la versión 2.0 B del estándar CAN. Este controlador CAN completo proporciona todo el hardware necesario para un filtrado de aceptación adecuado y la gestión de mensajes. Para cada mensaje a ser transmitido o recibido, este módulo contiene lo que se llama un "objeto de mensaje" (*Message Object*, MOb), en el cual se almacena toda la información relacionada con el mensaje (identificador, bytes de datos, etc.).

Durante la inicialización del periférico, la aplicación define qué MObs son para enviar y cuales para recibir. Sólo si el controlador CAN recibe un mensaje cuyo identificador coincide con uno de los identificadores programados en los MObs destinados a la recepción se guarda el mensaje y la aplicación es informada mediante una interrupción. Otra ventaja es que las tramas remotas entrantes pueden ser respondidas automáticamente por el controlador con la correspondiente trama de datos. De esta forma, la carga de la CPU se

reduce considerablemente en comparación con una solución CAN básica. Usando este controlador CAN completo, se pueden gestionar altas tasas de baudios y buses cargados con muchos mensajes.

Figura 2.28. Estructura del controlador CAN

# 2.4.3.3 Objetos de mensajes (MOb).

Un MOb describe una trama CAN, conteniendo toda la información para controlar una trama. Esto quiere decir que los MObs han sido definidos de forma que permitan describir un mensaje CAN como si fuera un objeto. Este dispositivo tiene 15 MObs, numerados del 0 al 14. Los MObs son independientes entre sí pero se le da prioridad al de menor número en caso de que se produzcan múltiples coincidencias. Cada MOb tiene su

propio campo para controlar el modo de operación. Antes de habilitar el periférico CAN, cada MOb debe ser configurado, ya que no existe un modo de operación por defecto. Los modos de operación se pueden observar en la Figura 2.29.

| MOb Configuration |     | Reply Valid | RTR Tag         | Operating Mode                             |  |  |

|-------------------|-----|-------------|-----------------|--------------------------------------------|--|--|

| 0                 | 0   | х           | X               | Disabled                                   |  |  |

|                   | х   | 0           | Tx Data Frame   |                                            |  |  |

| U                 | 0 1 | x           | 1               | Tx Remote Frame                            |  |  |

| 1 0               | х   | 0           | Rx Data Frame   |                                            |  |  |

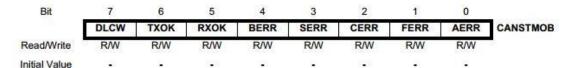

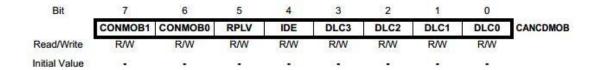

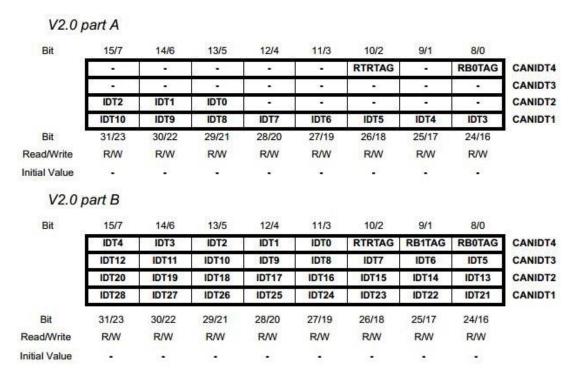

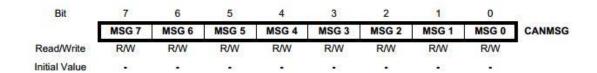

|                   | 0   |             | Rx Remote Frame |                                            |  |  |