## ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

DISEÑO E IMPLEMENTACIÓN DE UN PROTOTIPO HARDWARE PARA UN BANCO DE PRUEBAS DEL ESTÁNDAR AIS

Titulación: Grado en Ingeniería en Tecnologías de la

Telecomunicación

Autor: D. Nicolás Molina Padrón

Tutores: Dr. Francisco José Cabrera Almeida

Dr. Víctor Alexis Araña Pulido

Fecha: Julio de 2015

## ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

#### TRABAJO FIN DE GRADO

# DISEÑO E IMPLEMENTACIÓN DE UN PROTOTIPO HARDWARE PARA UN BANCO DE PRUEBAS DEL ESTÁNDAR AIS

#### HOJA DE FIRMAS

Firma de los tutores

Fdo. Dr. Francisco José Cabrera Almeida Fdo. Dr. Víctor Alexis Araña Pulido

Firma del alumno

Fdo. D. Nicolás Molina Padrón

Fecha: Julio de 2015

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

## DISEÑO E IMPLEMENTACIÓN DE UN PROTOTIPO HARDWARE PARA UN BANCO DE PRUEBAS DEL ESTÁNDAR AIS

## HOJA DE EVALUACIÓN

|         | Calificación: _ |         |            |       |       |

|---------|-----------------|---------|------------|-------|-------|

|         | Presidente      |         | Secretario |       | Vocal |

|         |                 |         |            |       |       |

| Fdo.: _ |                 | Fdo.: _ |            | Fdo.: |       |

Fecha: Julio de 2015

Estudia arduamente lo que más te interese, de la forma más indisciplinada, irreverente y original que puedas.

Richard P. Feynman, premio Nobel de Física en 1965.

## Agradecimientos

A mis padres, por todo el esfuerzo y los sacrificios que han hecho para que pueda estar hoy aquí, y por darme la fuerza y la confianza que a veces no tengo en mí mismo. Y mi hermano Rafa, que pese a nuestras diferencias, nos apreciamos más de lo que parece.

A mi tía Pepa, por ser desde que tengo memoria mi segunda madre, y a mi tío Vicente, que una vez me dijo que la fórmula del éxito es  $H_2O$  (Honestidad, Humildad y Osadía). Y también por darme el mejor regalo posible: mi prima Pepilla, a la que llevo incordiando desde que nació, pero ella sabe que es con cariño. Y a mi tío Octavio, porque siempre ha estado ahí para mi familia y para mí.

A mis amigos Ares y Kito, por todas las carcajadas que nos hemos sacado todos estos años. Bea y Rachel, con quienes que viví ese milagroso ascenso de la U.D. Las Palmas este año (y alguna lagrimilla que preferimos no reconocer en público). A Cris, por todas esas conversaciones sobre libros y viajes que amenizaron estos últimos meses agobiantes. Y a Guzmán, por todo lo que aprendí de él y por creer en mí.

A mis compañeros de clase. Hago especial mención a mi amigo Héctor, que nunca dudó en echarme un cable cuando lo necesité, y a quien eché en falta este último curso por Tafira. Y al resto de compañeros que, de una forma u otra, me ayudaron en muchas etapas de mi formación, especialmente Yoel, Santana y Gara.

Y a mis tutores Francis y Víctor, por la ayuda y el apoyo que me brindaron durante la elaboración de este trabajo, y por la confianza que depositaron en mí. Y a Juan Domingo, por la ayuda técnica que me ofreció en el laboratorio.

## Índice general

| A  | cróni   | mos                                           | ΧV |  |  |  |  |  |

|----|---------|-----------------------------------------------|----|--|--|--|--|--|

| Ι  | Memoria |                                               |    |  |  |  |  |  |

| 1. | Intr    | roducción                                     | 3  |  |  |  |  |  |

|    | 1.1.    | Antecedentes                                  | 3  |  |  |  |  |  |

|    | 1.2.    | Objetivos                                     | 7  |  |  |  |  |  |

|    | 1.3.    | Estructura de la memoria                      | 8  |  |  |  |  |  |

| 2. | Des     | cripción del estándar AIS                     | 9  |  |  |  |  |  |

|    | 2.1.    | Introducción                                  | 9  |  |  |  |  |  |

|    | 2.2.    | Regulación y regulación del estándar AIS      | 9  |  |  |  |  |  |

|    | 2.3.    | Arquitectura de red                           | 10 |  |  |  |  |  |

|    |         | 2.3.1. Nivel Físico                           | 12 |  |  |  |  |  |

|    |         | 2.3.2. Nivel de Enlace                        | 18 |  |  |  |  |  |

|    | 2.4.    | Tipos de mensajes AIS                         | 28 |  |  |  |  |  |

|    | 2.5.    | Descripción hardware de los transceptores AIS | 30 |  |  |  |  |  |

|    |         | 2.5.1. AIS clase A                            | 30 |  |  |  |  |  |

|    |         | 2.5.2 AIS clase B                             | 31 |  |  |  |  |  |

| 3. | Dise | eño mo         | odular del prototipo hardware                | 33 |  |  |  |

|----|------|----------------|----------------------------------------------|----|--|--|--|

|    | 3.1. | . Introducción |                                              |    |  |  |  |

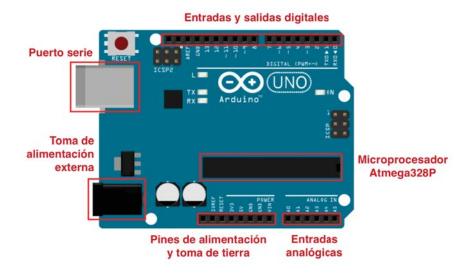

|    | 3.2. | Arduino UNO R3 |                                              |    |  |  |  |

|    |      | 3.2.1.         | Microcontrolador ATmega328P                  | 34 |  |  |  |

|    |      | 3.2.2.         | Entradas y salidas digitales                 | 35 |  |  |  |

|    |      | 3.2.3.         | Entradas y salidas analógicas                | 35 |  |  |  |

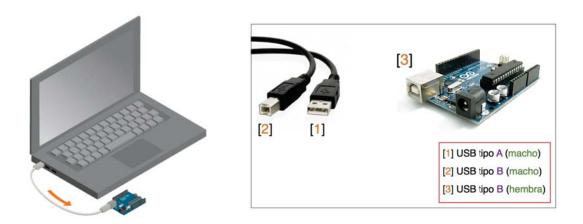

|    |      | 3.2.4.         | Puerto serie                                 | 36 |  |  |  |

|    | 3.3. | Módul          | lo banda base DV-MEGA GMSK                   | 36 |  |  |  |

|    |      | 3.3.1.         | Pines del módem DV-MEGA GMSK                 | 37 |  |  |  |

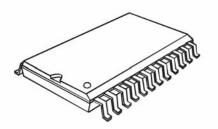

|    |      | 3.3.2.         | CMX589A                                      | 38 |  |  |  |

|    |      | 3.3.3.         | Circuito de sincronismo externo              | 39 |  |  |  |

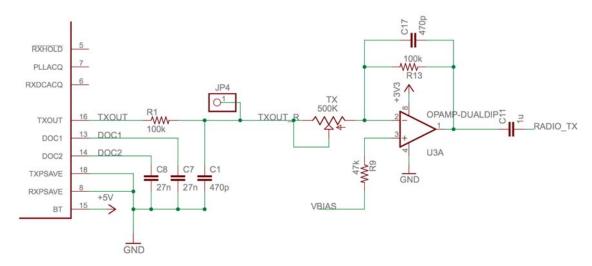

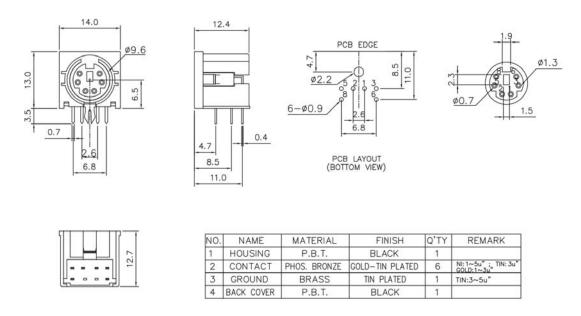

|    |      | 3.3.4.         | Etapas de filtrado y ganancia en transmisión | 40 |  |  |  |

|    |      | 3.3.5.         | Etapas de filtrado y ganancia en recepción   | 42 |  |  |  |

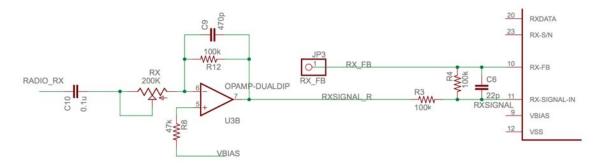

|    |      | 3.3.6.         | Push To Talk                                 | 43 |  |  |  |

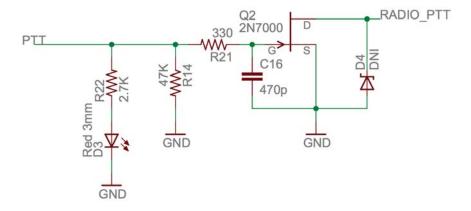

|    |      | 3.3.7.         | Conector Mini-DIN 6                          | 43 |  |  |  |

|    | 3.4. | Módul          | los paso banda FM Radiometrix                | 45 |  |  |  |

|    |      | 3.4.1.         | Radiometrix TX1                              | 45 |  |  |  |

|    |      | 3.4.2.         | Radiometrix RX1                              | 47 |  |  |  |

|    | 3.5. | Anten          | a de VHF marítimo                            | 50 |  |  |  |

| 4. | Inte | gració         | n del banco de pruebas AIS                   | 51 |  |  |  |

|    | 4.1. | O              | ucción                                       | 51 |  |  |  |

|    | 4.2. |                | ación de los módulos                         | 51 |  |  |  |

|    |      |                | amación de un firmware de control en Arduino | 53 |  |  |  |

|    |      | 4.3.1.         | Funciones propias de Arduino                 | 54 |  |  |  |

|    |      |                |                                              |    |  |  |  |

|            |      | 4.3.2. | Interrupciones en Arduino                                            | 56 |

|------------|------|--------|----------------------------------------------------------------------|----|

|            | 4.4. | Desarr | collo del firmware de control del transmisor                         | 57 |

|            |      | 4.4.1. | Definiciones y variables globales                                    | 58 |

|            |      | 4.4.2. | Inicialización del programa                                          | 59 |

|            |      | 4.4.3. | Programa principal                                                   | 60 |

|            |      | 4.4.4. | Rutina de servicio del transmisor                                    | 62 |

|            | 4.5. | Desarr | collo del firmware de control del receptor                           | 64 |

|            |      | 4.5.1. | Definiciones y variables globales                                    | 64 |

|            |      | 4.5.2. | Inicialización del programa                                          | 65 |

|            |      | 4.5.3. | Programa principal                                                   | 65 |

|            |      | 4.5.4. | Rutina de servicio del receptor                                      | 66 |

|            | 4.6. | Descri | pción de la interfaz Arduino - Puerto serie                          | 70 |

|            |      | 4.6.1. | Interfaz de transmisión                                              | 70 |

|            |      | 4.6.2. | Interfaz de recepción                                                | 71 |

| <b>5</b> . | Pru  | ebas y | resultados                                                           | 73 |

|            | 5.1. | Introd | ucción                                                               | 73 |

|            | 5.2. | Prueb  | as sobre los módulos paso banda                                      | 73 |

|            |      | 5.2.1. | Pruebas sobre el módulo Radiometrix TX1                              | 73 |

|            |      | 5.2.2. | Pruebas sobre el módulo Radiometrix RX1                              | 76 |

|            | 5.3. | Prueb  | as sobre los módulos banda base                                      | 78 |

|            |      | 5.3.1. | Prueba de transmisión y recepción de una secuencia binaria alternada | 79 |

|            |      | 5.3.2. | Prueba de transmisión y recepción de una secuencia binaria aleatoria | 81 |

|            |      | 5.3.3. | Prueba de transmisión y recepción de un carácter conocido            | 82 |

|    | 5.4.         | Pruebas de integración de los módulos paso banda y banda base    | 85 |

|----|--------------|------------------------------------------------------------------|----|

|    |              | 5.4.1. Medidas sobre antenas de VHF marítimo                     | 86 |

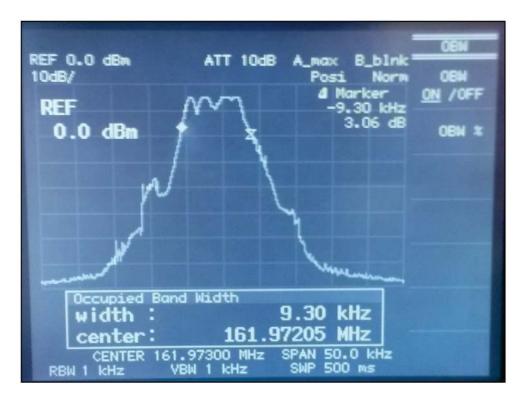

|    |              | 5.4.2. Pruebas de ancho de banda para tramas AIS                 | 88 |

|    |              | 5.4.3. Prueba de envío y recepción de tramas AIS                 | 89 |

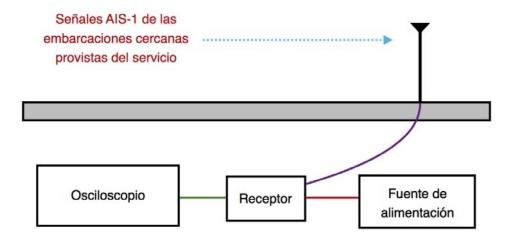

|    | 5.5.         | Prueba real de recepción de tramas AIS con el prototipo hardware | 91 |

| 6. | Con          | nclusiones                                                       | 95 |

|    | 6.1.         | Resultados y Revisión de Objetivos                               | 95 |

|    | 6.2.         | Líneas Futuras                                                   | 96 |

| II | P            | resupuesto                                                       | 99 |

| Pr | esup         | puesto 10                                                        | 01 |

|    | P.1.         | Introducción                                                     | 01 |

|    | P.2.         | Trabajo tarifado por tiempo empleado                             | 01 |

|    | P.3.         | Amortización del inmovilizado material                           | 02 |

|    |              | P.3.1. Amortización de los recursos hardware                     | 02 |

|    |              | P.3.2. Amortización de los recursos software                     | 03 |

|    | P.4.         | Redacción de la documentación                                    | 04 |

|    | P.5.         | Derechos de visado del COITT                                     | 05 |

|    | P.6.         | Gastos de tramitación y envío                                    | 06 |

|    | P.7.         | Aplicación de impuestos y coste total                            | 06 |

| II | $\mathbf{I}$ | Anexos 10                                                        | )9 |

| Α. | Des          | cripción del chip CMX589A                                        | 11 |

| ÍNDICE GENERAL                                   | XV  |

|--------------------------------------------------|-----|

| B. PCB del módulo transmisor                     | 129 |

| C. PCB del módulo receptor                       | 131 |

| D. Código del firmware de control del transmisor | 133 |

| E. Código del firmware de control del receptor   | 137 |

| F. Publicación de resultados                     | 141 |

## Índice de figuras

| 1.1.  | Cobertura global AIS por satélite                                                   | 4  |

|-------|-------------------------------------------------------------------------------------|----|

| 1.2.  | Visualización de un sistema radar convencional frente al sistema AIS $$ .           | 5  |

| 1.3.  | Funcionamiento de SOTDMA entre dos embarcaciones                                    | 6  |

| 1.4.  | Receptor AIS cedido por Marine Traffic al IDeTIC                                    | 7  |

| 1.5.  | Diagrama de bloques del banco de pruebas transmisor AIS                             | 7  |

| 1.6.  | Diagrama de bloques del banco de pruebas receptor AIS                               | 8  |

| 2.1.  | Esquema general de la arquitectura de red del estándar AIS                          | 11 |

| 2.2.  | Descripción de la banda de trabajo del servicio AIS                                 | 12 |

| 2.3.  | Esquema de codificación y de modulación en el estándar AIS                          | 13 |

| 2.4.  | Ejemplo de codificación NRZI sobre una secuencia binaria                            | 14 |

| 2.5.  | Comparativa entre los espectros FSK y GMSK                                          | 15 |

| 2.6.  | Respuesta al impulso de un filtro gaussiano ideal                                   | 15 |

| 2.7.  | Respuesta al impulso de un filtro gaussiano con $BT=0.3\ \mathrm{y}\ BT=0.5$ .      | 16 |

| 2.8.  | Interferencia entre símbolos en GMSK para factores $BT=0.3 \; \mathrm{y} \; BT=0.5$ | 17 |

| 2.9.  | Modulador y demodulador FM-GMSK                                                     | 18 |

| 2.10. | (a) Sincronismo UTC directo, (b) Sincronismo UTC indirecto                          | 19 |

| 2.11. | Formato de una trama AIS                                                            | 20 |

| 2.12. | Esquema TDMA en AIS para las frecuencia AIS-1 y AIS-2                               | 21 |

| 2.13. Esquemas TDMA en AIS en función de su aplicación                        | 21 |

|-------------------------------------------------------------------------------|----|

| 2.14. Algoritmo de la fase de inicialización en SOTDMA                        | 22 |

| 2.15. Selección de NTS en un intervalo SI                                     | 23 |

| 2.16. Algoritmo de la fase de entrada en red en SOTDMA                        | 24 |

| 2.17. Selección de NS definido en un NI                                       | 25 |

| 2.18. Algoritmo de la fase de operación continua en SOTDMA                    | 25 |

| 2.19. Campos incluidos en un mensaje AIS simple                               | 29 |

| 2.20. Campos incluidos en un mensaje AIS compuesto                            | 29 |

| 2.21. Diagrama de bloques de un transpondedor AIS clase A                     | 31 |

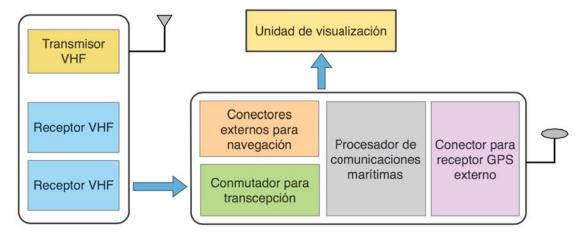

| 2.22. Diagrama de bloques de un transpondedor AIS clase B                     | 32 |

| 3.1. Diferentes modelos de plataforma Arduino                                 | 33 |

| 3.2. Microcontrolador Arduino UNO R3                                          | 34 |

| 3.3. Conectores USB tipo A/B macho y hembra sobre Arduino UNO                 | 36 |

| 3.4. Shield DV-MEGA GMSK                                                      | 37 |

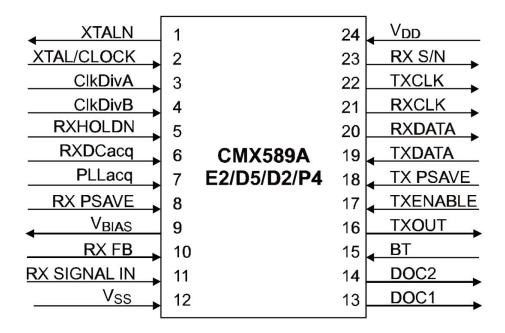

| 3.5. Encapsulado del chip CMX589A                                             | 38 |

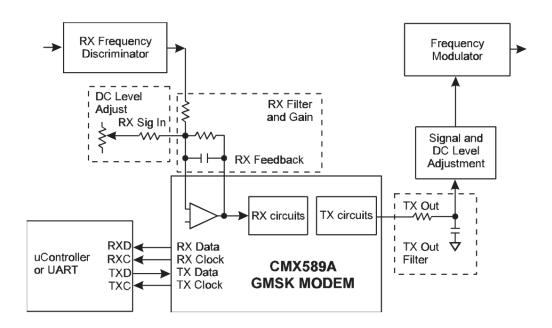

| 3.6. Subsistemas integrados al chip CMX589A                                   | 39 |

| 3.7. Circuito de sincronismo externo al chip CMX589A para 9.8 kbps            | 40 |

| 3.8. Filtro pasivo RC paso bajo                                               | 40 |

| 3.9. Filtro activo paso bajo                                                  | 41 |

| 3.10. Filtro de transmisión                                                   | 42 |

| 3.11. Filtro de recepción                                                     | 42 |

| 3.12. Circuito PTT del módem DV-MEGA GMSK                                     | 43 |

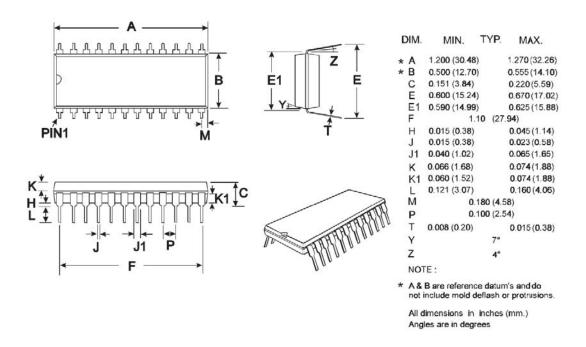

| 3.13. Dimensiones del conector Mini-DIN 6 (expresadas en milímetros, $mm$ ) . | 44 |

| 3.14. Pines del conector Mini-DIN 6                                           | 44 |

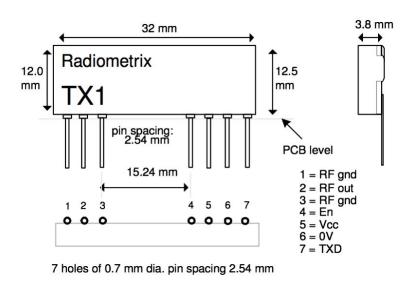

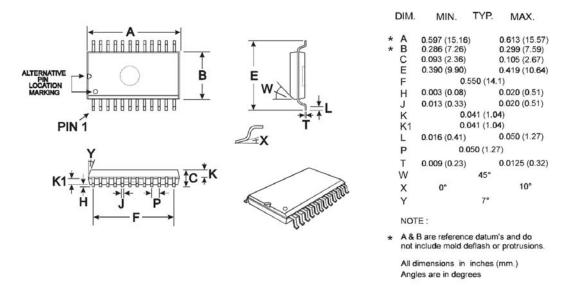

| 3.15. Dimensiones físicas del chip Radiometrix TX1                              | 45 |

|---------------------------------------------------------------------------------|----|

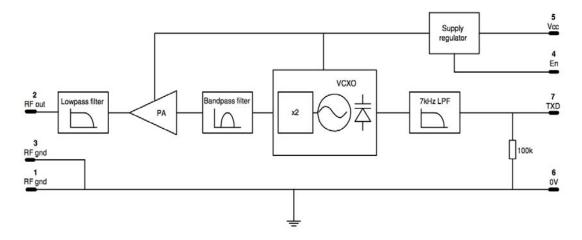

| 3.16. Diagrama de bloques del chip Radiometrix TX1                              | 46 |

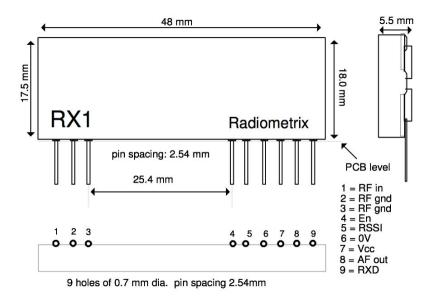

| 3.17. Dimensiones físicas del chip Radiometrix RX1                              | 47 |

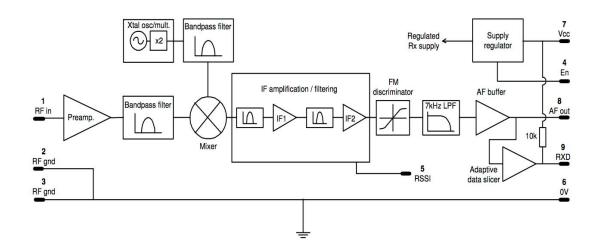

| 3.18. Diagrama de bloques del chip Radiometrix RX1                              | 49 |

| 3.19. Antena VHF marítimo Kenwood SMA macho                                     | 50 |

| 4.1. Diagrama de bloques del prototipo hardware del transmisor AIS              | 52 |

| 4.2. Diagrama de bloques del prototipo hardware del receptor AIS                | 52 |

| 4.3. Condiciones de disparo en Arduino                                          | 57 |

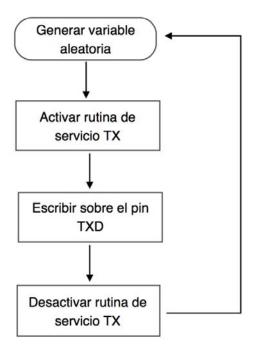

| 4.4. Flujograma del programa principal del firmware de control del transmisor   | 61 |

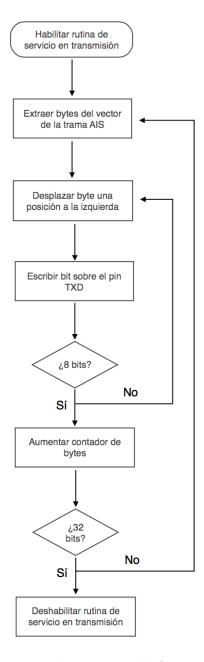

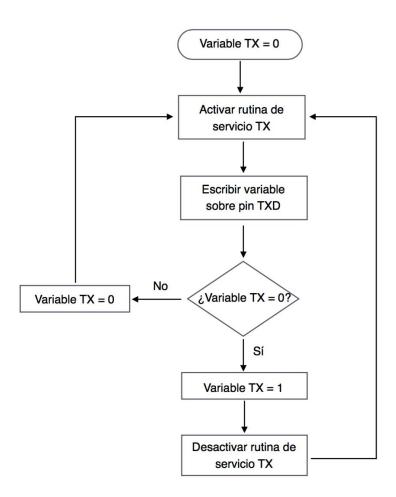

| 4.5. Flujograma de la rutina de servicio del firmware de control del transmisor | 63 |

| 4.6. Flujograma del programa principal del firmware de control del receptor     | 66 |

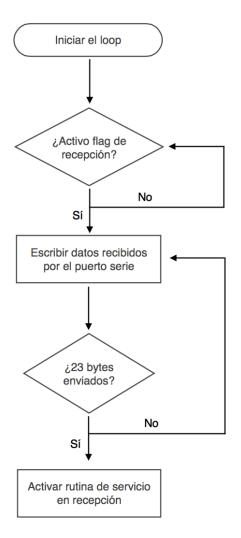

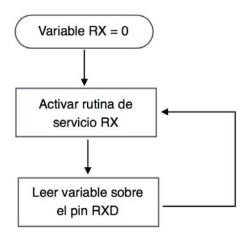

| 4.7. Flujograma de la rutina de servicio del firmware de control del receptor   | 69 |

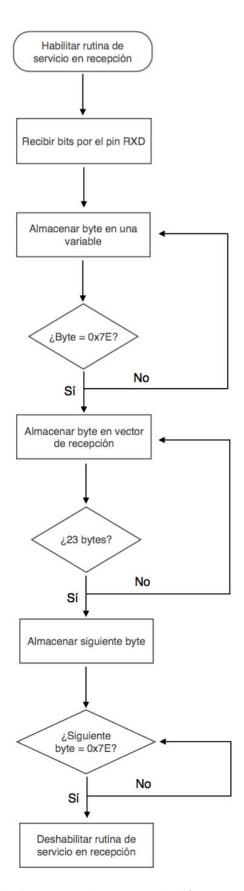

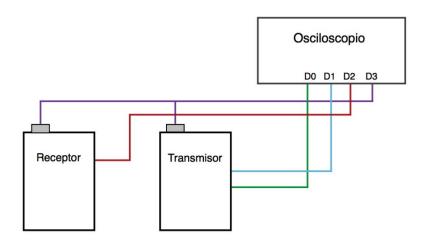

| 4.8. Banco de pruebas transmisor y receptor con interfaces Serial               | 70 |

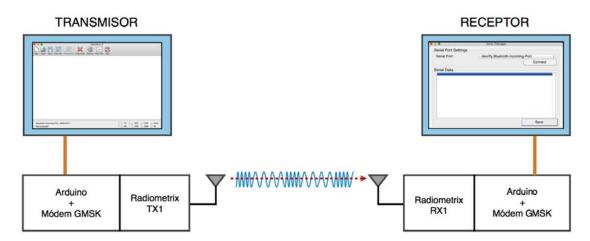

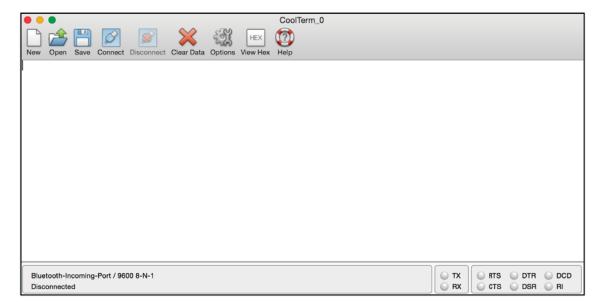

| 4.9. Interfaz de la aplicación <i>CoolTerm</i>                                  | 71 |

| $4.10.$ Envío de cadenas de caracteres por el puerto serie con $Send\ String$   | 71 |

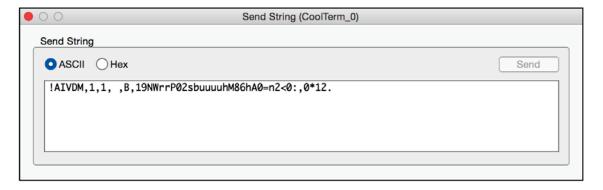

| 4.11. Interfaz de la aplicación $Serial\ Monitor$ de Matlab 2014b               | 72 |

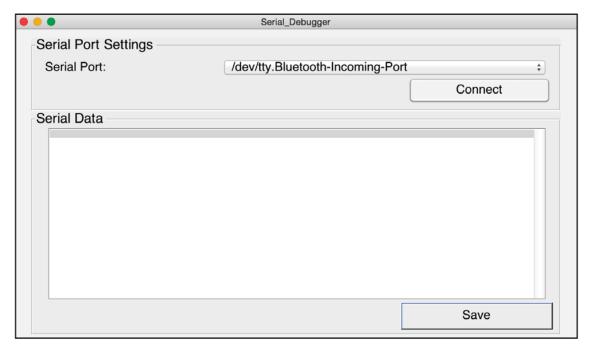

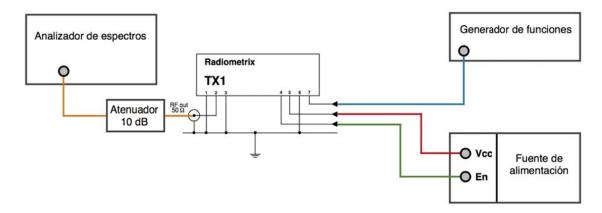

| 5.1. Montaje de prueba para el chip Radiometrix TX1                             | 74 |

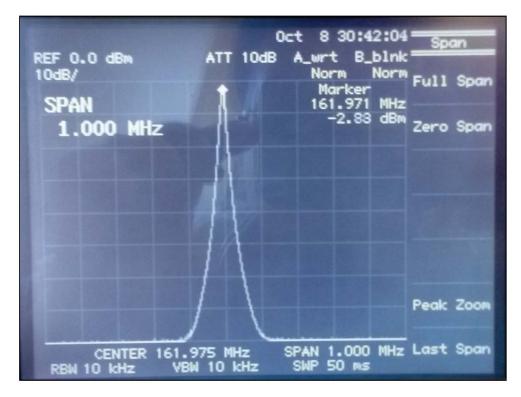

| 5.2. Señal portadora a 161.975 MHz generada por el chip Radiometrix TX1         | 75 |

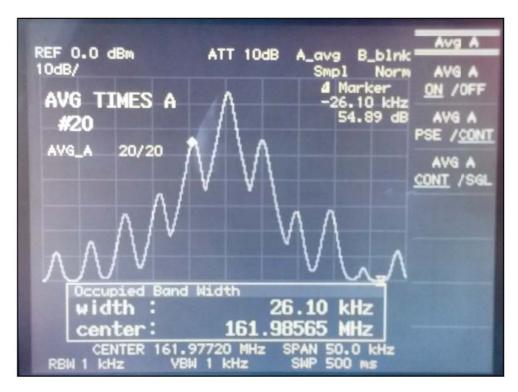

| 5.3. Espectro FM de una señal cuadrada como moduladora                          | 76 |

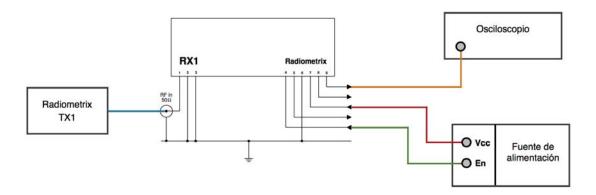

| 5.4. Montaje de prueba para el chip Radiometrix RX1                             | 77 |

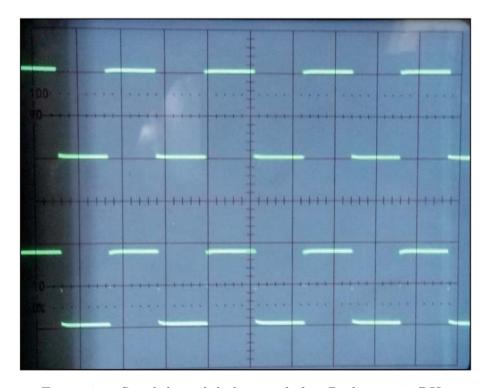

| 5.5. Señal demodulada por el chip Radiometrix RX1                               | 77 |

| 5.6. Montaje de prueba para el módem DV-MEGA GMSK                               | 78 |

| 5.7. Algoritmo de prueba de transmisión de una secuencia binaria alternada      | 79 |

| 5.8.  | Algoritmo de prueba de recepción de una secuencia binaria alternada .                                  | 80 |

|-------|--------------------------------------------------------------------------------------------------------|----|

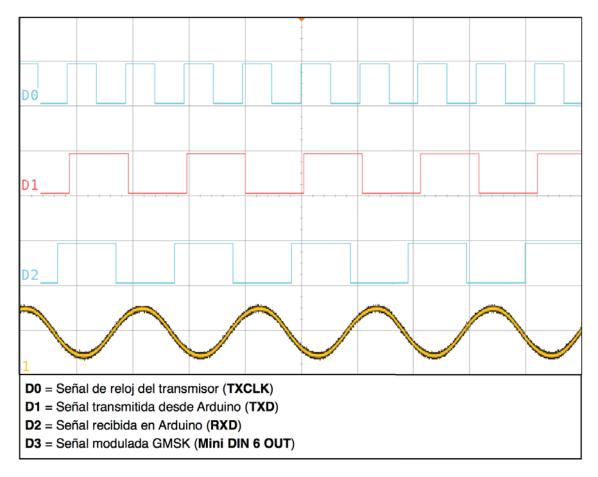

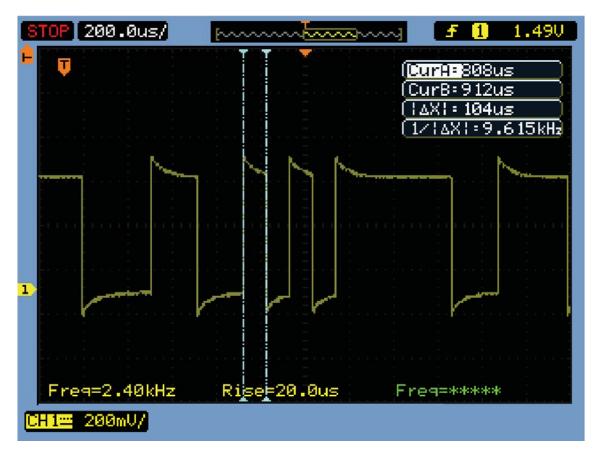

| 5.9.  | Visualización en osciloscopio multicanal de una secuencia binaria alternada en el módem DV-MEGA GMSK   | 80 |

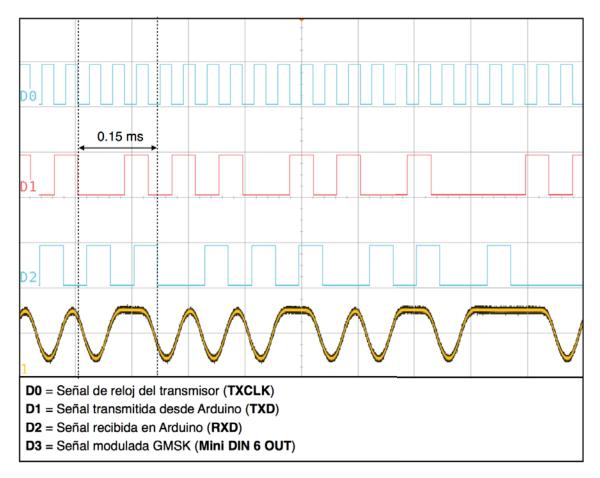

| 5.10. | Algoritmo de prueba de transmisión de una secuencia binaria aleatoria                                  | 81 |

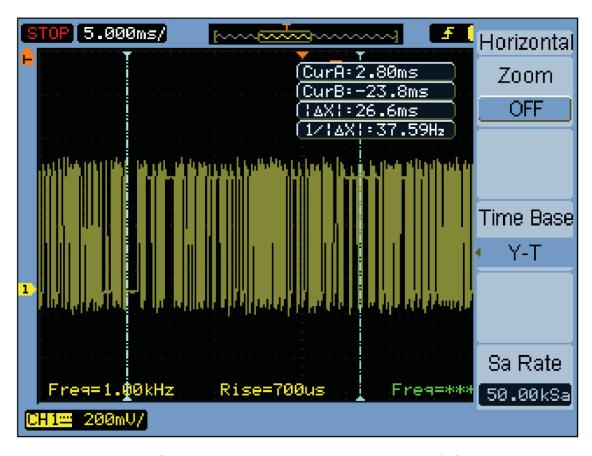

| 5.11. | Visualización en osciloscopio multicanal de una secuencia binaria aleatoria en el módem DV-MEGA GMSK   | 82 |

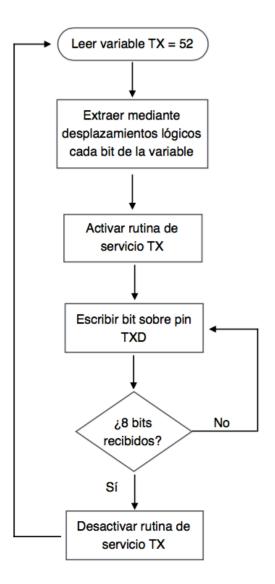

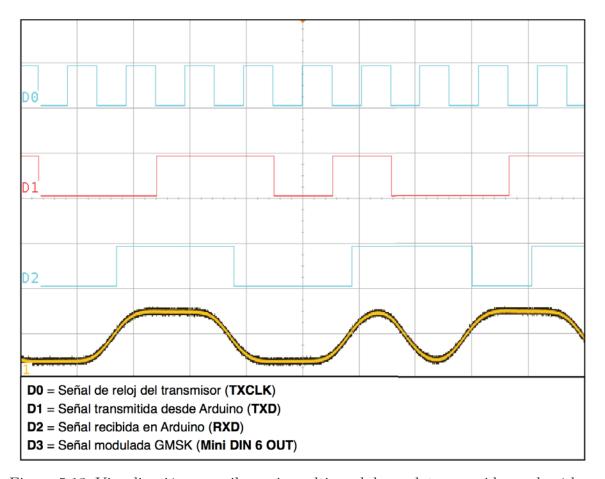

| 5.12. | Algoritmo de prueba de transmisión de una secuencia binaria conocida                                   | 83 |

| 5.13. | Visualización en osciloscopio multicanal de un dato conocido en el módem DV-MEGA GMSK                  | 84 |

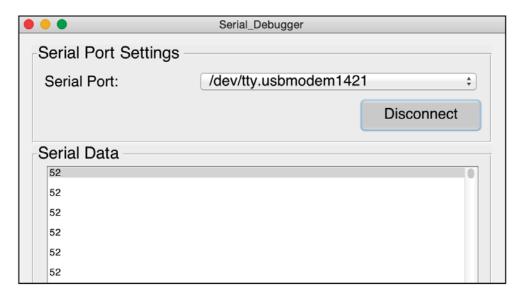

| 5.14. | Recepción del carácter 52 desde el módem GMSK hasta Serial Monitor                                     | 84 |

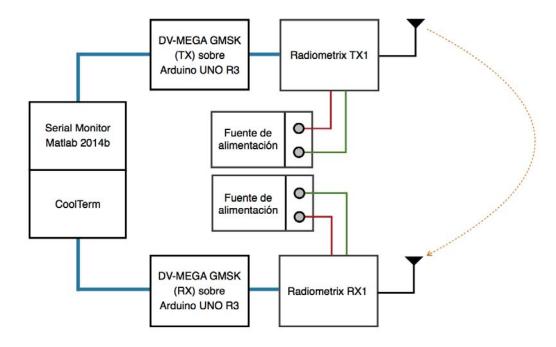

| 5.15. | Montaje de prueba para la visualización por pantalla de tramas $\operatorname{AIS}$                    | 85 |

| 5.16. | Banco de pruebas para la visualización por pantalla de tramas AIS $$ . $$ .                            | 86 |

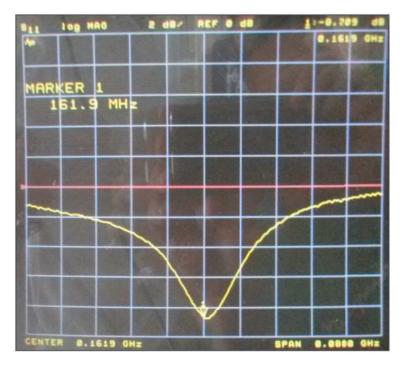

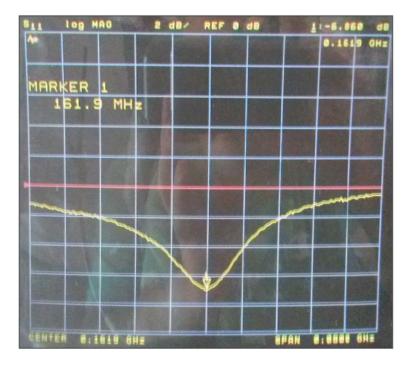

| 5.17. | Medida del parámetro $S_{11}$ para la antena VHF transmisora                                           | 87 |

| 5.18. | Medida del parámetro $S_{11}$ para la antena VHF receptora                                             | 87 |

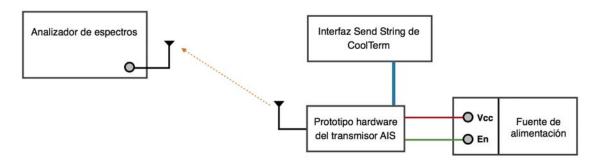

| 5.19. | Montaje de medida del ancho de banda de transmisión de tramas $\operatorname{AIS}$ .                   | 88 |

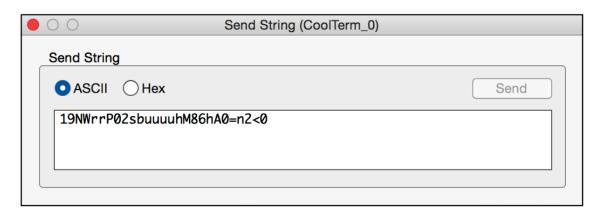

| 5.20. | Trama AIS de test sobre la interfaz $Send\ String\ de\ CoolTerm$                                       | 88 |

| 5.21. | Trama AIS modulada en FM-GMSK por el prototipo hardware del transmisor                                 | 89 |

| 5.22. | Trama AIS modulada en FM-GMSK por el prototipo hardware transmisor                                     | 90 |

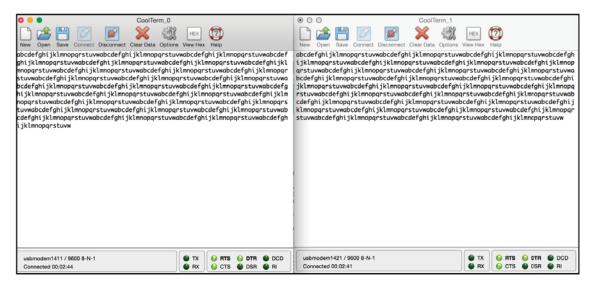

| 5.23. | Envío de la trama AIS durante 30 iteraciones ( $CoolTerm0$ como transmisor, $CoolTerm1$ como receptor) | 90 |

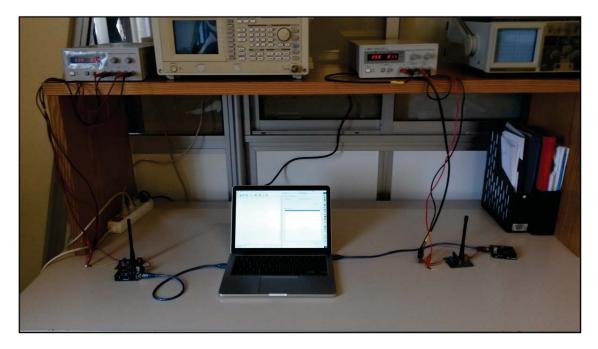

| 5.24. | Montaje del banco de pruebas de recepción de tramas AIS reales                                         | 91 |

| 5.25. | Montaje en laboratorio del banco de pruebas de recepción de tramas AIS reales                          | 91 |

| 5.26. | Banda de trabajo AIS a la frecuencia 161.975 MHz                                                       | 92 |

| 5.27. | Forma de onda de la trama AIS recibida                                                                 | 93 |

| 5.28. | Comprobación de los slots en las tramas AIS recibidas                                                  | 94 |

| A.1. Encapsulado del chip CMX589A                                                         | 111  |

|-------------------------------------------------------------------------------------------|------|

| A.2. Subsistemas integrados al chip CMX589A                                               | 112  |

| A.3. Diagrama de pines del chip CMX589A                                                   | 113  |

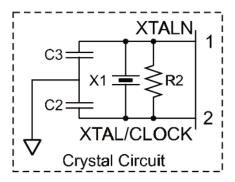

| A.4. Topología de sincronismo local con oscilador XTAL                                    | 115  |

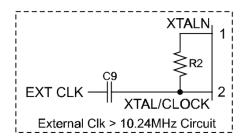

| A.5. Topología de sincronismo externo para $EXTCLK > 10.24~\mathrm{MHz}$                  | 116  |

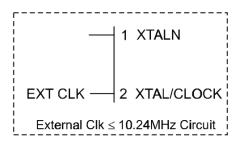

| A.6. Topología de sincronismo externo para $EXTCLK \leq 10.24~\mathrm{MHz}$               | 116  |

| A.7. Selección de $R_B$ en función de $f_{xtal}$ y los estados sobre ClkDivA y ClkDivE    | 3117 |

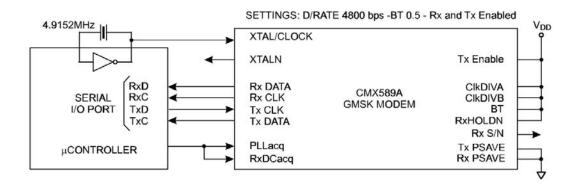

| A.8. Mínimas conexiones del CMX589A para $R_B=4800bps$                                    | 117  |

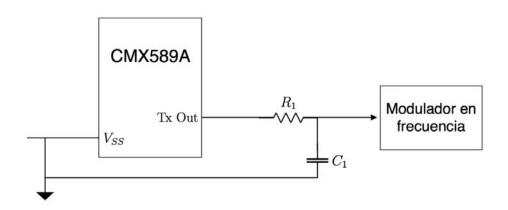

| A.9. Filtro RC para la selección del factor BT                                            | 118  |

| A.10.<br>Tabla de selección de $R_1$ y $C_1$ en función de<br>$R_B$ y factor BT           | 119  |

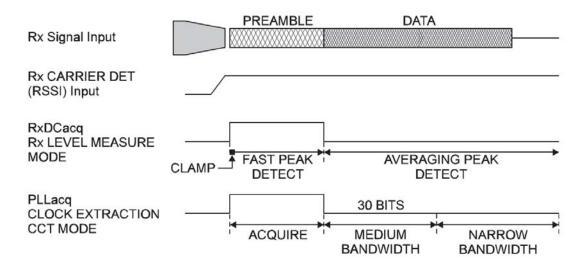

| A.11. Tabla de modos de funcionamiento del PLL en recepción                               | 121  |

| A.12.Modos de funcionamiento de control en recepción                                      | 122  |

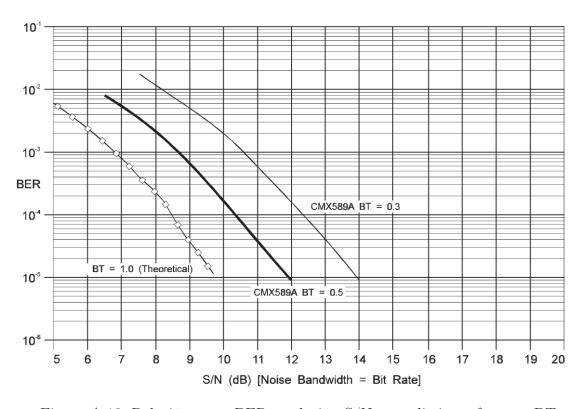

| A.13.<br>Relación entre BER y relación S/N para distintos factores BT<br>$\ .\ .\ .\ .$ . | 123  |

| A.14.<br>Relación entre tiempos de adquisición y relación S/N para distintos factores BT  | 124  |

| A.15.Respuesta al impulso del filtro de transmisión                                       | 125  |

| A.16.Encapsulado del modelo CMX589AE2                                                     | 127  |

| A.17.Diagrama de pines del chip CMX589AD5                                                 | 127  |

| A.18.Diagrama de pines del chip CMX589AD2                                                 | 128  |

| A.19.Diagrama de pines del chip CMX589AP4                                                 | 128  |

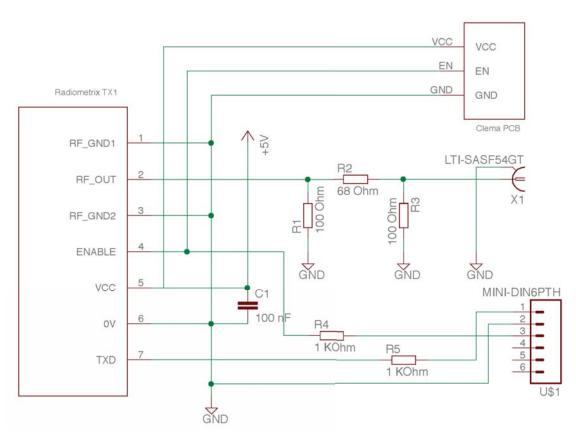

| B.1. Esquemático del módulo transmisor para el banco de pruebas AIS $$ . $$ .             | 129  |

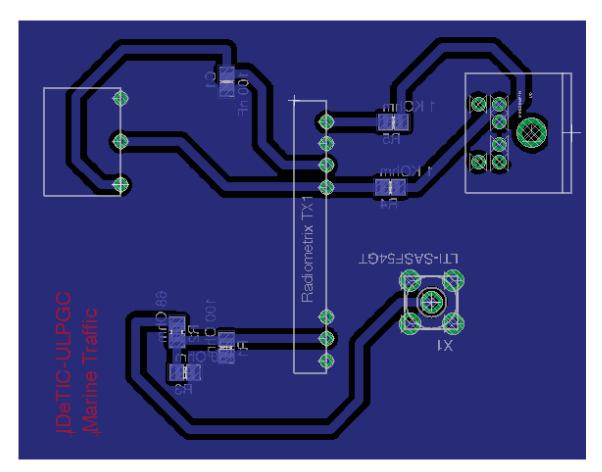

| B.2. Diseño PCB sobre Eagle PCB Design del transmisor FM                                  | 130  |

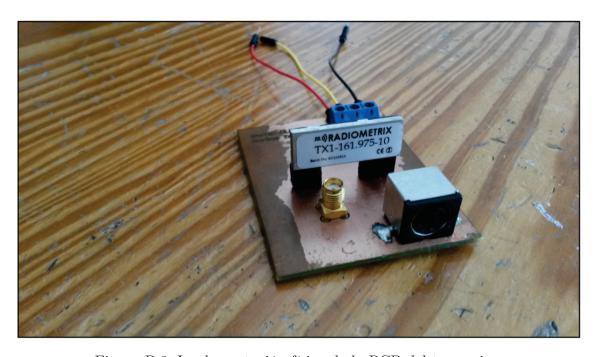

| B.3. Implementación física de la PCB del transmisor                                       | 130  |

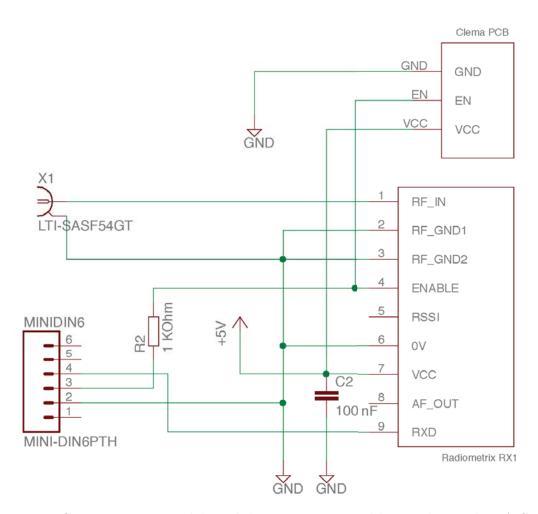

| C.1. Esquemático del módulo receptor para el banco de pruebas AIS                         | 131  |

|  |  |  |  | [G] |  |  |  |

|--|--|--|--|-----|--|--|--|

|  |  |  |  |     |  |  |  |

|  |  |  |  |     |  |  |  |

|  |  |  |  |     |  |  |  |

| 37 | 37 | T. | т |

|----|----|----|---|

| X  | X  |    | ı |

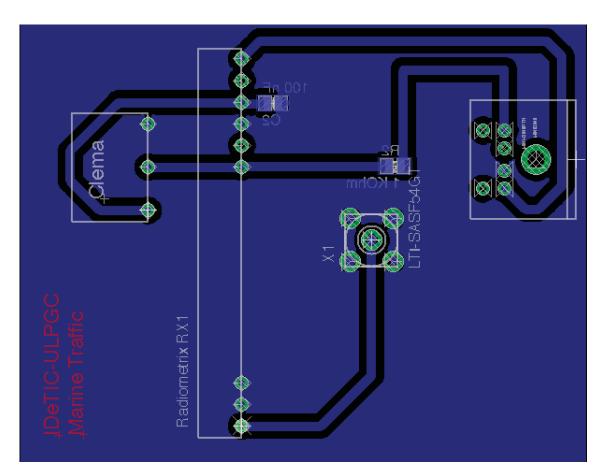

| C.2. | Diseño PCB sobre Eagle PCB Design del receptor FM | 132 |

|------|---------------------------------------------------|-----|

| C.3. | Implementación física de la PCB del receptor      | 132 |

## Índice de tablas

| 2.1. | Parámetros radio generales del estándar AIS                                       | 12  |

|------|-----------------------------------------------------------------------------------|-----|

| 2.2. | Características especiales para transmisores AIS                                  | 13  |

| 2.3. | Características especiales para receptores AIS                                    | 13  |

| 2.4. | Campos de datos de un mensaje AIS codificado con NMEA 0183                        | 30  |

| 3.1. | Descripción de los pines del módem DV-MEGA GMSK                                   | 38  |

| 3.2. | Características del chip Radiometrix TX1                                          | 47  |

| 3.3. | Características del chip Radiometrix RX1                                          | 49  |

| 3.4. | Características de la antena de VHF marítimo Kenwood                              | 50  |

| P.1. | Tabla de precios del material hardware fungible                                   | 103 |

| P.2. | Tabla de precios del material hardware no fungible                                | 103 |

| P.3. | Tabla de precios del material software                                            | 104 |

| P.4. | Presupuesto según el trabajo tarifado y la amortización del inmovilizado material | 105 |

| P.5. | Presupuesto incluyendo la redacción de la memoria                                 | 106 |

| P.6. | Presupuesto final del TFG                                                         | 107 |

## Acrónimos

| Acrónimo      | Descripción                                                 |

|---------------|-------------------------------------------------------------|

| ADC           | Analog-to-Digital Converter                                 |

| AIS           | Automatic Identification System                             |

| AtoN          | Aid to Navigation                                           |

| BER           | Bit Error Rate                                              |

| COITT         | Colegio Oficial de Ingenieros Técnicos de Telecomunicación  |

| CRC           | Código de Redundancia Cíclica                               |

| CSTDMA        | Carrier Sense Time Division Multiple Access                 |

| DGPS          | Differential Global Positioning System                      |

| DIN           | Deutsches Institut für Normung                              |

| DLS           | Data Link Service                                           |

| EEPROM        | Electrically Erasable Programmable Read Only Memory         |

| FATDMA        | Fixed Access Time Division Multiple Access                  |

| $\mathbf{FM}$ | Frequency Modulation                                        |

| GMDSS         | Global Maritime Distress and Safety System                  |

| GMSK          | Gaussian Minimum Shift Keying                               |

| GPS           | Global Positioning System                                   |

| GSM           | Global System for Mobile communications                     |

| HDLC          | High-Level Data Link Control                                |

| IDE           | Integrated Development Environment                          |

| IDeTIC        | Instituto para el Desarrollo Tecnológico y la Innovación en |

|               | Comunicaciones                                              |

| IMO           | International Maritime Organization                         |

| ISR           | Interrupt Service Routine                                   |

| ITDMA         | Incremental Time Division Multiple Access                   |

| ITU           | International Telecommunication Union                       |

| KB            | Kilobyte                                                    |

| LME           | Link Management Entity                                      |

| MAC           | Medium Access Control                                       |

| MMSI          | Maritime Mobile Service Identity                            |

| MN            | Milla náutica                                               |

| MSC           | Maritime Safety Committee                                   |

| NI            | Nominal Interval                                            |

| NMEA          | National Marine Electronics Association                     |

| NRZI          | Non Return Zero Inverted                                    |

| NS            | Nominal Slot                                                |

| NSS           | Nominal Start Slot                                          |

| NTS           | Nominal Transmission Slot                                   |

**OPAMP** | Operational Amplifier

OSI Open System Interconnection

PATDMA | Pre-Announced Time Division Multiple Access

PCB Printed Circuit Board

PTT Push To Talk

PWM Pulse-width Modulation

**RATDMA** | Random Access Time Division Multiple Access

RF Radio Frequency

RI Reporting Interval

RR Report Rate

SART | Search and Rescue Transponder

SMA SubMiniature version A SMD Surface Mount Device SOLAS Safety Of Life At Sea

**SOTDMA** | Self Organized Time Division Multiple Access

SRAM Static Random Access Memory

TDMA Time Division Multiple Access

TFG Trabajo Fin de Grado

UART Universal Asynchronous Receiver - Transmitter

USB Universal Serial Bus

VCO Universal Time Coordinated Voltage Controlled Oscillator

VHF Very High Frequency

VTS Vessel Tracking Service

Parte I

Memoria

## Capítulo 1

## Introducción

#### 1.1. Antecedentes

La preocupación por mejorar la seguridad en las travesías marítimas se remonta a 1912, cuando ocurrió la catástrofe naval del Titanic. Fue entonces cuando la seguridad en los océanos dejó de ser un tema trivial y los gobiernos de numerosas naciones decidieron crear un organismo que regulara ciertas normas que avalaran un incremento en la seguridad marítima. De esta manera, en 1914 se crea el Convenio SOLAS (Safety Of Life At Sea) con el objetivo de garantizar la seguridad en los océanos. Este convenio, desde sus orígenes, ha sufrido un alto número de enmiendas, en parte para incluir normas que se adapten a los nuevos cambios en lo que respecta al tráfico marítimo [1].

En 1948, la ONU crea la IMO (*International Maritime Organization*) con el objetivo de regular las normas adoptadas por el Convenio SOLAS a nivel global. Su objetivo es promover la seguridad en los océanos y garantizar la supervivencia humana en caso de catástrofe. Para ello, la IMO incorporó el MSC (*Maritime Safety Committee*) para llevar a cabo estas regulaciones, así como para encargarse de la incorporación de las enmiendas a las que se vea sometido el Convenio SOLAS.

Pero no fue hasta 1991 cuando se presenta el primer documento acerca de las especificaciones técnicas que caracterizarían al estándar AIS (Automatic Identification System), un estándar internacional y de libre acceso que actualmente es adoptado por un gran número de embarcaciones de todo tipo y que tiene como objetivo principal garantizar una mayor seguridad en las travesías marítimas. Este sistema es capaz de monitorizar la actividad naval en una misma zona de cobertura e identificar la posición de los buques, su velocidad o su rumbo, para así como evitar posibles colisiones a partir del conocimientos de estos datos por el resto de embarcaciones [2].

Aunque desde la presentación del estándar AIS se han modificado algunos aspectos técnicos del estándar, no fue hasta 2001 cuando comenzaron a realizarse las primeras pruebas de conformidad para el estándar AIS. Finalmente, en el año 2002, la IMO exige el uso obligatorio de AIS para aquellas embarcaciones con un tonelaje bruto superior a 500 toneladas, los buques de más de 300 toneladas que realicen travesías internacionales y todo buque de pasajeros (independientemente de su tonelaje) [3].

4 1.1. Antecedentes

Además, el estándar AIS se incorpora al sistema GMDSS (Global Maritime Distress and Safety System) [4], vigente desde 1999, que se trata de un conjunto de procedimientos, equipos y protocolos de comunicación diseñados con el objetivo de incrementar la seguridad en las travesías marítimas y facilitar la navegación y el rescate de las embarcaciones que se encuentren en situación de peligro. Un ejemplo de otro sistema incorporado a GMDSS con fines similares es COSPAS/SARSAT [5].

Entre las ventajas más relevantes que pueden citarse acerca del estándar AIS, son de especial interés las que se mencionarán a continuación:

- Fácil implementación, mantenimiento y actualización.

- Bajo costo operativo (incluso a veces inexistente).

- Estandarización internacional.

- Cobertura entre 20 MN y 100 MN (dependiendo de las alturas de las antenas y de los obstáculos de la transmisión).

- Robustez frente al estado del mar y las condiciones meteorológicas adversas.

- Auge de incorporación de este sistema en embarcaciones pesqueras y de recreo.

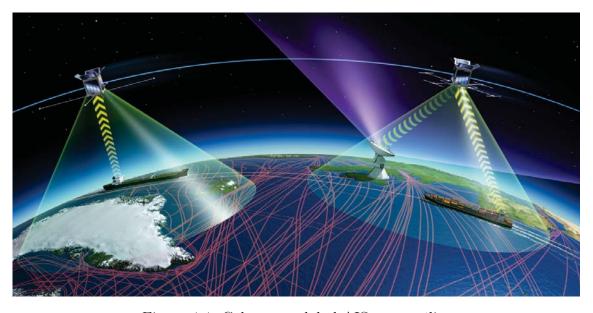

Además, el estándar AIS presenta cobertura global por satélite [5]. Esto permite que las zonas marítimas más alejadas de la costa, donde no hay una gran confluencia de tráfico marítimo y la cobertura es escasa o inexistente, estén provistas de suficiente cobertura para que los buques que integran AIS puedan realizar transmisiones de sus datos de travesía. Estos datos son recibidos por satélites AIS, como es el caso *Orbcomm* y *exactEarth*, que direccionan los mensajes hasta las estaciones base AIS que a su vez, transmiten los datos al cliente o a la autoridad con derecho para utilizarlos en diversos fines, como puede ser salvamento marítimo (Figura 1.1).

Figura 1.1: Cobertura global AIS por satélite

1. Introducción 5

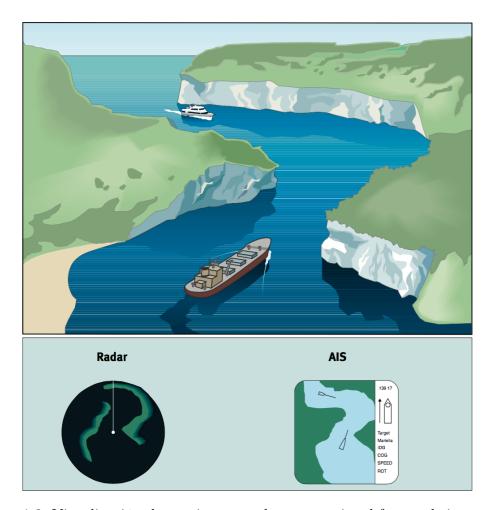

Otra de las ventajas que presenta el sistema AIS es su robustez frente a los elementos topográficos. Es de especial mención esta ventaja, dado que los sistemas radar destinados para los mismos fines sí se ven afectados por la orografía circundante, especialmente en las zonas costeras donde los acantilados pueden ocultar ciertas embarcaciones que no se encuentren en visibilidad directa con el radar (Figura 1.2).

Figura 1.2: Visualización de un sistema radar convencional frente al sistema AIS

No obstante, AIS puede ser integrado en los sistemas radar en dispositivos conocidos como AIS-VTS (*Automatic Identification System - Vessel Tracking Service*), considerado como uno de los principales avances en la tecnología de comunicaciones marítima desde la invención del radar. En los dispositivos AIS-VTS, se combina la visualización AIS y radar, consiguiendo manejar las ventajas de cada uno de estos en un mismo sistema [6].

Sin embargo, hay buques que no están sometidos al Convenio SOLAS. Un ejemplo de ello son las embarcaciones militares y los buques que prestan un servicio no comercial a un Estado (además de las embarcaciones de recreo, donde el uso de AIS es opcional). Esto genera el problema de que al no estar todas las embarcaciones obligadas a identificarse mediante este sistema, podría ser empleado para operaciones de piratería, terrorismo o pesca ilegal.

6 1.1. Antecedentes

Otra de las peculiaridades que hace de AIS un sistema cada vez más atractivo, incluso para aquellas embarcaciones que no se ven sometidas al Convenio SOLAS, es que a diferencia de otros sistemas móviles, como es el caso de GSM, los fallos en las estaciones base de control AIS no implican la caída total del sistema, pues cada estación móvil autogestiona su envío y recepción de datos hacia otras estaciones. Esto se consigue a través del principal aspecto técnico de este estándar: el esquema de multiplexación temporal SOTDMA (Self-Organized Time Division Multiple Access).

SOTDMA es una técnica de multiplexación que incorpora una sincronización UTC (*Universal Time Coordinated*) que permite a las estaciones AIS poder advertir al resto de estaciones su intención de transmitir en un determinado slot de tiempo. En caso de que este slot esté ocupado por otra estación, nuestra estación transmisora hará uso del algoritmo SOTDMA hasta encontrar un slot libre al que acceder. Este proceso será repetido por el resto de estaciones, asegurando que en ningún momento dos estaciones puedan interferirse ocupando el mismo slot para transmitir sus datos [7].

A través de los slots, cada embarcación transmitirá su información tanto estática (identificación) como dinámica (posición, rumbo, velocidad) para que el resto de embarcaciones puedan conocerla y así evitar conflictos de trayectoria en una misma zona de tránsito marítimo. De esta forma, todas las estaciones conocerán los datos del resto de estaciones (Figura 1.3).

Figura 1.3: Funcionamiento de SOTDMA entre dos embarcaciones

Desde abril de 2013, el IDeTIC (*Instituto para el Desarrollo Tecnológico y la Innovación en Comunicaciones*) cuenta con una estación receptora de AIS que fue cedida por la empresa *Marine Traffic* para realizar diversos estudios sobre operaciones portuarias y marítimas (Figura 1.4). Presenta un rango de cobertura que varía en función de las condiciones meteorológicas, pero ronda entre las 82.73 y 685.52 MN, y es capaz de recibir datos de cerca de 100 embarcaciones [8].

1. Introducción 7

| Rango de alimentación eléctr | ica: 9 - 30 Voltios DC                                                    |

|------------------------------|---------------------------------------------------------------------------|

| Consumo de energía:          | 180mA @ 12VDC                                                             |

| Velocidad de transmisión:    | 38400 Baud (38.4Kb)                                                       |

| Formato:                     | ITU/ NMEA 0183                                                            |

| Mensaje de salida:           | VDM                                                                       |

| Frecuencia de receptor:      | Canal A 161.975 MHz<br>Canal B 162.025 MHz                                |

| Separación entre canales:    | 25KHz                                                                     |

| Sensibilidad:                | -112dBm                                                                   |

| Demodulación:                | GMSK                                                                      |

| Velocidad de datos:          | 9600                                                                      |

| Impedancia de antena:        | 50 ohms                                                                   |

| Dimensiones físicas:         | L 165 x W 105 x H 46mm<br>Weight: 600g                                    |

| Montaje:                     | 4 agujeros de montaje en placa                                            |

| Conectores:                  | Antena BNC                                                                |

| Puerto Ethernet:             | RJ-45                                                                     |

| Puerto USB:                  | Tipo B                                                                    |

| Alimentación:                | Clavija fonográfica de 2.1mm                                              |

| Diseñado para cumplir:       | IEC 61993-2<br>Aprobación CE a EN 60945: EN<br>6100-6-1/2<br>FCC parte 15 |

Figura 1.4: Receptor AIS cedido por Marine Traffic al IDeTIC

### 1.2. Objetivos

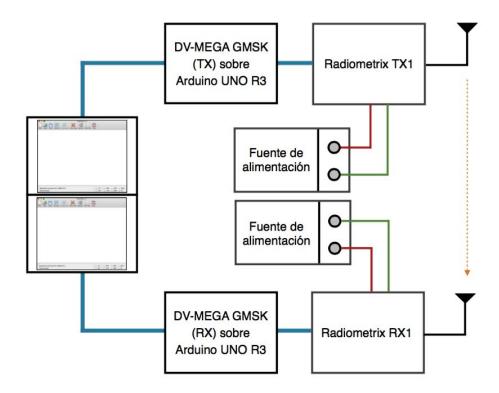

El principal objetivo de este Trabajo de Fin de Grado es el diseño y la implementación física de un prototipo hardware modular destinado a la realización de pruebas sobre el estándar AIS. Para este banco de pruebas, se atenderá al diseño de un transmisor y un receptor.

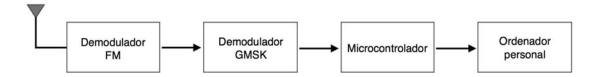

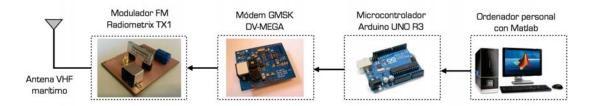

En el caso del transmisor, desde una interfaz conectada al puerto serie de un microcontrolador, es posible enviar tramas de datos. El microcontrolador dará formato a estas tramas y serán moduladas en banda base a través de un módem GMSK. Seguidamente, los datos modulados en banda base volverán a ser modulados en paso banda con un modulador FM, que a su salida entregará la señal generada a través de una antena de VHF marítimo (Figura 1.5).

Figura 1.5: Diagrama de bloques del banco de pruebas transmisor AIS

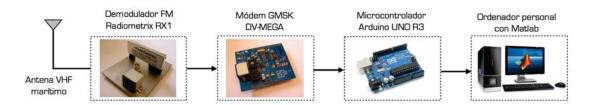

Por otra parte, el receptor recibirá los datos modulados en FM por una antena de VHF marítimo. Estos datos serán demodulados en FM y posteriormente, en GMSK, entregando a la entrada del microcontrolador los datos enviados desde el transmisor.

Por último, una interfaz conectada al puerto serie del microcontrolador permite que los datos recibidos queden representados en una pantalla de ordenador (Figura 1.6).

Figura 1.6: Diagrama de bloques del banco de pruebas receptor AIS

Para alcanzar el objetivo principal de este TFG, los pasos que se siguen son los siguientes:

- Estudio en profundidad del estándar AIS.

- Diseño modular del prototipo para el banco de pruebas.

- Implementación e integración física de los módulos.

- Programación del firmware de control para el banco de pruebas.

#### 1.3. Estructura de la memoria

En el Capítulo 1 de esta memoria se describen algunas consideraciones generales sobre el estándar AIS y el marco en el que se sitúa este trabajo, aportando una breve introducción que permita dar paso Capítulo 2, donde se realiza un estudio minucioso de este estándar. En este segundo capítulo, se estudia con mayor detalle el estándar con el objetivo de reconocer los requisitos que deben cumplir los dispositivos hardware que lo integran.

En el Capítulo 3 se se detallan las características técnicas de los módulos escogidos para el desarrollo del prototipo hardware. Este tercer capítulo permite abordar las consideraciones de diseño relativas al conexionado y funcionamiento del prototipo, que se describe en el Capítulo 4.

El Capítulo 5 recoge todas las pruebas realizadas para verificar el correcto funcionamiento del prototipo hardware y su viabilidad. Las conclusiones alcanzadas tras la realización de estas pruebas y las propuestas de mejoras para este trabajo se recogen en el Capítulo 6.

Seguidamente, se incluye la bibliografía que ha sido referenciada en la redacción de este trabajo y el presupuesto de este TFG. Se incluye como anexos alguna documentación relativa al hardware que se emplea en el prototipo hardware, destacando la inclusión de los resultados publicados en base a este trabajo.

## Capítulo 2

## Descripción del estándar AIS

#### 2.1. Introducción

En este capítulo se realiza un estudio previo del estándar AIS, que está especificado en la recomendación ITU-R M.1371-5 [9]. En primer lugar, se habla de la regulación del estándar AIS y la obligatoriedad de incorporación del mismo en ciertos tipos de embarcaciones. Por último, se describe la arquitectura de red de este estándar, entrando en mayor detalle con los niveles Física y de Enlace, pues tienen una repercusión directa con este trabajo.

### 2.2. Regulación y regulación del estándar AIS

Desde 2003, la IMO exige la incorporación obligatoria del estándar AIS en ciertos tipos de embarcaciones en función de su tonelaje bruto y el servicio al que se destinan.

Los buques con un tonelaje bruto superior a 500 toneladas, superior a 300 toneladas y que realicen travesías internacionales y todo buque de pasajeros, independientemente de su tonelaje bruto, están obligados a incorporar transpondedores AIS en sus equipos de abordo.

Aquellos buques que prestan un servicio no comercial para un Estado, los buques militares y las pequeñas embarcaciones de recreo o de pesca, no están obligados a integrar este sistema. En cualquier caso, la mayoría de los buques militares integran AIS como sistema de respaldo para otros equipos de a bordo, pero no están obligados a identificarse en el sistema.

En este conjunto de embarcaciones exentas del cumplimiento del estándar AIS se encuentran también las embarcaciones de recreo (dimensiones de eslora máxima de 24 metros), los barcos pesqueros de pequeñas dimensiones y cualquier otra embarcación con dimensiones y tonelaje inferiores a las que exige la IMO en relación a la obligatoriedad de integración del estándar AIS.

La obligatoriedad de integración de los equipos AIS para ciertos tipos de embarcaciones hace que este sistema diferencie entre dos tipos de transpondedores, llamados AIS clase A y AIS clase B, que difieren entre sí tanto en prestaciones técnicas como en sus esquemas de acceso al medio.

- AIS clase A: se trata del sistema con mayores prestaciones dentro de la gama de transpondedores AIS. Su uso es obligatorio en buques con un tonelaje bruto superior a 500 toneladas, superior a 300 toneladas que realicen travesías internacionales y cualquier buque de transporte de pasajeros, independientemente de su tonelaje bruto.

- AIS clase B: es un sistema con menores prestaciones que los transpondedores AIS clase A, y su calidad depende principalmente de las técnicas de acceso al medio implementadas. Se destina a aquellos buques para los que el uso de AIS no sea obligatorio, como pueden ser las embarcaciones de recreo o los buques pesquero de pequeñas dimensiones.

Por otro lado, el estándar AIS puede ser integrado en diversos dispositivos dependiendo de los fines a los que se destina. En función de su uso, se establece la siguiente clasificación:

- AIS BS (*Base Station*): estaciones de control instaladas en la costa, que integran AIS para para proveer de cobertura a los barcos que se encuentran próximos a los puertos y realizan operaciones de atraque.

- AtoN (Aid to Navigation): sistema integrado en boyas de salvamento marítimo, que prestan cobertura en las zonas más hostiles del entorno marino.

- AIS SART (Search and Rescue Transponder): dispositivos AIS integrados en numerosos vehículos terrestres, marítimos y aéreos, con el objetivo de determinar la posición de los buques de salvamento y así poder servir como red de apoyo en operaciones de rescate.

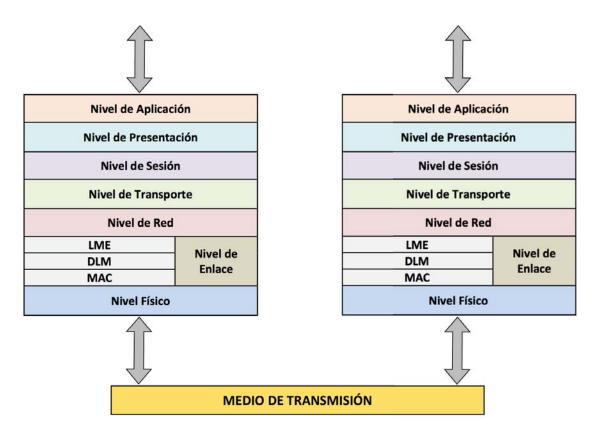

#### 2.3. Arquitectura de red

El estándar AIS presenta una arquitectura de red basada en el modelo de referencia OSI (*Open System Interconnection*), lo que significa que está formada por 7 capas o niveles relacionados entre sí (Figura 2.1). Sin embargo, el estándar AIS solamente describe el funcionamiento de los tres primeros niveles de esta arquitectura:

• Nivel Físico: en él se realizan todas las conexiones entre los sistemas que pretenden comunicarse en formato digital a través de un mismo estándar, de manera que se puede interpretar como la interfaz entre el sistema de comunicación y el canal.

- Nivel de Enlace: se relaciona con el manejo de las tramas de bits, así como con la detección y corrección de errores que se realiza previamente al envío de paquetes por la red. Por ello, es la capa que asegura la fiabilidad del flujo binario. A su vez, se compone de tres subniveles:

- MAC (*Medium Access Control*): asegura la correcta transferencia de datos desde el medio físico hasta el Nivel de Enlace.

- **DLS** (*Data Link Service*): realiza la detección y el control de errores tras realizarse la transferencia de datos sobre el Nivel de Enlace.

- LME (*Link Management Entity*): controla las operaciones que realiza las subcapas MAC y DLS.

- Capa de Red: en esta capa se realiza el envío y recepción de paquetes de datos. Realiza las tareas de descongestión de paquetes en red, en caso de existir flujos masivos de datos que pusiesen en riesgo el intercambio de información entre sistemas bajo un mismo estándar.

En lo que respecta a las capas de Transporte, Sesión, Presentación y Aplicación, la única exigencia del estándar es que se implementen de forma coherente a los paquetes de datos que son intercambiados desde el Nivel de Red.

Figura 2.1: Esquema general de la arquitectura de red del estándar AIS

# 2.3.1. Nivel Físico

El Nivel Físico hace referencia a la interfaz que existe entre el propio sistema de comunicación y el canal. En esta capa se transmiten y reciben las secuencias de bits de los datos del protocolo implementado, y se caracteriza por todos aquellos parámetros ligados al hardware del sistema.

# 2.3.1.1. Banda de trabajo y parámetros radio

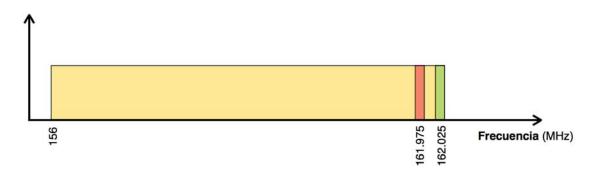

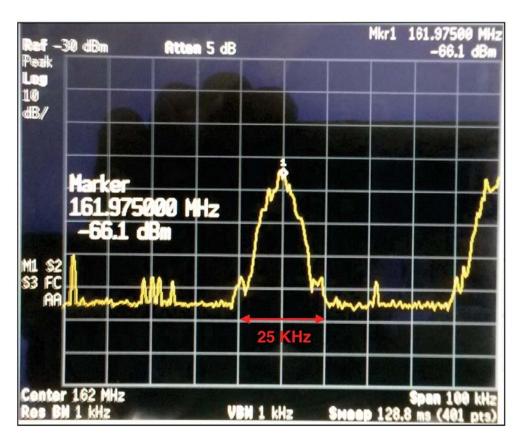

El servicio AIS se establece en la banda de VHF marítimo (156.00 MHz - 162.025 MHz), tomando dentro de esta banda dos posibles canales: **AIS-1** (161.975 MHz) y **AIS-2** (162.025 MHz), también llamados canales 87 y 88, respectivamente (Figura 2.2).

La canalización de la banda de trabajo en AIS es 25 KHz, establecido por la recomendación ITU-R M.1084-5 [11].

Figura 2.2: Descripción de la banda de trabajo del servicio AIS

Los parámetros radio definen aquellas características que los equipos deben satisfacer en la banda de trabajo donde operan. Para el estándar AIS, estas características quedan recogidas en la Tabla 2.1.

| Parámetro radio                       | Valor                  |

|---------------------------------------|------------------------|

| Banda de trabajo del servicio         | 156.025 - 162.025  MHz |

| Frecuencia de trabajo AIS-1           | 161.975 MHz            |

| Frecuencia de trabajo AIS-2           | $162.025~\mathrm{MHz}$ |

| Canalización del servicio             | $25~\mathrm{KHz}$      |

| Velocidad de transmisión              | 9600 baudios           |

| Potencia transmitida en AIS clase A   | 12.5 W                 |

| Potencia transmitida en AIS clase B   | 1 W                    |

| Factor BT en transmisión (aproximado) | 0.4                    |

| Factor BT en recepción (aproximado)   | 0.5                    |

| Índice de modulación                  | 0.5                    |

Tabla 2.1: Parámetros radio generales del estándar AIS

Además, el estándar AIS también especifica las características propias de los equipos de transmisión (Tabla 2.2) y de recepción (Tabla 2.3).

| Parámetro radio                              | Valor                       |

|----------------------------------------------|-----------------------------|

| Desviación de frecuencia de la portadora     | $\pm 500~\mathrm{Hz}$       |

| Desviación de potencia de la portadora       | $\pm 1.5 \text{ dB}$        |

| Respuesta de rechazo para emisiones espúreas | -36  dBm  (9  KHz - 1  GHz) |

|                                              | -30  dBm (1  GHz - 4  GHz)  |

| Atenuación de intermodulación                | ≥ 40 dB                     |

Tabla 2.2: Características especiales para transmisores AIS

| Parámetro radio                              | Valor                       |

|----------------------------------------------|-----------------------------|

| Sensibilidad                                 | -107  dB                    |

| Tasa de error por saturación                 | 1% para $-77$ dBm           |

|                                              | 1% para $-7$ dBm            |

| Selectividad para canales adyacentes         | 70 dB                       |

| Selectividad para el propio canal            | 10 dB                       |

| Respuesta de rechazo para emisiones espúreas | -57  dBm  (9  KHz - 1  GHz) |

|                                              | -47  dBm  (1  GHz - 4  GHz) |

| Atenuación sobre emisiones espúreas          | ≥ 70 dB                     |

| Atenuación de intermodulación                | ≥ 74 dB                     |

Tabla 2.3: Características especiales para receptores AIS

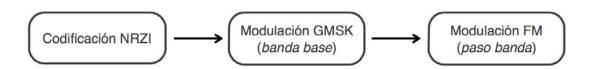

Por último, el estándar AIS establece sus propios esquemas de codificación y modulación. Emplea un esquema de codificación NRZI sobre los datos digitales transmitidos. Estos datos son modulados en banda base con GMSK, que se combina con una modulación paso banda FM (Figura 2.3).

Figura 2.3: Esquema de codificación y de modulación en el estándar AIS

En los siguientes puntos se trata el estudio del esquema de codificación y de modulación del estándar AIS en mayor profundidad.

## 2.3.1.2. Esquemas de codificación

El estándar AIS incopora un tipo concreto de *codificación diferencial*, que son un grupo de codificaciones ampliamente utilizadas en comunicaciones por radio y satélites,

que se emplean para la recepción precisa de los bits cuando la señal se ve sometida a algún tipo de modulación digital.

Estas técnicas permiten que los datos transmitidos no dependan del bit actual únicamente, sino también del bit anterior que ha sido transmitido. De esta manera, hay un mayor control en el flujo de los datos transmitidos, aunque cabe destacar que son muy sensibles a los llamados errores de multiplicación por los que una detección incorrecta de un símbolo conlleva a la generación de dos símbolos incorrectos, duplicando de esta forma la tasa de error de bit (BER).

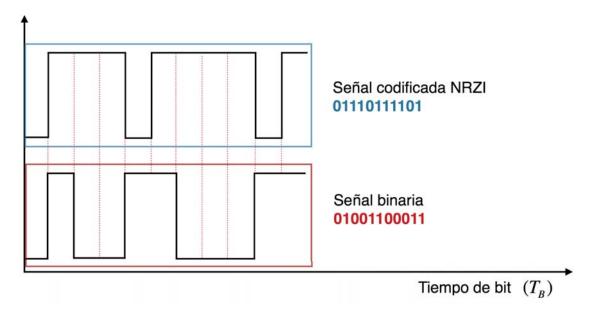

La codificación diferencial empleada por el estándar AIS se denomina NRZI (Non Return to Zero inverted). Esta codificación mantiene constante el nivel de tensión durante la duración de un bit, de forma que los datos están codificados mediante la presencia o ausencia de una transición de la señal al principio del intervalo del tiempo de bit [12].

Cuando se tiene un 1 lógico, se codifica mediante la transición (sea desde nivel bajo hasta nivel alto, o viceversa) al principio del intervalo de bit. Por el contrario, un  $\theta$  lógico representa la ausencia de una transición, de manera que cuando el valor del bit es 1, la señal cambia de estado después de que el ciclo de reloj lo indique, y si es  $\theta$ , la señal no cambia de estado (Figura 2.4).

Figura 2.4: Ejemplo de codificación NRZI sobre una secuencia binaria

Esta codificación presenta importantes ventajas que justifican la elección de la misma en el estándar AIS, como son las siguientes:

- Precisión en la detección o ausencia de señal.

- Inmunidad frente a ruido e interferencias en el canal.

- Facilidad para detectar la transición entre símbolos.

En cuanto a sus desventajas, la principal es que cuando existe una corriente continua durante una secuencia de ceros, se perturba el sincronismo entre transmisor y receptor. Por este motivo, las tramas AIS deben presentar un formato sobre el que, al realizar la codificación NRZI, se eviten las largas cadenas de  $\theta$  lógicos que afecten al sincronismo entre los sistemas transmisor y receptor.

# 2.3.1.3. Esquema de modulación

El estándar AIS emplea la combinación de una modulación paso banda FM (Frequency Modulation) con una modulación banda base GMSK (Gaussian Minimum Shift Keying), conocida como modulación FM-GMSK.

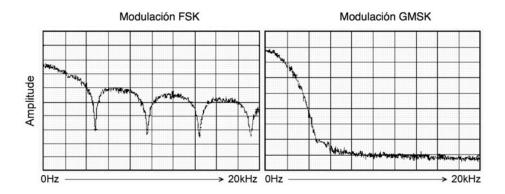

La modulación GMSK es un tipo particular de modulación MSK en banda base, que emplea un filtrado previo sobre los datos para reducir el ancho de banda de la señal. Más concretamente, es capaz de eliminar aquellas componentes relativas a los lóbulos secundarios del espectro [13].

En la Figura 2.5 se muestra una comparativa en el dominio de la frecuencia entre una modulación FSK y una modulación GMSK. Se observa, pues, la mejora que sufre el espectro en lo que respecta a la reducción del ancho de banda en banda base al filtrar los lóbulos secundarios.

Figura 2.5: Comparativa entre los espectros FSK y GMSK

El tipo de filtro que se emplea para ello es un filtro gaussiano [14]. Se trata de un filtro paso bajo con una respuesta al impulso capaz de transformar una delta de Dirac a su entrada en una forma de onda que, idealmente, se corresponde con una curva de Gauss (Figura 2.6).

Figura 2.6: Respuesta al impulso de un filtro gaussiano ideal

Matemáticamente, la respuesta al impulso g(t) del filtro gaussiano viene dada por de la ecuación (2.1):

$$g(t) = \frac{1}{2} \cdot \left[ Q\left( -\frac{2\pi B}{\sqrt{2 \cdot \ln(2)}} \cdot t \right) - Q\left( -\frac{2\pi B}{\sqrt{2 \cdot \ln(2)}} \cdot (t - T_B) \right) \right]$$

(2.1)

donde B representa el ancho de banda a -3 dB de la señal filtrada a través del filtro gaussiano,  $T_B$  el periodo de bit y Q es una función de distribución de Gauss dada por la expresión (2.2):

$$Q(t) = \int_{t} \frac{1}{\sqrt{2}} \cdot e^{-\frac{x^2}{2}} dx \tag{2.2}$$

Del espectro de la señal modulada en GMSK se pueden extraer algunos parámetros fundamentales para caracterizar esta modulación [15]. Se encuentra así el factor BT, que marca una relación entre la frecuencia de corte del filtro gaussiano a  $-3 \ dB$  y la tasa binaria de la señal (2.3).

$$BT = \frac{f_{-3 \ dB}}{R_B} \tag{2.3}$$

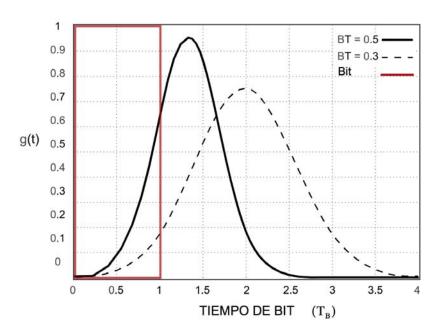

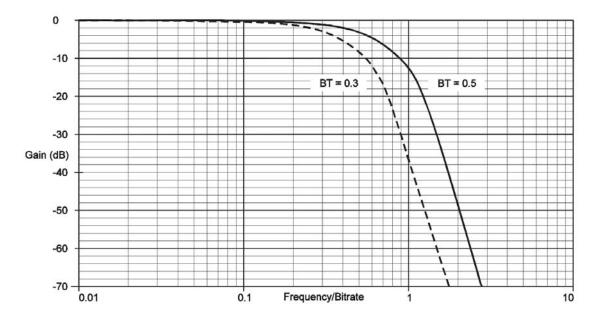

Hay dos valores del factor BT con los que normalmente trabajan los sistemas de comunicaciones digitales. Estos son BT = 0.3 y BT = 0.5. En la Figura 2.9 puede observarse la diferencia entre estos dos valores al definir un eje de abscisas para el periodo de bit  $(T_B)$  y la respuesta al impulso normalizada en el eje de ordenadas.

Figura 2.7: Respuesta al impulso de un filtro gaussiano con BT=0.3 y BT=0.5

En la Figura 2.7 se observa cómo al emplear un factor BT=0.5, la respuesta al impulso del filtro gaussiano se extiende 2 periodos de bits. En cambio, con un factor BT=0.3, la respuesta se extiende hasta cerca de 3 periodos de bits. En el dominio del tiempo, la diferencia entre los dos factores BT radica en la interferencia entre símbolos (IES).

Se evidencia que en el caso de un factor BT = 0.3, la IES es mayor que en el caso de BT = 0.5. No obstante, para un factor BT = 0.5, la tasa binaria máxima aceptada por el filtro para una misma frecuencia de corte es menor, dado que el factor BT y la tasa binaria son variables inversamente proporcionales.

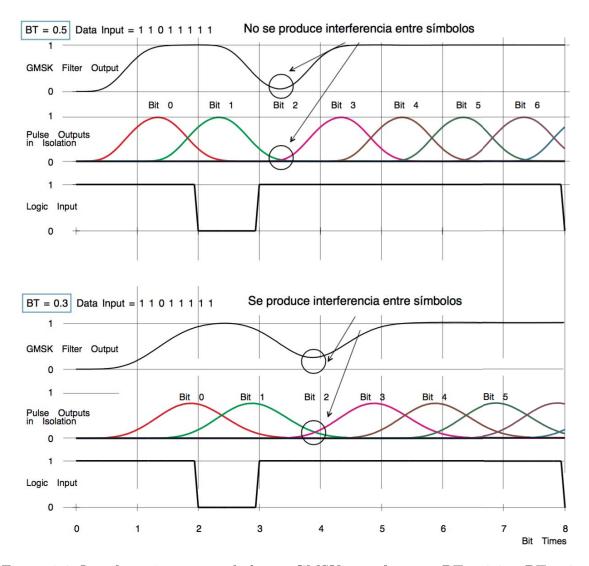

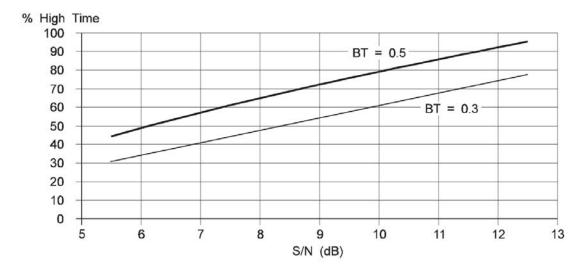

Figura 2.8: Interferencia entre símbolos en GMSK para factores BT = 0.3 y BT = 0.5

En la Figura 2.8 se observa el incremento de la IES para un factor BT = 0.3. Sin embargo, para BT = 0.5 también existe IES, pero en comparación al factor BT = 0.3 y con respecto al resto de modulaciones digitales, como es MSK, se considera que la IES es aceptable. Por tanto, hay un compromiso entre eficiencia espectral e interferencia entre símbolos durante la elección del factor BT.

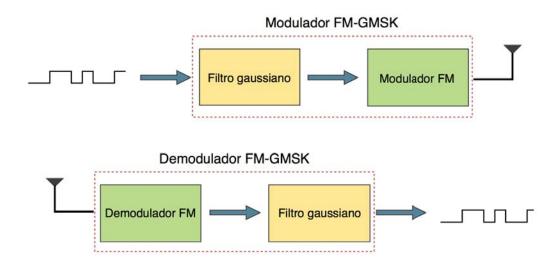

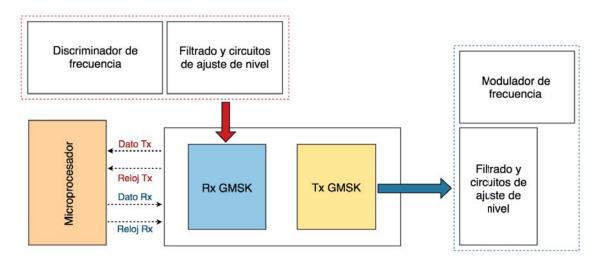

El esquema de modulación del estándar AIS, a nivel de sistemas, se puede describir con la inclusión de un modulador o demodulador GMSK en banda base conectado a un modulador o demodulador FM, respectivamente. De esta forma, se engloban las virtudes de la modulación GMSK con la robustez frente al canal radio de la modulación FM sobre un mismo sistema.

El diagrama de bloques genérico de un modulador y un demodulador FM-GMSK se representa en la Figura 2.9.

Figura 2.9: Modulador y demodulador FM-GMSK

### 2.3.2. Nivel de Enlace

El Nivel de Enlace de cualquier arquitectura de red se encarga de que realizar la transferencia fiable de los datos hasta el Nivel de Red. En esta capa se genera la detección y corrección de errores en las tramas.

Asimismo, el Nivel de Enlace para el estándar AIS se divide en tres subniveles que se denominan, en sentido ascendente: MAC (*Medium Access Control*), DLS (*Data Link Service*) y LME (*Link Management Entity*). Seguidamente, se describe la función de cada uno de estos subniveles.

## 2.3.2.1. Subcapa MAC

La subcapa MAC (*Medium Access Control*) se encarga de garantizar que la comunicación del Nivel Físico por el medio de transmisión se realice de una forma fiable. Para ello, el estándar AIS incluye las referencias de tiempo común entre las estaciones AIS que integran la red.

Todas las estaciones AIS deben estar sincronizadas bajo una referencia de tiempo común denominada UTC (*Universal Time Coordinated*), que viene dada por la red de satélites GPS (*Global Position System*).

Hay diferentes formas de acceder al sincronismo UTC por partes de las estaciones, diferenciando entre dos formas elementales: sincronismo UTC directo y sincronismo UTC indirecto (Figura 2.10).

- Sincronismo UTC directo: el sincronismo UTC deriva de la propia red GPS. El transpondedor AIS debe incluir un receptor GPS que tome esta referencia temporal para sincronizarse a un tiempo común entre estaciones.

- Sincronismo UTC indirecta: el sincronismo UTC es heredado de aquellas estaciones que se sincronizan de forma directa con la red GPS.

Figura 2.10: (a) Sincronismo UTC directo, (b) Sincronismo UTC indirecto

El sincronismo entre las estaciones AIS permite la actualización de las tasas de informes de posición. Esto quiere decir que en función del estado de la embarcación, más concretamente su velocidad de desplazamiento, los informes de posición se envían más rápidamente dependiendo de que el barco también aumente su velocidad.

## 2.3.2.2. Subcapa DLS

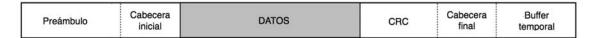

La subcapa DLS (*Data Link Service*) se encarga de dar formato a las tramas AIS que son enviadas o recibidas por el sistema. Cada trama AIS está formada por 32 bytes (Figura 2.11), organizados de la siguiente manera:

- **Preámbulo**: es una cadena de 24 bits configurada como una secuencia alternada de 1 y 0 lógicos. Tiene la forma binaria 01010101010101010101010101, que en hexadecimal se representa como tres bytes con la forma 0x55.

- Cabecera de inicio: son 8 bits dispuestos como un flag HDLC (*High-Level Data Link Control*) que alertan del inicio de los datos transmitidos. Tiene la forma binaria 01111110, que en hexadecimal se representa como un byte con la forma 0x7E.

- Datos: son 168 bits de datos en los que se incluye la información, tanto estática como dinámica, que conforma cada paquete AIS que transmite una estación. Sin embargo, el contenido de estos datos no queda definido en la subcapa DLS, sino desde capas superiores como la de red. En caso de que un paquete tenga un tamaño superior a 168 bits, se emplean técnicas de segmentación de paquetes.

- CRC: se trata de un polinomio generador de 16 bits que emplea un código de redundancia cíclica (CRC) definido en la norma *ISO/CEI 3309:1993* para realizar el control de errores que puede aparecer durante una transmisión.

- Cabecera de fin: tiene la misma forma que la cabecera de inicio (0x7E), pero a diferencia de esta, indica el final de los datos almacenados en un paquete.

- Buffer temporal: es una secuencia adicional de 24 bits que complementa a la trama para las siguientes tareas:

- Relleno de bits (4 bits).

- Retardo por distancia (12 bits).

- Retardo del repetidor (4 bits).

- Efectos por *jitter* (4 bits).

Figura 2.11: Formato de una trama AIS

En lo que respecta al campo de datos de las tramas AIS, la codificación de los mensajes se describe en la recomendación *ITU-R M.1371-5 (Anexo VIII)*, donde se recogen los diferentes tipos de mensajes que pueden enviar las estaciones AIS y el significado de cada uno de sus campos.

#### **2.3.2.3.** Subcapa LME

La subcapa LME (*Link Management Entity*) implementa el esquema de acceso al medio TDMA (*Time Division Multiple Access*). De esta manera, cada estación AIS tiene un intervalo de tiempo asignado (slot) para acceder al medio compartido con el resto de estaciones y realizar la transferencia de datos. Una vez agotado este slot, la estación desocupa el slot y permite a otra estación acceder al mismo.

Generalmente, los esquemas TDMA exigen que las estaciones estén sincronizadas. En el caso de las estaciones AIS, el sincronismo viene dado por el tiempo de referencia UTC, común a todas las estaciones AIS integradas en una misma región de cobertura.

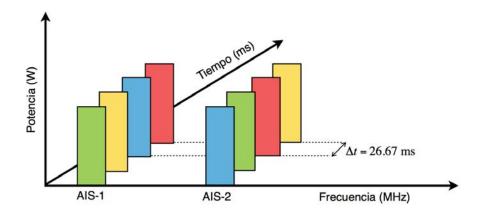

En el estándar AIS, cada slot tiene una duración de  $26.67 \ ms$ . Si cada trama AIS tiene una duración temporal de  $60 \ s$ , el número de slots totales en una trama AIS es:

$$N = 60 \cdot \Delta t_{slot} = 60 \cdot 26.67 \simeq 2250 \ slots$$

(2.4)

En la Figura 2.12 se observa el esquema TDMA para los dos canales AIS disponibles, verificando una duración por cada slot de 26.67 ms.

Figura 2.12: Esquema TDMA en AIS para las frecuencia AIS-1 y AIS-2

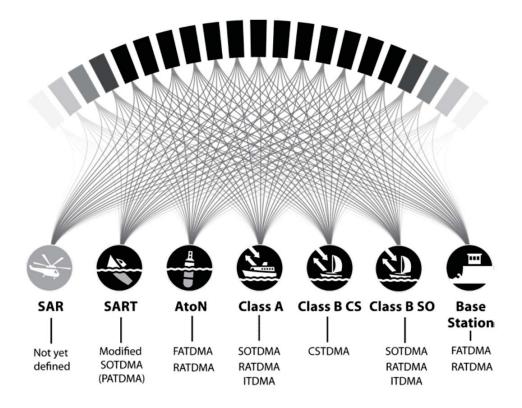

El estándar AIS incorpora diferentes esquemas de acceso al medio TDMA, pero los principales son el esquema SOTDMA, integrado en las estaciones AIS clase A, y el esquema CSTDMA, integrado en las estaciones AIS clase B [16].

En la Figura 2.13 se contemplan los usos de los diferentes esquemas TDMA en AIS en relación a las posibles aplicaciones de AIS que se describen en el punto 2.2.

Figura 2.13: Esquemas TDMA en AIS en función de su aplicación

A continuación, se explica el funcionamiento de cada uno de estos esquemas de acceso al medio, dando un mayor enfoque al esquema SOTDMA.

## **SOTDMA**

El esquema SOTDMA (Self-Organized Time Division Multiple Access) es el principal esquema de multiplexación que caracteriza al estándar AIS, y se integra en los transpondedores AIS clase A.

Este esquema contempla los siguientes modos de operación:

- Modo autónomo y continuo: las estaciones AIS ejecutan continuamente este modo para poder realizar la transmisión y recepción de mensajes AIS en todo momento.

- Modo asignado: es programado mediante una autoridad competente que configura los datos en función del área donde se realiza la travesía.

- Modo interrogación: se ejecuta únicamente cuando una estación AIS solicita una respuesta por parte de otra estación AIS sobre un determinado evento durante la travesía.

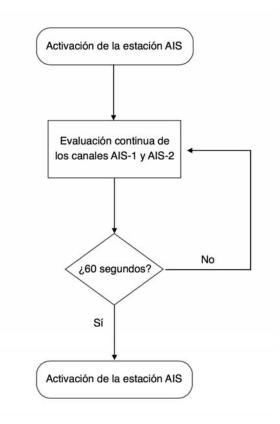

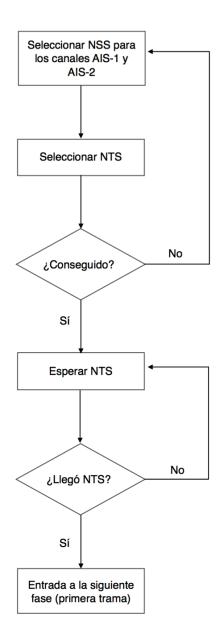

El modo autónomo y continuo comienza con la fase de inicialización, que se establece en el momento en que la estación es activada. El primer paso consiste en monitorizar los canales VHF marítimo del sistema AIS durante 60 segundos. De esta manera, cada estación puede identificar al resto de estaciones activas en su misma región de cobertura, además del estado de los slots a los que pretende acceder (Figura 2.14).

Figura 2.14: Algoritmo de la fase de inicialización en SOTDMA

Una vez la estación monitoriza la actividad de las estaciones en los canales AIS-1 y AIS-2, debe seleccionar un primer slot para presentarse en el sistema. Esta es la *fase de entrada en red*, que consigue que el resto de estaciones conozcan la incorporación de esta nueva estación AIS, y así gestionar el acceso a los slots, teniendo en cuenta que un elemento nuevo competirá con ellas para dicho acceso.

Para ello, lo primero que hace la estación es seleccionar para los canales AIS-1 y AIS-2 los NSS (Nominal Start Slot), llamados  $NSS_A$  y  $NSS_B$ . Considerando un cierto NI (Nominal Increment), se define la siguiente relación:

$$NSS_B = NSS_A + NI \tag{2.5}$$

donde el incremento nominal NI se define como:

$$NI = \frac{2250}{R_r} \tag{2.6}$$

siendo  $R_r$  (Report Rate) el número de informes de posición que el sistema genera cada minuto, de forma que si RI (Reporting Interval) es el intervalo de duración de cada informa, entonces:

$$R_r = \frac{60}{RI} \tag{2.7}$$

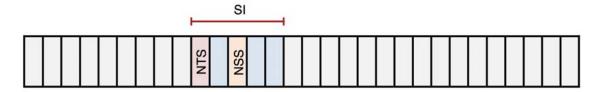

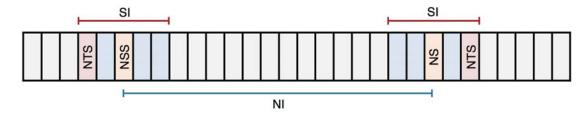

En la Figura 2.15 se observa la selección un intervalo SI con los posibles slots destinados a la transmisión y del NTS, que es el slot que realiza la transmisión.

Figura 2.15: Selección de NTS en un intervalo SI

Cabe destacar que el comienzo de la selección del slot se establece a partir de un NTS (*Nominal Transmission Slot*), que tiene especial relevancia en la tercera etapa de funcionamiento del esquema de acceso SOTDMA (Figura 2.16).

Figura 2.16: Algoritmo de la fase de entrada en red en SOTDMA

La tercera etapa de funcionamiento de SOTDMA es la fase de la primera trama. En esta etapa, cada estación AIS localiza de forma continua los distintos NTS y transmite sobre estos sus informes de posición. Al alcanzar el primer NTS, se seleccionan unos nuevos NS (Nominal Slot) y NTS para las próximas transmisiones que llevará a cabo.

Dicho de otra manera, cuando se selecciona un slot sobre el que se va a realizar una transmisión, se selecciona otro para la próxima transmisión, y así sucesivamente hasta cumplir 60 segundos desde que se alcanza el primer NSS de la transmisión.

Para llevar a cabo este proceso, se almacena en un registro el número de transmisiones efectuadas hasta el momento en el canal, con un tamaño que va desde 0 a  $R_r - 1$ . De esta manera, la selección de NS debe efectuarse conforme a la siguiente expresión:

$$NS = NSS + (n \cdot NI) \qquad \forall \ n \in [0, R_r - 1] \tag{2.8}$$

En la Figura 2.17 se observa la selección del siguiente NS en función del NSS con el que se realiza la transmisión del informe de posición en el slot actual.

Figura 2.17: Selección de NS definido en un NI

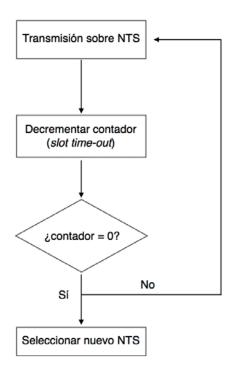

Por último, se establece la fase de operación continua. En esta fase, la estación realiza de forma continua las transmisiones sobre los slots asignados. Un contador (slot time-out) marca los tiempos en que es ocupado el slot de transmisión, y cuando este contador se pone a 0, se selecciona un nuevo NTS sobre el intervalo SI de igual forma a como se establece en la fase de la primera trama (Figura 2.18).

Figura 2.18: Algoritmo de la fase de operación continua en SOTDMA

Esta fase se mantiene hasta que el equipo se apaga, pasa al modo asignado o al modo interrogación o bien si cambia la tasa de actualización de los informes.

### **RATDMA**

El esquema RADTMA (Random Access Time Division Multiple Access) se emplea para anunciar previamente la transmisión aperiódica de slots.

Las estaciones transmisoras que emplean RATDMA usan un *mapa de slots* interno que selecciona aleatoriamente los slots que no están siendo ocupados por otras estaciones. No se anuncia el uso de ningún slot usado para transmisiones aperiódicas (actuales o futuras).

No es aconsejable usar RATDMA en transmisiones periódicas para la asignación de slots. Esto se debe a que RATDMA no permite el reconocimiento de estos slots por otros dispositivos que integren AIS, ya que provienen del mapa de slots interno del dispositivo. De hecho, si se usara para transmisiones periódicas, implicaría serios problemas de colisión de datos que comprometerían el correcto funcionamiento del sistema.

Por ello, RATDMA se suele emplear como técnica de entrada en red por las estaciones AIS clase A. Esto ocurre cuando un dispositivo que integra AIS clase A se conecta a la red y pretende anunciarse por primera vez en la misma. La selección aleatoria del slot inicial que realiza RATDMA mejora considerablemente esta etapa para otros esquemas de mayor calidad, como SOTDMA.

# **ITDMA**

El esquema ITDMA (*Incremental Time Division Multiple Access*) se emplea cuando una estación necesita asignar un slot, pero esta asignación no ha sido anunciada previamente.

A diferencia de RATDMA, con el esquema ITDMA sí se anuncia al resto de estaciones qué slots están siendo ocupados en todo momento. De esta manera, permite que una estación transmisora pueda anunciar un cambio temporal en el intervalo de información que ocupa un mensaje periódico. Por tanto, es posible completar envíos de mensajes aperiódicos (por ejemplo, un mensaje relacionado con la seguridad de la embarcación).

Este esquema se suele emplear, al igual que RATDMA, para la fase de entrada en la red. Sin embargo, necesita apoyarse del esquema SOTDMA, por lo que no se usa como un esquema de acceso independiente como ocurre con RATDMA.

# **FATDMA**

El esquema FATDMA (*Fixed Access Time Division Multiple Access*) se gestiona manualmente para todos los dispositivos AIS que están configurados para utilizar los slots a los que se accede para el resto de transmisiones.

Las estaciones configuradas con FATDMA transmiten un mensaje DLM (Data Link Management), que informan al resto de estaciones que integran este esquema sobre la

asignación de slots, y permiten bloquear estos slots para que no sean ocupados por otras estaciones cercanas.

Este esquema TDMA se usa exclusivamente en las estaciones base AIS y en el sistema AtoN. De hecho, se intenta que su integración no abunde entre dispositivos AIS, ya que puede influir en la dinamización de la asignación de slots en la red AIS.

### **CSTDMA**

El esquema CSTDMA (Carrier Sense Time Division Multiple Access) se emplea como técnica de acceso al medio para transpondedores AIS clase B. Estos transpondedores deben ser compatibles con SOTDMA y garantizar que, en todo momento, SOTDMA tenga prioridad sobre cualquier otro esquema.

Este esquema TDMA no necesita sincronismo UTC directo para operar correctamente, por lo que emplea sincronismo UTC indirecto. De esta manera, el sincronismo entre las estaciones que emplean este esquema deriva de otras estaciones con sincronismo UTC directo (por GPS).

En cuanto a su funcionamiento, las estaciones con CSTDMA monitorizan continuamente el nivel de ruido de fondo en los canales AIS y toman como referencia este nivel de ruido. De esta forma, se logra medir el nivel de la señal al inicio de cada slot. Usando una asignación aleatoria de slots, se mide el nivel de señal al inicio del slot, seleccionado aleatoriamente, y toma la siguiente decisión:

- Si el nivel de señal es superior al nivel de ruido de referencia, asume que ese slot está en uso y, por tanto, no accede al mismo.

- Si el nivel de señal es inferior al nivel de ruido de referencia, asume que ese slot está libre y, por tanto, accede al mismo.

La principal desventaja de este sistema, frente a la ventaja económica indiscutible que supone la integración de este esquema de acceso sobre transpondedores AIS, es que requiere la existencia de estaciones AIS que empleen otros esquemas de mayor calidad, como SOTDMA, para poder sincronizarse con el resto de estaciones.

Además, una mala medida del nivel de referencia de ruido en el canal puede ocasionar que las estaciones que integran CSTDMA interfieran sobre los slots en uso y provocar la colisión de paquetes. Es por ello por lo que normalmente se emplea en equipos receptores.

### **PATDMA**

El esquema PATDMA (*Pre-Announced Time Division Multiple Access*), también conocido como *SOTDMA modificado*, es un esquema de acceso basado en SOTDMA que se utiliza para anunciar futuras transmisiones. Está destinado únicamente a los dispositivos de transmisión.

Las estaciones PATDMA seleccionan de forma aleatoria el slot que se utiliza para transmitir. La primera transmisión anuncia la intención de utilizar este slot durante 8 minutos para la siguiente transmisión, y una vez transcurre este primer periodo, se selecciona aleatoriamente el siguiente slot. Por ello, las transmisiones se realizan en ráfagas de 8 mensajes (un mensaje por minuto), garantizando de esta manera que la transmisión tenga éxito cuando se establece la comunicación cerca de la superficie del mar, pues podría bloquearse por el oleaje u otros fenómenos adversos.

El hecho de que PATDMA use un sistema de acceso aleatorio a los slots implica que el esquema sea más sensible a las colisiones de paquetes. Por ello, suele aplicarse casi exclusivamente en boyas de salvamento marítimo, puesto que no reciben una cantidad masiva de datos como ocurre en el resto de estaciones AIS.

# 2.4. Tipos de mensajes AIS

La información compartimentada entre las estaciones AIS depende de la tecnología del transpondedor AIS que ofrece el servicio. En cualquier caso, la clasificación de los mensajes AIS para cualquier tipo de transpondedor AIS es la siguiente:

- Información estática: está referida a todos aquellos parámetros propios de una embarcación que permiten identificarla, de manera unívoca, frente al resto de estaciones:

- MMSI (Maritime Mobile Service Identity).

- Nombre de la embarcación.

- Tipo de embarcación.

- Dimensiones físicas.

- Bandera del país de origen de la embarcación.

- Información dinámica: está referida a la información variable durante una travesía y que es de especial importancia para un correcto control de las operaciones marítimas provistas del sistema AIS:

- Posición.

- Velocidad.

- Trayectoria.

- Estado de la navegación.

- Información sobre el viaje: el usuario puede introducir manualmente algunos datos relevantes acerca de la travesía marítima y que no son monitorizados de forma automática por el sistema AIS.

Además de la clasificación de los mensajes AIS según su aplicación, se abre una nueva clasificación que diferencia en mensajes simples y mensajes compuestos [17].

Los mensajes simples contienen la información más básica de la embarcación (Figura 2.19), y se envían en diferentes intervalos de tiempo en función de la velocidad del buque. Si el barco está anclado o atracado, cada 3 minutos envía un informe de posición. Si está en movimiento, con una velocidad menor a 14 nudos, los informes se envían cada 10 segundos, y si supera los 14 nudos, las tasas de actualización varían entre 6 y 2 segundos, dependiendo si la embarcación cambia su rumbo.

| MENSAJE SIMPLE |  |

|----------------|--|

| 1. MMSI        |  |

| 2. Nombre      |  |

| 3. Latitud     |  |

| 4. Longitud    |  |

| 5. Velocidad   |  |

| 6. Rumbo       |  |

| 7. Status      |  |

| 8. Fecha       |  |

| 9. Hora        |  |

Figura 2.19: Campos incluidos en un mensaje AIS simple

Por otro lado, los mensajes compuestos incorporan información adicional sobre la travesía de la embarcación que envía este mensaje (Figura 2.20), y son enviados cada 6 minutos.

| MENSAJE COMPUESTO |                                                     |           |  |

|-------------------|-----------------------------------------------------|-----------|--|

| 1. IMO            | 10. Tipo embarcación 19. Eslora                     |           |  |

| 2. MMSI           | 11. Indicativo radio                                | 20. Manga |  |

| 3. Latitud        | 12. Bandera 21. Calado                              |           |  |

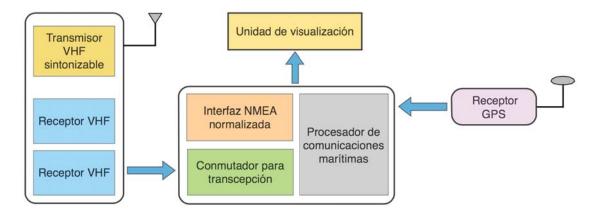

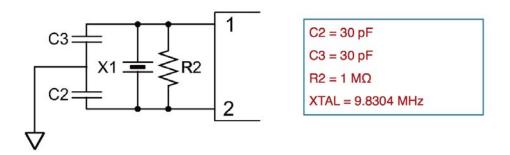

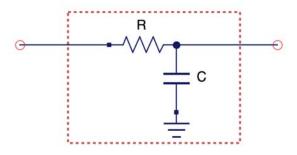

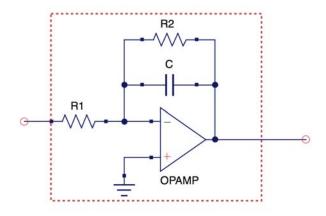

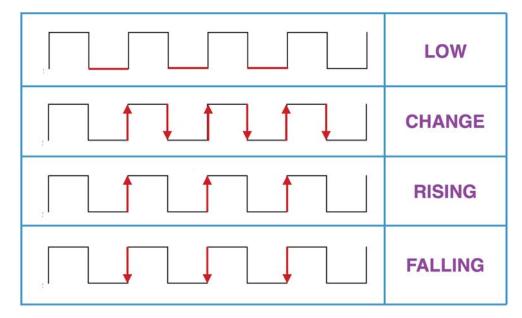

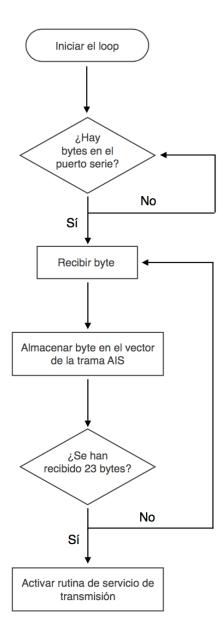

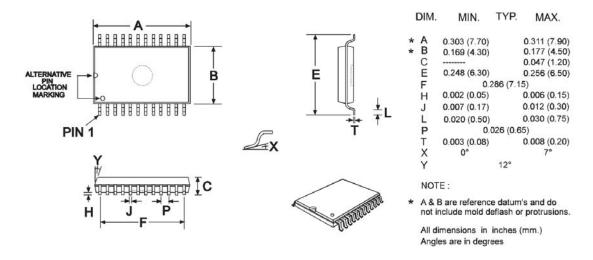

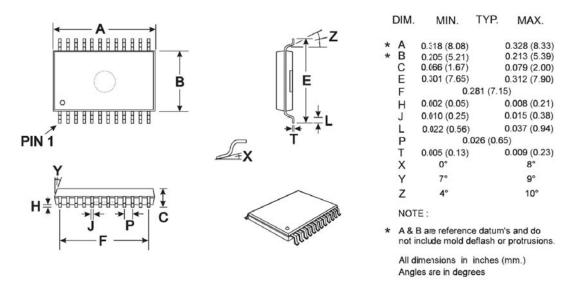

| 4. Longitud       | 13. Puerto actual 22. Tonelaje bruto                |           |  |