# © Universidad de Las Palmas de Gran Canaria. Biblioteca Digital, 2004

#### UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

#### **DEPARTAMENTO DE INFORMÁTICA Y SISTEMAS**

#### **TESIS DOCTORAL**

ACELERADORES VECTORIALES PARA PROCESADORES SUPERESCALARES

#### FRANCISCA QUINTANA DOMÍNGUEZ

Las Palmas de Gran Canaria, Noviembre del 2001

#### 27/2001-02 UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA UNIDAD DE TERCER CICLO Y POSTGRADO

Reunido el día de la fecha, el Tribunal nombrado por el Excmo. Sr. Rector Magfco. de esta Universidad, el/a aspirante expuso esta TESIS DOCTORAL.

Terminada la lectura y contestadas por el/a Doctorando/a las objeciones formuladas por los señores miembros del Tribunal, éste calificó dicho trabajo con la nota de

Las Palmas de Gran Canaria, a 19 de diciembre de 2001.

El/a Presidente/a: Dr.D. Roberto Moreno Díaz,

El/a Secretario/a: Dr.D. Enrique Fernández García,

El/a Vocal: Dr.D. José María Llabería Griñó,

El/a Vocal: Dr.D. Francisco Tirado Fernández,

El/a Vocal: Dr.D. Emilio López Zapata,

La Doctoranda: Da. Francisca Candelaria Quintana Domínguez,

# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

## Departamento de Informática y Sistemas

## **TESIS DOCTORAL**

# ACELERADORES VECTORIALES PARA PROCESADORES SUPERESCALARES

Francisca Quintana Domínguez

Las Palmas de Gran Canaria

Noviembre de 2001

# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# Departamento de Informática y Sistemas

Tesis doctoral titulada **ACELERADORES VECTORIALES PARA PROCESADORES SUPERESCALARES**, que presenta Dña. Francisca Quintana Domínguez, realizada bajo la dirección de los doctores D. Mateo Valero Cortés y D. Roger Espasa Sans.

Las Palmas de Gran Canaria, Noviembre de 2001

La doctoranda

Los directores

Dña. Francisca Quintana Domínguez D. Mateo Valero Cortés D. Roger Espasa Sans

#### **ACKNOWLEDGMENTS**

Quiero agradecer a Mateo Valero y Roger Espasa, mis directores de tesis, su guía y su apoyo durante la realización de esta tesis. Mateo, que me aceptó como doctoranda sin conocerme, ha sido más que un director. Siempre me ha aconsejado honradamente y me ha ayudado en todo lo que le he pedido y más. Roger, con quien he discutido hasta la saciedad, ha sido insuperable como compañero de fatigas. Supe que había terminado esta tesis cuando por fin le gané una discusión. A los dos, muchas gracias.

También me gustaría agradecer a todo el personal del Departamento de Arquitetura de Computadores de la UPC lo bien que me han tratado durante estos años. Con ellos he compartido no sólo el lugar de trabajo, sino también muchas sobremesas entretenidas, algunas juergas, días de playa y un montón de buenos momentos. Me gustaría mencionar especialmente a Montse Peirón, mi primera amiga en Barcelona, Roger Espasa y Marta Jiménez, que confiaron tanto en mi como para dejarme su propia casa, Agustín Fernández, Fermín Sánchez, Dolors Royo, Toni Juan, Josep Llosa, David López, Susana Moreno, Anna del Corral, Jesús Corbal, Cristina Coll y tantos otros. Me gustaría aprovechar esta ocasión para agradecer también a Teresa Monreal los buenos momentos vividos mientras compartimos piso en Barcelona. Afortunadamente, el choque inicial no fue un presagio de lo que luego nos divertiríamos.

Este trabajo no habría sido posible sin el soporte técnico extraordinario del Laboratorio de Cálculo del Departamento de Arquitectura de Computadores de la UPC y del Centro Europeo de Paralelismo de Barcelona. Víctor Mora, Oriol Riu, Judit Jiménez, y en general todos los que allí trabajan, son extraordinarios profesionales. Me gustara agradecer al CEDEX que nos hayan permitido acceder al Convex C4 que poseen, y a Mayte Castro, la ayuda prestada, especialmente durante el terrible "efecto 2000".

⊚ Universidad de Las Palmas de Gran Canaria. Biblioteca Digital, 2004

Me gustaría agradecer también a mis compañeros del Departamento de Informática y Sistemas, en especial los del área de Arquitectura y Tecnología de Computadores, su apoyo durante todo este tiempo. Ricardo Pérez es un maravilloso compañero de despacho que me alegra la vida con su caracter polifacético. A Carmelo Cuenca, amigo de tantos años, tengo que agradecerle que siempre haya creído en mi, y que me haya apoyado.

Muchas otras personas han contribuido también con su apoyo a que esta tesis salga adelante: Alvaro Suárez me dio el empujón para saltar el charco; Kiko de Sande y Paco Almeida me facilitaron mucho los momentos iniciales; Jose López me ha animado mucho con sus correos al principio y con su presencia al final; Miguel Alemán, amigo reciente, me ha alentado durante estos últimos meses.

Mis padres y mis hermanos siempre han estado ahí, apoyándome y animándome a seguir adelante. A ellos les agradezco su cariño y aliento de tantos años. En especial a mi madre, que se ha encargado siempre de esas pequeñas cosas que no se notan, pero que me han hecho la vida más fácil, sobre todo en los últimos tiempos. Finalmente, a Abraham tengo que agradecerle su amor, su paciencia, su apoyo, y muchas cosas más. Y aunque parezca una broma, a Tricky le agradezco que haya servido de excusa para estirar las piernas y meditar un poco. A todos ellos va dedicado este trabajo.

Este trabajo ha sido realizado gracias a la colaboración de: el Gobierno Autónomo de Canarias, la CICYT (proyectos TIC 0429/95, TIC98-0511-C02-01 y TIC2001-0995-C02-01), la Universidad de Las Palmas de Gran Canaria, el Departamento de Informática y Sistemas de la ULPGC, la Fundación Universitaria de Las Palmas, el Departamento de Arquitectura de Computadores de la UPC, el Centro Europeo de Paralelismo de Barcelona (CEPBA) y el CEDEX.

### CONTENTS

| 1 | IN            | TRODUCTION                                      | 1  |

|---|---------------|-------------------------------------------------|----|

|   | 1.1           | Motivations                                     | 2  |

|   | 1.2           | Sources of parallelism                          | 4  |

|   | 1.3           | ILP Paradigm                                    | 7  |

|   | 1.4           | DLP Paradigm: Another source of parallelism     | 11 |

|   |               | 1.4.1 DLP: Past, Present and Future             | 14 |

|   | 1.5           | Related Work                                    | 21 |

|   | 1.6           | A suitable application space for exploiting DLP | 25 |

|   | 1.7           | Thesis Overview                                 | 27 |

|   |               | 1.7.1 Structure of this work                    | 30 |

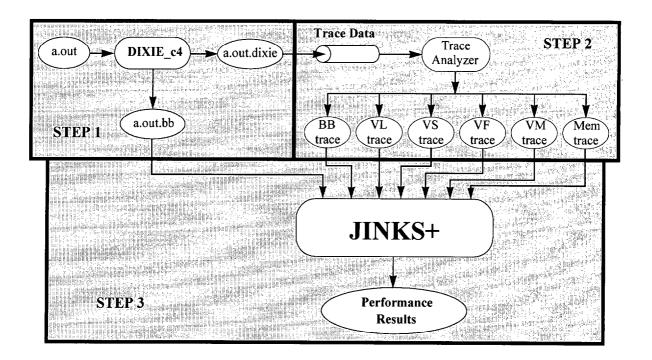

| 2 | $\mathrm{TR}$ | ACING AND SIMULATION TOOLS, BENCHMARKS          |    |

|   | AN            | D METRICS                                       | 33 |

|   | 2.1           | Introduction                                    | 34 |

|   | 2.2           | Tracing and Simulation Tools                    | 34 |

|   |               | 2.2.1 Vector tracing tool: Dixie-c4             | 34 |

|   |               | 2.2.2 Scalar tracing tool: Atom                 | 37 |

|   |               | 2.2.3 Parameterizable Simulator: Jinks+         | 37 |

|   | 2.3           | Convex C4 Vector Architecture                   | 38 |

|   | 2.4           | Alpha EV6 Scalar Architecture                   | 40 |

|   | 2.5           | Benchmark Programs                              | 42 |

|   |               | 2.5.1 Numerical Benchmarks                      | 42 |

|   |               | 2.5.2 Multimedia Benchmarks                     | 44 |

|   | 2.6  | Benchmark Modifications                                  | 45  |

|---|------|----------------------------------------------------------|-----|

|   |      | 2.6.1 Modifying Multimedia benchmarks for vectorization  | 45  |

|   |      | 2.6.2 Manual Stripmining                                 | 46  |

|   |      | 2.6.3 Slicing a Program into Regions                     | 48  |

|   | 2.7  | The Quality of the scalar code in vector programs        | 49  |

|   | 2.8  | The EIPC Performance Measure                             | 51  |

| 3 | SC   | ALAR AND VECTOR ISAS COMPARISON                          | 53  |

|   | 3.1  | Introduction                                             | 54  |

|   | 3.2  | Benefits of Vector ISA                                   | 55  |

|   | 3.3  | Basic Block Distribution                                 | 58  |

|   | 3.4  | Instruction Breakdown                                    | 59  |

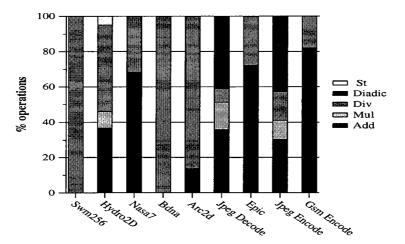

|   | 3.5  | Operation Distribution                                   | 63  |

|   | 3.6  | Distribution of Data types                               | 66  |

|   | 3.7  | Vector Characterization                                  | 67  |

|   |      | 3.7.1 Vectorization Percentage and Average Vector Length | 67  |

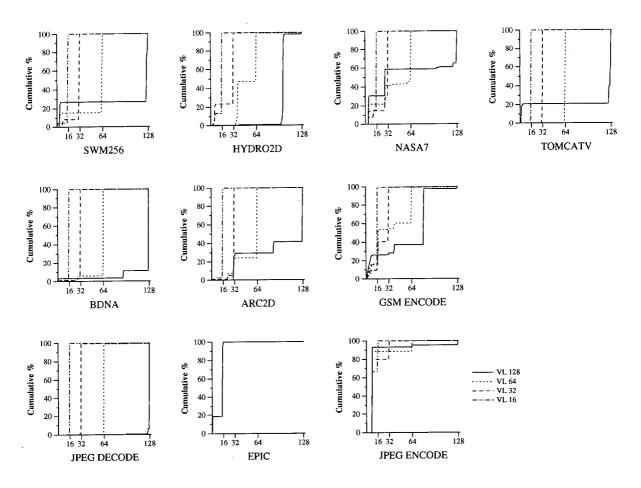

|   |      | 3.7.2 Vector Length Distribution                         | 69  |

|   |      | 3.7.3 Vector Stride Distribution                         | 71  |

|   |      | 3.7.4 Vector First Capability                            | 72  |

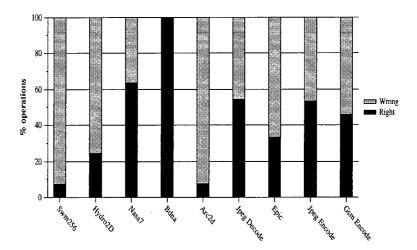

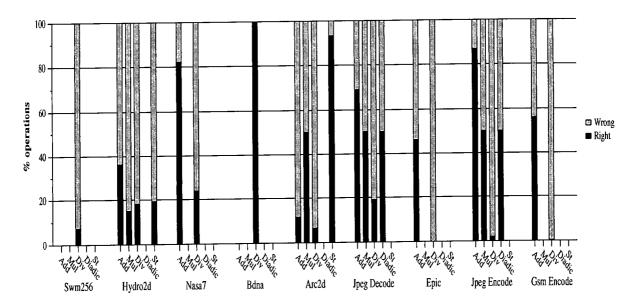

|   |      | 3.7.5 Vector Mask Execution                              | 74  |

|   | 3.8  | Influence of the Vector Length                           | 77  |

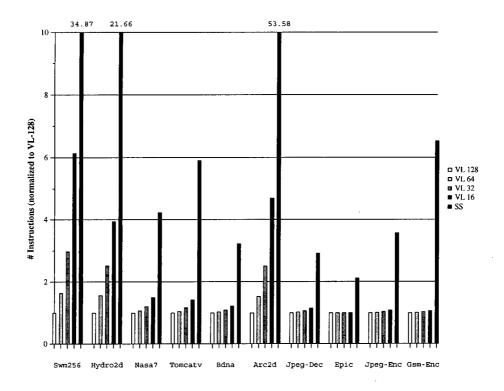

|   |      | 3.8.1 Instructions Executed                              | 78  |

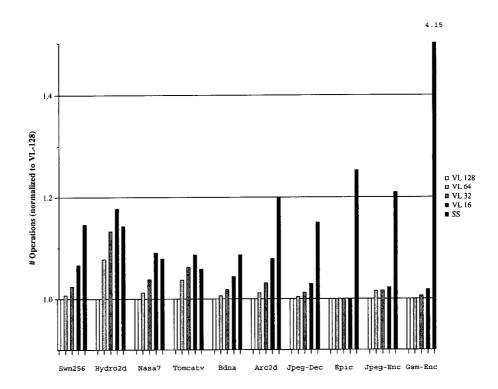

|   |      | 3.8.2 Operations Executed                                | 79  |

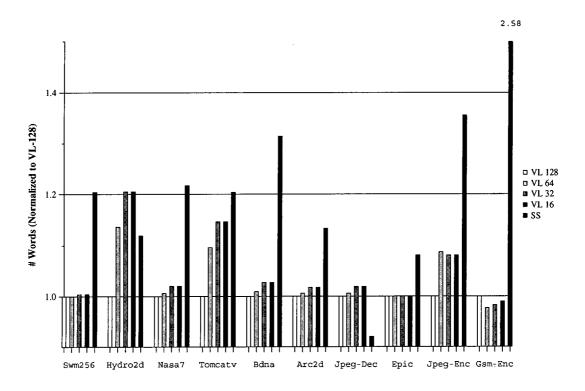

|   |      | 3.8.3 Processor-Memory Traffic                           | 81  |

|   | 3.9  | Analysis by Regions                                      | 82  |

|   |      | 3.9.1 General Characteristics of S-regions and D-regions | 83  |

|   |      | 3.9.2 Basic Block Distribution                           | 84  |

|   |      | 3.9.3 Instruction Breakdown                              | 85  |

|   |      | 3.9.4 Operation Distribution                             | 97  |

|   | 2 10 | Hybrid Renchmarks for Vector Execution: Characteristics  | 100 |

|   |      | 3.10.IInstruction Breakdown                         | 101 |

|---|------|-----------------------------------------------------|-----|

|   |      | 3.10.20 peration Distribution                       | 101 |

|   |      | 3.10.3 Vector Characteristics                       | 102 |

|   | 3.11 | Summary                                             | 104 |

| 4 | A S  | SUPERSCALAR PROCESSOR WITH A VECTOR UNIT            | 107 |

|   | 4.1  | Introduction                                        | 108 |

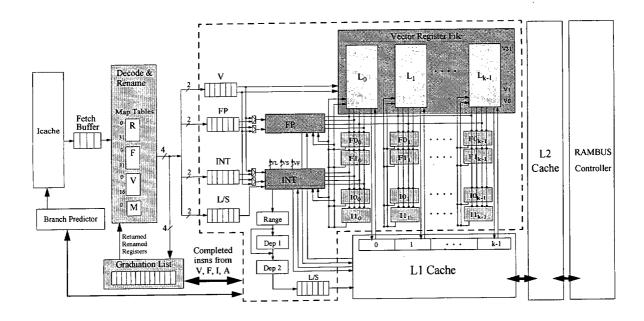

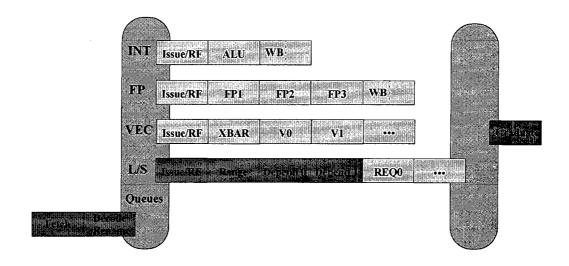

|   | 4.2  | General Datapath                                    | 109 |

|   | 4.3  | The Memory Hierarchy                                | 116 |

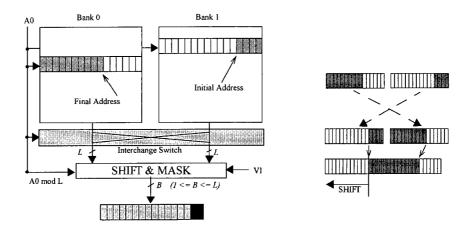

|   |      | 4.3.1 The Vector Cache: A Cache for Vector Accesses | 116 |

|   |      | The bandwidth problem                               | 116 |

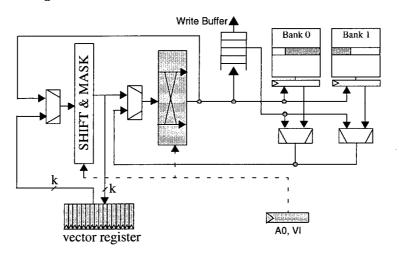

|   |      | The vector cache                                    | 119 |

|   |      | The write buffer                                    | 121 |

|   |      | The non-blocking mechanism                          | 122 |

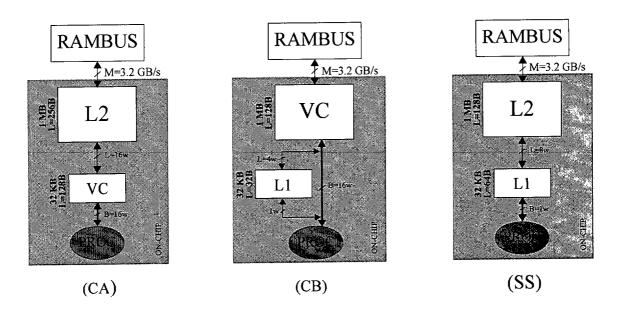

|   |      | 4.3.2 Cache Hierarchy                               | 123 |

|   |      | Model A: Vector Cache in L1                         | 123 |

|   |      | Model B: Vector Cache in L2                         | 125 |

|   |      | Coherency Protocol in the Memory System             | 125 |

|   |      | 4.3.3 RAMBUS Main Memory                            | 126 |

|   | 4.4  | Summary                                             | 127 |

| 5 | РО   | TENTIAL PERFORMANCE AND SCALABILITY                 | 131 |

|   | 5.1  | Introduction                                        | 132 |

|   | 5.2  | Machine Configurations                              | 135 |

|   | 5.3  | Perfect Cache and Scalability                       | 141 |

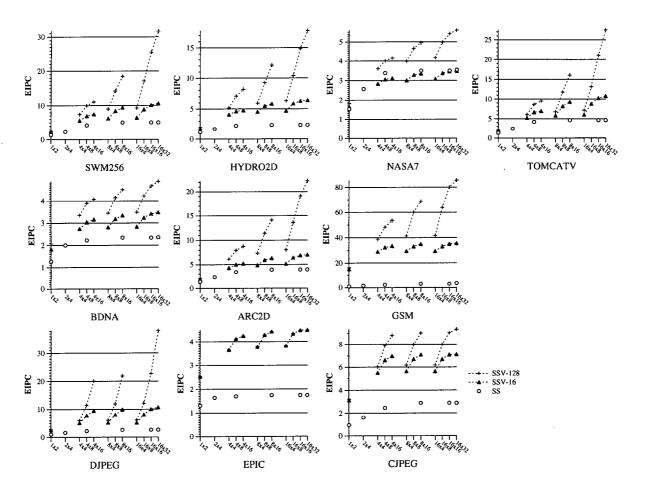

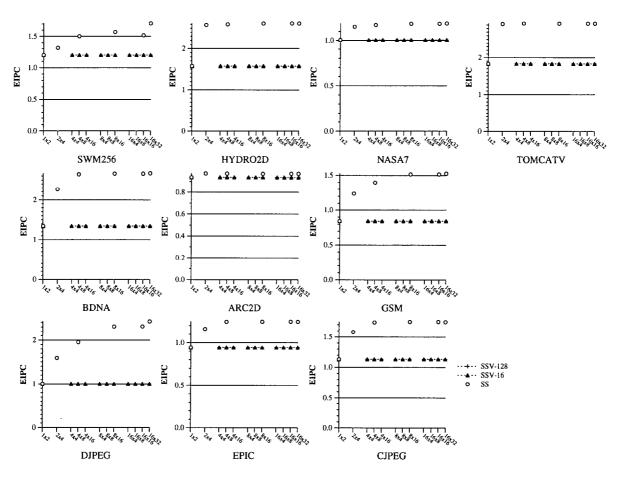

|   |      | 5.3.1 General Performance                           | 141 |

|   |      | 5.3.2 Performance Breakdown by Regions              | 145 |

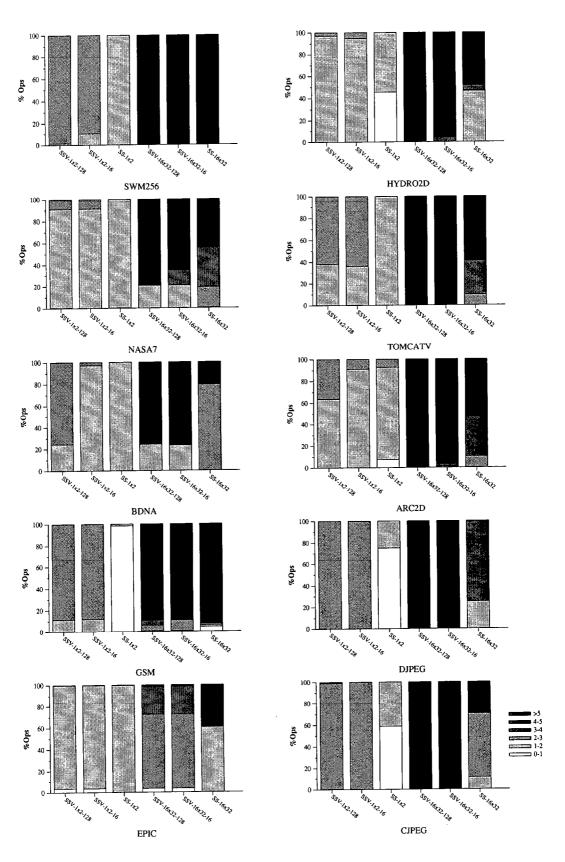

|   |      | 5.3.3 Data Parallelism Inside Vector Regions        | 150 |

|   | 5.4  | Real Memory Hierarchy                               | 153 |

|   |      | 5.4.1 Processor Configurations                      | 153 |

|   |      | 5.4.2 Memory Hierarchy Configurations               | 154 |

|     |             | 5.4.3 Cache Hierarchy Efficiency                                     | 158                                                                                                                                                                                                                    |

|-----|-------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

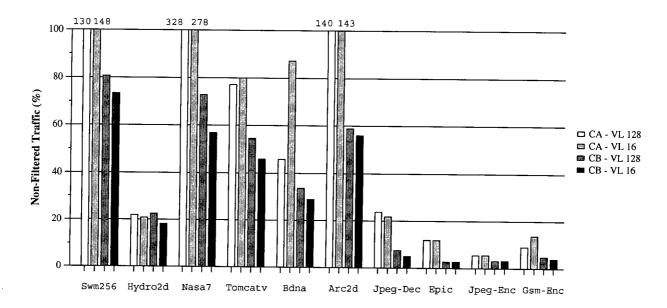

|     |             | Memory Traffic Filtered                                              | 159                                                                                                                                                                                                                    |

|     |             | Cache Hit Rate                                                       | 162                                                                                                                                                                                                                    |

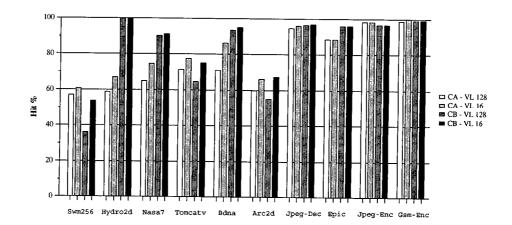

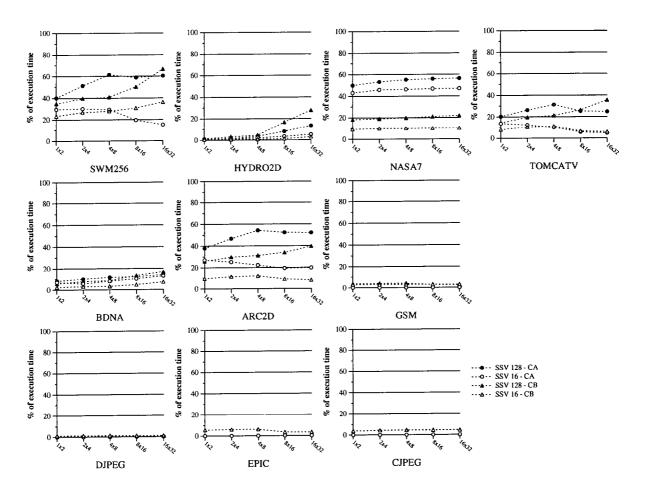

|     |             | 5.4.4 Vector Cache Stall Time and Bottlenecks                        | 163                                                                                                                                                                                                                    |

|     |             | 5.4.5 Performance Evaluation                                         | 173                                                                                                                                                                                                                    |

|     |             | General Performance                                                  | 173                                                                                                                                                                                                                    |

|     |             | Performance Breakdown by Regions                                     | 176                                                                                                                                                                                                                    |

|     |             | 5.4.6 Data Parallelism Inside Vector Regions                         | 179                                                                                                                                                                                                                    |

|     | 5.5         | Summary                                                              | 182                                                                                                                                                                                                                    |

| 6   |             | PROVING PERFORMANCE BY TUNING THE MEMORY                             | 107                                                                                                                                                                                                                    |

|     |             | ERARCHY Introduction                                                 | 187                                                                                                                                                                                                                    |

|     | 6.1         |                                                                      |                                                                                                                                                                                                                        |

|     | 6.2         | Increasing Non-Blockingness                                          |                                                                                                                                                                                                                        |

|     | 6.3         | Additional memory port for scalar accesses                           |                                                                                                                                                                                                                        |

|     | 6.4         | Improving Main Memory Bandwidth                                      |                                                                                                                                                                                                                        |

|     | 6.5         | Effects of Microprocessor Integration                                | 205                                                                                                                                                                                                                    |

|     | 6.6         | Attacking the Stride problem: Collapsing and Multi-Address Secondary |                                                                                                                                                                                                                        |

|     |             | Caches                                                               | 209                                                                                                                                                                                                                    |

|     |             | 6.6.1 General Performance                                            | 212                                                                                                                                                                                                                    |

|     |             | 6.6.2 Performance inside D-regions                                   | 214                                                                                                                                                                                                                    |

|     | 6.7         | Summary                                                              | 216                                                                                                                                                                                                                    |

| 7   | СО          | NCLUSIONS AND FUTURE WORK                                            | 219                                                                                                                                                                                                                    |

|     | 7.1         | Conclusions                                                          | 220                                                                                                                                                                                                                    |

|     | 7.2         | Future Work                                                          | 227                                                                                                                                                                                                                    |

| LIS | <b>вт</b> О | F FIGURES                                                            | nory port for scalar accesses  197  Memory Bandwidth 200  processor Integration 205  tride problem: Collapsing and Multi-Address Secondary 209  erformance 212 nce inside D-regions 214  AND FUTURE WORK 219  220  227 |

| LIS | вт О        | F TABLES                                                             | 240                                                                                                                                                                                                                    |

| RE  | FEF         | RENCES                                                               | 241                                                                                                                                                                                                                    |

#### **Summary**

In this chapter we present the motivations behind this thesis. Current trends in the exploitation of the different sources of parallelism are presented, especially describing the data-level parallelism (DLP) paradigm and its related advantages. This chapter also analyzes different applications of DLP in past and present computers. The relation of this thesis with previous and current research works is presented, and some comments are made about the application characteristics that are suitable for executing in DLP processors.

2 Chapter 1

#### 1.1 MOTIVATIONS

Over the last two decades, microprocessors have enjoyed a continuous increase in performance and attendant reduction in price/performance [Sla96] [Yu96] [Mal95]. Among the different emerging tendencies, superscalar processors have succeeded in different marketplaces [Sit92] [BDHS94] [Hun95] [TGN95] [WPS95] [Yag96] [Chr96] [Kel96] [Pap96]. From the initial two-way execution in HP PA7100 [AAD+93], DEC Alpha [Sit92], Intel Pentium [AA93] and IBM PowerPC [SDC94], much research efforts have been devoted to the development and enhancement of new and existing techniques that can provide better performance. All these techniques deal with topics such as instruction caches [SV87] [CMMP95] [LBCG95] [WOR96] [WO97], branch prediction [McF93] [YMP93] [SJSM96] [Zha96] [JSN98], register file organization [FJC96] [WB96], register renaming [SP94] [GGV98] [JRB+98], the increasing number of instructions issued for execution [SV87] [FS94], dynamic instruction scheduling and out-of-order execution [PJS97] [VM97], and data caches [WO95] (including multilevel caches [JW94], data prefetching [Zha96] [Vei97], non-blocking accesses [Kro81] [CB92], multiported caches [WOR96], and others [JNT97] [SF91]).

All these improvements have allowed walking one step forward in the performance gain path. Current best of breed microprocessors operate at frequencies over 1GHz [Int00] [Kah99] and offer superscalar instruction dispatch, sophisticated branch prediction techniques and support for high performance memory systems, including on-chip second level caches [Int00] [Kah99] [Kes99] [Yag96] [Kum96]. These advances do not come without a price, and all these techniques are getting even more complicated, as can be seen when looking at complex instruction caches [RQJS97] and value speculation mechanisms [GM96].

Given that, as technology evolves, an increasing number of transistors will be included on a single chip [Yu96], the question is how future processors will use these additional transistors. The majority of current processors have been focused on techniques aimed at exploiting more and more instruction level parallelism [Eme99] [Kah99]. However, measurements of actual performance of applications running on machines exploiting instruction level parallelism, show that the actual performance achieved falls very short

of the theoretical peak performance of the machines [CB96]. Many studies have pointed out that this lack of performance can be due to different effects, such as data and instruction cache misses, branch mispredictions, memory dependences or lack of program parallelism [Wal91] [LW92] [BGB98].

Therefore, although the exploitation of instruction level parallelism has yielded large performance improvements, and scaling current superscalar processors to achieve large amounts of ILP is an area of very active research, there is a growing consensus that this scaling can not be done by simply trying to fetch, decode and issue more and more instructions per cycle [PJS96] [PJS97] [AHKB00]. Some of the reasons are:

- First of all, an aggressive fetch and decode engine must be designed, which is far from being trivial due to branches as well as instruction cache bandwidth issues [PW94] [RBS96] [CMMP95] [RLPN+99].

- Second, an aggressive issue engine, with a large instruction window, is required to be able to feed a large number of functional units [HKLS00]. The instruction window lookup time increases quadratically with the window size [PJS97].

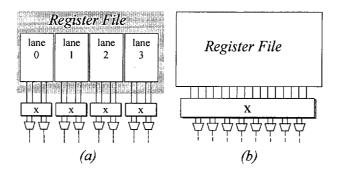

- Third, to issue a large number of instructions a heavily multiported register file is needed, which can both endanger the cycle time and consume a large amount of chip area [CGVT00].

- Also, sustaining multiple memory accesses per cycle requires a multiported TLB and cache, and their cost is also proportional to the number of independent memory ports [JNT97] [BGK96].

All these aspects make the scalability of superscalar processors expensive and strongly technology-dependent [AHKB00]. Moreover, even if these problems can be overcome with future technology, the performance results generally do not pay off the amount of chip area and the design effort required [LWS96] [QCEV99], as we will see along this thesis.

Therefore, we think that we should exploit more than one source of parallelism in order to overcome the scalability problems of current superscalar architectures. We

will first analyze, in the following section, the different sources of parallelism available in programs, and how they are being exploited in current processors.

#### 1.2 SOURCES OF PARALLELISM

There are different sources of parallelism in programs: instruction level parallelism, thread level parallelism and data level parallelism. Let us analyze each of them in more detail.

#### Instruction level parallelism

Among the different sources of parallelism, the instruction level parallelism (ILP) has been one of the most exploited sources [RF93]. A program presents ILP whenever different instructions of a single control flow can be executed in parallel and the program result is not altered. The detection of the instructions that can be executed in parallel can be done at compilation time or at run time. In the first case, the compiler selects groups of instructions that can be executed in parallel [Gas89]. These instructions are typically packed in a single instruction. The architectures that exploit ILP in this way are called Very Long Instruction Word (VLIW) architectures because of the large multioperation instructions that are generated by the compiler [KM89] [PSW91] [Gas91]. The Intel-HP's Itanium [Sha99] is an example of VLIW-based processor. It has builtin parallelism description to avoid "searching" for ILP that the compiler already knew about. The concept behind VLIW is to make hardware scheduling decisions visible to the compiler, which could make its own optimizations [Lam88]. VLIW processors also employ new techniques [EGK+94] [Rau93], such as predication and speculation, which allow a processor anticipating and performing calculations before the need for the calculation, or the validity of data, can be fully checked. Of course, the drawback of these approaches is that results of speculative executions are often tossed out when the data can not be validated, and the practice of profiling code for VLIW processors creates an unnecessary software burden.

The exploitation of ILP at run time is mainly supported in current superscalar processors [Joh91]. In these processors, instructions are fetched, decoded, renamed and sent to the execution queues where they execute when their operands are available. This way of detecting and exploiting ILP is more flexible as the hardware has full information about the dependences between instructions (as opposed to the limited static information available to a compiler) [RF]. Looking at current superscalar microprocessors roadmaps, there is a disparity on how to exploit ILP and improve performance, without incurring in excessive circuit complexity that may result in clock speed limitations [AHKB00]. On one end, the Alpha 21464 [Eme99] and Power4 [Kah99] processors are going for 8-wide issue. On the other, Intel's Pentium4 [Int00] is an attempt at extreme clock frequency with limited issue width. This processor has a trace cache [PW94] that delivers up to 3 micro operations per clock cycle to the core but, in return, it provides a very fast clock by using hyper pipelined technology.

#### Thread level parallelism

Another source of parallelism is the thread level parallelism (TLP). A program presents TLP if it can be decomposed in different threads, or groups of instructions, that can be concurrently executed, whether speculatively or not. This approach yields a system with higher throughput and better resource utilization.

One of the types of TLP is the simultaneous multithreading (SMT) [TEL95]. In this case, instructions from different threads coexist at the same time in the reorder buffer. In each processor cycle, the processor issues to execution instructions from different threads. A few bits of thread information in the instruction queues and per-thread rename tables are needed in this case. One example of this trend is the announcement of the Alpha 21464 [Eme99] being a simultaneous multithreaded processor. This processor can execute as many as eight instructions in a clock cycle. To fully exploit that potential, this processor uses out-of-order execution and special fetching techniques to create four virtual "thread processing units" that make the CPU look like a four-way multiprocessing system. This processor will be first used at the high-end server space, where multiprocessing-ready applications already exist. Outside that space, however, there is no such code, and to use the 21464's virtual thread processors optimally, ap-

Chapter 1

plications would have to be tuned to the realities of the underlying hardware resources that are shared among the virtual thread processors. This effort in the software field is the major drawback of the thread level parallelism approach, as it requires a significant transition towards multithreaded software models.

There is also another approach for exploiting the TLP paradigm. It is called chip multiprocessing (CMP) and it is based on putting more than one processor core in a single chip. IBM uses CMP on its Power4 processor [Kah99], as well as Compaq does in Piranha [BGM+00]. This proposal does not suffer from the software support drawback, but incurs in the extra cost of putting two processors on a single large -and sometimes hot- die. The problem in CMP is the increasing number of pins that are needed, so the memory bandwidth becomes a bottleneck and prevents from achieving sustained performance.

#### Data level parallelism

Finally, the third another source of parallelism in programs is data level parallelism (DLP). A program presents data level parallelism whenever there is a piece of code (normally a loop) that executes the same operation over a stream of data [PH96] [Fly97]. These data are usually allocated in data structures like vectors or matrices. The operation can be carried out over consecutively allocated data, or over elements that are separated in memory a fixed amount of positions, called stride. The number of elements on which the operation is carried out is called the vector length. Exploiting data level parallelism in loops decreases the number of instructions and operations executed. Moreover, vector instructions provide with a large amount of work, as large as the vector length, that will keep the functional units busy for many cycles.

Although many processors have used DLP exploitation in their design [Rus78] [IW91] [Oed92], only two companies are currently manufacturing processors that exploit word level parallelism, NEC [vdSD01c] and Cray [BS00]. Over the last few years, however, there has been a growing interest on ISA extensions aimed at exploiting sub-word level parallelism, such as MMX [PW96], Altivec [NJ99], MAX [Lee96], VIS [Koh95] or MDMX [MIP97]. This is also a form of data level parallelism in which short data

are packed on a in single register and operations are carried out simultaneously on the different register elements.

All in all, some of the different parallelism paradigms discussed above are orthogonal from each other and in practice they are implemented together in a single processor. For example, the IBM Power4 [Kah99] has two processors on a chip, each of them issuing several instructions in each cycle. The Alpha 21464 [Eme99] executes up to four threads simultaneously, and each of them can issue out-of-order eight instructions per cycle. In the limit case, we could have several processors on a single chip, each of them could be simultaneous multithreaded and could extract ILP by issuing several instructions per cycle. This is an important idea that leads us to conclude that there are several natural sources of parallelism in programs, and each microprocessor tries to achieve high performance by exploiting some of them. In this thesis we rely on this idea, and we propose a processor design that exploits data-level parallelism coupled with traditional superscalar ILP execution. This processor will be backed with a especially designed cache hierarchy aimed at accessing vector and scalar data. Our design reaches performance values for numerical and multimedia applications that the superscalar processor can not achieve on its own.

Since our proposal is based on a fusion of ILP and DLP, let us take an in depth look at these two paradigms.

#### 1.3 ILP PARADIGM

The ILP paradigm is mainly exploited in current superscalar architectures [Joh91] [SS95] [SFK97]. Table 1.1 presents the different characteristics of some of the current superscalar processors. These processors use different techniques aimed at detecting and exploiting instruction level parallelism:

Pipelining. The pipelined execution of instructions exploits instruction level parallelism since different parts of the different instructions are executed simultaneously.

In a pipelined datapath the execution of each instruction is carried out following

Chapter 1

| Processor       | Alpha<br>21264C | AMD<br>AthlonMP | HP<br>PA-8600 | IBM<br>Power3-II | Intel<br>Itanium | Intel<br>Pentium4 | MIPS<br>R14000 | Sun<br>Ultra-II | Sun<br>Ultra-III |

|-----------------|-----------------|-----------------|---------------|------------------|------------------|-------------------|----------------|-----------------|------------------|

|                 | 1               |                 |               |                  |                  | 1                 |                |                 |                  |

| Clock Rate      | 1001 MHz        | 1.2 GHz         | 552 MHZ       | 450 MHZ          | 800 MHz          | 1.8 GHz           | 500 MHz        | 480 MHz         | 900 MHz          |

| Cache (I/D/L2)  | 64K/64K         | 64K/64K/256K    | 512K/1M       | 32K/64K          | 16K/16K/96K      | 12K/8K/256K       | 32K/32K        | 16K/16K         | 32K/64K          |

| Issue Rate      | 4 issue         | 3 x86instr      | 4 issue       | 4 issue          | 6 issue          | 3 ROPs            | 4 issue        | 4 issue         | 4 issue          |

| Pipeline Stages | 7/9             | 9/11            | 7/9           | 7/8              | 10               | 22/24             | 6              | 6/9             | 14/15            |

| Out of order    | 80 instr        | 72 ROPs         | 56 instr      | 32 instr         | None             | 126 ROPs          | 48 instr       | None            | None             |

| Rename Regs     | 48/41           | 36/36           | 56 total      | 16 int/24 fp     | 328 total        | 128 total         | 32/32          | None            | None             |

| Memory B/W      | 2.66 GB/s       | 2.1 GB/s        | 1.54 GB/s     | 1.6 GB/s         | 2.1 GB/s         | 3.2 GB/S          | 539 MB/s       | 1.9 GB/S        | 4.8 GB/s         |

| Die size (mm2)  | 115             | 128             | 477           | 163              | 300              | 217               | 204            | 126             | 210              |

| Transistors     | 15.4mill        | 37.5mill        | 130mill       | 23mill           | 25mill           | 42mill            | 7.2mill        | 3.8mill         | 29mill           |

| Availability    | 3Q01            | 2Q01            | 3Q00          | 4Q00             | 2Q01             | 3Q01              | 3Q01           | 3Q00            | 3Q01             |

**Table 1.1** Main statistics for the key high-end processors available. Figure reproduced from [Mic01].

a set of sequential stages [Kog81] [PH96] [Fly97]. The number of stages depends on each processor [DF90], as can be seen in table 1.1. However, the main steps in the execution of an instruction are: fetch, decode, issue, execute and write results. In some processors these stages can be additionally divided into different stages, depending on the design decisions. In the instruction fetch stage, the instruction cache is accessed in order to read the instruction. The decode and rename stage decodes the instruction, renames logical registers into physical registers and predicts the outcome of the branch in order to be able to make a decision about the execution of the following instructions (wether sequentially continue execution or branch to the destination address). After that, the instruction is issued to the execution queues of the different functional units. Then, the instruction is executed in the appropriate functional unit (or accesses the data cache, if it is a memory access). The instruction finishes its execution writing the result in the register file, if it has to.

• Multiple instruction issue. The pipelined model previously commented can be evolved to deal with more than one instruction in each cycle [SV87]. In that case several instructions are fetched, renamed, issued, executed and finished in each cycle. Instructions executed in parallel can not depend on each other, of course. The early 1990s saw a number of processors, like DEC 21064 [McL93], HP PA

7100 [AAD+93] and MIPS R8000 [Hsu94]. All of them were implementations that achieved multiple issue by executing instructions of different types. In table 1.1 we can see that different current processor designs issue different number of instructions. The majority of them issue four instructions in each cycle, being Itanium [Sha99] the processor that issues the larger number of instructions (up to six instructions in each cycle).

■ Dynamic scheduling and Out-of-order execution. The previous technique allows exploiting much more instruction level parallelism, but it also relies on the ability for finding several independent instructions that can be executed in parallel. This process can be carried out statically, at compilation time, or dynamically, at execution time. In the first case, the compiler selects groups of independent instructions and packs them in a single VLIW instruction [PSW91] [Gas91]. In the later case, instructions are fetched, decoded and issued in original program order, but once issued they can be executed out of program order, based on the availability of their operands. After execution, instructions are graduated in original program order in order to preserve the semantics of the program [DT92]. This technique provides the processor with additional flexibility in order to find independent instructions that can be executed, thus keeping the functional units busier.

All these techniques combined allow the computer to achieve high performance. Table 1.2 presents the best reported SPEC CPU2000 (base) results for each shipping vendor previously commented in table 1.1.

Of course, processors can reach even better performance if programs are compiled by knowing the underlying processor design. For example, the compiler can apply some compilation techniques, like loop unrolling or scalar replacement, in order to expose more parallelism between instructions, thus facilitating exploiting parallelism at execution time.

The two major challenges of an ILP processor are branches and cache memory misses. These two elements disrupt the instruction flow and prevent instructions from flowing through the pipeline. Cache misses are a problem because they stall the pipeline, thus decreasing performance. Several techniques have been developed in order to fight

|                  | Alpha      | AMD         | HP            | IBM       | Intel     | Intel     | MIPS    | Sun          | Sun        |

|------------------|------------|-------------|---------------|-----------|-----------|-----------|---------|--------------|------------|

| Processor        | 21264C     | AthlonMP    | PA-8600       | Power3-II | Itanium   | Pentium4  | R14000  | Ultra-II     | Ultra-III  |

| System or        | Alpha ES40 | AMD         | HP9000        | RS/6000   | Dell      | Dell      | SG12200 | Sun          | Sun        |

| Motherboard      | Model 6    | TyanThunder | <b>J</b> 6000 | 44P-170   | Prec. 730 | Prec. 330 |         | Enterprs 450 | Blade 1000 |

| Clock Rate       | 1001 MHz   | 1.2 GHz     | 552 MHZ       | 450 MHZ   | 800 MHz   | 1.8 GHz   | 500 MHz | 480 MHz      | 900 MHz    |

| External Cache   | 8 MB       | None        | None          | 8 MB      | 2 MB      | None      | 8 MB    | 8 MB         | 8 MB       |

| 164.gzip         | 466        | 608         | 376           | 230       | 332       | 663       | 266     | 165          | 348        |

| 175.vpr          | 482        | 319         | 421           | 285       | 262       | 330       | 460     | 212          | 384        |

| 176.gcc          | 636        | 357         | 577           | 350       | 359       | 649       | 367     | 232          | 491        |

| 181.mcf          | 374        | 229         | 384           | 498       | 187       | 506       | 607     | 356          | 474        |

| 186.crafty       | 803        | 665         | 472           | 304       | 355       | 586       | 409     | 175          | 442        |

| 197.parser       | 405        | 436         | 361           | 171       | 246       | 541       | 342     | 211          | 414        |

| 252.eon          | 798        | 836         | 395           | 280       | 414       | 795       | 433     | 209          | 463        |

| 253 perlbmk      | 605        | 759         | 406           | 215       | 309       | 828       | 305     | 247          | 456        |

| 254.gap          | 309        | 581         | 229           | 256       | 269       | 823       | 242     | 171          | 304        |

| 255.vortex       | 752        | 764         | 764           | 312       | 505       | 832       | 569     | 304          | 575        |

| 256.bzip2        | 606        | 401         | 349           | 258       | 286       | 471       | 404     | 237          | 503        |

| 300.twolf        | 821        | 417         | 479           | 414       | 356       | 444       | 552     | 243          | 481        |

| SPECint_base2000 | 561        | 495         | 417           | 286       | 314       | 599       | 397     | 225          | 439        |

| 168.wupside      | 482        | 669         | 340           | 360       | 591*      | 897       | 321     | 284          | 413        |

| 171.swim         | 898        | 785         | 761           | 279       | 1369*     | 1294      | 310     | 285          | 319        |

| 172.mgrid        | 343        | 464         | 462           | 319       | 749*      | 639       | 249     | 226          | 233        |

| 173.applu        | 411        | 437         | 563           | 327       | 1022*     | 739       | 261     | 150          | 218        |

| 177.mesa         | 785        | 662         | 300           | 330       | 329*      | 671       | 348     | 273          | 466        |

| 178.galgel       | 1577       | 314         | 569           | 429       | 1019*     | 589       | 1154    | 735          | 906        |

| 179.art          | 1987       | 345         | 419           | 969       | 2369*     | 530       | 1213    | 920          | 973        |

| 183.equake       | 179        | 355         | 347           | 560       | 834*      | 816       | 229     | 149          | 210        |

| 187.facerec      | 996        | 417         | 258           | 257       | 637*      | 524       | 475     | 459          | 643        |

| 188.ammp         | 473        | 347         | 376           | 326       | 511*      | 399       | 475     | 313          | 409        |

| 189.lucas        | 511        | 480         | 370           | 284       | 837*      | 866       | 272     | 205          | 206        |

| 191.fma3d        | 415        | 446         | 302           | 340       | 323*      | 445       | 211     | 207          | 297        |

| 200.sixtrack     | 404        | 304         | 286           | 234       | 575*      | 307       | 248     | 159          | 282        |

| 301.apsi         | 506        | 315         | 523           | 349       | 350*      | 474       | 285     | 189          | 328        |

| SPECfp_base2000  | 585        | 433         | 400           | 356       | 703*      | 615       | 362     | 274          | 369        |

Table 1.2 Best reported SPEC CPU2000 (base) results for each shipping vendor. Figure reproduced from [Mic01]. (\*) Dell PowerEdge 7150 with 4MB L3 cache.

against the effect of cache misses [CB92] [SV97] [SC97] [Zha96] [Vei97] [RBS96]. However, there is always a certain number of compulsory cache misses that can not be eliminated.

Regarding branches, the problem are misspredictions. Accurately predicting branch outcomes is an important research topic [McF93] [YMP93] [SJSM96] [Zha96] [JSN98] on which there is a growing interest in the research community. Each time a branch is misspredicted, and the wrong path is being executed, the processor pipeline must be flushed and refilled with the appropriate instructions. In those situations there is a performance loss because of those cycles spent in executing the wrong instructions.

# 1.4 DLP PARADIGM: ANOTHER SOURCE OF PARALLELISM

The data level parallelism (DLP) paradigm uses vectorization techniques to discover data level parallelism in a sequentially specified program and expresses this parallelism using vector instructions [Rus78] [Oed92] [CGMW88] [NKT+95] [WKI86] [AJ88] [DH] [SK86] [Smi91] [CTS96]. A single vector instruction specifies a series of operations to be performed on a stream of data. Each operation performed on each individual element is independent of all others and, therefore, a vector instruction is easily pipelineable and highly parallel [Arn83] [HT72] [Ric78] [GBH96] [NKT+95].

There are two very important advantages in using vector instructions to express datalevel parallelism. First, the total number of instructions that have to be executed to complete a program is reduced because each vector instruction has more semantic content that the corresponding scalar instructions. Second, the fact that the individual operations in a single vector instruction are independent allows a more efficient execution: once a vector instruction is issued to a functional unit, it will use it with useful work for many cycles. During those cycles, the processor can look for other vector instructions to be launched to the same or other functional units. It is very likely that, by the time a vector instruction completes all its work, there is already another vector instruction ready to occupy the functional unit. Meanwhile, in a scalar processor, when an instruction is launched to a functional unit, another instruction is required at the very next cycle to keep the functional unit busy. Unfortunately, many hazards can get in the way of this requirement: true data dependencies, cache misses, branch misspredictions, etc.

The combination of these two effects has many related advantages:

• First, the pressure on the fetch unit is greatly reduced. By specifying many operations with a single instruction, the total number of different instructions that have to be fetched is reduced. Many branches disappear embedded in the semantics of vector instructions [QEV98b].

Chapter 1

• A second advantage is the simplicity of the control unit. With relatively few control effort, a vector architecture can control the execution of many different functional units, since most of them work in parallel in a fully synchronous way.

- A third advantage is related to the way the memory system is accessed: a single vector instruction can exactly specify a long sequence of memory addresses. Consequently, the hardware has considerable advance knowledge regarding memory references and can schedule these accesses in an efficient way [VLL+92] [PVAL95] [CEV98]. Moreover, in the DLP style of accessing memory every single data item requested by the processor is actually needed. There is no implicit prefetching due to cache lines. Additionally, the information on the pattern used to access memory is conveyed to the hardware through the stride information and it can be used to improve memory system performance [VLL+92] [VLPA95] [PVAL95].

- In addition, a vector memory instruction is able to amortize startup latencies over a potentially long stream of vector elements. Since each vector instruction works on a long stream of operations, functional unit latencies and memory latencies can be amortized across all vector elements. In the particular case of memory accesses, once a memory load operation is started, it pays for some initial latency, but then, assuming no memory conflicts, it can deliver one word per machine cycle.

- Finally, the DLP model can be easily scaled up to higher levels of parallelism by replicating the number of functional units and adding wider paths from the vector registers to the functional units. All this without increasing a single bit the complexity or the pressure on the decode unit. The semantic contents of the vector instructions already include the notion of parallel operations. This increase can be as large as the vector length.

All these advantages, which will be largely addressed in section 3.2, lead us to consider that it is worthwhile including DLP in future microprocessor trends. Moreover, including DLP techniques does not prevent from also exploiting ILP by issuing several instructions to execute. Our proposal is focused on the fine architecture level and consists in merging ILP and DLP techniques in a single chip processor. We strongly believe that adding DLP to an ILP processor can guide us to higher levels of paral-

lelism. Although our proposal does not include it, additionally, TLP techniques can also be applied at the coarser level to reach even higher performance levels.

#### Thesis goal

The goal of this thesis is to show that ILP and DLP can be merged in a single architecture to execute regular vectorizable code at a performance level that can not be achieved using either paradigm on its own. We will try to show that the combination of the two techniques yields very high performance at a low cost and a low complexity: the resulting architecture has a relatively simple control unit, tolerates very well memory latency and can be easily partitioned into regular blocks to overcome the wire delay problem of future VLSI implementations. Also, the control simplicity and the implementation regularity both help in achieving very short cycle times. Moreover, we will show that this architecture can be scaled up very easily, while scaling up an ILP processor is very costly in terms of hardware (and, at some point, may even not be feasible). Even if one scales up a superscalar, we will show that their performance falls behind the performance of the machine exploiting both ILP and DLP.

In order to reach high performance it is a key point of this thesis to also propose a novel cache hierarchy, tuned for the exploitation of the ILP and DLP paradigms. Each source of parallelism exposes a different way of accessing memory data. Therefore, the exploitation of each source of parallelism requires an especially designed memory hierarchy. In our case, we propose a memory hierarchy tuned to accessing scalar and vector data. This memory hierarchy is based on the "vector cache", which is a cache aimed at accessing vector and scalar data. This cache will be able to provide high bandwidth to the vector register file, to allow this bandwidth to scale up as we scale the functional units, to minimize conflicts between vector and scalar data and to guarantee that the processor cycle time is not in jeopardy due to the inclusion of a high bandwidth port to the vector register file.

|            |      | Clock Freq. |            |          | Main Memory | Load        |

|------------|------|-------------|------------|----------|-------------|-------------|

| Machine    | Year | (MHz)       | Mflops/CPU | No. CPUs | Bw/CPU      | latency(ns) |

| Cray-1     | 1976 | 80          | 160        | 1        | 640 MB/s    | 150         |

| Cray-XMP   | 1982 | 105         | 210        | 2        | 2.5 GB/s    | 123         |

| Cray-2     | 1982 | 243         | 486        | 4/8      | 1.9 GB/s    | 200         |

| Cray-YMP   | 1989 | 167         | 334        | 8        | 4 GB/s      | 100         |

| Cray-C90   | 1992 | 243         | 970        | 16       | 12 GB/s     | 95          |

| Cray-J90   | 1995 | 100         | 200        | 32       | 1.6 GB/s    | 340         |

| Cray-T90   | 1994 | 450         | 1800       | 32       | 21 GB/s     | 70/116      |

| Cray-SV1ex | 2001 | 500         | 2000       | 32       | 6.4 GB/s    | NA          |

Table 1.3 Evolution of the Cray vector machines.

#### 1.4.1 DLP: Past, Present and Future

Given all the advantages mentioned above, one could ask what was the fault in the previous implementations of the DLP paradigm, that made them be slowly outshaded by other forms of computing.

#### Past of DLP

The DLP paradigm has been exploited using vector instruction sets [Rus78] [IW91] [Oed92]. The first vector machines were supercomputers using memory-to-memory operation [HT72] [Wat72], but vector machines only became commercially successful with the addition of vector registers in the Cray-1 [Rus78]. Following the Cray-1, a number of vector machines have been designed and sold, from supercomputers with very high vector bandwidths [Oed92] [KIS+94] to more modest mini-supercomputers [Con92] [PM86].

The peak performance of vector supercomputers has been constantly improving from the original 160 Mflops per processor of the Cray-1 up to 10 Gflops per processor of the more recent NEC SX-5 [vdSD01c]. This improvement has been achieved both through better cycle times (from 12.5 ns in the Cray-1 down to 3.2 ns in the SX-5) and higher number of floating point operations initiated per cycle. As an example of these improvements, table 1.3 shows the evolution of the Cray vector processors from the initial Cray-1 until the current Cray SV1.

⊚ Universidad de Las Palmas de Gran Canaria. Biblioteca Digital, 2004

Some years ago, parallel vector processors (PVP) were slowly displaced from the marketplace by other forms of supercomputing. There were several reasons:

- First, vector computers are not as general purpose as scalar processors. Vector processors achieve their highest performance values during the execution of vector-izable programs. For non vectorizable programs their performance results are very low since they can not take advantage of the latency tolerant vector code. Therefore, the flat memory system, without caches or with a small scalar cache, becomes a bottleneck when almost every data is accessed in scalar mode. Meanwhile, scalar processors obtain higher performance values for these non vectorizable programs, since their memory hierarchy is aimed at accessing scalar data.

- Second, because of the high cost of traditional vector processors. In order to keep the powerful cpu fed with enough data two related problems had to be solved. It was necessary to provide enough bandwidth from the memory system to the processor to ensure that the maximum processing rate is achieved. Moreover, this bandwidth had to be provided without increasing too much the latency delays that each memory request had to pay. Vector processors relied on high-performance, highly-interleaved memory systems that could sustain a bandwidth rate in accordance with their computing capabilities. Through the use of many parallel banks of interleaved memory (between 256 and 1024 banks depending on processor and configuration [SWL+91]) the necessary bandwidth was usually achieved. To keep the latency reasonably low, the fastest memory technology must be used. Vector processors tended to have SRAM/SSRAM memory modules [Pri96], which had a very high cost and, usually, turned out to be a very large fraction of the overall system cost. In comparison, their market adversaries leveraged commodity technology, which yielded a very low cost and delivered a very good price/performance ratios.

- Fourth, vector computers could not follow the impressive evolution of scalar processors in those years. Scalar processors using CMOS technology evolved very rapidly and their speed increased at a rate of 60% per year [PAY96]. Those scalar processors included a variety of architecture techniques, such as decoupling [Smi82], out-of-order execution [Tom67] [Yag96] and hierarchical memory systems based on

16 Chapter 1

caches [KELS62] [Wil65] [Hil87] [Hil88] [Smi82] [SG83] [PH96] [LR91], that had greatly improved their processing power. This led to a situation where, for certain classes of cache-friendly problems, a microprocessor could match and sometimes exceed the performance of a vector supercomputer at a small fraction of its cost. While it was true that not all problems were well suited for cache-based machines, it is clear that those types of systems took a substantial share of applications that had previously belonged to the vector computing realm. As a result, vector processors were relegated to those classes of problems where the data size was too big to fit in a cache-based memory system.

- Fifth, the slow decline of vector processors can also be attributed to the fact that their architecture did not change much since the introduction of the Cray-1 [Rus78]. While superscalar microprocessors adopted many architectural features to increase performance while still retaining low cost, vector machines used almost the same architectural concepts introduced in 1976. In order to remain viable, and to extend to low cost systems, vector designs needed somehow evolve.

- Finally, despite the theoretical processing rates of vector cpus and the high bandwidth memory systems built around them, a constant in the evolution of vector supercomputers has been that the achieved performance of real programs has always been far from the theoretical peak performance [SH91] [Don93] [SH94] [Del91] [PB88]. What is worse is that this discrepancy between peak and actual performance occurred even for programs that were highly vectorized. As a result, the theoretical advantage of the vector computing paradigm over other forms of supercomputing was lost.

These most notable forms of computing that outshaded vector processors were large (MPP) and medium (SMP) scale multiprocessors built out of commodity microprocessors. The success of these other technologies were mostly based on leveraging CMOS microprocessor technology and DRAM main memory systems, yielding systems that had a high performance at a low cost. Meanwhile, PVP used expensive ECL technology, as in those days gate-switching speed was the limit on performance. This led to a shrinkage of the traditional PVP market niche. As a result, many companies devoted to manufacturing vector computers, like IBM, HP/Convex, Meiko, Alliant, Thinking

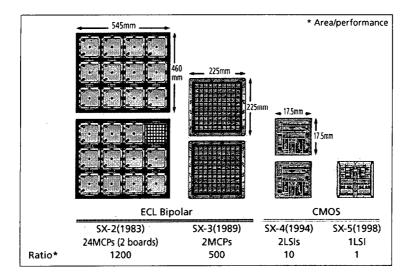

**Figure 1.1** Vector processor migration from ECL to CMOS technology. Figure reproduced from [Lan98].

Machine and others, left the vector supercomputing business, and nowadays only two companies keep on manufacturing vector supercomputers: NEC and Cray.

#### Present of DLP

Over the last ten years these vector supercomputer manufacturers have made an important effort in adapting vector processors to the new technologies. All of them have moved from the costly ECL technology to CMOS technology, which lowers the fabrication costs and the power consumption appreciably. In the NEC case, the area/performance ratio has been reduced from 1200 down to 1 because of this evolution [Lan98], as can be observed in figure 1.1.

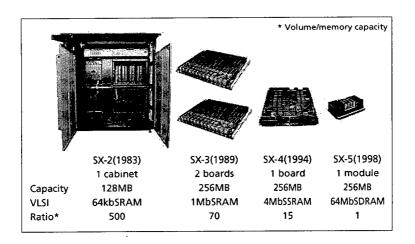

In the memory field, they have also migrated from expensive SRAM to commodity SDRAM chips, which provide a higher memory density, lower cost and higher performance. Figure 1.2 shows that in fifteen years the volume/memory capacity ratio has decreased from 500 down to 1, for NEC vector computers [Lan98].

Figure 1.2 Vector processor migration from SRAM to SDRAM technology. Figure reproduced from [Lan98].

Nowadays, parallel vector machine vendors offer supercomputing to the user at a much lower cost and with a higher performance. NEC is currently selling the SX-5 [IKFN98] series. It was first introduced in 1998 and it is characterized by NEC as a machine that works well for vectors that are not very long and for programs that also contain a non-negligible amount of scalar code. This can be attributed to the lower multiplicity of the vector pipes in the vector units. Each NEC SX-5 processor works at 313 MHZ, that is 3.2 ns cycle time, and it can achieve a theoretical peak performance of 10 Gflops [vdSD01c].

Fujitsu has introduced in 1999 the VPP5000 series [Fuj01], which is the distributed-memory vector multiprocessor that succeed the former VPP700 systems [Uch97]. The main enhancements have been the reduction in cycle time, down to 3.3 ns, and the floating-point vector pipes are able to deliver floating multiply-add results. Each vector processor is able to reach a peak performance of 9.6 Gflops. Although the system was announced in November 1999, the first performance results have only recently been available [vdSD01b].

Finally, Cray has recently introduced the new SV1[BS00], a shared-memory multivector processor. The Cray SV1 is built using CMOS technology and it is the successor of both, the CMOS-based Cray J90 and the Cray T90, which was based on ECL

technology. Although the initial cycle time was higher, they have announced a 2 ns cycle time by the middle of 2001 [BS00], and each processor will reach a peak performance of 2 Gflops. The very new characteristic of the SV1 vector processor is the addition of a 256 Kbyte cache, as we already proposed at [QCEV99]. In the same way as we did, the cache is combined with the cpu onto one ASIC. Their initial step, however, is simpler than our proposal. Although no independent measured performance is available at the moment, some tests have shown the importance of the cache in SV1 [vdSD01a]. For large sized vectorizable problems the presence of the cache has almost no effect. However, for modestly sized problems the cache can boost the performance with a factor of 1.5 up to 2. The reason is probably that with large sized problems the program's working set does not fit in cache, so program execution does not benefit from exploiting temporal locality. Therefore, many memory accesses miss in cache and data must be brought from the main memory at a 6.4 GB/s bandwidth. On the contrary, for modestly sized problems the program's working set fits in the cache and data can be reused, thus benefiting from the 14.4 GB/s processor-cache bandwidth.

Besides, the DLP paradigm has been also recently introduced in commodity microprocessors. During the last years, PC and workstation users unknowingly have been using a restricted form of DLP, since the commodity chip makers have began incorporating SIMD hardware into their mainstream superscalar processors. However, it is important to distinguish our proposal from this tendency in microprocessor design targeted at the exploitation of sub-word parallelism. Most major computer vendors have recently included multimedia specific instructions in their architectures such as MMX [PW96], VIS [TONH96], MAX [Lee96], MDMX [MIP97] or Altivec [NJ99]. Except for the Altivec case, all other extensions only offer sub-word parallelism. That is, a 64-bit register can be broken into independent entities of 8, 16 or 32 bits that are operated on in parallel. Although the term "SIMD" is used to refer to these instructions, they are a restricted form of vector computing, and care must be taken to distinguish traditional vector-like SIMD operation and sub-word SIMD operation.

In this thesis we do not focus on sub-word level parallelism. Rather, we integrate a full vector unit in an out-of-order superscalar processor. Our proposal has true vector instructions where a single instruction operates on multiple, independent 64-bit words

CHAPTER 1

(a vector register). The advantage of having full-blown vector units is that numerical applications can benefit greatly from them while, typically, they do not take advantage of MMX-like ISAs. Furthermore, some multimedia applications that are not amenable to exploit sub-word parallelism can also take advantage of our vector units. Of course, although beyond the scope of this thesis, nothing would prevent our vector units to also include sub-word parallel instructions, such as the ones provided by Altivec.

#### **Future of DLP**

Future trends in computing are very difficult to predict. What is clear, however, is that those trends will include exploiting DLP. At the supercomputing high-end, NEC and Cray will still keep on manufacturing vector processors. In fact, NEC has recently announced that there will be at least three more generations of the SX processor, called SX-6, SX-7 and SX-8 [NEC01], which give us an idea about future expectations about vector supercomputing for this company. Meanwhile, the Cray SV2 system, currently in development, will be the next supercomputer from Cray [Inc01].

At a lower-end, it is expected that the interest on SIMD extensions for superscalar processors will increase, in order to meet the increasing users demand on media processing [Wil98], such as video and audio processing, image rendering, and other media applications [DD97] [LW97] [BE98]. Also at that end, as technology continues to evolve, miniaturization will make the space needed for a single processor much smaller than the actual chip size [Lan00]. As a processor is 0.1 square cm in size, and the chip is 6.2 square cm, there is room for multiple processors [Kah99]. However, that is not the only way. The alternative, which is proposed in this thesis, is to complement the superscalar processor with vector processing and large, especially designed cache memory hierarchies.

#### 1.5 RELATED WORK

Over the last few years, there has been an increasing interest on studies regarding DLP. These studies deal with the different ways of exploiting DLP: vector processors and sub-word level parallelism.

In the work presented in [LD97] and [LS98], it is proposed the use of simple vector processors in future desktop systems. Although this may sound similar to our proposal, indeed the differences are profound. Lee argues that by using vector units, one can keep the scalar core in-order (dispensing with the expensive and slow out-of-order features) and thus favor high clock rates. Although we agree with the argument, we claim that any feature that goes against integer performance will not be adopted by chip vendors. That is, to successfully add a vector unit to general purpose microprocessors, the vector unit has to be perceived as an add-on that does not disrupt, slowdown or interfere with the performance of the integer core. Therefore, if the current tendency is to include out-of-order execution even in high frequency designs such as the Alpha lineage, the vector unit must be adapted to out-of-order execution and register renaming.

Furthermore, Lee does not discuss the implications of the vector unit on the memory system, while this thesis is mainly devoted to designing a feasible cache hierarchy that fits both the scalar engine and the vector unit.

In [EVS97] [Esp97] Espasa makes the case for an out-of-order vector processor. The study starts from an obsolete in-order vector architecture [Con92]. Although this processor issued only one instruction in each cycle there was overlapping between scalar and vector instructions. However, a stall in a vector instruction prevented further vector instruction dispatching until the hazard was resolved. It was a register-to-register machine with few vector registers, and connected to the functional units through a crossbar. The main memory system was a flat multi-banked one, connected to the processor through a single memory port. The study is focused on applying register renaming and out-of-order execution to this vector processor, while keeping its 1-way nature, in order to improve performance. In [EVS98] they identify two possible evolutions of vector architectures. One of them, that they studied in [EV97], is the proposal

Chapter 1

of a simultaneous multithreaded vector processor able to be implemented with one billion transistors. This proposal is aimed at high end vector supercomputers. The other possible evolution, situated at the mid-range servers, is what they called the "Micro Vector", which uses out-of-order execution, short vector registers and specialized caches.

Our proposal, which is more concerned with the "Micro Vector" that they define, does not deal with vector processors at all, we start from a full superscalar architecture and we study what is the minimum additional components that must be included in order to introduce vector computing inside. We also propose a new cache hierarchy, based on a traditional one, aimed at accessing vector and scalar data.

Villa [VEV97] [VEV98] studies the importance of the vector registers length in vector processors. For different vector lengths, it analyzes performance and cost. Our study will include results for 16-element and 128-element vector registers, as we consider this exploration essential in determining the minimum vector elements required to achieve a performance improvement. The fact that the memory system that Villa uses is flat and multi-banked, while our proposal is a cache hierarchy, make their behavior different. Therefore, its conclusions can not be directly applied in our field.

In the sub-word level DLP exploitation research field there have been different approaches. Although these studies deal with DLP exploitation, they only exploit sub-word level parallelism while we focus on word level parallelism exploitation. Moreover, they only study multimedia applications, while we are also interested in numerical applications. Finally, some of these studies are restricted to embedded processors, while ours are aimed at general purpose processors. As discussed above, our work could be additionally improved with the inclusion of sub-word level instructions. Therefore, these works complements, rather than overlaps, ours.

Among these studies, [CEV99] proposes the Matrix Oriented Multimedia (MOM) ISA extension by fusing conventional vector ISA approaches together with media ISA extensions like MMX [PW96]. MOM instructions can be viewed as vector versions of sub-word parallel instructions, that is, they operate on matrices where each row corresponds to a packed data type. MOM is targeted at small matrix structures typically

found in multimedia applications. This proposal has been additionally extended in [CEV01]. In this work the MOM ISA extension is combined with packed accumulators (as found in MDMX [MIP97]) in order to deal with reduction operations. These extensions outperform MDMX and MMX extensions.

In [SCEV99] an evaluation of different DLP oriented embedded architectures for a media workload is presented. This study includes SIMD ISA extensions, a traditional vector ISA (with long and short vector registers) and MOM ISA extension. For the embedded domain, the SIMD-like architecture arises as the more cost-effective option.

In [JTVW01] the Complex Streamed Instruction (CSI) set is presented. It is an ISA extension with some different characteristics to previous ones: CSI instructions process two-dimensional data streams (as MOM does), there is no architectural constraint on the length of the data streams, and it does not include pack/unpack instructions as conversions between different packed data are performed internally in hardware.

Another related proposal is the Imagine media processor [Wil98] [RDK<sup>+</sup>98] which has a load/store architecture for one-dimensional streams of data records. Imagine is organized around a large 128 KB stream register file, and consists of 48 functional units grouped in 8 arithmetic clusters. All operations are performed by transferring streams to and from the stream register file. Memory instructions transfer streams between the stream register file and memory. Stream computations are performed by passing a stream from the stream register file through the arithmetic units and back to the stream register file. In this processor the individual stream elements may be operated on in parallel to exploit data level parallelism. Instruction level parallelism can be exploited within the individual computation kernels. Imagine is suited for applications performing many arithmetic operations on each element of a long, one-dimensional stream. It seems less suited when only a few operations on each record are performed or when the vector length is small.

Another research topic that we deal with in this thesis, is the use of specialized cache hierarchies for ILP+DLP processors. In this sense, it is interesting to comment the cache-based memory system recently appeared in the Cray SV1 [BS00]. As we already

CHAPTER 1

proposed in [QCEV99], this processor has a 256 Kbyte cache that is combined with the cpu onto one ASIC. Their proposal, however, is simpler than ours in several aspects:

- First, their cache is unified for instructions and scalar and vector data. Our proposal, however, follows the traditional cache designs of separated instruction and data caches [QCEV99] [QCEV01].

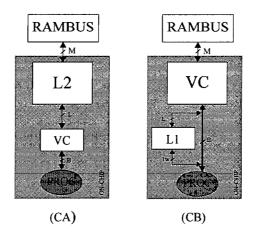

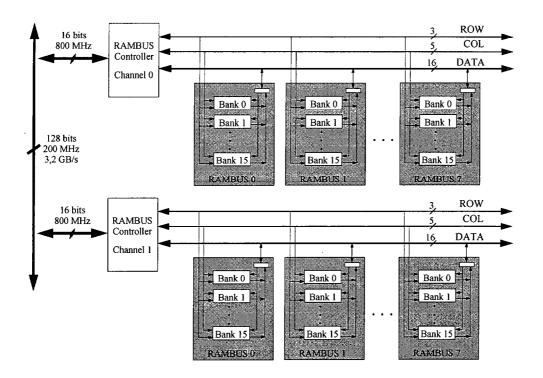

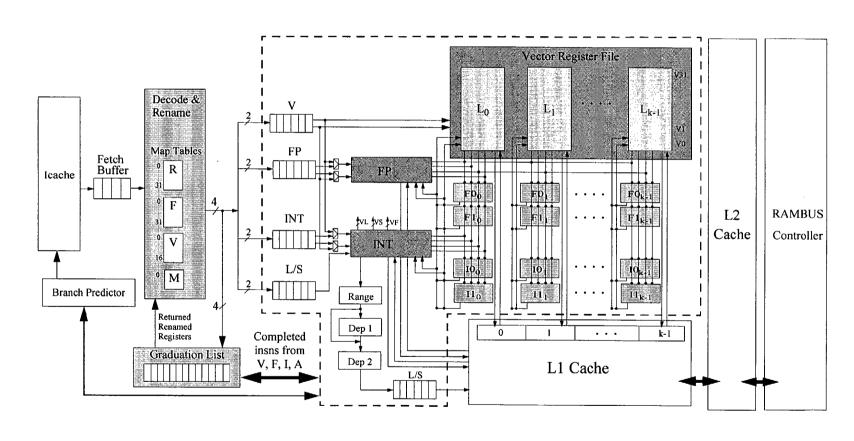

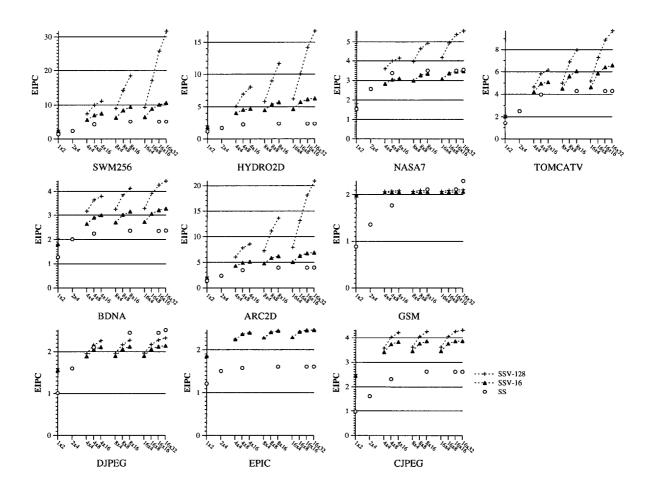

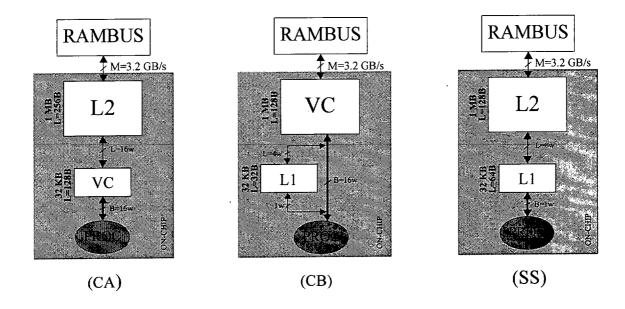

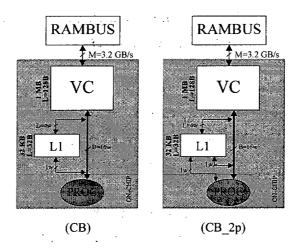

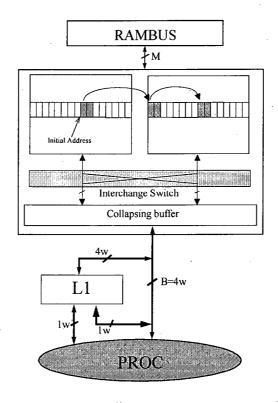

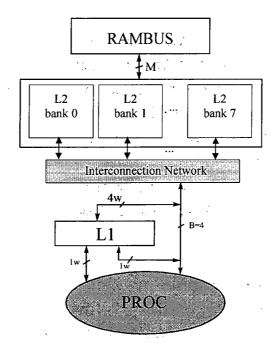

- Second, they propose a unique first level cache. Meanwhile, we propose a two-level cache hierarchy system [QCEV99] [QCEV01], as we will explain in detail in chapter 4. We will study two cache hierarchy models. In the first one both, scalar and vector data, are located in both cache levels and they behave similarly to a traditional cache hierarchy. In the second model the first level cache only contains scalar data. Vector data is located in the second cache level and a direct path from the processor to that cache allows accessing them [Hsu94] [Sha99]. Our proposal goes further away exploring the separation of vector and scalar workload.

- Third, the cache line size in the SV1 cache is just one word. This is by no mean common in a cache, which has traditionally been used to exploit both, temporal and spatial locality. This cache line size prevents from exploiting spatial locality, which is fully present in the instruction flow and in stride-1 vector accesses. The only reason to set such small cache lines is to avoid moving useless data when non stride-1 or gather/scatter vector memory accesses are executed. When multiple-word line sizes are used, these types of accesses spend some memory bandwidth as some data are moved to the cache, but they are not actually used later. However, there are two approximations in order to solve this problem: the first one, adopted in SV1, is to sidestep the problem by using 1-word cache lines, thus losing the opportunity of improving performance by exploiting spatial locality. The second one, which we propose [QCEV99] [QCEV01], consists in facing the problem and designing a memory hierarchy that deals well with strided memory accesses, as we will see in chapter 6.

- Closely related to the previous consideration is the fact that the SV1 cache delivers four data elements to the processor in each cycle [vdSD01a]. As the cache line size is just one word large, four independent memory accesses have to be done to four different cache lines. Therefore, four independent memory ports are needed,

⊚ Universidad de Las Palmas de Gran Canaria. Biblioteca Digital, 2004

which is an expensive solution. In our proposal, however, the multiple-word line size allows having just one four-word width memory port [QCEV99] [QCEV01]. A vector memory access goes to one cache line and brings the four consecutive elements, which is a lower cost solution.

# 1.6 A SUITABLE APPLICATION SPACE FOR EXPLOITING DLP

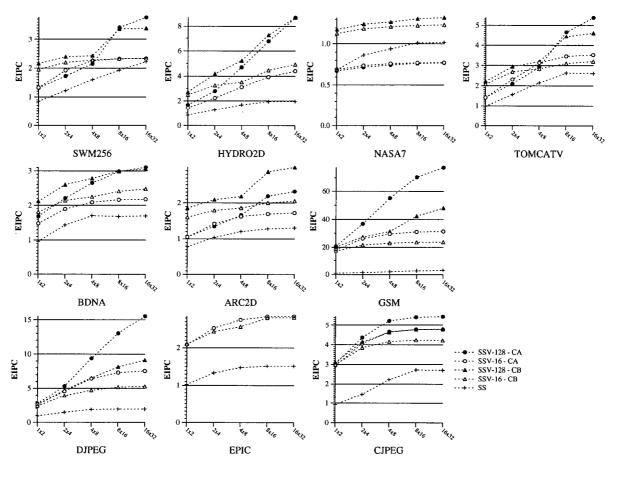

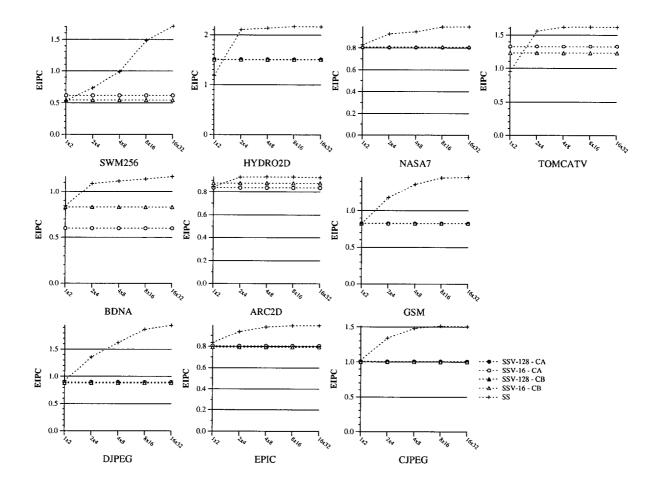

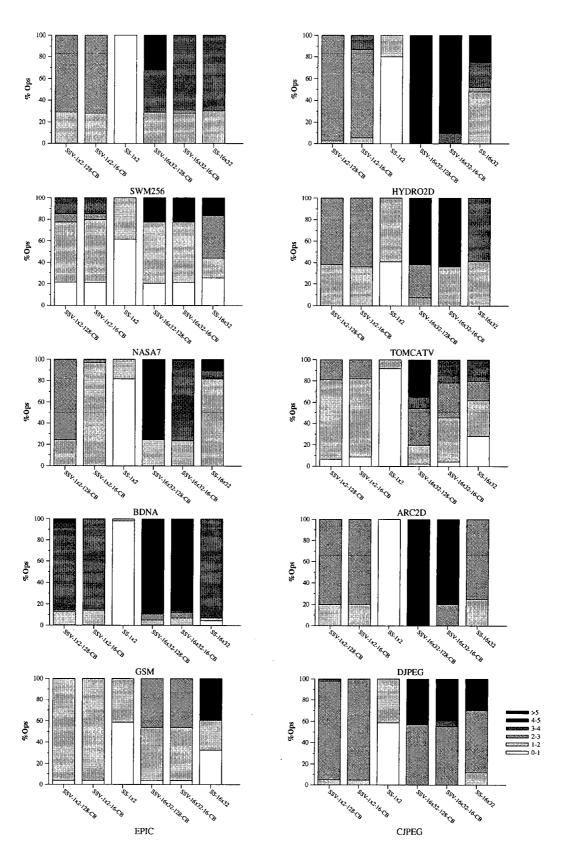

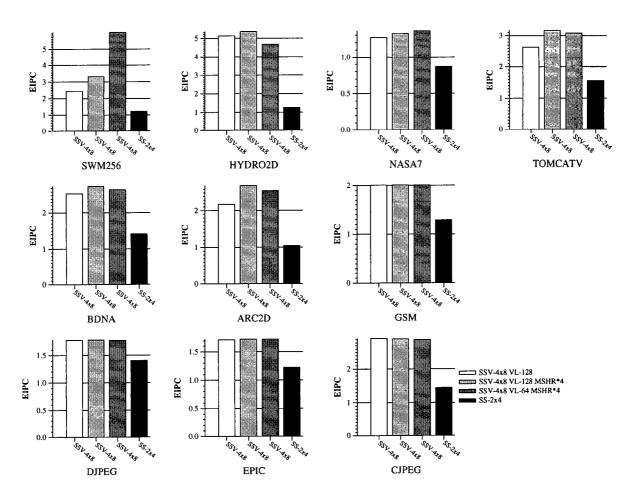

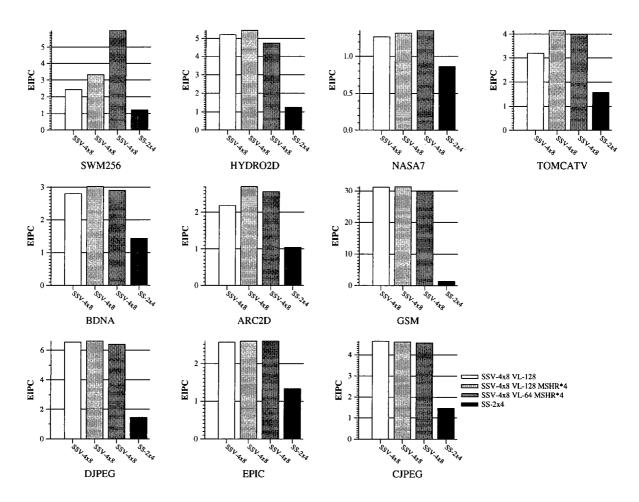

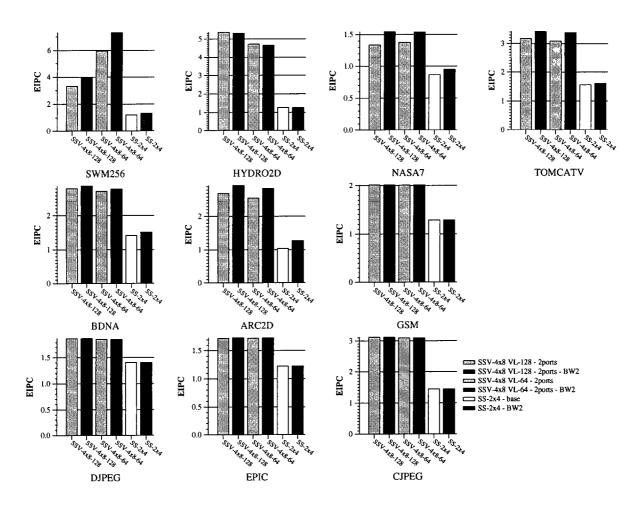

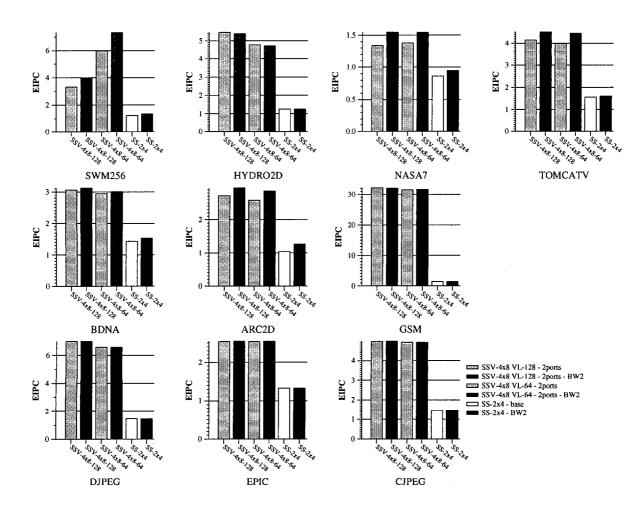

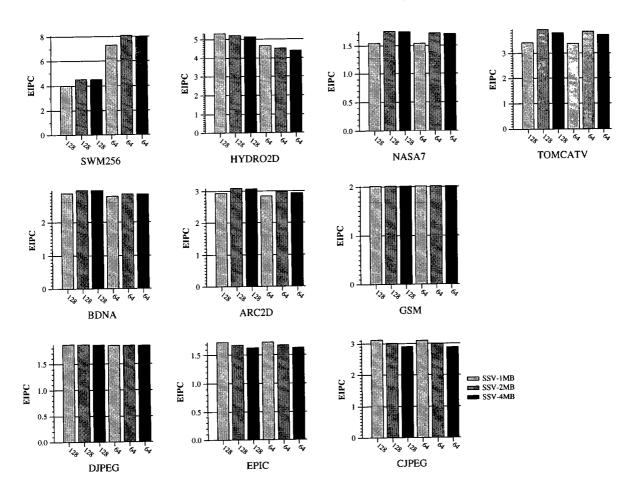

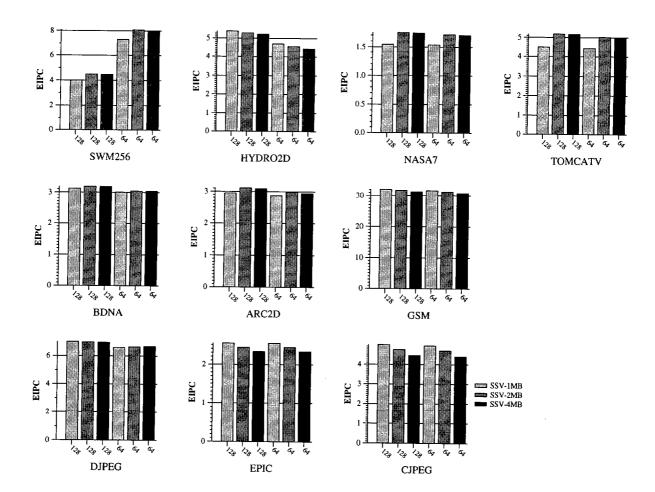

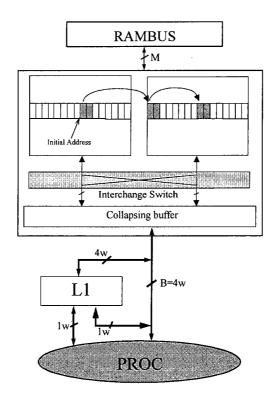

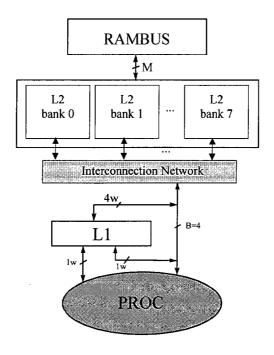

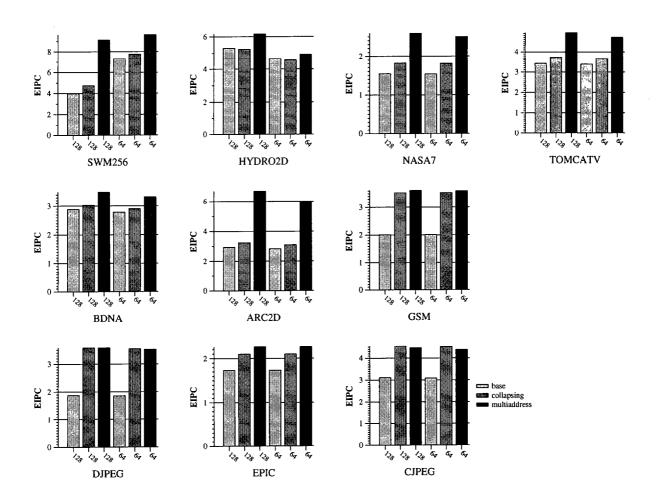

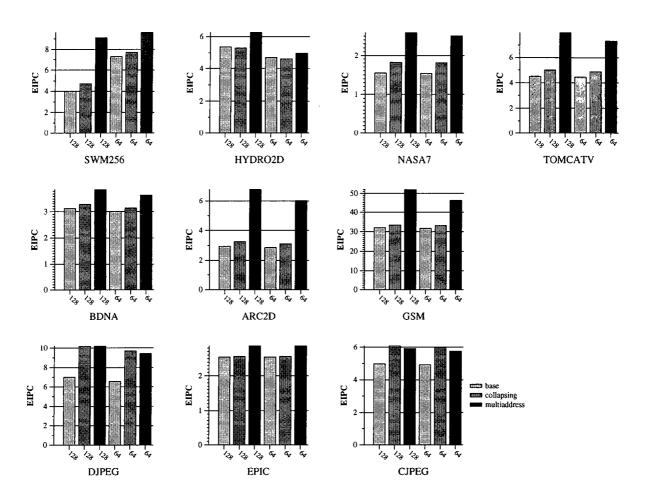

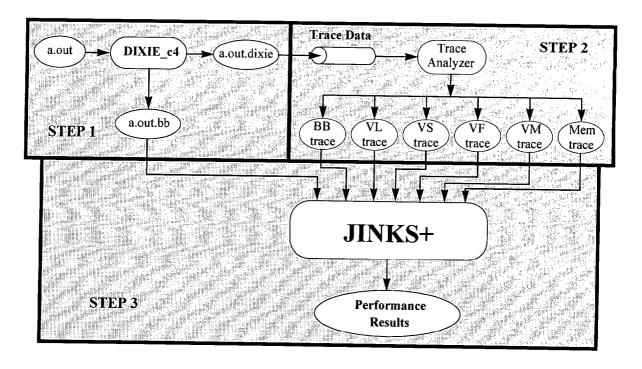

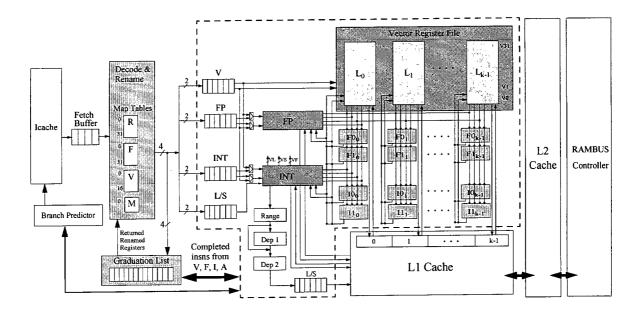

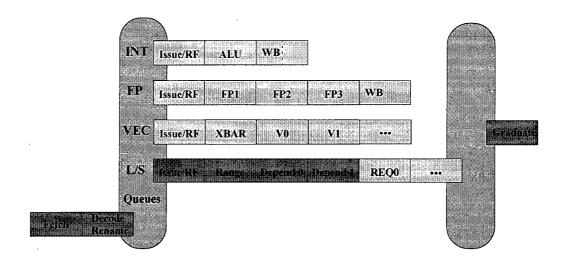

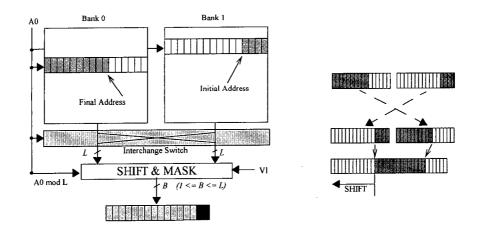

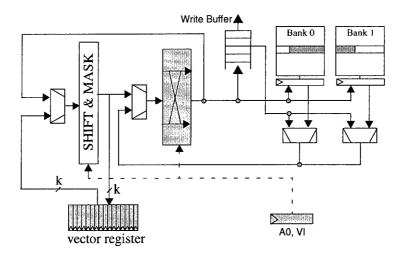

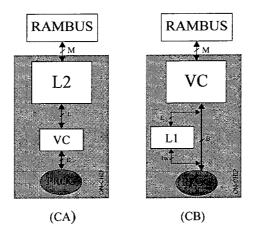

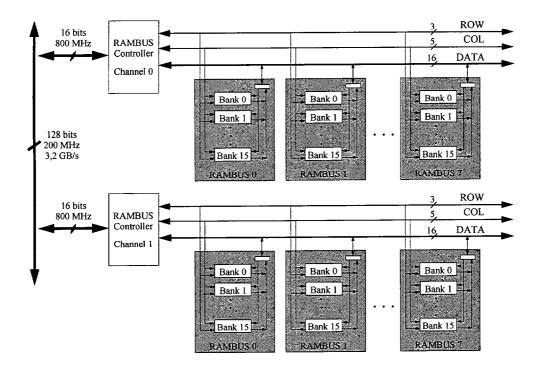

As stated in section 1.4, page 11, the DLP paradigm is expressed by means of vector instructions. However, not all tasks can be expressed by using vector instructions, and even inside a vectorizable program some parts will not be amenable to be formulated in a vector form. Therefore, from the DLP point of view, we can say that a program has two types of regions, data-parallel regions (D-regions) containing those zones that can be expressed with vector instructions, and scalar regions (S-regions), whose contents can not be formulated with vector instructions.