# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA UNIVERSITARIA DE INGENIERÍA TÉCNICA DE TELECOMUNICACIÓN

# PROYECTO FIN DE CARRERA

# DISEÑO DE UN AMPLIFICADOR CMOS INTEGRADO PARA SER UTILIZADO COMO DRIVER PARA CARGAS CAPACITIVAS ELEVADAS

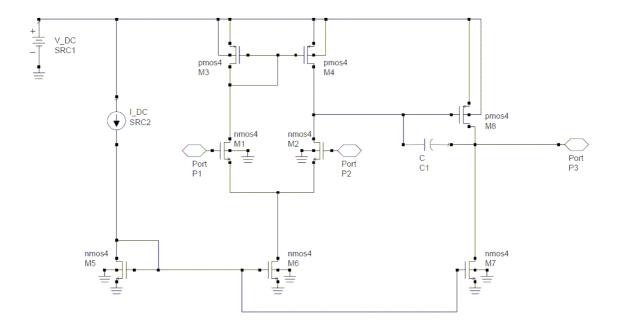

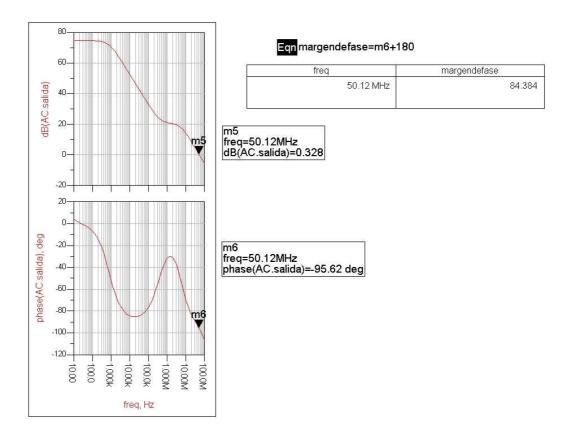

Titulación: Sistemas Electrónicos.

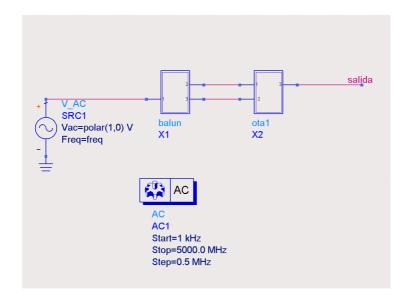

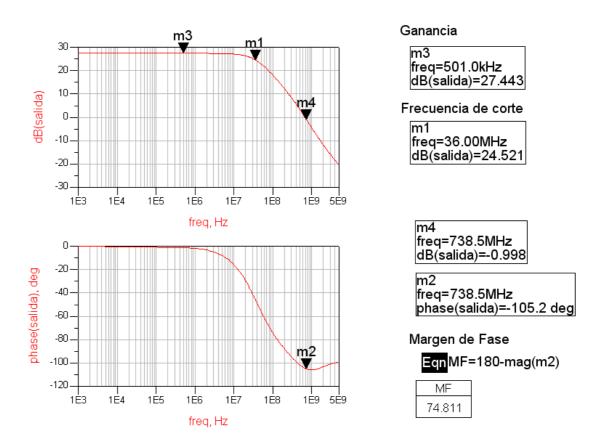

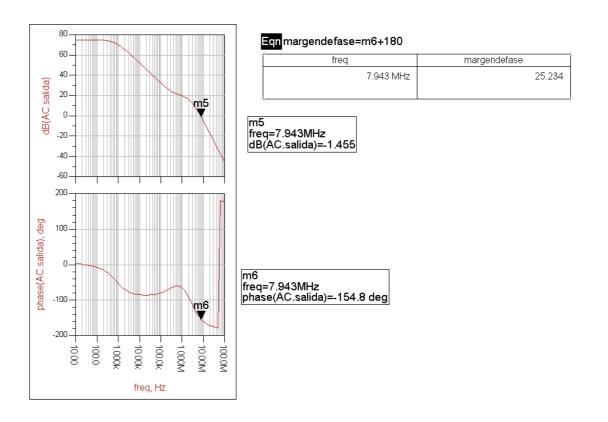

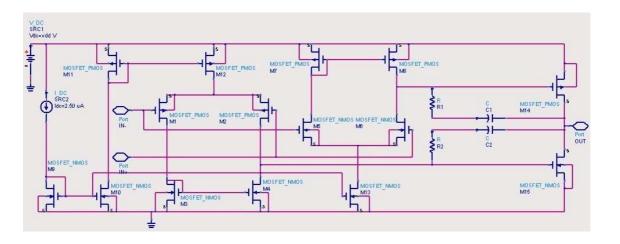

Autor: Enara Ortega García.

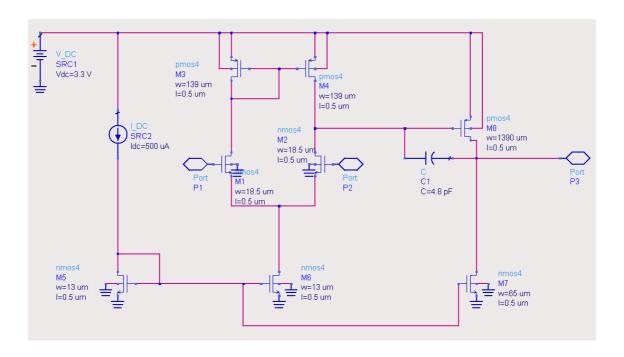

Tutores: Fco. Javier del Pino Suárez.

Sunil Lalchand Khemchandani.

Fecha: Septiembre 2009.

# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA UNIVERSITARIA DE INGENIERÍA TÉCNICA DE TELECOMUNICACIÓN

# PROYECTO FIN DE CARRERA

# DISEÑO DE UN AMPLIFICADOR CMOS INTEGRADO PARA SER UTILIZADO COMO DRIVER PARA CARGAS CAPACITIVAS ELEVADAS

| Presidente: | Secretario: | Vocal: |

|-------------|-------------|--------|

| Tutores:    |             | Autor: |

| N           | OTA:        |        |

Titulación: Sistemas Electrónicos.

Autor: Enara Ortega García.

Tutores: Fco. Javier del Pino Suárez.

Sunil Lalchand Khemchandani.

Fecha: Septiembre 2009.

# Índice

| 1. | . Introducción |                   |                                                            |  |  |

|----|----------------|-------------------|------------------------------------------------------------|--|--|

|    | 1.1            | Introdu           | cción                                                      |  |  |

|    | 1.2            | Objetiv           | os                                                         |  |  |

|    | 1.3            |                   | ura de la memoria                                          |  |  |

|    |                |                   |                                                            |  |  |

| 2. | El tra         | El transistor MOS |                                                            |  |  |

|    | 2.1            | Introdu           | cción                                                      |  |  |

|    | 2.2            | Funcion           | namiento                                                   |  |  |

|    | 2.3            | Curva c           | característica de los transistores                         |  |  |

|    |                |                   | Transistor tipo N                                          |  |  |

|    |                |                   | Transistor tipo P                                          |  |  |

|    | 2.4            |                   | es de operación de los transistores                        |  |  |

|    |                | 2.4.1 I           | Región de corte                                            |  |  |

|    |                | 2.3.2 I           | Región lineal                                              |  |  |

|    | 2 =            | 2.3.3             | Region de saturacion                                       |  |  |

|    | 2.5            | Calculo           | de la K y la Vt de los transistores                        |  |  |

|    | 2.6<br>2.7     | Desvia            | ciones del modelo                                          |  |  |

|    | 2.7            | Modelo            | en Pequeña Señal                                           |  |  |

|    | 2.8<br>2.9     | Conclu            | en Alta Frecuenciasiones                                   |  |  |

|    |                |                   |                                                            |  |  |

| 3. | Introd         | lucción           | a los Amplificadores Operacionales                         |  |  |

|    | 3.1            |                   | ucción                                                     |  |  |

|    | 3.2            |                   | etros de un Op-Amp                                         |  |  |

|    |                |                   | Tensión de Offset                                          |  |  |

|    |                |                   | Corriente de entrada                                       |  |  |

|    |                |                   | Tensión de entrada en modo común                           |  |  |

|    |                |                   | Excursión de salida máxima                                 |  |  |

|    |                |                   | Impedancia de salida                                       |  |  |

|    |                |                   | Rechazo en modo común                                      |  |  |

|    |                |                   | Rechazo en modo comun  Rechazo a la fuente de alimentación |  |  |

|    |                |                   |                                                            |  |  |

|    |                | 3.2.8             | Slew Rate                                                  |  |  |

|    |                |                   | Ancho de banda para ganancia unidad y margen de fase       |  |  |

|    |                |                   | Гіеmpo de establecimiento                                  |  |  |

|    | 3.3            | Conclu            | siones                                                     |  |  |

|      | o ae i            | Op-Amps                                             |  |

|------|-------------------|-----------------------------------------------------|--|

| 4.1  | Intro             | ducción                                             |  |

| 4.2  | Etapa             | a de entrada                                        |  |

|      | 4.2.1             | Circuitos equivalentes en pequeña señal             |  |

| 4.3  | Fuen              | Fuentes de corriente                                |  |

|      | 4.3.1             | Características ideales de un espejo de corriente   |  |

|      | 4.3.2             | Análisis de un espejo de corriente básico           |  |

|      | 4.3.3             | Espejos de corriente analizados                     |  |

|      |                   | 4.3.3.1 Espejo de corriente básico                  |  |

|      |                   | 4.3.3.2 Espejo de corriente cascada/cascodo         |  |

|      |                   | 4.3.3.3 Espejo de corriente Wilson                  |  |

|      |                   | 4.3.3.4 Espejo de corriente Wilson modificado       |  |

|      |                   | 4.3.3.5 Espejo de corriente cascodo reducido        |  |

|      | 4.3.4             | Fuentes de corriente como cargas activas            |  |

| 4.4  | Etapa             | as de salida                                        |  |

|      | 4.4.1             | Clasificación de las etapas de salida               |  |

|      |                   | 4.4.1.1 Etapa de salida clase A                     |  |

|      |                   | 4.4.1.2 Etapa de salida clase B                     |  |

|      |                   | 4.4.1.3 Etapa de salida clase AB                    |  |

| 4.5  | Resp              | uesta en frecuencia                                 |  |

| 4.6  | Reali             | mentación y compensación                            |  |

|      | 4.6.1             | Realimentación negativa                             |  |

|      | 4.6.2             | Estabilidad de amplificadores realimentados         |  |

|      | 4.6.3             | Tipos de compensación                               |  |

|      | 4.6.4             | Implementación                                      |  |

|      |                   | 4.6.4.1 Compensación por polo dominante o Miller    |  |

|      |                   | 4.6.4.2 Compensación por polo-cero                  |  |

| 4.7  | Cálcu             | alo del producto ganancia por ancho de banda (GBW)_ |  |

| 4.8  | Relac             | ción importante para el diseño                      |  |

| 4.9  | Ejemplo de diseño |                                                     |  |

|      | 4.9.1             | Diseño de un OTA                                    |  |

|      | 4.9.2             | Diseño de un Op-Amp de dos etapas                   |  |

| 4.10 | Conc              | lusiones                                            |  |

|              | 6.1                 | <ul><li>6.1 Introducción</li></ul>            |  |  |

|--------------|---------------------|-----------------------------------------------|--|--|

|              | 6.2                 |                                               |  |  |

|              | 6.3                 |                                               |  |  |

|              |                     | 6.3.1 Layout de pistas                        |  |  |

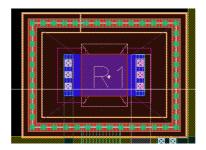

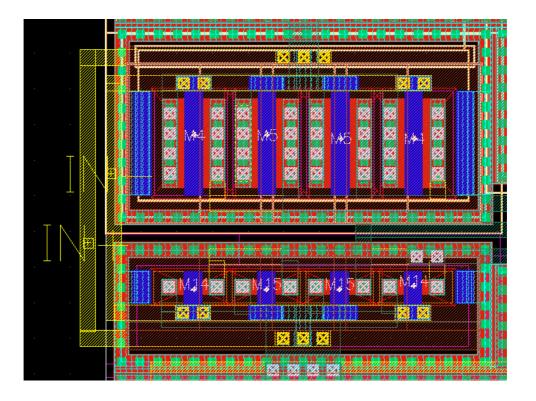

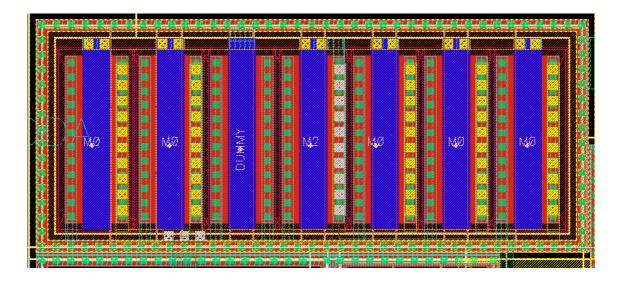

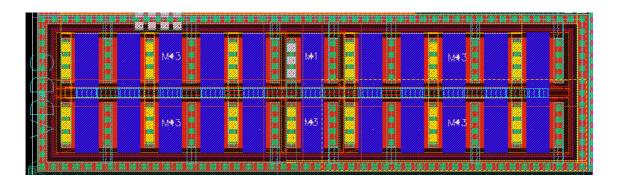

|              |                     | 6.3.2 Layout de transistores MOS              |  |  |

|              |                     | 6.3.3 Layout de resistencias                  |  |  |

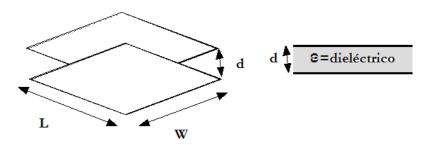

|              |                     | 6.3.4 Layout de capacidades                   |  |  |

|              |                     | 6.3.5 Técnicas de diseño                      |  |  |

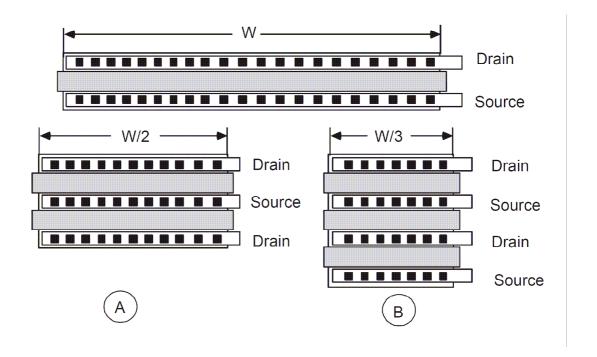

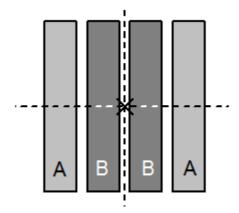

|              |                     | 6.3.5.1 División de los transistores en dedos |  |  |

|              |                     | 6.3.5.2 Apareamiento o matching               |  |  |

|              |                     | 6.3.5.3 Técnica del centroide común_          |  |  |

|              |                     | 6.3.6 Reglas de diseño                        |  |  |

|              |                     | 6.3.6.1 Tamaño de los polígonos               |  |  |

|              |                     | 6.3.6.2 Regla de separación                   |  |  |

|              |                     | 6.3.6.3 Regla de solapamiento                 |  |  |

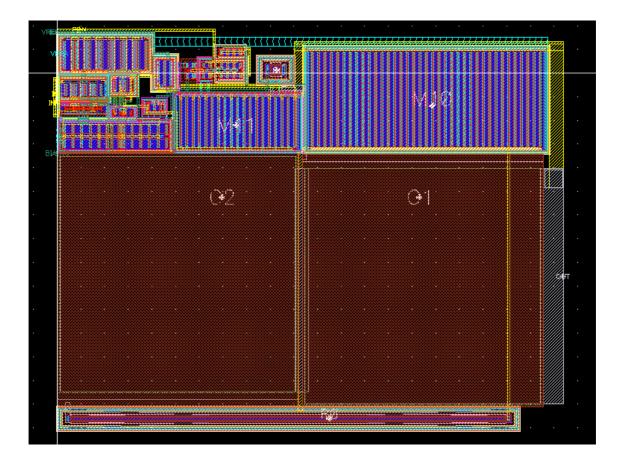

|              | 6.4                 | Nuestro layout                                |  |  |

|              | 6.5                 |                                               |  |  |

|              | 0.3                 | Conclusiones                                  |  |  |

| 7 <b>.</b> ] | Resul               | tados y conclusiones                          |  |  |

| <b>7.</b> [  | Resul               | tados y conclusiones Introducción             |  |  |

| 7 <b>.</b> [ | Resul               | tados y conclusiones                          |  |  |

| <b>7.</b> [  | Resul               | tados y conclusiones Introducción             |  |  |

| <b>7.</b> ો  | Resul<br>7.1<br>7.2 | tados y conclusiones Introducción Resumen     |  |  |

Capítulo 1

# INTRODUCCIÓN

#### 1.1 Introducción

El primer circuito integrado se desarrolló en 1958 por el ingeniero Jack Kilby, desde entonces han evolucionado rápidamente, tanto que habiendo transcurrido tan sólo medio siglo desde su desarrollo, éstos se han vuelto casi omnipresentes en nuestras vidas. Hoy en día encontramos circuitos integrados en todos los aparatos electrónicos modernos como automóviles, televisores, teléfonos móviles, etc.

Podemos definir un circuito integrado como la incorporación de todos los componentes activos y pasivos de un circuito electrónico de manera conjunta en una única pastilla de material semiconductor.

Actualmente, la tecnología más empleada en la fabricación de circuitos integrados es la del silicio llegando a cubrir más del 85% del mercado mundial de los semiconductores. Además, es considerada como la tecnología actual más madura y en ella se incorporan los circuitos más avanzados.

Los procesos de fabricación actuales de los circuitos integrados se basan en los principios de la tecnología *planar*, en la que todos los componentes están localizados en la superficie superior del cristal de silicio. El proceso de fabricación consiste en la aplicación de una secuencia de procesos físico-químicos en la superficie del cristal, actuando de forma selectiva mediante el uso de máscaras junto a un delicado y crítico proceso de fotolitografía miniaturizada.

Por lo tanto, podemos decir que los circuitos integrados, en su versión de tecnología CMOS, actualmente madura, o en la de tecnologías previsibles a medio plazo, han tenido un protagonismo en el progreso de las áreas de la computación, las comunicaciones y la automatización. Hasta la actualidad y según la previsión para la próxima década, este progreso se puede expresar básicamente por la ley de Moore: "Todos los parámetros característicos de las tecnologías de la información mejoran en un factor de 2 cada 1.5 a 3 años".

En 1980 muchos expertos predijeron el declive de los circuitos analógicos ya que el mundo digital estaba desarrollándose rápidamente debido a los avances en las tecnologías de los circuitos integrados. Muchas funciones que habían sido realizadas por los circuitos analógicos ahora se realizaban fácilmente en el dominio digital. Pero esta predicción nunca se ha llegado a cumplir, porque aunque el procesado de señales digitales haya avanzado mucho desde entonces los circuitos analógicos son necesarios en muchos sistemas.

Un gran paso en el desarrollo de los circuitos integrados fue aplicar la tecnología CMOS a diseños analógicos. El bajo coste de fabricación y la posibilidad de localizar circuitos analógicos y digitales en el mismo chip mejora el rendimiento y reduce el coste.

Sin embargo, en un principio los MOSFETs eran más lentos y ruidosos que los transistores bipolares, encontrando limitaciones en diversas aplicaciones. A pesar de esto la tecnología CMOS ha llegado a ser dominante en el mercado analógico debido a la continua mejora de la velocidad, la cual se ha incrementado muchísimo en los últimos 30 años, llegando a ser comparable con la de los transistores bipolares.

Por lo tanto, podemos decir que las tecnologías de circuitos integrados han abarcado ampliamente diseños analógicos, permitiendo una complejidad, velocidad y precisión que sería imposible conseguir usando implementaciones discretas.

# 1.2 Objetivos

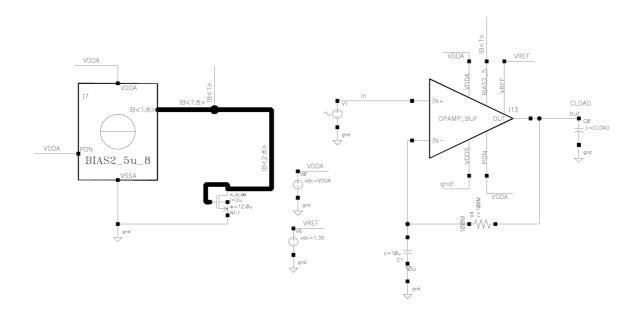

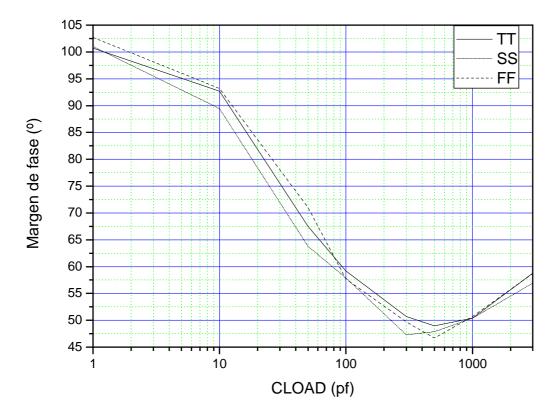

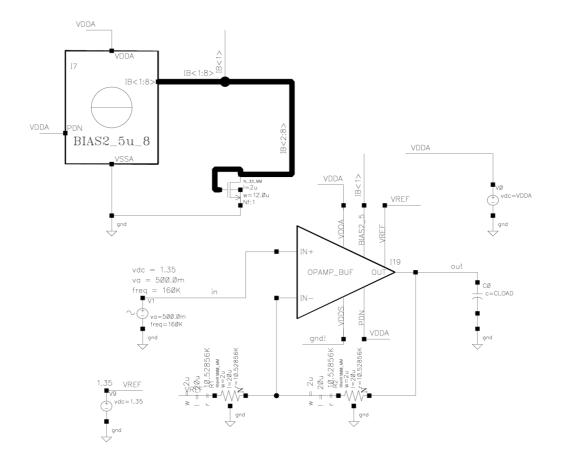

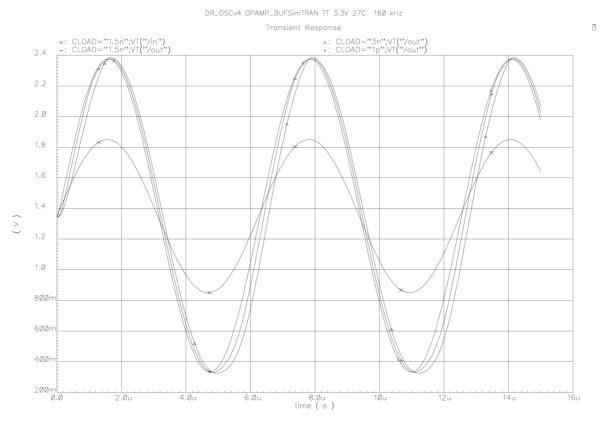

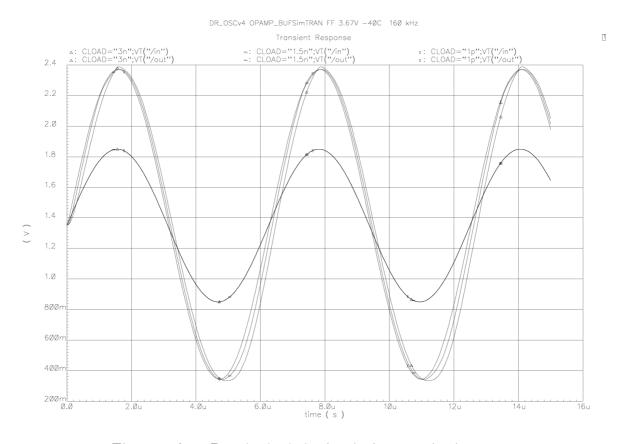

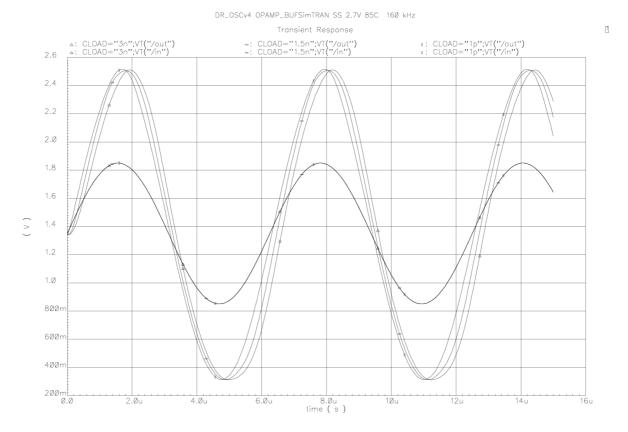

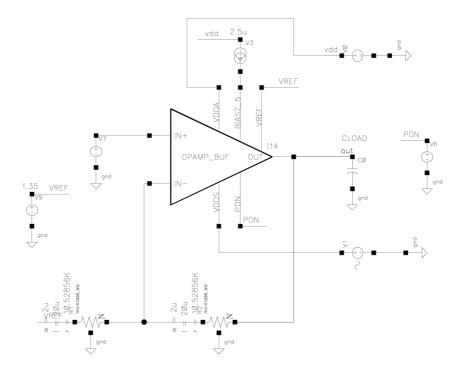

El principal objetivo de este proyecto es realizar el diseño de un amplificador operacional completamente integrado en tecnología CMOS para ser utilizado como driver. Por tanto, el circuito de salida deberá proporcional corrientes de salida lo suficientemente altas, como para soportar cargas capacitivas de salida elevadas. Concretamente, el circuito debe ser capaz de trabajar con cargas de salida de valores comprendidos entre 1pF y 3nF y todo ello con un consumo máximo de 1.6mA. Además, el circuito deberá ser estable para diferentes condiciones de polarización (VDD: 2.7V – 3.6V) y de temperatura (T=-40° - 85°). El circuito será integrado en la tecnología CMOS 0.18µm de UMC.

Para el diseño del amplificador operacional se llevará a cabo un estudio teórico de los transistores MOS que vamos a emplear y de los parámetros más importantes que debemos tener en cuenta a la hora del diseño.

Una vez completado el estudio teórico se procede a la elaboración del diseño. Para la elaboración del mismo se seguirá el flujo de diseño típico en un sistema integrado, es decir, se partirá de un diseño a nivel de esquemático que poco a poco se irá optimizando para, posteriormente, pasar a la elaboración del *layout* del mismo. Una vez finalizadas las simulaciones de los diseños se procede al envío de los circuitos a fabricación, dando por finalizado el trabajo. Es digno de mención que al tratarse de un sistema analógico, el diseño a nivel de *layout* debe realizarse enteramente a mano ya que no se dispone de células estándar que faciliten el diseño del mismo (diseño *full-custom*).

En el siguiente apartado daremos una visión general de la estructura de la memoria así como un resumen del desarrollo del proyecto.

#### 1.3 Estructura de la memoria

La memoria se desarrollará en siete capítulos aconpañados del presupuesto y de la bibliografía. A continuación presentamos un breve resumen de cada capítulo.

En el Capítulo 2 se hará un estudio de los dispositivos activos, los transistores MOS. En donde además de ver el funcionamientos de éstos, calcularemos los parámetros K y Vt de la tecnología en la que implementaremos nuestro diseño.

En el Capítulo 3 se hará una pequeña introducción a los amplificadores operacionales donde veremos todos aquellos parámetros más importantes que deberemos tener en cuenta a la hora del diseño de los mismos.

En el Capítulo 4 veremos el diseño de un amplificador operacional básico. Para ello estudiaremos las diferentes etapas que lo componen (fuentes de corriente, etapas de entrada y salida, realimentación, etc). También veremos el diseño de un amplificador de transconductancia (OTA) como paso previo al diseño del amplificador operacional.

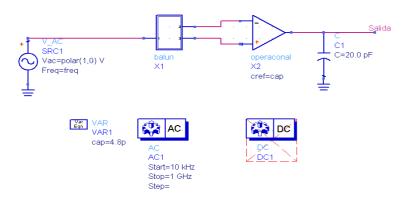

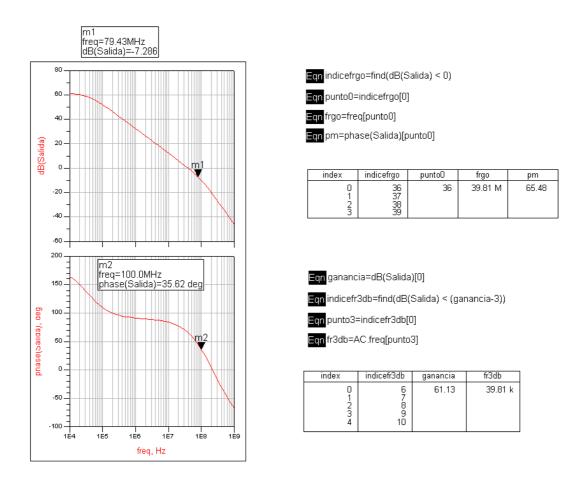

En el Capítulo 5 probaremos diferentes estructuras de amplificadores operacionales hasta encontrar el diseño óptimo que cumpla con las especificaciones pedidas en este proyecto. Estos diseños por simplicidad los haremos en ADS para, una vez decidida la estructura de nuestro diseño, pasarnos a *CADENCE* donde trabajaremos con la tecnología en la que será implementado.

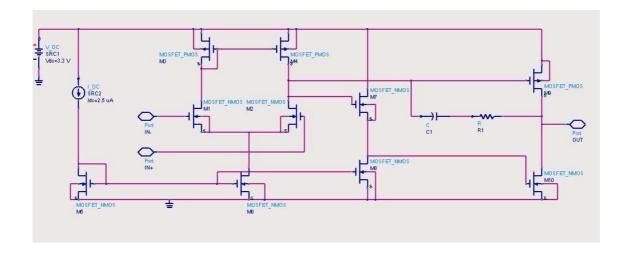

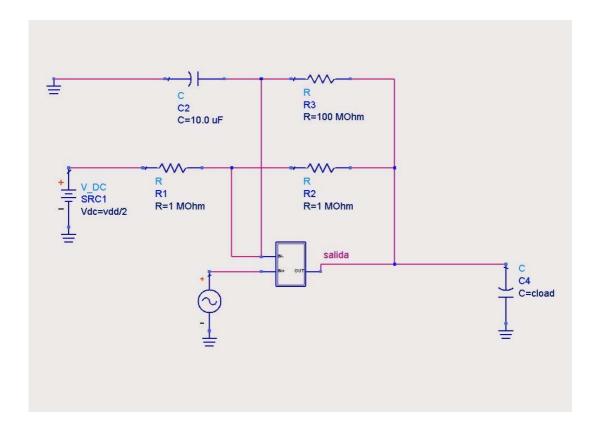

En el Capítulo 6 optimizaremos en *CADENCE* el diseño elegido en el capítulo anterior ya con la tecnología en la cual se va a implementar. Probaremos que el diseño funciona para todos los casos posibles y, una vez comprobado que su comportamiento es el deseado pasaremos a realizar su vista *layout*.

Por último, en el Capítulo 7, se resumirán las principales conclusiones. Por otro lado, se muestran los resultados de las simulaciones del diseño donde vemos que cumple con todas las condiciones en todos los casos posibles.

Capítulo 2

# EL TRANSISTOR MOS

#### 2.1 Introducción

Antes de comenzar con el diseño debemos realizar un estudio de la tecnología que vamos a utilizar en nuestro diseño. En este caso usaremos la tecnología CMOS 0.18µm de UMC. De los dispositivos activos de esta tecnología sólo estudiaremos los MOSFET, ya que nuestro diseño constará únicamente de estos transistores, siendo la longitud de puerta mínima de 0,18 µm.

Los primeros estudios de los transistores de efecto de campo se remontan a 1953 (Shockley con la teoría del JFET), pero no es hasta principios de los años sesenta cuando D. Kahng y J. Atalla realizan el primer transistor de efecto de campo MOS, también denominado MOSFET (iniciales de Metal Oxide Semiconductor Field Effect Transistor).

El principio de funcionamiento de los transistores MOS se basa en el uso de un campo eléctrico para la creación de un canal de conducción por donde circulará la corriente que podrá ser en forma de electrones o huecos.

El MOSFET es un dispositivo de cuatro terminales denominados drenador (D, del inglés *Drain*), puerta (G, del inglés *Gate*), surtidor o fuente (S, del inglés *Source*) y sustrato (B, del inglés *Bulk*). La corriente (electrones o huecos) en el interior del dispositivo, circula desde la fuente hasta el drenador, y es controlada por la puerta. Al terminal del sustrato se le aplica una tensión constante y ésta fijará la tensión umbral del transistor.

En estos transistores bajo el terminal de puerta existe una capa de óxido (SiO<sub>2</sub>) que impide prácticamente el paso de corriente; por lo que el control de la puerta se establece en forma de tensión. La calidad y estabilidad con que es posible fabricar estas finas capas de óxido es la principal causa del éxito de este transistor. Además, una propiedad muy importante de este dispositivo es que suele ocupar sobre el silicio un área muy pequeña, lo que permite una alta densidad de integración.

## 2.2 Funcionamiento

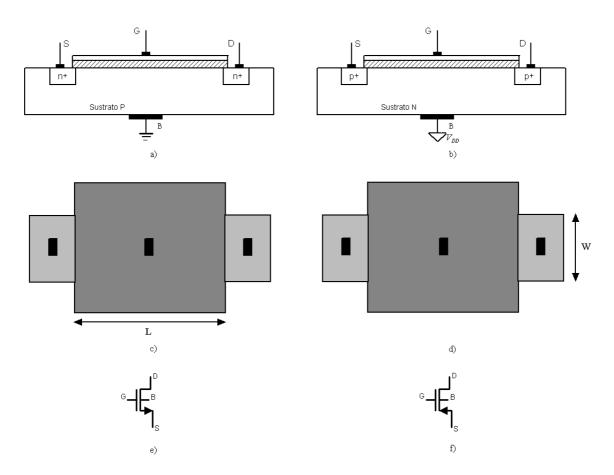

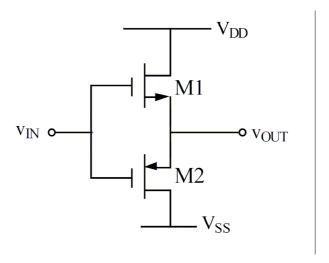

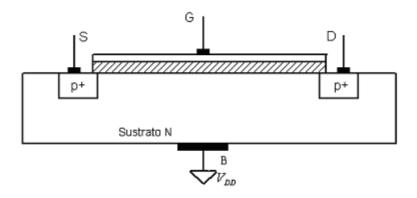

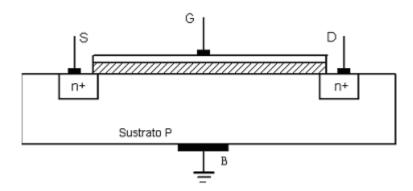

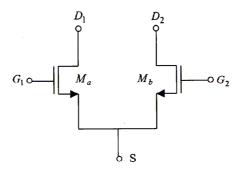

Existen dos tipos de transistores **MOS**, dependiendo de que la corriente sea por huecos o electrones: **MOSFET** de canal N o **NMOS** y **MOSFET** de canal P o **PMOS**. El corte esquemático y símbolo de estos transistores se muestra en la Figura 2.1:

Figura 2. 1 Corte esquemático y símbolos de los transistores MOS

Vemos que el dopaje del sustrato es opuesto al tipo de portador que origina la corriente. Así, para un transistor NMOS (electrones en conducción) el dopaje del sustrato es tipo P, mientras que para un transistor PMOS (huecos en conducción) el dopaje del sustrato es

tipo N. Y con el fin de facilitar la corriente a través de los terminales de fuente y drenador, se crea bajo ellas regiones con dopaje elevado, del mismo tipo que los portadores del canal (regiones N+ y P+).

Cuando aplicamos una tensión positiva al terminal de puerta de un MOSFET de canal N, se crea un campo eléctrico bajo la capa de óxido que incide perpendicularmente sobre la superficie del semiconductor. Este campo atrae a los electrones hacia la superficie bajo el óxido, repeliendo los huecos hacia el sustrato. Si el campo eléctrico es muy intenso se logra crear en dicha superficie una región muy rica en electrones, denominada canal N, que permite el paso de corriente de la fuente al drenador; cuanto mayor sea la tensión de puerta mayor será el campo eléctrico y, por tanto, la carga en el canal. Una vez creado el canal, la corriente se origina aplicando una tensión en el drenador positiva respecto a la de la fuente.

En el caso de un MOSFET de canal P el funcionamiento es a la inversa. Para que exista conducción el campo eléctrico perpendicular a la superficie debe tener sentido opuesto al del MOSFET de canal N, por lo que la tensión aplicaba debe ser negativa. Ahora los huecos son atraídos hacia la superficie bajo el óxido, y los electrones repelidos hacia el sustrato. Si la superficie es muy rica en huecos se forma el canal P. Cuanto más negativa sea la tensión de puerta mayor podrá ser la corriente que se establece al aplicar al terminal de drenador una tensión negativa respecto a la de la fuente. El sentido de la corriente en este caso será opuesto al de un MOSFET tipo N.

La tensión de puerta necesaria para que se produzca el canal se conoce como tensión umbral, V<sub>p</sub> y se fija aplicándole al sustrato una tensión constante.

La capa de óxido bajo la puerta impide que haya corriente a través de ésta (esto es cierto en continua y a frecuencias bajas). Así, la corriente en el terminal de fuente,  $I_s$ , coincidirá con la de drenador,  $I_D$ , por lo que:

$$I_G = 0 (2.1)$$

$$I_D = I_S \tag{2.2}$$

#### 2.3 Curva característica de los transistores

#### 2.3.1 TRANSISTOR TIPO N

En un amplificador MOSFET de canal N sin ninguna tensión de polarización existen dos diodos rectificadores en serie entre el drenador y la fuente, éstos previenen que fluya corriente desde el drenador hacia la fuente cuando aplicamos un voltaje  $V_{DS}$ . De hecho, la conexión entre drenador y fuente tiene una resistencia muy alta (del orden de  $10^{12}\Omega$ ).

Si aplicamos a la puerta un voltaje positivo que supere la tensión umbral,  $V_t$ , el transistor forma un canal N. Además, cuando aplicamos un voltaje positivo entre drenador y fuente, como se muestra en la Figura 2.2, se crea una corriente.

Figura 2. 2 Circuito para simular la curva característica del NMOS

La tensión  $V_{DS}$  que como dijimos crea una corriente  $I_D$  que fluye directamente en el canal N. La corriente está formada por electrones libre que fluyen desde la fuente hacia el drenador, por lo tanto, la magnitud de Id dependerá de la densidad de electrones en el canal, que a su vez depende de la magnitud de  $V_{GS}$ . Como  $V_{GS}$  supera  $V_D$ , más electrones son atraídos hacia el canal. El resultado de esto es un canal con una conductancia elevada o una resistencia equivalente pequeña.

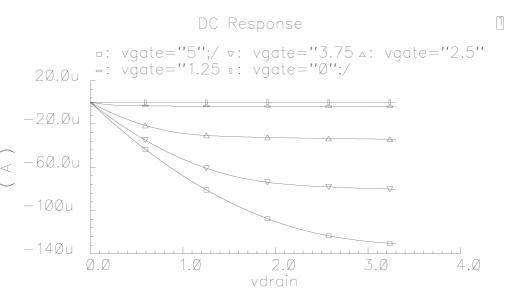

A continuación en la Figura 2.3 mostramos la gráfica de  $I_D$  frente a  $V_{DS}$  cuando incrementamos  $V_{DS}$  de 0 a 3.3V y mantenemos  $V_{GS}$  constante con valores superiores a  $V_t$ .

DC Response

: vgate="5";/ v: vgate="3.75 \( \text{\text{a}} : \text{vgate}="2.5" \)

300u

: vgate="1.25 \( \text{\text{i}} : \text{vgate}="0";/ \)

200u

0.00

1.00

2.00

3.00

4.00

# Figura 2.3 Curva características del NMOS

vdrain

Para las diferentes tensiones de puerta,  $V_{GS}$ , hay una curva característica que muestra la dependencia de la corriente de drenador, Id, con el voltaje entre drenador y fuente,  $V_{DS}$ .

Vemos que si la tensión de drenador es inferior a la tensión umbral, V, el trasistor está cortado y, por tanto, no circulará corriente.

Si aumenta  $V_{DS}$  y supera la tensión umbral, el transistor opera en una región lineal: apreciándose el comportamiento parabólico de la corriente con la tensión de drenador.

Vemos en la gráfica que la corriente de drenador, I<sub>D</sub>, se satura cuando:

$$V_{DS} = V_{GS} - V_t \tag{2.3}$$

Entonces decimos que el transistor está en la región de saturación:

$$V_{DS,sat} = V_{GS} - V_t \tag{2.4}$$

Obviamente, para todos los valores de  $V_{GS} \ge V_t$ , hay un valor correspondiente de  $V_{DS,sat}$ . El dispositivo opera en la región de saturación cuando  $V_{DS} \ge V_{DS,sat}$ .

Por lo tanto, podemos ver que hay distintas regiones de operación: la región de corte, la región lineal y la región de saturación. La región que se usa si el transistor opera como amplificador es la de saturación.

## 2.3.2 TRANSISTOR TIPO P

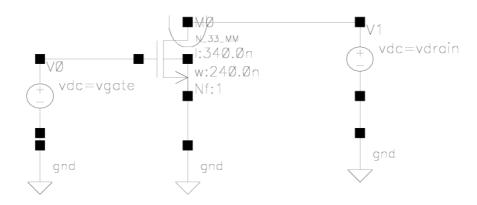

En un transistor PMOS el funcionamiento es igual al de un transistor NMOS pero las tensiones de  $V_{GS}$ ,  $V_t$  y  $V_{DS}$  son negativas. Para obtener la gráfica de  $I_D$  frente a  $V_{DS}$  aplicamos a la puerta una tensión negativa que supere la tensión umbral,  $V_t$ , para que en el transistor se forme un canal P. Además, para que circule corriente aplicamos un voltaje negativo entre drenador y fuente (Figura 2.4):

Figura 2. 4 Circuito para la simulación de la curva característica del PMOS

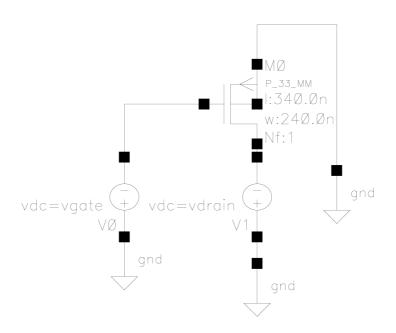

En la Figura 2.5 mostramos la gráfica de  $I_D$  frente a  $V_{DS}$  cuando incrementamos  $V_{DS}$  de 0 a 3.3V y mantenemos  $V_{GS}$  constante con valores superiores a  $V_t$

prueba prueba\_pmos schematic : Jul 16 11:36:09 2008

Figura 2. 5 Curva característica del PMOS

Igual que en los NMOS podemos distinguir tres regiones de funcionamiento del transistor: la región de corte, la región lineal y la región de saturación, e igualmente la región que se usa si el transistor opera como amplificador es la de saturación.

## 2.4 Regiones de Operación de los Transistores

## 2.4.1 REGIÓN DE CORTE

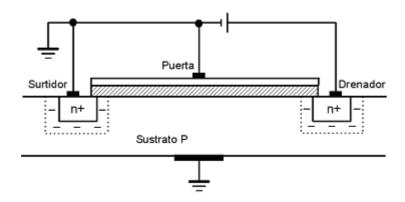

Cuando la tensión de la puerta es idéntica a la del sustrato (Figura 2.6), el MOSFET está en estado de no conducción: ninguna corriente fluye entre fuente y drenador aunque se aplique una diferencia de potencial entre ambos.

Para los N-MOS:

$$V_{GS} \le V_T; V_{DS} > 0 \Rightarrow I_D = 0$$

(2.5)

Para los P-MOS:

$$V_{GS} > V_T; V_{DS} < 0 \Rightarrow I_D = 0$$

(2.6)

Figura 2. 6 MOSFET tipo N en corte

## 2.4.2 REGIÓN LINEAL

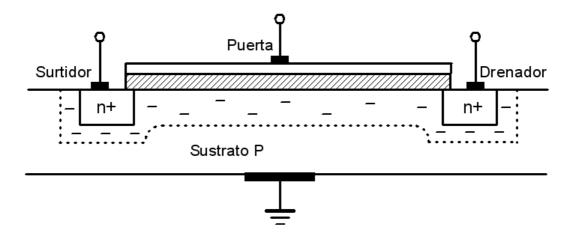

Al polarizarse la puerta con una tensión negativa (PMOS) o positiva (NMOS) el transistor pasa entonces a estado de conducción (Figura 2.7), de modo que una diferencia de potencial entre fuente y drenador dará lugar a una corriente.

Para los N-MOS:

$$V_{GS} > V_T; 0 < V_{DS} \le V_{GS} - V_T \Rightarrow I_D = \frac{k \cdot W}{L} \left[ (V_{GS} - V_T) \cdot V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.7)

Para los P-MOS:

$$V_{GS} < V_T; 0 > V_{DS} > V_{GS} - V_T \Rightarrow I_D = \frac{k \cdot W}{L} \left[ (V_{GS} - V_T) \cdot V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.8)

Figura 2. 7 Mosfet tipo N en la región lineal

## 2.4.3 REGIÓN DE SATURACIÓN

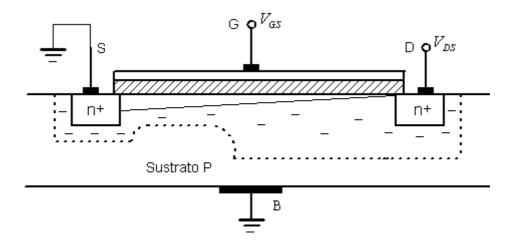

Cuando la tensión entre drenador y fuente supera cierto límite la corriente entre fuente y drenador se hace independiente de la diferencia de potencial entre ambos terminales como se muestra en la Figura 2.8.

Para los N-MOS:

$$V_{GS} > V_T; V_{DS} > V_{GS} - V_T \Rightarrow I_D = \frac{k}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_T)^2$$

(2.9)

Para los P-MOS:

$$V_{GS} < V_T; V_{DS} < V_{GS} - V_T \Rightarrow I_D = \frac{k}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_T)^2 \qquad (2.10)$$

Donde  $V_t$  es la tensión umbral, W y L la anchura y longitud del canal respectivamente, y k es el llamado parámetro de transconductancia cuyo valor viene dado por:

$$k = \mu_n \cdot C_{OX} \tag{2.11}$$

Donde  $\mu_n$  es la movilidad de los electrones y  $C_{OX}$  es la capacidad de la puerta por unidad de área. Y sus unidades son:  $[k] = \left\lceil \frac{A}{V^2} \right\rceil$ .

Figura 2. 8 Mosfet tipo N en saturación

## 2.5 Cálculo de la K y la V, de los transistores

Con las gráficas anteriores podemos calcular el parámetro de transconductancia, k, y la tensión umbral, V, de los transistores que vamos a usar en nuestro diseño. Sabemos que los transistores simulados tienen un ancho y una longitud de:

$$W = 240nm$$

$$L = 340nm$$

En las gráficas justo donde comienza la región de saturación sabemos que:

$$V_{DS} = V_{GS} - V_t \tag{2.12}$$

Y la corriente en esta región es:

$$I_{D} = \frac{k}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{T})^{2}$$

(2.13)

Por lo tanto sustituyendo valores en ambas ecuaciones podremos calcular k y V<sub>v</sub>, en este caso el valor de la tensión umbral para ambos transistores es:

$$V_{tr} \cong 0.65V$$

$$V_{tp} \cong -0.7V$$

Y calculando el parámetro de transconductancia para ambos transistores tenemos:

$$K_n = 100 \cdot 10^{-6}$$

$$K_p = 30 \cdot 10^{-6}$$

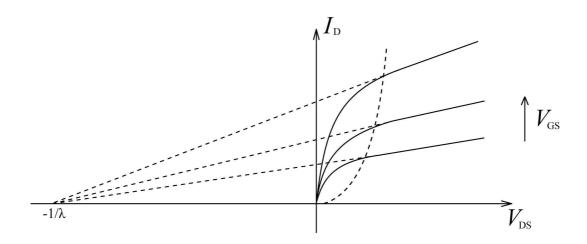

#### 2.6 Desviaciones del modelo

En realidad, cuando el transistor opera en la región de saturación la corriente de drenador no es independiente del voltaje entre el drenador y la fuente, sino que a medida que aumenta  $V_{DS}$  la corriente crece ligeramente. Este efecto se denomina modulación de la longitud del canal, el parámetro que modela esto es  $\lambda$ . Para tener en cuenta esta discrepancia con el modelo ideal, basta con multiplicar la ecuación de la  $I_D$  por el factor  $(1+\lambda\cdot V_{DS})$ , según el modelo analítico de Sah [21], obteniendo la ecuación 2.14.

$$I_{D} = \frac{K_{n}}{2} \cdot \frac{W}{L} (V_{GS} - V_{T})^{2} [1 + \lambda \cdot V_{DS}]$$

(2.14)

La ecuación 2.14 es válida únicamente para los valores de  $V_{DS}$  por encima de  $V_{DSP}$  (Región de Saturación). La presencia de  $\lambda$  en la ecuación de la corriente de drenador produce una ligera pendiente ascendente de la  $I_D$  con respecto a  $V_{DS}$  como se muestra en la Figura 2.9.

Figura 2. 9 Efecto de la modulación de la longitud del canal

A pesar de que el desarrollo anterior se refiere a un transistor MOSFET tipo n, en el caso del transistor MOSFET tipo p las ecuaciones son equivalentes, teniendo en cuenta que las tensiones puerta-surtidor, drenador-surtidor y umbral tienen signos contrarios, así que la corriente  $I_D$  en el MOSFET tipo p es de signo opuesto al del MOSFET tipo n.

## 2.7 Modelo en Pequeña Señal

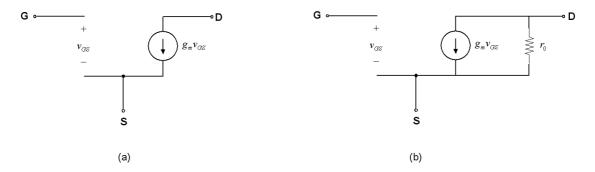

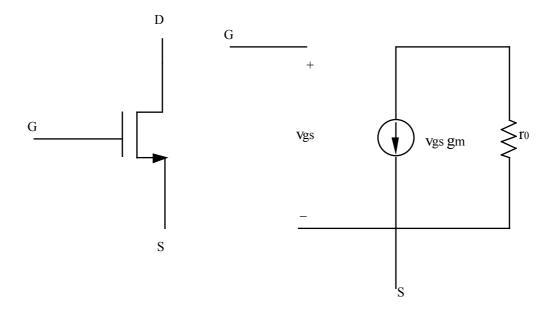

En la Figura 2.10 se muestra el modelo en baja frecuencia del transistor MOS trabajando en la región de saturación, viendo al transistor como una fuente de corriente controlada por tensión.

El parámetro  $g_m$ , es denominado parámetro de transconductancia del MOSFET y viene definido por la ecuación 2.15:

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} = K_n (V_{GS} - V_t) (1 + \lambda V_{DS})$$

(2.15)

Figura 2. 10 (a) Modelo de baja frecuencia del MOSFET, (b) incorporación de la modulación de la longitud del canal.

El parámetro  $r_0$  es la resistencia dinámica de salida, que viene definida por la ecuación 2.16.

$$r_0 = \left(\frac{\partial I_D}{\partial V_{DS}}\right)^{-1} = \frac{1}{\frac{1}{2} \cdot K_n \cdot \frac{W}{L} (V_{GS} - V_t)^2 \cdot \lambda} \approx \frac{1}{\lambda \cdot I_D}$$

(2.16)

Esta resistencia representa la impedancia de salida como consecuencia del efecto de la modulación del canal.

#### 2.8 Modelo en Alta Frecuencia

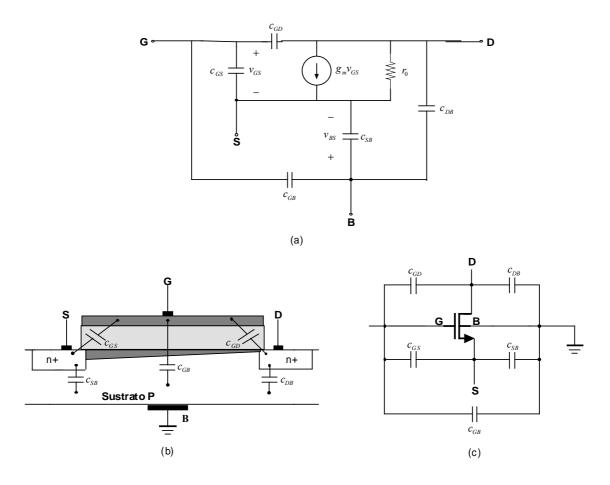

En la Figura 2.11 (a) se muestra el modelo de alta frecuencia del transistor MOS. Este modelo, conocido como *modelo de Shichman-hodges* [refa4], muestra las capacidades parásitas del MOSFET cuando trabaja a alta frecuencia. En la Figura 2.11 (b) y (c) se muestra más gráficamente donde se encuentran ubicadas estas capacidades.

Figura 2. 11 Modelo del MOSFET en Alta Frecuencia

Se pueden considerar claramente dos familias de capacidades:

• Capacidades de la zona de carga espacial:

Son las capacidades  $C_{DB}$  y  $C_{SB}$  y se producen en las uniones PN polarizadas inversamente (*depletion capacitances*). Son dependientes de la tensión y son causa del retardo y consumo indeseado cuando los terminales del transistor son nodos dinámicos. Son proporcionales al área y perímetro de las regiones del drenador y surtidor. Estas capacidades vienen dadas por las ecuaciones 2.17 y 2.18:

$$C_{DB} = \frac{C_{DB0}}{\left(1 - \frac{V_{DB}}{\psi_o}\right)^m} \tag{2.17}$$

$$C_{SB} = \frac{C_{SB0}}{\left(1 - \frac{V_{SB}}{\psi_{0}}\right)^{m}}$$

(2.18)

Donde  $C_{DB0}$  y  $C_{SB0}$  son las capacidades de las uniones cuando la polarización de estas son nulas,  $V_{DB}$  y  $V_{SB}$  son las tensiones directas de las uniones,  $\Psi_o$  es la barrera de potencial y m es una constante dependiente del tipo de unión.

## Capacidades en la zona de óxido:

Estas capacidades aparecen entre el terminal de puerta y el resto de terminales del dispositivo. El valor de estas capacidades dependen de las variables de diseño, de las dispersiones en el proceso de fabricación y del estado en el que se encuentre el transistor.

Las principales capacidades de óxido son  $C_{GB}$  (capacidad de óxido entre puerta y sustrato),  $C_{SG}$  (capacidad de óxido entre surtidor y puerta) y  $C_{GD}$  (capacidad de óxido entre puerta y drenador).

En la Tabla 2.1 se muestra el valor de las capacidades de óxido en las distintas regiones de trabajo del transistor MOSFET.

Tabla 2.1 Capacidades de la zona de óxido de un transistor MOSFET:

| CAPACIDAD | CORTE          | ÓHMICA                     | SATURACIÓN                  |

|-----------|----------------|----------------------------|-----------------------------|

| $C_{GD}$  | $C_{OX}L_{d}W$ | $C_{OX}L_{d}W+0,5C_{OX}LW$ | $C_{OX}L_{d}W$              |

| $C_{GS}$  | $C_{OX}L_{d}W$ | $C_{OX}L_{d}W+0,5C_{OX}LW$ | $C_{OX}L_{d}W+0,66C_{OX}LW$ |

| $C_{GB}$  | $C_{OXd}W$     | 0                          | 0                           |

En la Tabla 2.1 los parámetros implicados en las expresiones son: Cox (capacidad de puerta por unidad de área),  $L_d$  (distancia de difusión lateral que se produce bajo la puerta), L (longitud del canal del transistor), W (ancho del canal del transistor).

# 2.9 Conclusiones

En este capítulo hemos hecho una pequeña introducción a los transistores MOS donde hablamos de su evolución histórica y funcionamiento. Con esto hemos conseguido obtener una visión más profunda del comportamiento de los MOSFET para la realización del amplificador operacional. Una vez completado el estudio teórico de los transistores MOS en el próximo capítulo haremos una pequeña introducción a los amplificadores operacionales donde veremos los parámetros más importantes para el diseño de los mismos.

Capítulo 3

# INTRODUCCIÓN A LOS AMPLIFICADORES OPERACIONALES (OP-AMPS)

#### 3.1 Introducción

En esta sección estudiaremos los parámetros más importantes de un amplificador operacional. En el diseño de un Op-Amp se debe tener un claro conocimiento del significado de los parámetros del mismo y de cómo afectan al diseño del circuito. La elección de cualquiera de estos parámetros deberá basarse en el conocimiento de qué parámetros son los más importantes para la aplicación en la que se esté trabajando. En la siguiente sección, discutiremos el método de medida de los diferentes parámetros.

### 3.2 Parámetros de un Op-Amp

#### 3.2.1 TENSIÓN DE OFFSET

Todos los Op-Amps requieren un pequeño voltaje entre sus entradas inversora y no inversora para equilibrar los desajustes debido a las inevitables variaciones del proceso. El voltaje requerido es conocido como offset de entrada,  $V_{os}$ . Normalmente, este voltaje es modelado como una fuente de tensión conectada a la entrada no inversora. Generalmente, las entradas de los Op-Amps bipolares ofrecen mejores parámetros de offset que la entrada de los Op-Amps JFET o CMOS. Hay otros dos parámetros relacionados que afectan al  $V_{os}$ : el coeficiente de temperatura media del offset de entrada, y la deriva a largo plazo de la tensión de offset de entrada. El coeficiente de temperatura media de la tensión de offset de entrada,  $\alpha \cdot V_{os}$ , especifica la deriva del offset de entrada con la temperatura. Su unidad es

$\left[\frac{mV}{{}^{o}C}\right]$ . El  $V_{os}$  se mide en los extremos de temperatura del circuito, y, el coeficiente de temperatura media,  $\alpha \cdot V_{os}$ , se calcula como  $\frac{V_{os}}{{}^{o}C}$ . El envejecimiento normal en los semiconductores causa cambios en las características de los dispositivos. La deriva a largo plazo del voltaje del offset de entrada especifica como se espera que cambie con el tiempo el  $V_{os}$ . Las unidades son  $\frac{mV}{month}$ . El voltaje del offset de entrada es motivo de preocupación en cualquier momento que se requiera precisión en DC del circuito. Una manera de eliminar el offset es usando entradas externas de eliminación de offset. De esta forma, entre estas entradas se conecta un potenciómetro con el terminal ajustable conectado a la alimentación negativa a través de una resistencia en serie, ver Figura 3.1. El voltaje del offset de entrada se elimina cortocircuitando las entradas y ajustando el potenciómetro hasta que la salida sea cero. Sin embargo, aún anulando el offset de esta manera, éste cambiará con la temperatura y algunas otras condiciones.

Figura 3. 1 Ajuste de la tensión de offset

#### 3.2.2 CORRIENTE DE ENTRADA

Los circuitos de entrada de todos los Op-Amps requieren una cierta cantidad de corriente de polarización para funcionar correctamente. La corriente de entrada de polarización,  $I_{IB}$ , se calcula como la media de dos entradas:

$$I_{IB} = \frac{I_N + I_P}{2} \tag{3.1}$$

Los circuitos de entrada CMOS y JFET necesitan una corriente mucho más baja que las de los bipolares. La diferencia entre la corriente de polarización en la entrada inversora y la no inversora es el llamado offset de corriente de entrada,  $I_{OS} = I_N - I_P$ . Típicamente el offset de corriente es de un orden de magnitud inferior a la corriente de polarización.

La corriente de polarización de entrada es importante cuando la impedancia de la fuente es alta. Si el Op-Amp tiene una corriente de polarización de entrada alta, cargará a la fuente y la tensión vista a la entrada será menor a la esperada. La mejor solución es usar un Op-Amp con entrada CMOS o JFET. Otra alternativa es bajar la impedancia de la fuente usando una etapa buffer entre la entrada y el Op-Amp. En el caso de entradas bipolares, el offset de corriente se puede anular ajustando la impedancia vista a la entrada. En el caso de entradas CMOS o JFET, el offset de corriente por lo general no es un problema y no es necesario ajustar la impedancia. El coeficiente de temperatura media del offset de entrada de corriente, I<sub>os</sub>, especifica la deriva del offset de entrada esperado con la temperatura. Las unidades son

$$\left\lceil \frac{mA}{{}^{\circ}C} \right\rceil$$

Figura 3. 2 Máxima excursión de salida

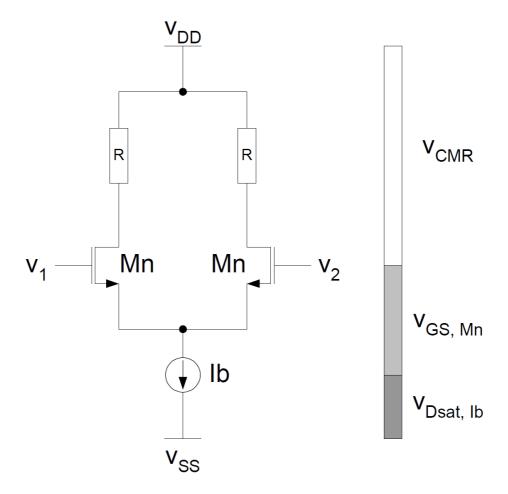

# 3.2.3 TENSIÓN DE ENTRADA EN MODO COMÚN

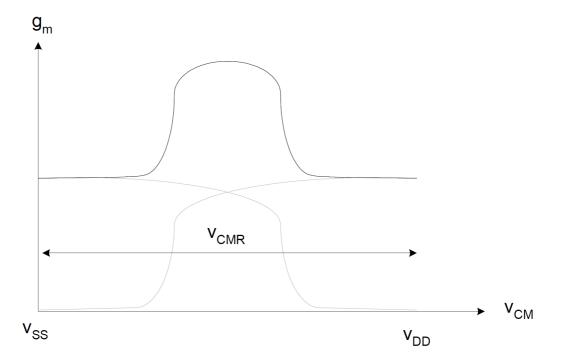

La tensión de entrada en modo común se define como el voltaje medio en los pines inversor y no inversor de entrada. Si la tensión en modo común se hace demasiado grande o demasiado baja, las entradas se cortarán y el circuito dejará de funcionar. El rango de tensión en modo común de entrada, VICR, especifica el rango por encima del cual el funcionamiento es garantizado. Por ejemplo, los Op-Amps con entrada rail to rail¹ usa la tensión de entrada en dispositivos complementarios tipo N y P en las entradas diferenciales. Cuando la tensión de entrada en modo común se acerca a cualquier rail, al menos una de las entradas diferenciales sigue activa, y el circuito sigue funcionando correctamente.

## 3.2.4 EXCURSIÓN DE SALIDA MÁXIMA

La tensión máxima de salida,  $V_{OM}$ , se define como la tensión de pico positivo o negativo máxima sin que se recorte la forma de onda, cuando la tensión de salida en DC es cero. La  $V_{OM}$  viene limitada por la impedancia de salida del amplificador, la tensión de saturación de los transistores de salida, y por la tensión de la fuente de alimentación. Esto se muestra de forma gráfica en la Figura 3.2.

La estructura seguidor de emisor mostrada no puede hacer que la tensión de salida llegue a cualquiera de los railes. Los Op-Amps con salida rail-to-rail suelen usar etapas de salida en

1

<sup>&</sup>lt;sup>1</sup> Rail to rail: que va de Vcc a -Vcc.

emisor común (bipolares) o fuente común (CMOS). Con estas estructuras, la excursión de salida sólo estará limitada por las tensiones de saturación (bipolares) o las resistencias de ON (CMOS) de los transistores de salida, y por la carga.

#### 3.2.5 IMPEDANCIA DE SALIDA

Las hojas de datos o data sheets de los Op-Amps definen la impedancia de salida bajo dos condiciones diferentes. En algunos data sheets la impedancia de salida está dada en lazo cerrado y en otras está en lazo abierto, ambas designadas por  $Z_0$ . La impedancia de salida se define como la impedancia en pequeña señal entre el terminal de salida y tierra. Generalmente, tiene valores de 50 a  $200\Omega$ .

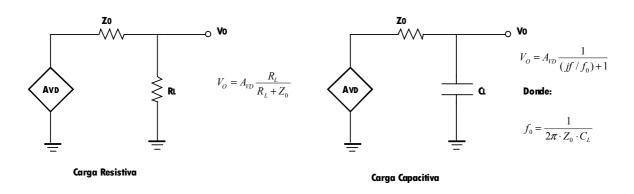

Las etapas de salida en emisor común (bipolar) o fuente común (CMOS) típicas de los Op-Amps rail-to-rail tienen mayor impedancia de salida que las etapas de salida en seguidor de emisor. La impedancia de salida es, por tanto, un problema cuando usamos un Op-Amp rail-to-rail con cargas resistivas pequeñas o cargas capacitivas grandes. Si la carga es principalmente resistiva, la impedancia de salida limitará cómo de cerca de los railes puede ir la salida. Si la carga es capacitiva, la fase extra empeorará el margen de fase. En la Figura 3.3 se muestra cómo la impedancia de salida afecta a la señal de salida suponiendo que  $Z_0$  es principalmente resistiva.

Figura 3. 3 Efecto de la Impedancia de Salida

# 3.2.6 RECHAZO EN MODO COMÚN

El rechazo en modo común, CMRR, se define como la relación entre la ganancia de tensión diferencial y la ganancia de tensión en modo común,  $\frac{A_{dif}}{A_{com}}$ . Idealmente esta relación debería ser infinita, es decir, las tensiones en modo común deberían ser totalmente rechazadas.

La tensión de entrada en modo común afecta al punto de polarización del par diferencial de entrada. Debido a los desajustes inherentes a la circuitería de entrada, cualquier variación del punto de polarización cambia la tensión de offset, que, en consecuencia, cambia la tensión de salida.

#### 3.2.7 RECHAZO A LA FUENTE DE ALIMENTACIÓN

La relación de rechazo a la fuente de alimentación, PSRR, es la relación entre la variación de la tensión de alimentación del circuito y la tensión de salida del mismo. La fuente de alimentación afecta al punto de polarización del par diferencial de entrada. Debido a los desajustes inherentes a la circuitería de entrada, cualquier variación del punto de polarización cambia la tensión de offset que, en consecuencia, cambia la tensión de salida.

Por tanto, la relación de rechazo a la fuente de alimentación se define como  $PSRR = \frac{V_{CC}}{V_{OS}}$  ó

$PSRR = \frac{V_{DD}}{V_{OS}}$ . Nótese que el mecanismo que produce el PSRR es el mismo que para el

CMRR. Por tanto, el PSRR se publica en el *datasheet* como un parámetro DC igual que el CMRR. Si se representa el PSRR frente a la frecuencia, éste cae a medida que aumenta la frecuencia.

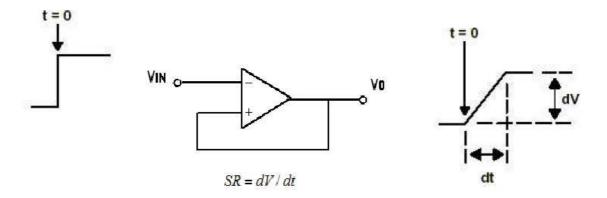

#### 3.2.8 SLEW RATE

El slew rate, SR, se define como el tiempo máximo de cambio del voltaje de salida cuando hay un cambio en el voltaje de entrada. Sus unidades son V/ms. La Figura 3.4 muestra el slew rate gráficamente.

Figura 3. 4 Slew Rate

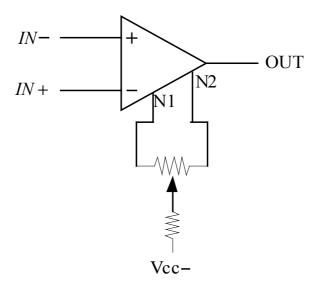

El principal factor que controla el slew rate en la mayoría de amplificadores es el condensador de compensación interna,  $C_C$ , que se añade para hacer que el Op-Amp sea estable. Por ejemplo, para el amplificador de la Figura 3.5, el máximo voltaje de salida está limitado por lo rápido que la corriente del transistor  $M_5$  carga y descargar al condensador de compensación  $C_C$ . El máximo tiempo de cambio es cuando cualquiera de los lados del par diferencial conduce 2IE, es decir,  $SR = 2IE/C_C$ . Sin embargo, no todos los Op-Amps tienen condensadores de compensación. En los Op-Amps sin condensadores de compensación interna, el slew rate viene determinado por capacidades parásitas internas del Op-Amp. Los Op-Amps no compensados tienen mejor ancho de banda y slew rate, pero el diseñador debe asegurar la estabilidad del circuito.

Figura 3. 5 Op-Amp de dos etapas

En los Op-Amps, existe un compromiso entre consumo, ruido y velocidad. Esto implica que si queremos incrementar el slew rate, debemos aumentar las corrientes de polarización internas del Op-Amp.

#### 3.2.9 ANCHO DE BANDA PARA GANANCIA UNIDAD Y MARGEN DE FASE

El ancho de banda para ganancia unidad (B1) y el producto ganancia por ancho de banda (GBW) son muy similares. B1 especifica la frecuencia a la que la ganancia diferencial,  $A_{VD}$ , del Op-Amp es 1. El GBW especifica el producto de ganancia por ancho de bando del Op-Amp en configuración de lazo abierto y con carga a la salida:

$$GBW = A_{VD} \cdot f \tag{3.2}$$

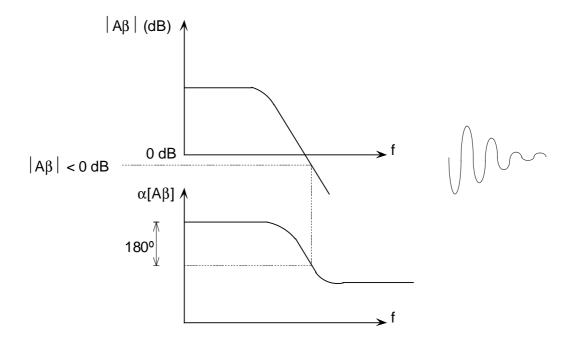

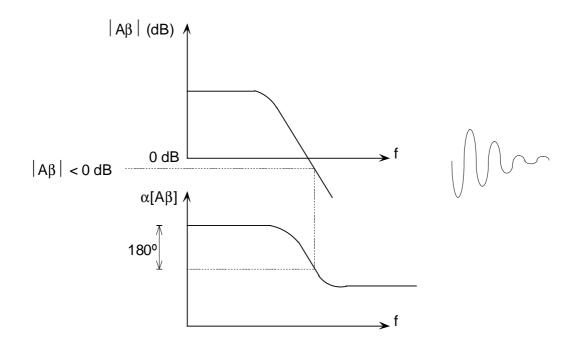

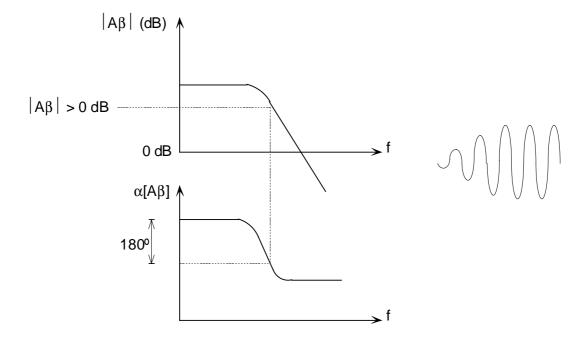

El margen de fase es la diferencia entre el valor de la fase a la frecuencia donde el módulo de la ganancia en lazo abierto cae a 0dB y -180°. Por razones de estabilidad el margen de fase

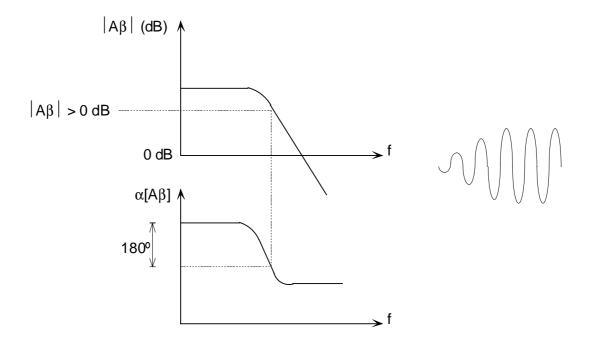

del amplificador debe ser como mínimo de 45° (se recomienda un margen de fase de 60°). Si es menor de 45° dará lugar a un tiempo de establecimiento demasiado grande y esto incrementará el retardo de propagación. En la Figura 3.6 se muestra una medida del margen de fase para un circuito estable y en la Figura 3.7 para un circuito inestable.

Figura 3. 6 Margen de fase para un circuito estable

Figura 3. 7 Margen de fase para un sistema inestable

Con el fin de hacer el Op-Amp estable se suele incluir en la segunda etapa del Op-Amp un condesador, Cc, de compensación. Este tipo de compensación en frecuencia se llama compensación por polo dominante. La idea es causar que la ganancia en lazo abierto del Op-Amp llegue a 0dB antes que la fase de salida pase por 180°.

El margen de fase y el margen de ganancia son maneras diferentes de especificar la estabilidad del circuito. Puesto que los Op-Amps con salida rail-to-rail tienen una impedancia de salida mayor, mayor será el cambio de fase para cargas capacitivas elevadas. Este cambio de fase extra erosiona el margen de fase, y por esta razón la mayoría de los Op-Amps CMOS con salidas rail-to-rail no son aptos para cargas capacitivas elevadas.

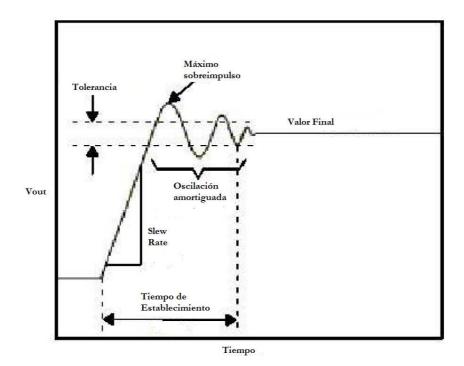

#### 3.2.10 TIEMPO DE ESTABLECIMIENTO

La propagación de una señal a través de los circuitos internos de un Op-Amp se toma un tiempo finito. Por consiguiente, para que la salida reaccione a un cambio tipo salto en la entrada tarda un periodo de tiempo determinado. Además, la salida normalmente rebasa el valor final, experimenta una oscilación amortiguada, y finalmente llega al valor final. El tiempo de establecimiento o settling time, t<sub>s</sub>, es el tiempo requerido para que el voltaje de salida se estabilice dentro de un porcentaje específico de el valor final dado un salto de entrada como se muestra en la Figura 3.8.

Figura 3. 8 Tiempo de Establecimiento

# 3.3 Conclusiones

En este capítulo hemos hecho una pequeña a los amplificadores operaciones (Op-Amps) donde hemos visto los parámetros más importantes que debemos tener en cuenta a la hora de diseñarlos. Una vez conocidos los parámetros que debemos tener en cuenta a la hora del diseño, en el próximo capítulo estudiaremos las diferentes etapas que componen un amplificador operacional y los diferentes tipos de compensaciones. Finalmente diseñaremos un amplificador de transconductancia como paso previo al diseño de un amplificador operacional de dos etapas.

# DISEÑO DE OP-AMPS

### 4.1 Introducción

En este capítulo estudiaremos las diferentes partes que componen un amplificador operacional y las consideraciones que debemos tener en cuenta a la hora de diseñarlo. Además, al final del mismo realizaremos un pequeño diseño de ejemplo.

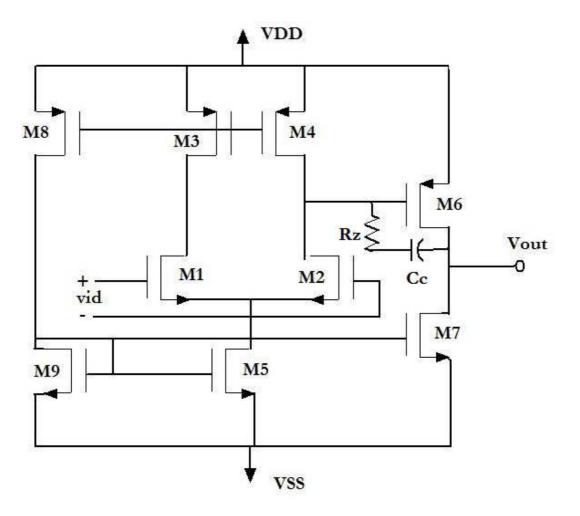

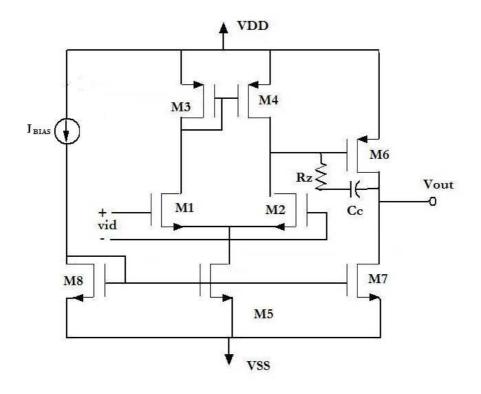

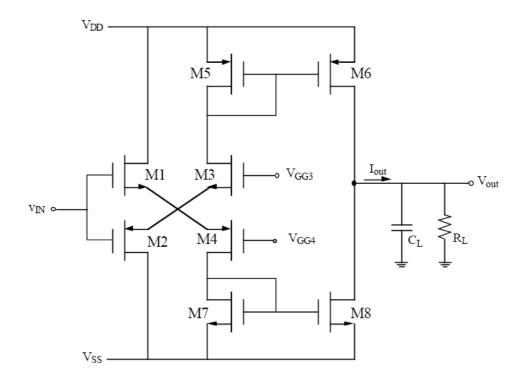

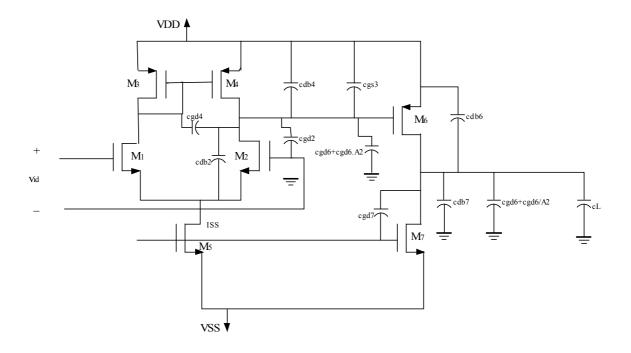

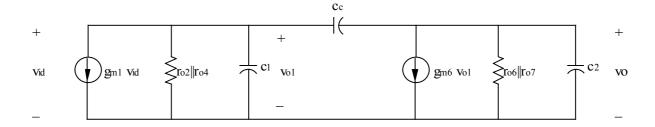

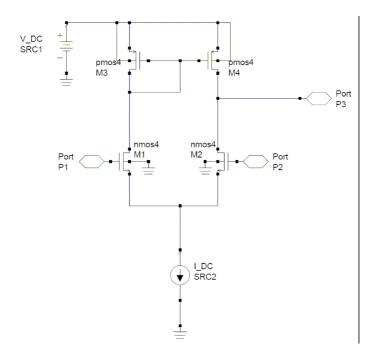

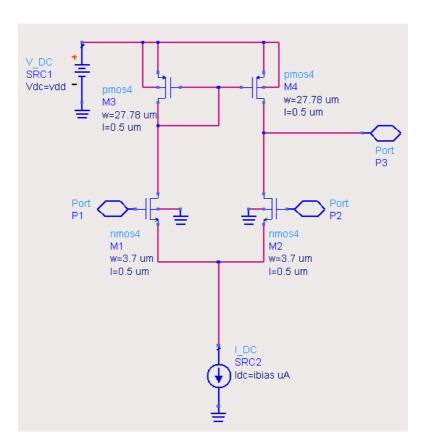

El esquema de la Figura 4.1 muestra un Op-Amp de dos etapas que se divide en:

- Un bloque de polarización.

- Una etapa de entrada diferencial.

- Una etapa de salida.

El bloque de polarización está formado por la fuente de corriente y los transistores  $M_8$  y  $M_5$ . La corriente de polarización es muy importante ya que afecta al funcionamiento del amplificador. La etapa de entrada diferencial la forman los transistores  $M_1$ ,  $M_2$ ,  $M_3$  y  $M_4$  donde  $M_1$  está apareado con  $M_2$  y  $M_3$  está apareado con  $M_4$ . Y, por último, la etapa de salida la forman los transistores  $M_6$  y  $M_7$ .

Figura 4.1 Op-Amp de dos etapas

# 4.2 Etapa de Entrada

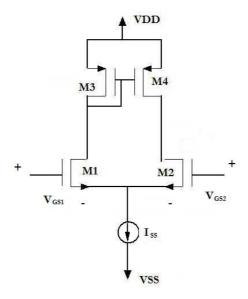

En este apartado estudiaremos la etapa de entrada diferencial que se muestra en la Figura 4.2, donde el transistor  $M_5$  de la Figura 4.1 se ha sustituido por una fuente de corriente  $I_{SS}$ .

Figura 4. 2 Etapa de entrada diferencial

# 4.2.1 CIRCUITOS EQUIVALENTES EN PEQUEÑA SEÑAL

En el análisis de circuitos amplificadores MOSFET, el MOSFET puede sustituirse por su modelo equivalente en pequeña señal visto en el Capítulo 2 que se muestra en la Figura 4.3.

Figura 4. 3 MOSFET tipo N y su equivalente en pequeña señal

Donde:

$$r_o = \frac{|VA|}{I_d} \tag{4.1}$$

$$VA = \frac{1}{\lambda} \tag{4.2}$$

y  $g_m$  es el parámetro de transconductancia del transistor:

$$g_m = K_n \frac{W}{I} (V_{GS} - V_t) \tag{4.3}$$

Por tanto, los parámetros del modelo en pequeña señal $g_m$  y  $r_o$ , dependen de la polarización en DC del transistor.

En pequeña señal, las fuentes ideales de tensión continua se sustituyen por cortocircuitos, esto se debe al hecho de que el voltaje frente a una fuente ideal de tensión continua no cambia y de este modo habrá siempre un voltaje nulo en la señal frente a una fuente de

tensión continua. Además, la señal de corriente de una fuente de corriente continua ideal siempre será nula, de esta forma una fuente de corriente continua ideal puede sustituirse por un circuito abierto.

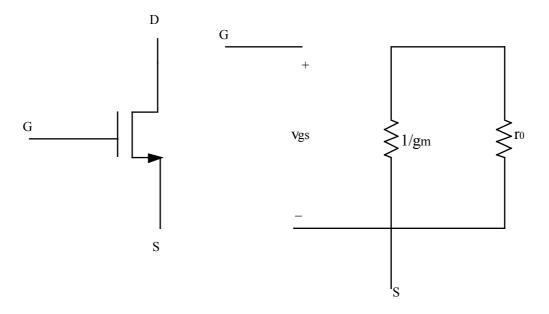

El modelo en pequeña señal para un MOSFET con puerta y drenador cortocircuitados se muestra en la Figura 4.4.

Figura 4. 4 Resistencia MOSFET y su equivalente en pequeña señal

Como

$$v_{ds} = v_{gs}$$

la resistencia efectiva será:  $\frac{v_{gs}}{v_{gs} \cdot g_m} = \frac{1}{g_m}$

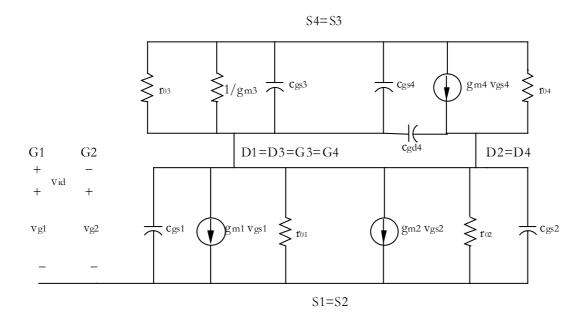

El modelo en pequeña señal de esta etapa diferencial, lo podemos ver en la Figura 4.5, donde si los transistores  $M_1$  y  $M_2$  están perfectamente apareados el punto donde se conectas las fuentes de estos dos transistores se puede considerar tierra en AC. Esto evita que aparezca el efecto de cuerpo (body-effect).

El modelo simplificado de la etapa diferencial se muestra en la Figura 4.6. Dado que  $M_1$  está apareado con  $M_2$  y  $M_3$  con  $M_4$  los nodos S1 y S2 donde se unen  $M_1$  y  $M_2$  se pueden considerar tierra en AC. De la misma forma, dado que, S3 y S4 son tierra en AC, S1, S2, S3 y S4 se pueden unir en un único nodo.

Figura 4. 5 Modelo en pequeña señal de la etapa diferencial

Figura 4. 6 Modelo simplificado de la etapa diferencial

Haciendo referencia a la figura 4.6:

$$C_1 = c_{gd1} + c_{gs3} + c_{gs4} (4.4)$$

$$C_2 = c_{gd2} \tag{4.5}$$

$$C_3 = c_{gd4} \tag{4.6}$$

Cualquier pequeña señal que exista en la puerta de  $M_1$  dará lugar a una corriente en pequeña señal  $i_{d1}$ , que circulará desde el drenador a la fuente de  $M_1$ .

$$i_{d1} = g_{m1} \cdot v_{gs1} \tag{4.7}$$

Esta corriente se refleja de M<sub>3</sub> a M<sub>4</sub>, por lo que:

$$g_{m4} \cdot v_{gs4} = i_{d1} \tag{4.8}$$

Dado que S1, S2, S3 y S4 tienen el mismo potencial (mismo nodo)  $i_{d1}$  también fluirá de la fuente al drenador de  $M_2$ . Por tanto:

$$g_{m2} \cdot v_{gs2} = -i_{d1} \tag{4.9}$$

$$i_{out} = i_{d1} - (-i_{d1}) = 2i_{d1} (4.10)$$

$$r_{out} = r_{o2} \parallel r_{o4} \tag{4.11}$$

$$i_{d1} = g_{m1} \cdot v_{gg} \tag{4.12}$$

Como  $v_{gs1} = v_{gs2}$

$$v_{id} = v_{gs1} + v_{gs2} (4.13)$$

Por tanto,  $v_{id} = 2v_{gs1}$

$$\frac{i_{d1}}{v_{id}} = \frac{g_{m1}v_{gs1}}{2v_{gs}} = \frac{g_{m1}}{2} \tag{4.14}$$

$$v_{id} = \frac{2i_{d1}}{g_{m1}} \tag{4.15}$$

El voltaje de salida en pequeña señal es:

$$v_{out} = i_{out} \cdot r_{out} \tag{4.16}$$

$$v_{out} = 2i_{d1} \cdot (r_{o2} \parallel r_{o4}) \tag{4.17}$$

Si dividimos  $v_{out}$  entre  $v_{id}$  para obtener la ganancia:

$$\frac{v_{out}}{v_{id}} = \frac{2i_{d1}(r_{o2} \parallel r_{o4})}{\frac{2i_{d1}}{g_{m1}}}$$

(4.18)

$$\frac{v_{out}}{v_{id}} = g_{m1,2}(r_{o2} \parallel r_{o4}) \tag{4.19}$$

Además tenemos que:

$$g_{m1,2} = (2\beta_{1,2}I_{D1,2})^{\frac{1}{2}}$$

(4.20)

$$(r_{o2} \parallel r_{o4}) \cong \frac{1}{2\lambda I_{D,2}} \text{ (siendo } r = \frac{1}{\lambda I})$$

(4.21)

Por tanto:

$$\frac{v_{out}}{v_{id}} \cong (2\beta_{1,2}I_{D1,2})^{\frac{1}{2}} \cdot \left[\frac{1}{2\lambda I_{D1,2}}\right]$$

(4.22)

$$\frac{v_{out}}{v_{id}} \cong K \cdot \left[\frac{W_{1,2}}{L_{1,2}I_{D1,2}}\right]^{\frac{1}{2}} \cdot \left(\frac{1}{\lambda}\right) \tag{4.23}$$

Donde K es una constante, que el diseñador no controla. El efecto de  $\lambda$  en la ganancia disminuye cuando L aumenta, así que  $\frac{1}{\lambda}$  es directamente proporcional a la longitud del canal.

Entonces podemos establecer una relación entre  $\frac{W_{1,2}}{L_{1,2}}$  y la corriente de drenador con la ganancia en pequeña señal:

$$\frac{v_{out}}{v_{id}} \propto \left[\frac{W_{1,2}L_{1,2}}{I_{D1,2}}\right]^{\frac{1}{2}} \tag{4.24}$$

La constante no aparece debido a que el valor no es dependiente de algo que el diseñador pueda ajustar.

#### Conclusiones:

- Si incrementamos W<sub>1,2</sub>, L<sub>1,2</sub> o ambos, la ganancia aumenta.

- Si disminuimos la corriente de drenador de M<sub>1</sub> y M<sub>2</sub> la ganancia aumenta.

#### 4.3 Fuentes de Corriente

Una de las partes más importantes de un diseño analógico es la polarización del circuito. El propósito del circuito de polarización es establecer un punto de operación en DC apropiado para el transistor. Con el punto de operación en DC establecido de forma correcta, la corriente de drenador I<sub>D</sub> y la tensión drenador-fuente serán estables y medibles y aseguran la operación en la región de saturación para todas las señales de entrada con las que pueda encontrarse el circuito.

En este apartado estudiaremos cinco tipos diferentes de espejos de corriente; Espejo de Corriente Básico, Espejo de Corriente Cascada/Cascodo, Espejo de Corriente Wilson, Espejo de Corriente Wilson modificado y Espejo de corriente Cascodo Reducido.

La capacidad de un espejo de corriente de mantener la corriente constante, el número de transistores usados y sus tamaños son los factores generales que definen si un espejo de corriente es "bueno" o no. Estos factores deben ser considerados cuando se decide sobre el espejo de corriente que se va a utilizar en el diseño de un Op-Amp.

# 4.3.1 CARACTERÍSTICAS IDEALES DE UN ESPEJO DE CORRIENTE

Un espejo de corriente ideal posee las siguientes cualidades:

- La corriente de salida es función lineal de la corriente de entrada.  $I_{out} = A \cdot I_{in}$ .

- La resistencia de entrada es nula.

- La resistencia de salida es infinita.

Por lo que a la hora de diseñar un espejo de corriente intentaremos que su comportamiento se asemeje al espejo ideal.

# 4.3.2 ANÁLISIS DE UN ESPEJO DE CORRIENTE BÁSICO

En la Figura 4.7 se muestra el espejo de corriente básico, donde el transistor Q<sub>1</sub> está operando en la región de saturación ya que el drenador está cortocircuitado con la puerta.

Figura 4. 7 Espejo de corriente Básico

Por lo tanto:

$$I_{D1} = \frac{1}{2} K_n \left( \frac{W}{L} \right)_1 (V_{GS} - V_t)^2$$

(4.25)

Donde no prestamos atención a la modulación de la longitud del canal y suponemos  $\lambda$ =0.

La corriente de drenador de  $Q_1$  la suministra la tensión de alimentación,  $V_{DD}$ , a través de una resistencia, R. Suponiendo que las corrientes de puerta son aproximadamente cero:

$$I_{D1} = I_{ref} = \frac{V_{DD} - V_{GS}}{R} \tag{4.26}$$

Por otro lado, el transistor  $Q_2$  tiene la misma  $V_{GS}$  que  $Q_1$ , y suponiendo que está en la región de saturación, su corriente de drenador, que es la corriente de salida  $I_0$  de la fuente de corriente será:

$$I_O = I_{D2} = \frac{1}{2} K_n \left(\frac{W}{L}\right)_2 (V_{GS} - V_t)^2$$

(4.27)

Otra vez no prestamos atención a la modulación de la longitud del canal.

Usando las ecuaciones 4.25, 4.26 y 4.27 somos capaces de relacionar la corriente de salida  $I_0$  con la corriente de referencia  $I_{ref}$ .

Reordenando la ecuación 3.26 y sustituyendo  $I_{ref} = I_{D1}$ :

$$\frac{I_{ref}}{\left(\frac{W}{L}\right)_{1}} = \frac{1}{2} K_{n} (V_{GS} - V_{t})^{2}$$

(4.28)

Sabiendo que

$$I_{O} = \left[\frac{1}{2}K_{n}(V_{GS} - V_{t})^{2}\right] \left(\frac{W}{L}\right)_{2}$$

(4.29)

Sustituimos en la ecuación 3.29:

$$I_O = \frac{I_{ref}}{\left(\frac{W}{L}\right)_1} \cdot \left(\frac{W}{L}\right)_2 \tag{4.30}$$

$$\frac{I_O}{I_{ref}} = \frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1} \tag{4.31}$$

Así tenemos una relación de ambas corrientes con la que modificando el ancho y la longitud de los transistores podemos cambiar la corriente de salida.

De este modo si los transistores son iguales, es decir el ancho y la longitud son iguales tenemos:

$$\frac{I_O}{I_{ref}} = 1 \tag{4.32}$$

$$I_O = I_{ref} \tag{4.33}$$

Esto se llama espejo corriente porque la corriente de referencia es "reflejada" a la salida.

# 4.3.3 ESPEJOS DE CORRIENTE ANALIZADOS

### 4.3.3.1 Espejo de Corriente Básico

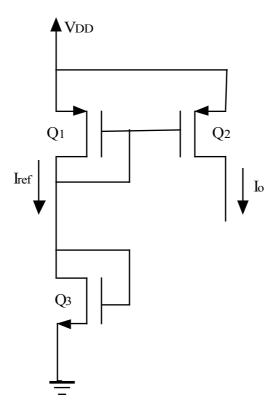

En este apartado examinaremos el espejo de corriente más simple, el Espejo de Corriente Básico (Figura 4.8). Este tipo de espejo de corriente usa un mínimo de tres transistores. El análisis visto anteriormente muestra el funcionamiento general de un espejo de corriente por el que la corriente se mantiene constante para cualquier valor de la tensión de alimentación.

Figura 4. 8 Espejo de Corriente Básico tipo P

En este caso el espejo de corriente lo forman los transistores tipo  $P(Q_1 \ y \ Q_2)$ . Pero, dado que la resistencia ocupa mucho área en los circuitos integrados se ha sustituido por el transistor  $Q_3$  en el que la puerta está conectada al drenador para forzarlo a trabajar en la región de saturación.

La gran ventaja de este circuito es su simplicidad, además de que la corriente que suministra es bastante constante. Sin embargo, presenta dos desventajas importantes: el valor de la corriente de salida no es totalmente estable y su impedancia de salida es bastante baja.

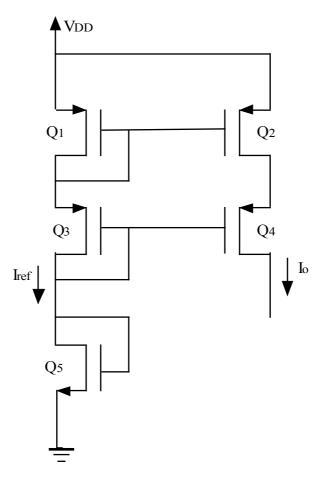

# 4.3.3.2 Espejo de Corriente Cascada/Cascodo

El segundo espejo de corriente que examinamos es el Espejo de Corriente Cascada/Cascodo, este tipo de espejo de corriente usa un mínimo de cinco transistores y su estructura se muestra en la Figura 4.9.

Figura 4. 9 Espejo de Corriente Cascada/Cascodo

El espejo de corriente lo forman los transistores tipo  $P(Q_1, Q_2, Q_3 y Q_4)$  y, por la misma razón que en el caso del espejo de corriente básico se sustituye la resistencia por el transistor  $Q_5$ .

Este circuito es un poco más complejo que el Espejo de Corriente Básico. Su gran problema es que a la hora de suministrar grandes cantidades de corriente su funcionamiento no es del todo bueno, por ejemplo, para suministrar corriente a etapas de salida.

Las grandes ventajas que presenta son: una alta impedancia de salida, una corriente estable y todo esto con un tamaño transistores relativamente pequeño. Sin embargo, la principal desventaja es que su excursión de salida mínima es más alta que la del espejo de corriente básico, y esto reduce la excursión de salida disponible.

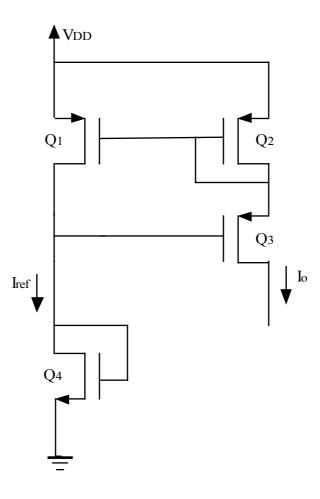

# 4.3.3.3 Espejo de Corriente Wilson

El tercer espejo de corriente que vamos a examinar en este apartado es la fuente de corriente Wilson, que usa un mínimo de cuatro transistores como se observa en la Figura 4.10.

Figura 4. 10 Espejo de Corriente Wilson

Este espejo está formado por los transistores tipo P ( $Q_1$ ,  $Q_2$  y  $Q_3$ ) y como en casos anteriores el transistor  $Q_4$  actúa como una resistencia.

Este circuito es menos complejo que el Espejo de Corriente Cascada/Cascodo y proporciona una corriente, estable debido a la realimentación negativa. Sin embargo, para suministrar la misma cantidad corriente este espejo usa un tamaño de transistores mayor, por lo que este espejo proporciona cualidades similares al Espejo de Corriente Cascada/Cascodo pero usando transistores de mayor tamaño.

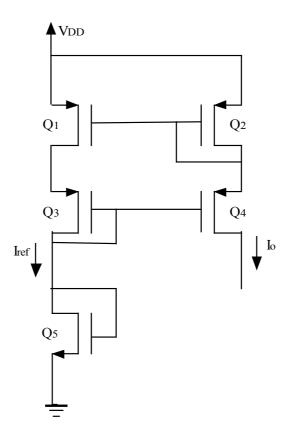

# 4.3.3.4 Espejo de Corriente Wilson Modificado

El cuarto espejo de corriente examinado es el Espejo de Corriente Wilson Modificado. Este espejo de corriente usa un mínimo de cinco transistores y su esquema es similar al Espejo de Corriente Cascada/Cascodo como se muestra en la Figura 4.11. Su rendimiento es similar al Espejo de Corriente Wilson normal.

Figura 4. 11 Espejo de Corriente Wilson Modificado

El espejo de corriente lo forman los transistores tipo  $P(Q_1, Q_2, Q_3 y Q_4) y Q_5$  actuará como resistencia. A diferencia del Espejo de Corriente Wilson normal, este espejo está hecho simétricamente, y la tensión drenador-fuente de  $Q_1$  y  $Q_2$  son iguales.

# 4.3.3.5 Espejo de Corriente Cascodo Reducido

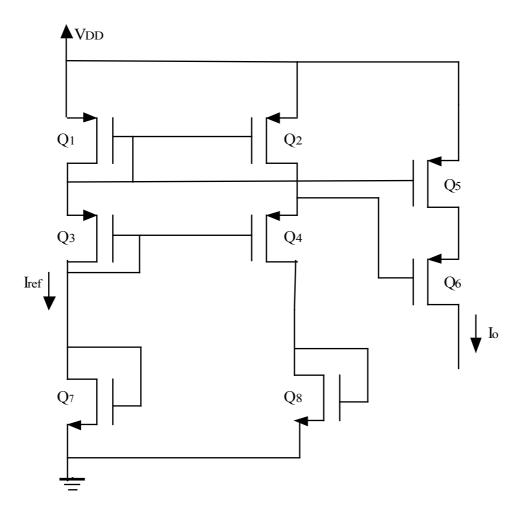

El quinto y último espejo de corriente a examinar es el Espejo de Corriente Cascodo Reducido (Figura 4.12). Este espejo de corriente usa un mínimo de ocho transistores y tiene una topología similar al Espejo de Corriente Cascada/Cascodo básico. La Palabra "Reducido" en el nombre se refiere a que el voltaje con el que la corriente alcanza una salida estable, es alrededor de la mitad del voltaje normal.

Figura 4. 12 Espejo de Corriente Cascodo Reducido

El espejo lo forman los transistores tipo  $P(Q_1, Q_2, Q_3, Q_4, Q_5, y, Q_6)$  y  $Q_7$  y  $Q_8$  actúan como cargas. Este esquema es igual al Espejo de Corriente Cascada/Cascodo pero se le ha añadido un seguidor de fuente  $(Q_2, y, Q_4)$  entre las puertas de  $Q_3, y, Q_6$ . Con esto se consigue disminuir el tamaño de  $Q_3, y, Q_6$  la excursión de salida mínima.

Este espejo de corriente es más complejo que el Espejo de Corriente en Cascada/Cascodo básico. Sin embargo, el Espejo de Corriente en Cascodo Reducido ofrece altas cantidades de corriente con un voltaje bajo que es muy útil en las etapas de salida donde son necesarias corrientes elevadas para polarizarlas.

Las principales ventajas que presenta este tipo de espejo son: proporciona una corriente estable, es capaz de suministrar grandes cantidades de corriente de salida si es necesario, además de, el reducido voltaje con el que la corriente es estable en comparación con el resto de las fuentes de corriente que hemos estudiado.

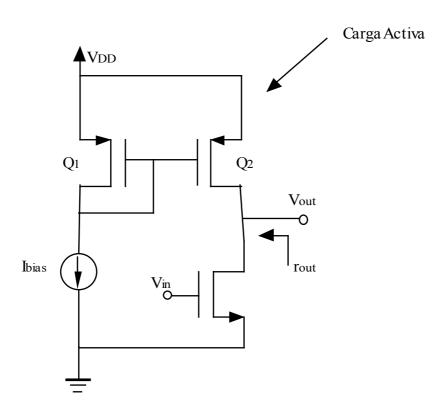

### 4.3.4 FUENTES DE CORRIENTE COMO CARGAS ACTIVAS

Una fuente de corriente además de actuar como circuito de polarización posee una impedancia equivalente en alterna de valor muy alto (teóricamente infinita) y, como la ganancia de la etapa depende de esta resistencia, esto produciría una ganancia infinita. En continua ofrecen mucha corriente. Por tanto, las fuentes de corriente se pueden utilizar como elemento de carga de amplificadores consiguiendo de esta manera cargas de un alto valor resistivo con un área muy inferior con respecto a las resistencias de difusión de ese mismo valor. En la Figura 4.13 se muestra una aplicación de los espejos de corriente como cargas activas en un amplificador de fuente común.

Figura 4. 13 Carga Activa

# 4.4 Etapas de Salida

El principal objetivo de la etapa de salida CMOS es actuar como un convertidor de corriente. La mayoría de las etapas de salida poseen una gran ganancia en corriente y una ganancia pequeña en tensión. Sus objetivos principales son:

- 1. Proporcionar suficiente tensión o corriente. Por ello la etapa de salida debe proporcionar al amplificador una impedancia de salida baja de tal forma que la ganancia de tensión no se vea afectada por el valor de la carga.

- 2. Evitar distorsión en la señal producida por la no linealidad.

- 3. Ser eficiente (entendiendo por eficiencia la relación de la potencia disipada en la carga y la potencia suministrada por la fuente). Esto es minimizar la potencia que disipan los transistores en comparación con la que se disipa en la carga.

- 4. Proporcionar una protección frente a condiciones anormales (cortocircuitos, temperaturas altas, etc.) que podemos encontrar en las etapas de salida CMOS debido a que los transistores MOS están autolimitados.

Una característica importante de esta etapa es que proporciona al amplificador una impedancia de salida baja y con esto el amplificador evita pérdidas de ganancia en la señal de salida. Dado que la etapa de salida es la etapa final del amplificador, normalmente trabaja con señales relativamente grandes y, por tanto, las aproximaciones con el modelo en pequeña señal o cualquier otro modelo no suelen usarse. No obstante, la linealidad permanece como un requisito muy importante, de hecho, una medida de calidad de la etapa de salida es la distorsión armónica total (THD) introducida.

#### 4.4.1 CLASIFICACIÓN DE LAS ETAPAS DE SALIDA

En este apartado veremos varias implementaciones de la etapa de salida. Estas se clasifican según la forma de onda de la corriente de drenador cuando en la entrada aplicamos una señal. Por ejemplo, en un amplificador Clase A, el transistor conduce para todo el ciclo de la señal de entrada, mientras que en un amplificador Clase B, cada transistor conduce para medio ciclo de la señal de entrada, y en un amplificador Clase AB, cada transistor conduce para un intervalo ligeramente mayor que medio ciclo ya que se polarizan a una corriente en

DC mucho más pequeña que el pico de corriente de la señal senoidal y como resultado el ángulo de conducción es mayor que 180° pero mucho menor que 360°.

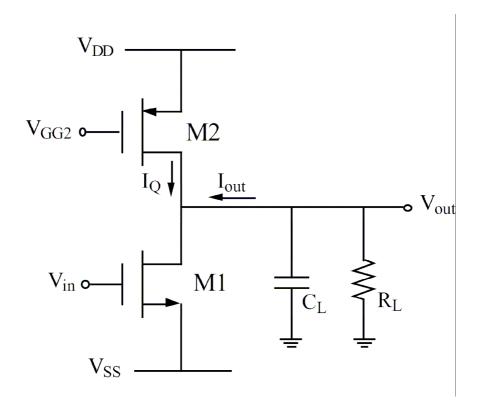

# 4.4.1.1 Etapa de Salida Clase A

Como ya dijimos, en las etapas de salida de Clase A el transistor de salida funciona el 100% del tiempo que tengamos una señal a la entrada. En este apartado veremos dos tipos de estas etapas.

Salida Simple en Fuente Común

El circuito se muestra en la Figura 4.14.

Figura 4. 14 Etapa de Salida Clase A con Salida Simple en Fuente Común

• Salida Simple en Drenador Común (Seguidor de Fuente)

El circuito se muestra en la Figura 4.15 donde observamos que en lugar de usar un transistor tipo P y uno tipo N se usan dos transistores iguales tipo N. Esta configuración presenta una impedancia de salida bastante baja lo que da lugar a una ganancia en corriente elevada. Sin embargo, uno de los principales problemas que presenta es su dependencia con

el body-effect debido a que la fuente es el nodo de salida. El body-effect causa que la tensión umbral  $V_t$  se incremente cuando el voltaje de salida aumenta, causando que el voltaje máximo a la salida sea bastante menor que  $V_{\rm DD}$ .

Figura 4. 15 Etapa de Salida Clase A (Seguidor de Fuente)

La eficiencia del seguidor de fuente es similar al visto anteriormente. Sin embargo, la distorsión del seguidor de fuente será mejor debido a la inherente realimentación negativa. La eficiencia se define como la relación de la potencia disipada en la carga y la potencia suministrada por la fuente de alimentación.

#### Análisis de Eficiencia

Para calcular la eficiencia tratamos de encontrar la relación que existe entre la potencia suministrada a la carga y la consumida por la fuente (sólo por la etapa de salida):

$$E_{ff} = \frac{load\_power(P_L)}{\sup plv\_power(P_S)}$$

(4.34)

Primero calculamos la potencia suministrada a la carga (partiendo de la base de que se está suministrando la máxima potencia) para ello usaremos la fórmula de la potencia eficaz:

$$P_L = V_{ef} \cdot I_{ef} \tag{4.35}$$

En estas etapas si seleccionamos una buena corriente de polarización, I, la tensión de salida puede variar de 0 a  $V_{DD}$  donde el valor máximo absoluto debería ser  $V_{DD}/2$ . Así con esta corriente de polarización permitimos una corriente máxima en la carga de  $\frac{V_{DD}}{2R_L}$ , y la corriente de drenador del transistor de arriba variará de 0 a 2I siendo su valor medio I. Por lo tanto, la máxima potencia instantánea disipada por el transistor de arriba será  $V_{DD} \cdot \frac{I}{2}$  siendo  $\left(I = \frac{V_{DD}}{2R_L}\right)$ .

Con estos datos ya podemos calcular la tensión y la corriente eficaz:

$$V_{ef} = \frac{V_{\text{max}}}{\sqrt{2}} = \frac{V_{DD}}{2\sqrt{2}} \tag{4.36}$$

$$I_{ef} = \frac{I_{\text{max}}}{\sqrt{2}} = \frac{V_{DD}}{2R_L \sqrt{2}} \tag{4.37}$$

Por tanto, la potencia máxima suministrada a la carga es:

$$P_L = \frac{V_{DD}^2}{8R_L} \tag{4.38}$$

Una vez calculada la potencia suministrada a la carga, tenemos que calcular la consumida en la fuente:

$$P_{S} = V_{DD} \cdot I_{media} \tag{4.39}$$

Donde  $I_{\text{media}}$  para suministrar la máxima potencia a la carga es:  $I_{\text{media}} = \frac{V_{DD}}{2R_L}$ .

Por tanto:

$$P_{S} = \frac{V_{DD}^{2}}{2R_{I}} \tag{4.40}$$

Así, la máxima eficiencia posible es:

$$E_{ff}(\%) = \frac{P_L}{P_S} \cdot 100 = 25\%$$

Dado que es una eficiencia bastante baja, la etapa de salida Clase A no suele usarse en aplicaciones de alta energía. Además, hay que tener en cuenta que en la práctica la tensión de salida está limitada a valores más bajos para evitar la saturación de los transistores y la distorsión no lineal. Por ello, la eficiencia suele encontrarse en el rango del 10% al 20%.

# 4.4.1.2 Etapa de Salida Clase B

# Amplificador CMOS Inversor tipo Push-Pull

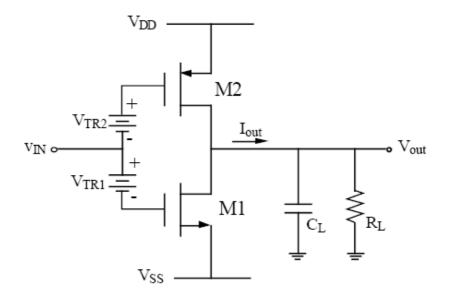

La principal ventaja del amplificador Push-Pull (Figura 4.16) es su elevada eficiencia. Sabemos que un Clase B, amplificador push-pull, tiene una eficiencia máxima del 78.5% que significa que necesitamos menor corriente fija para conseguir las corrientes de salida demandadas. El circuito opera en modo push-pull: cuando en la entrada está el semiciclo positivo, M1 se activa al exceder  $V_{GS}$  la tensión umbral, de la misma forma, cuando en la entrada está el semiciclo negativo se activará M2. Pero hay una "zona muerta" donde ambos transistores están apagados, por lo que no habrá salida, esto provoca una distorsión de cruce. Esta distorsión puede reducirse sustancialmente empleando una ganancia del Op-Amp alta y una realimentación negativa global. Otra opción para reducir esta distorsión es usar un amplificador Clase AB. Además, en este amplificador la excursión de salida está limitada a  $V_{DD}$  menos la tensión umbral y  $V_{SS}$  más la tensión umbral.

Figura 4. 16 Etapa de Salida Clase B

### Análisis de Eficiencia

Para calcular la eficiencia de energía, Eff, de una etapa Clase B, olvidamos la distorsión de cruce y consideramos el caso de una salida sinusoidal con una amplitud de pico  $V_O$ . Así  $P_L = \frac{{V_o}^2}{2R_L}$ . La corriente consumida por cada fuente de alimentación consistirá en media onda de amplitud  $V_O$ . De este modo, la corriente media suministrada por cada fuente de alimentación será  $I_m = \frac{2V_o}{\pi \cdot R_L}$ . Si consideramos que la potencia que se le suministra a la carga es máxima:

$$P_{L} = \frac{V_{DD}^{2}}{2R_{L}} \tag{4.41}$$

Y la potencia consumida por la fuente de alimentación:

$$P_{S} = V_{DD} \cdot I_{m} = \frac{2V_{DD}^{2}}{\pi \cdot R_{L}}$$

(4.42)

Por tanto, la máxima eficiencia posible es:

$$E_{ff}(\%) = \frac{P_L}{P_S} \cdot 100 = \frac{\pi}{4} \cdot 100 = 78.5\%$$

Comprobamos que esta configuración posee una eficiencia mucho mayor que las etapas de Clase A.

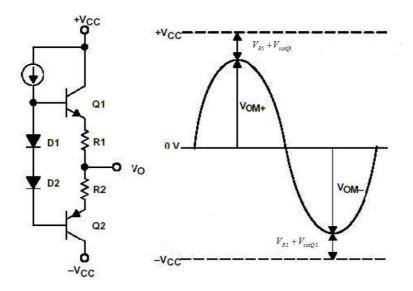

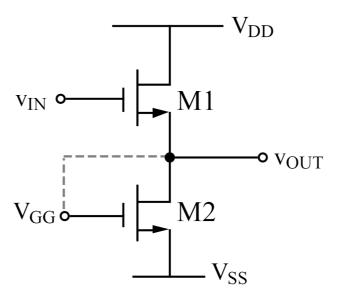

#### 4.4.1.3 Etapa de Salida Clase AB

La distorsión de cruce que introduce la etapa de salida Clase B puede ser minimizada polarizando los transistores de salida complementariamente con una pequeña corriente. El resultado es la etapa de salida Clase AB (ver Figura 4.17). Esta etapa opera prácticamente de la misma manera que el circuito Clase B, con una excepción importante, cuando en la entrada hay una pequeña señal, ambos transistores conducen, y a medida que esta señal aumenta o disminuye, uno de los dos transistores toma posesión de la operación.

Figura 4. 17 Etapa de Salida Clase AB

La implementación de esta etapa se muestra en la Figura 4.18. Su eficiencia será similar a la vista en la etapa de salida Clase B, es decir, su eficiencia máxima será alrededor de un 78.5%.

Figura 4. 18 Implementación de la Etapa de Salida Clase AB

# 4.5 Respuesta en Frecuencia

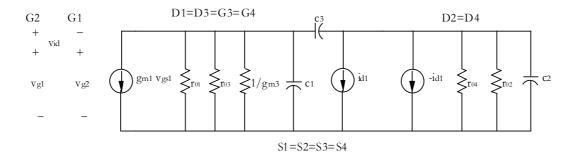

En este apartado nos referiremos de nuevo al modelo de la etapa de entrada de la Figura 4.6. Para simplificar el circuito eliminaremos todos los nodos de baja impedancia, es decir, aquellos que presenten una constante de tiempo RC alta y que, por tanto, generen polos a muy alta frecuencia.

Si suponemos que:

$$\frac{1}{c_1 \cdot \frac{1}{g_{m3}}} >> \frac{1}{\left[c_2 \cdot (r_{o2} \parallel r_{o4})\right]}$$

(4.43)

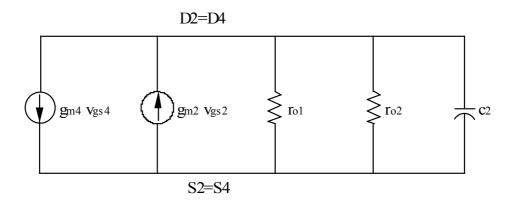

Entonces el nodo (D1=D2=G3=G4) es un nodo de baja impedancia y, por tanto, lo podemos eliminar. Otra suposición que se suele hacer es que  $c_3$ =0, lo que resulta ser válido en muchas aplicaciones de amplificadores diferenciales. Por tanto, el modelo que vamos a tener en cuenta para el análisis en alta frecuencia es el que se muestra en la figura 4.19.

En la configuración en la que se aplica una pequeña señal a la puerta de  $M_1$  mientras la puerta de  $M_2$  está conectada a tierra,  $v_{gs2}=0$ ,  $v_{id}=v_{gs1}$ . Entonces:

$$g_{m4}v_{gs4} = i_{d1} = g_{m1}v_{gs1} = g_{m1}v_{id}$$

(4.44)

Figura 4. 19 Modelo en pequeña señal de alta frecuencia con capacidades parásitas

Esto nos permite redibujar el modelo de la figura 4.6 quedándonos uno mucho más simple (Figura 4.20).

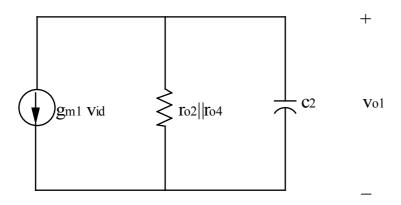

Figura 4. 20 Modelo en pequeña señal de la etapa de entrada usado para determinar la respuesta en frecuencia

Donde la salida en alta frecuencia viene dada por:

$$v_{o1} = g_{m1}v_{id} \cdot (r_{o2} \parallel r_{o4}) \cdot \frac{1}{\left[1 + S \cdot \frac{1}{c_2(r_{o2} \parallel r_{o4})}\right]}$$

(4.45)

Y la respuesta en frecuencia será:

$$\frac{v_{o1}}{v_{id}} = g_{m1} \cdot (r_{o2} \parallel r_{o4}) \cdot \frac{1}{\left[1 + S \cdot \frac{1}{c_2(r_{o2} \parallel r_{o4})}\right]}$$

(4.46)

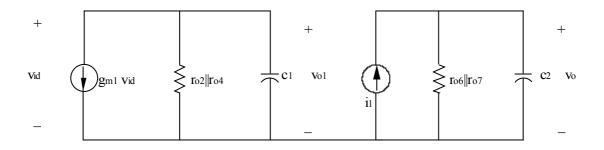

Ahora analizamos la etapa de entrada y de salida vistas en la Figura 4.1.

En un primer análisis el condensador de compensación,  $C_C$ , no se tiene en cuenta. Así,  $c_1$  y  $c_2$  representan las capacidades totales del nodo de salida del par diferencial y del nodo de salida de la etapa de salida. Dado que ambos nodos son de alta impedancia, tendremos que tenerlos en cuenta.

En la Figura 4.21 se muestra el modelo derivado de la Figura 4.1 haciendo uso de la Figura 4.20 para determinar la respuesta en frecuencia del Op-Amp de dos etapas.

Para determinar el valor exacto de  $c_1$  y  $c_2$ , la figura 4.22 muestra todas las capacidades parásitas de la etapa de entrada y de la de salida que incluye las capacidades de las zonas de deplexión ( $c_{gb}$ ,  $c_{sb}$ ,  $c_{db}$ ) y las capacidades de solapamiento ( $c_{gs}$ ,  $c_{gd}$ ).

Figura 4. 21 Modelo usado para determinar la respuesta en frecuencia del Op-Amp de dos etapas

Para determinar el efecto del condensador,  $c_{gd6}$ , conectado de la puerta al drenador de  $M_6$  usamos el teorema de Miller. Este teorema aproxima los efectos del condensador puerta-drenador reemplazándolo por un condensador equivalente de entrada de valor  $c_{gd}(1+A_2)$  y un condensador equivalente de salida de valor  $c_{gd}(1+\frac{1}{A_2})$ . Donde  $A_2$  es la ganancia entre los nodos en los que estaba conectado el condensador original. Su valor, según la Figura 4.21 es:

Figura 4. 22 Op-Amp de dos etapas con las capacidades parásitas

$$A_2 = \frac{v_o}{v_{o1}} = -g_{m6} \cdot v_{o1} \frac{r_{o6} \parallel r_{o7}}{v_{o1}}$$

(4.47)

$$A_2 = -g_{m6}(r_{o6} \parallel r_{o7}) \tag{4.48}$$

De este modo c<sub>1</sub> y c<sub>2</sub> para la Figura 4.21 pueden calcularse examinando la Figura 4.22.

$$c_1 = c_{db4} + c_{gd4} + c_{db2} + c_{gd2} + c_{gs6} + c_{gd6} \cdot (1 + A_2)$$

(4.49)

$$c_2 = c_{db6} + c_{db7} + c_{gd7} + c_{gd6} \cdot \left(1 + \frac{1}{A_2}\right) + c_L \tag{4.50}$$

Si suponemos que  $c_1 < c_2$ , el polo asociado con la salida del amplificador diferencial  $\left(\frac{1}{c_1(r_{o2} \parallel r_{o4})}\right)$  será más bajo en frecuencia que el polo asociado a la salida de la etapa de salida  $\left(\frac{1}{c_2(r_{o6} \parallel r_{o7})}\right)$ .

Además del modelo de alta frecuencia de la Figura 4.21 tenemos:

$$\frac{v_o}{v_{id}} = \left[\frac{v_o}{v_{o1}}\right] \cdot \left[\frac{v_{o1}}{v_{id}}\right] \cdot \left[\frac{1}{1 + \frac{s}{c_2(r_{o6} \parallel r_{o7})}}\right] \cdot \left[\frac{1}{1 + \frac{s}{c_1 \cdot (r_{o2} \parallel r_{o4})}}\right]$$

(4.51)

$$\frac{v_o}{v_{o1}} = g_{m6} \cdot (r_{o6} \parallel r_{o7}) \frac{1}{\left(1 + \frac{s}{c_2 \cdot (r_{o6} \parallel r_{o7})}\right)}$$

(4.52)

$$\frac{v_{o1}}{v_{id}} = g_{m1} \cdot (r_{o2} \parallel r_{o4}) \frac{1}{\left(1 + \frac{s}{c_1 \cdot (r_{o2} \parallel r_{o4})}\right)}$$

(4.53)

Por tanto, la respuesta en frecuencia es:

$$\frac{v_o}{v_{id}} = \left[g_{m6} \cdot (r_{o6} \parallel r_{o7})\right] \cdot \left[g_{m1} \cdot (r_{o2} \parallel r_{o4})\right] \cdot \left[\frac{1}{1 + \frac{s}{c_1 \cdot (r_{o2} \parallel r_{o4})}}\right] \cdot \left[\frac{1}{1 + \frac{s}{c_2 \cdot (r_{o6} \parallel r_{o7})}}\right]$$

(4.54)

Donde los polos se corresponden con:

$$P_1 = \frac{1}{c_1 \cdot (r_{o2} \parallel r_{o4})} \tag{4.55}$$

$$P_2 = \frac{1}{c_2 \cdot (r_{o6} \parallel r_{o7})} \tag{4.56}$$

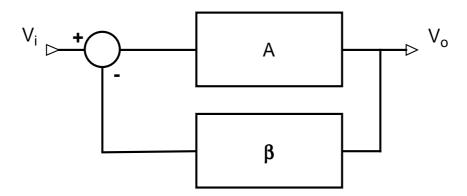

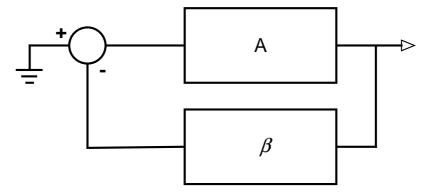

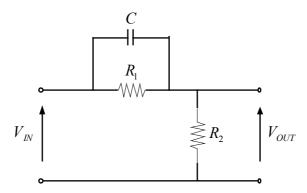

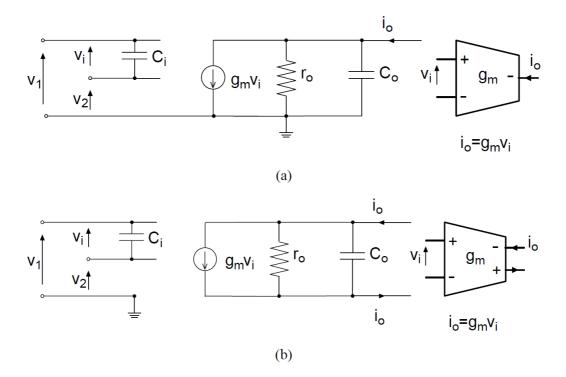

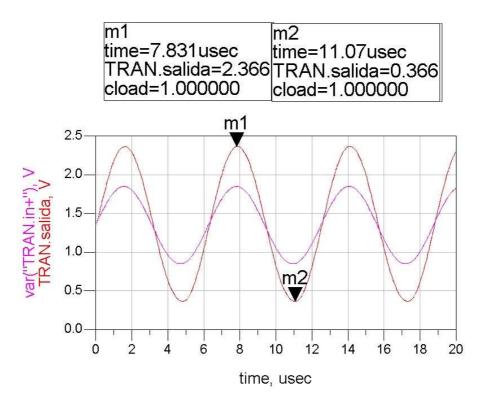

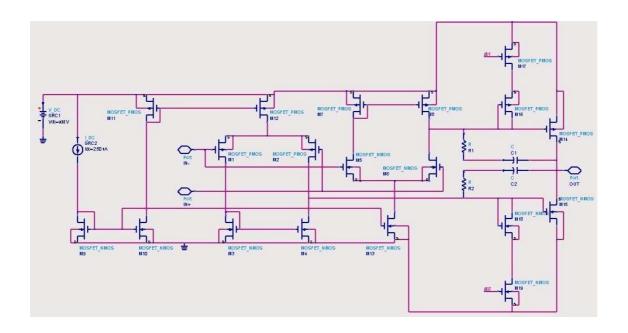

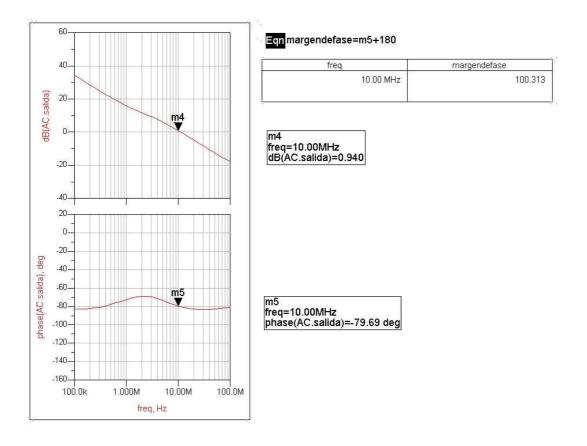

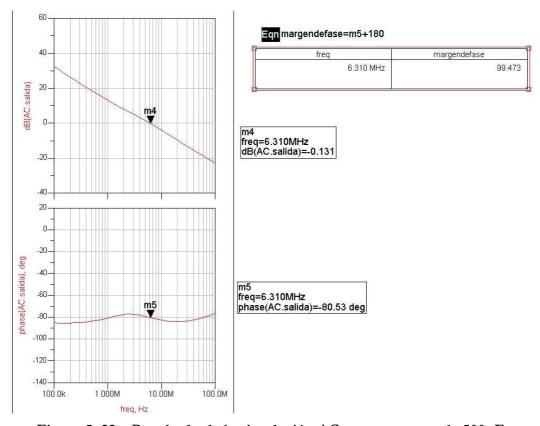

# 4.6 Realimentación y Compensación