A modular approach for the compression of payload information on-board satellites

**Yubal Barrios Alfaro**

Las Palmas de Gran Canaria, May 2022

#### Abstract

The integration on-board satellites of high-resolution sensors, such as spectroscopic or video sensors, is becoming common in the space industry. These sensors provide a large amount of information about the observed scene that is difficult to handle on-board, because satellites have limited computational and storage resources. For these reasons, on-board data compression is becoming mandatory for future space missions integrating this kind of high-resolution sensors. At the same time, compression algorithms must meet some requirements specifically imposed by the space environment, such as low complexity, low power consumption or robustness to errors due to radiation, among others. This makes challenging both to develop specific compression techniques for space missions and also to implement them in electronic devices that must be qualified to work in the outer space.

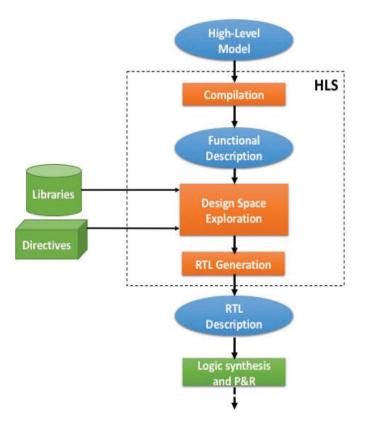

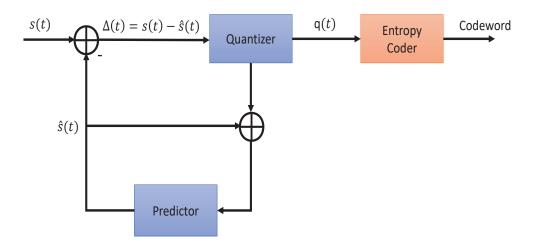

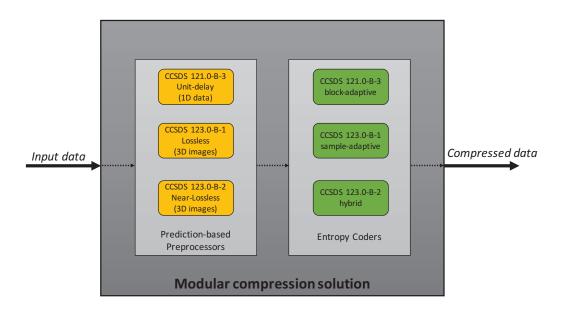

This Thesis proposes new modular hardware solutions for the compression of generic data and hyperspectral images on-board satellites. The goal is to provide several alternatives of prediction-based preprocessors and entropy coders, which are the two main stages of a compressor, that can be combined by the user. In this way, the optimal solution for the final application can be selected depending on certain requirements, such as target compression ratio, data quality after decompression, computational performance, hardware occupancy or robustness against radiation-induced failures. The implementation of the different prediction-based preprocessors and entropy coding alternatives is carried out on FPGAs, which are becoming popular in the space industry due to their high computational capabilities, low power consumption and the possibility of being reconfigured during the mission lifetime, either to add new functionality or to repair errors caused by radiation. Implementation results are provided for two recently available radiation tolerant FPGA technologies, the BRAVE and Kintex UltraScale families, manufactured by NanoXplore and Xilinx, respectively. Two different design methodologies have been combined, RTL (using VHDL) and HLS, choosing one or the other depending on certain constraints, such as computational performance requirements, logic resource utilization or design time restrictions, among others.

Concerning algorithms, this Thesis focuses on the compression algorithms proposed by CCSDS, an international organism in charge of publishing standards to be used in onboard processing systems for space missions. For generic data compression, the CCSDS 121.0-B-3 lossless compression standard is proposed, while the CCSDS 123.0-B-1 and CCSDS 123.0-B-2 standards are considered for the lossless and near-lossless compression, respectively, of multi- and hyperspectral images. These compression standards have been studied in detail, in order to detect existing data dependencies between internal tasks and how to solve them. In this way, it is possible to parallelize certain computations of the algorithm, which are then executed concurrently thanks to the possibilities offered by FPGAs.

A fully compliant solution with the CCSDS 121.0-B-3 standard (i.e., unit-delay predictor plus block-adaptive entropy encoder), has been developed in VHDL and successfully mapped on the Xilinx Kintex UltraScale XCKU040 FPGA, obtaining a throughput of 176.3 and 163.7 MSamples/s when the input samples have a bit-depth of 8 and 16 bits, respectively. This performance enables real-time processing for spectroscopic sensors currently in orbit and for those planned for launch in the short to medium term. This computational performance is achieved with a low area footprint, using only 4.2% of the LUTs available on the device and with a minimum memory consumption (around 0.8%).

Regarding the CCSDS 123.0-B-1 lossless standard, it has also been completely developed in VHDL and is comprised by both the 3D predictor defined in the standard and the sample-adaptive encoder. Different architectures have been developed for the prediction stage, taking into account data dependencies in the processing of each possible order of the input image, with the aim of maximising the throughput without significantly affecting logic resource utilization. When the input order is Band-Interleaved by Pixel (BIP), the only one that allows processing of one sample per clock cycle, a maximum throughput of 151.6 MSamples/s is obtained for the XCKU040 FPGA, when compressing scenes acquired by AVIRIS, which have a precision of 16 bits per pixel. Logic resource consumption is considerably low (around 3% of the total LUTs available on the device), while the memory consumption depends directly on the image size (e.g., 12 % of BRAMs of the XCKU040 FPGA are used for AVIRIS scenes).

The CCSDS 123.0-B-2 near-lossless algorithm has been fully developed in HLS to quickly perform a design space exploration of the different predictor architectures, while at the same time the existing restrictions in terms of available design time are overcome. A design space exploration has been carried out to know which parts of the algorithm are the most critical in terms of achieved compression ratio and hardware occupancy. The impact of the different configuration parameters defined by the standard on the performance of the hardware implementation has also been studied. This solution consumes the 7.2% of LUTs and 14.2% of BRAMs available on the Kintex UltraScale XCKU040. A tailored version of this approach was made for the CHIME instrument, composed of just the

CCSDS 123.0-B-2 predictor features that allow the highest possible compression ratio, and the block-adaptive encoder. This approach, although it is not capable of providing real-time compression, has an acceptable hardware footprint (the 6.0% of LUTs and 28.5% of BRAMs available on the Xilinx XCKU040 FPGA). As it can be seen from the results obtained, the proposed implementations are feasible to be successfully implemented on hardware available on-board satellites.

Finally, as part of this Thesis, the application of the CCSDS 123.0-B-2 algorithm for monochromatic and RGB video compression has been evaluated, demonstrating the versatility of the proposed modular compression solution, capable of compressing both threedimensional images and video sequences by using a single processing core. This solution provides acceptable compression ratios for a real Remote Sensing scenario, obtaining a video quality after decompression high enough to not perceive significant losses from a visual point of view.

In conclusion, this work presents efficient compression solutions capable of handling different types of data, including one-dimensional data, hyperspectral imagery and video sequences, which can be embarked on-board satellites in future space missions. In this way, flexible and high-performance compression approaches are provided, all with a low use of computational and memory resources.

### Resumen

La integración a bordo de satélites de sensores de alta resolución, como pueden ser sensores hiperspectrales o de vídeo, es cada vez más común por parte de la industria espacial. Estos sensores proporcionan una gran cantidad de información acerca de la escena observada que es difícil de manejar a bordo, debido a que los satélites cuentan con recursos tanto computacionales como de almacenamiento limitados. Por estas razones, la compresión a bordo de satélites se está convirtiendo en una necesidad para futuras misiones espaciales que integren sensores de alta resolución. Al mismo tiempo, los algoritmos de compresión deben cumplir una serie de requisitos impuestos específicamente por el entorno espacial, como puede ser una baja complejidad, un reducido consumo de potencia o robustez frente a errores debido a la radiación, entre otros. Todo esto hace que suponga un reto tanto el desarrollo de técnicas de compresión específicas para misiones espaciales como su implementación en dispositivos electrónicos que deben estar calificados para trabajar en el espacio.

En esta Tesis se proponen nuevas soluciones hardware modulares para la compresión de datos genéricos e imágenes hiperespectrales a bordo de satélites. La idea fundamental radica en proporcionar varias alternativas de preprocesadores basados en predicción y de codificadores entrópicos, que son las dos etapas básicas de que consta un compresor, pudiendo ser combinadas por el usuario. De esta forma, se podrá seleccionar la opción óptima para la aplicación final dependiendo de determinados requisitos, como puede ser compresión objetivo, calidad de los datos después de la decompresión, prestaciones temporales, ocupación en términos de área, o robustez frente a fallos provocados por la radiación. Concretamente, dichas implementaciones se llevan a cabo en FPGAs, dispositivos electrónicos que están adquiriendo cada vez más interés por parte de la industria espacial debido a sus altas capacidades computacionales, reducido consumo de potencia y posibilidad de ser reconfiguradas durante el ciclo de vida de la misión, bien para añadir nueva funcionalidad o para reparar errores producidos por la radiación. En este sentido, cabe destacar que se proporcionan resultados para dos tecnologías FPGA tolerantes a la radiación recientemente disponibles en el mercado, como son las familias BRAVE y Kintex UltraScale, proporcionadas por los fabricantes NanoXplore y Xilinx, respectivamente. Dos diferentes metodologías de diseño han sido combinadas, RTL (utilizando VHDL) y HLS, eligiendo una u otra en función de ciertas restricciones, como pueden ser requisitos de rendimiento computacional, de utilización de recursos lógicos o limitaciones en el tiempo de diseño, entre otras.

En lo que a algoritmos se refiere, se presta especial atención a los estándares de compresión propuestos por el CCSDS, organismo encargado de publicar normas para ser empleadas en los sistemas de procesamiento a bordo de misiones espaciales. Para la compresión de datos genéricos, se propone el empleo del estándar de compresión sin pérdidas CCSDS 121.0-B-3, mientras que los estándares CCSDS 123.0-B-1 y 123.0-B-2 se consideran para la compresión de imágenes multi- e hiperspectrales sin o con pérdidas, respectivamente. Ambos estándares de compresión han sido profundamente estudiados, para poder detectar las dependencias de datos existentes entre tareas internas y cómo solucionarlas. De este modo, se consigue paralelizar ciertos cómputos del algoritmo, que son ejecutados concurrentemente gracias a las posibilidades ofrecidas por las FPGAs.

Se ha desarrollado en VHDL una solución conforme al estándar CCSDS 121.0-B-3 (*unitdelay predictor* más *block-adaptive encoder*), mapeado satisfactoriamente en la FPGA Kintex UltraScale XCKU040 de Xilinx, obteniendo un *throughput* de 176.3 y 163.7 MSamples/s cuando las muestras de entrada tienen una precisión de 8 y 16 bits, respectivamente. Estas prestaciones temporales permiten un procesamiento en tiempo real para los sensores hiperespectrales que se encuentran actualmente en órbita y para los que está previsto lanzar a corto o medio plazo. Este rendimiento computacional está unido a una baja ocupación de área, usando únicamente un 4.2% de las LUTs disponibles en el dispositivo y con un consumo de memoria prácticamente nulo (alrededor del 0.8%).

Respecto al estándar CCSDS 123.0-B-1, también ha sido completamente desarrollado en VHDL y está compuesto tanto por el predictor 3D definido en el estándar, como por el *sample-adaptive encoder*. Diferentes arquitecturas han sido desarrolladas para la etapa de predicción, teniendo en cuenta las dependencias de datos existentes en el procesamiento de cada orden posible de la imagen de entrada, con el objetivo de maximizar el *throughput* sin que la ocupación de recursos lógicos se vea significativamente afectada. Cuando el orden de entrada es *Band-Interleaved by Pixel* (BIP), el único que permite un procesamiento de una muestra por ciculo de reloj, se obtiene un *throughput* máximo de 151.6 MSamples/s para la FPGA XCKU040, cuando se comprimen escenas adquiridas por AVIRIS, que tienen una precisión de 16 bits por píxel. La utilización de recursos lógicos es considerablemente baja (alrededor del 3% del total de LUTs disponible en el dispositivo), mientras que el consumo de memoria depende directamente del tamaño de la imagen (por ejemplo, se utiliza el 12% de BRAMs de la FPGA XCKU040 para escenas adquiridas por AVIRIS).

El algoritmo descrito en el estándar CCSDS 123.0-B-2 se ha desarrollado completamente en HLS para realizar una exploración rápida del espacio de diseño y estudiar las diferentes arquitecturas posibles del predictor, mientras que al mismo tiempo se evitan las restricciones existentes en cuanto a tiempo de diseño disponible. Se ha realizado una exploración del espacio de diseño para identificar qué partes del algoritmo son más críticas en términos de ratio de compresión y utilización del hardware. También se ha estudiado el impacto de los diferentes parámetros de configuración definidos en el estándar en el rendimiento de la implementación hardware. Esta solución consume el 7% de LUTs y el 14.2% de BRAM disponibles en la Kintex UltraScale XCKU040. Se ha realizado una versión a medida de esta solución para el instrumento del programa espacial CHIME, compuesta por la funcionalidad del predictor propuesto en el estándar CCSDS 123.0-B-2 que permitía alcanzar un mayor ratio de compresión, y el *block-adaptive encoder*. Esta solución, aunque no es capaz de proporcionar compresión en tiempo real, tiene una ocupación de hardware comedida (el 6% de LUTs y el 28.5% de BRAMs disponibles en la FPGA XCKU040 de Xilinx). Como se puede comprobar a partir de los resultados obtenidos, las implementaciones propuestas son viables para ser implementadas satisfactoriamente en hardware disponible a bordo de satélites.

Adicionalmente, se ha evaluado el uso del algoritmo CCSDS 123.0-B-2 para la compresión de vídeo monocromático y RGB, obteniendo de esta forma una solución de compresión versátil, capaz de comprimir tanto imágenes tridimensionales como secuencias de vídeo obteniendo un único núcleo de procesamiento. Esta solución proporciona ratios de compresión aceptables para un escenario real de teledetección, obteniendo una calidad de vídeo después de la decompresión lo suficientemente alta para no percibir pérdidas significativas desde un punto de vista visual.

En definitiva, este trabajo proporciona soluciones de compresión eficientes capaces de manejar diferentes tipos de datos, incluyendo datos unidimensionales, imágenes hiperespectrales y vídeo, que puedan ser embarcadas a bordo de satélites en futuras misiones espaciales. De esta forma, se dota a la misión espacial de técnicas de compresión flexibles y de alto rendimiento, y todo ello con un bajo uso de recursos computacionales y de memoria.

### Acknowledgements

The development of this Thesis has not been an easy journey and it would have been practically impossible to finish it without the support of countless people who have been part of my professional and personal life during the last four years. First of all, I would like to express my gratitude to my supervisors, Prof. Roberto Sarmiento and Dr. Lucana Santos, who have supported and guided me during this research, always providing constructive comments from their experience in the field. During these four years, I have been part of the Institute for Applied Microelectronics (IUMA), research centre associated to the University of Las Palmas de Gran Canaria (ULPGC). As part of the IUMA team, I have involved in different European and ESA-funded projects, which have contributed to support with funding my PhD, whose research topics are clearly connected to the work done in those projects.

I also thank the European Space Agency for offering me the opportunity to make an international research stay in their facilities at the European Space Research and Technology Centre (ESTEC) located in Noordwijk, the Netherlands. I would like to thank all the TEC-EDM section for their hospitality during those three months and for sharing with me a valuable knowledge about the status of the European space industry in the short- and near-future. I am also grateful to people from Thales Alenia Space in Spain and in France, whose I have collaborated in different space programs during the past four years.

I cannot forget to thank my colleagues of the DSI Lab for easing the coexistence in the professional environment and also for the enriching discussions, the innumerable anecdotes out of work and of course for their patience in some stressful moments. If I had the possibility to come back to the beginning of my PhD to choose my teammates, needless to say that I would choose them.

Finally, but not less important, I am infinitely grateful to the most important people of my life, whose are of course my parents, for their generous support and the way they educate me, which has made me the person that I am. Thanks also to Laura for being my life partner and for always believing in me.

## Contents

| Abstract         | i   |

|------------------|-----|

| Resumen          | v   |

| Acknowledgements | ix  |

| List of Figures  | XV  |

| List of Tables   | xix |

| Abbreviations    | xxi |

| 1 | Intr | oducti | on                                                                  | 1  |

|---|------|--------|---------------------------------------------------------------------|----|

|   | 1.1  | Motiva | ution                                                               | 2  |

|   | 1.2  | Applic | ation environment constraints                                       | 6  |

|   |      | 1.2.1  | Hardware on-board satellites                                        | 7  |

|   |      | 1.2.2  | Design methodology                                                  | 10 |

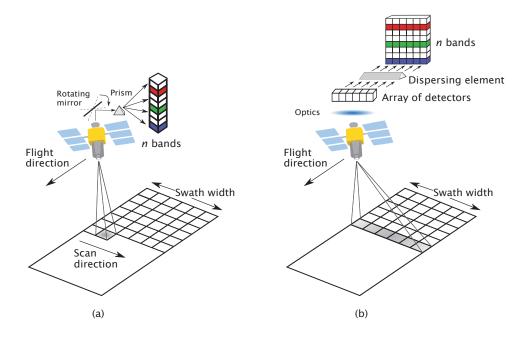

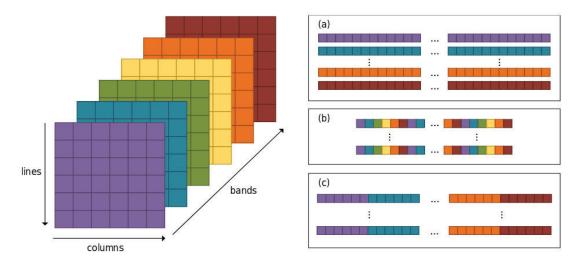

|   |      | 1.2.3  | Hyperspectral sensors and image formats                             | 12 |

|   |      | 1.2.4  | Real-time video acquisition on satellites                           | 15 |

|   | 1.3  | On-boa | ard data compression                                                | 16 |

|   | 1.4  | Thesis | framework                                                           | 18 |

|   | 1.5  | Object | ives of the Thesis                                                  | 20 |

|   | 1.6  | Docum  | nent structure                                                      | 21 |

|   |      | 1.6.1  | Chapter 2: Satellite data compression algorithms and their hardware |    |

|   |      |        | implementation                                                      | 22 |

|   |      | 1.6.2  | Chapter 3: FPGA implementations of prediction-based preprocessors   |    |

|   |      |        | for data decorrelation                                              | 22 |

|   |      | 1.6.3  | Chapter 4: Low-complexity hardware solutions for                    |    |

|   |      |        | entropy coding                                                      | 22 |

|   |      | 1.6.4  | Chapter 5: Modular solutions for on-board data                      |    |

|   |      |        | compression                                                         | 23 |

| Contents |

|----------|

|----------|

|          |      | 1.6.5  | Chapter 6: Conclusions                                                                          | 23       |

|----------|------|--------|-------------------------------------------------------------------------------------------------|----------|

| <b>2</b> |      |        | lata compression algorithms and their hardware implementa-                                      |          |

|          | tion |        |                                                                                                 | 25       |

|          | 2.1  |        | 1e                                                                                              | 26       |

|          | 2.2  |        | imensional data compression algorithms                                                          | 26       |

|          | 2.3  |        | spectral image compression                                                                      | 29       |

|          |      | 2.3.1  | Prediction-based algorithms                                                                     | 30       |

|          |      | 2.3.2  | Transform-based solutions                                                                       | 32       |

|          | 2.4  | Video  | compression                                                                                     | 35       |

|          | 2.5  | Physic | cal implementations for on-board data                                                           |          |

|          |      | compr  | ession                                                                                          | 39       |

|          |      | 2.5.1  | Software-based                                                                                  | 40       |

|          |      | 2.5.2  | Hardware-based                                                                                  | 42       |

|          |      |        | 2.5.2.1 FPGAs                                                                                   | 42       |

|          |      |        | 2.5.2.2 ASICs                                                                                   | 46       |

|          | 2.6  | Conclu | usions                                                                                          | 47       |

| 3        | Des  | ign an | d characterization of prediction-based preprocessing blocks                                     | 49       |

|          | 3.1  | 0      | 1e                                                                                              | 50       |

|          | 3.2  |        | S 121.0-B-3 unit-delay predictor $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 51       |

|          | -    | 3.2.1  | Algorithm overview                                                                              | 51       |

|          |      | 3.2.2  | Block design                                                                                    | 53       |

|          |      | 3.2.3  | Block characterization                                                                          | 54       |

|          | 3.3  |        | S 123.0-B-1 spectral and spatial decorrelator for HSI lossless compression                      |          |

|          | 0.0  | 3.3.1  | Algorithm overview                                                                              | 56       |

|          |      | 3.3.2  | Block design                                                                                    | 59       |

|          |      | 0.0.2  | 3.3.2.1 BIP architecture                                                                        | 62       |

|          |      |        | 3.3.2.2 BSQ architecture                                                                        |          |

|          |      |        | 3.3.2.3 BIL architecture                                                                        | 65       |

|          |      | 3.3.3  | Block characterization                                                                          | 66       |

|          | 3.4  | 0.0.0  | OS 123.0-B-2 spectral and spatial decorrelator for HSI near-lossless                            | 00       |

|          | 0.4  |        | ession                                                                                          | 69       |

|          |      | -      |                                                                                                 |          |

|          |      | 3.4.1  | Algorithm overview                                                                              | 69<br>72 |

|          |      | 3.4.2  | Block design                                                                                    | 73       |

|          | 0.5  | 3.4.3  | Block characterization                                                                          | 78       |

|          | 3.5  | Conclu | usions                                                                                          | 81       |

| 4        | Des  | -      | d characterization of entropy coding blocks                                                     | 83       |

|          | 4.1  | Outlin | ne                                                                                              | 84       |

|          | 4.2  | CCSD   | S 121.0-B-3 block-adaptive encoder                                                              | 85       |

|          |      | 4.2.1  | Algorithm overview                                                                              | 85       |

|          |      | 4.2.2  | Block design                                                                                    | 87       |

|          |      | 4.2.3  | Block characterization                                                                          | 89       |

|   | 4.3          | CCCD           | C 1920 D 1 comple adaptive encoder                                                                | 91  |

|---|--------------|----------------|---------------------------------------------------------------------------------------------------|-----|

|   | 4.0          |                | S 123.0-B-1 sample-adaptive encoder                                                               |     |

|   |              | 4.3.1          | Algorithm overview                                                                                |     |

|   |              | 4.3.2          | Block design                                                                                      |     |

|   | 4 4          | 4.3.3          | Block characterization                                                                            |     |

|   | 4.4          |                | S 123.0-B-2 hybrid encoder                                                                        |     |

|   |              | 4.4.1          | Algorithm overview                                                                                |     |

|   |              | 4.4.2          | Block design                                                                                      |     |

|   |              |                | 4.4.2.1 High-entropy unit                                                                         |     |

|   |              |                | 4.4.2.2 Low-entropy unit                                                                          |     |

|   |              | 4.4.3          | Block characterization                                                                            |     |

|   | 4.5          | Conclu         | usions                                                                                            | 102 |

| 5 | Мо           | dular e        | solutions for on-board data compression                                                           | 103 |

| J | 5.1          |                |                                                                                                   |     |

|   | $5.1 \\ 5.2$ |                | tion scenarios $\ldots$                                                                           |     |

|   | $5.2 \\ 5.3$ |                | ss one-dimensional data and image                                                                 | 100 |

|   | 0.0          |                |                                                                                                   | 106 |

|   |              | 5.3.1          | System development                                                                                |     |

|   |              | 5.3.2          | Experimental results                                                                              |     |

|   |              | 5.3.2          | Demonstrator set-up                                                                               |     |

|   | 5.4          |                | ss hyperspectral image compression                                                                |     |

|   | 0.4          | 5.4.1          |                                                                                                   |     |

|   |              | 5.4.1<br>5.4.2 | System development                                                                                |     |

|   |              |                | Experimental results                                                                              |     |

|   |              | 5.4.3          | Comparison with state-of-the-art implementations                                                  |     |

|   | 5.5          |                | ossless hyperspectral image compression                                                           | 125 |

|   |              | 5.5.1          | Compression solution fully compliant with the CCSDS 123.0-B-2                                     | 196 |

|   |              |                | standard                                                                                          |     |

|   |              |                | 5.5.1.1 System development $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                  |     |

|   |              |                | 5.5.1.2 Experimental results                                                                      |     |

|   |              |                | 5.5.1.3 Demonstrator set-up $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                          |     |

|   |              | <b>F F</b> 0   | 5.5.1.4 Evaluation of the HLS approach                                                            | 131 |

|   |              | 5.5.2          | Compression solution based on the CCSDS 123.0-B-2                                                 | 190 |

|   |              |                | standard for CHIME                                                                                |     |

|   |              |                | 5.5.2.1 Parameter tuning                                                                          |     |

|   |              |                | $5.5.2.2$ System development $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                         |     |

|   |              |                | 5.5.2.3 Experimental results                                                                      |     |

|   | FC           | <b>X</b> 7 · 1 | 5.5.2.4 Demonstrator set-up                                                                       |     |

|   | 5.6          |                | compression solution based on the CCSDS 123.0-B-2 algorithm                                       | 142 |

|   |              | 5.6.1          | Application of the CCSDS 123.0-B-2 algorithm for panchromatic                                     | 140 |

|   |              |                | video compression                                                                                 |     |

|   |              |                | 5.6.1.1 Proposed approach $\ldots$                                                                |     |

|   |              | 500            | 5.6.1.2 Experimental results                                                                      |     |

|   |              | 5.6.2          | Adapting the CCSDS 123.0-B-2 algorithm to compress RGB video .                                    |     |

|   |              |                | 5.6.2.1 Proposed approach $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 147 |

|   | 5.7               | 5.6.2.1.1Using a single CCSDS-123 compression core for<br>each color channel5.6.2.1.2Transformation to the YCbCr domain5.6.2.2Experimental resultsConclusions | 148<br>150                      |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 6 | <b>Con</b><br>6.1 | clusions and future work                                                                                                                                      | 161<br>162                      |

|   | 0.1               | 6.1.1 State-of-the-art analysis                                                                                                                               |                                 |

|   |                   | 6.1.2 Functional blocks                                                                                                                                       |                                 |

|   |                   | 6.1.3 Solutions provided                                                                                                                                      |                                 |

|   |                   | 6.1.4 Validation $\ldots$                                                    | 167                             |

|   |                   | 6.1.5 Summary                                                                                                                                                 | 168                             |

|   | 6.2               | Further research work                                                                                                                                         | 169                             |

| A |                   | <ul> <li>Introducción</li></ul>                                                                                                                               | 176<br>179<br>180<br>181<br>184 |

|   | A.4               | Conclusiones                                                                                                                                                  |                                 |

| В | B.1<br>B.2        | lications Journals                                                                                                                                            | 191                             |

#### References

193

# List of Figures

| 1.1  | NanoXplore NG-MEDIUM FPGA                                                                         | 8        |

|------|---------------------------------------------------------------------------------------------------|----------|

| 1.2  | Overview of the HLS design methodology                                                            | 11       |

| 1.3  | Hyperspectral scanners. a) Whiskbroom; b) Pushbroom (extracted from [51])                         | 14       |

| 1.4  | Samples arrangement in hyperspectral cubes. a) BSQ; b) BIP; c) BIL                                | 15       |

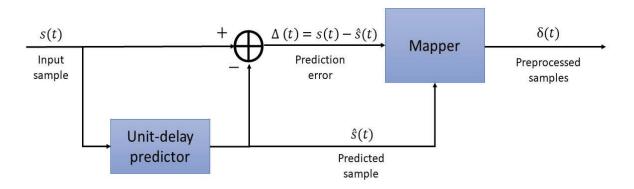

| 2.1  | Overview of a DPCM architecture combined with a Huffman encoder $\ . \ .$                         | 28       |

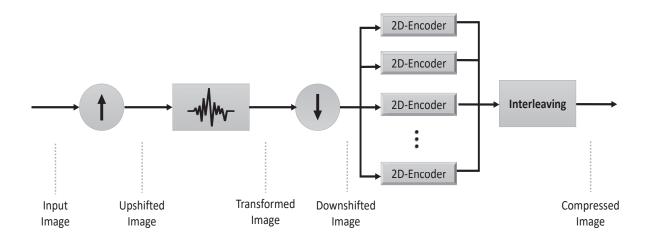

| 2.2  | CCSDS 122.1-B-1 standard - Block diagram                                                          | 34       |

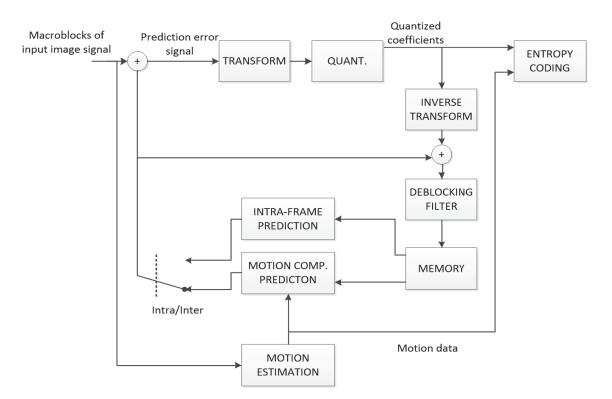

| 2.3  | H.264 standard - Structure overview                                                               | 36       |

| 2.4  | CWICOM ASIC for image compression (extracted from [176])                                          | 47       |

| 3.1  | Unit-delay predictor overview                                                                     | 52       |

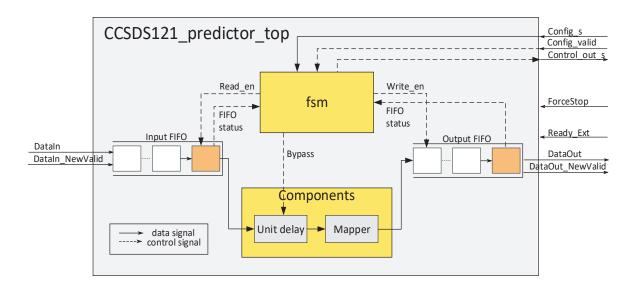

| 3.2  | Block diagram of the CCSDS 121.0-B-3 predictor top module                                         | 54       |

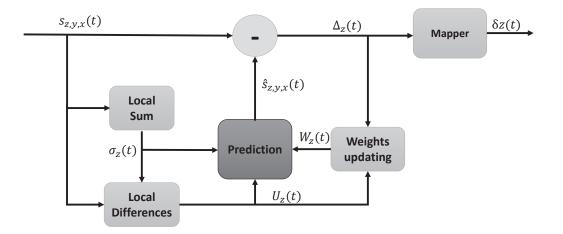

| 3.3  | CCSDS 123.0-B-1 predictor overview                                                                | 56       |

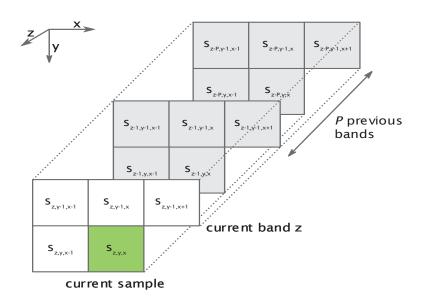

| 3.4  | Set of samples used for prediction                                                                | 57       |

| 3.5  | CCSDS 123.0-B-1 algorithm - BSQ and BIL schedule                                                  | 60       |

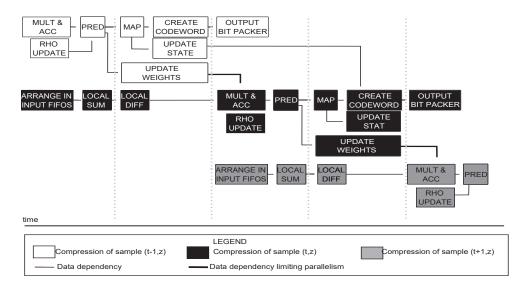

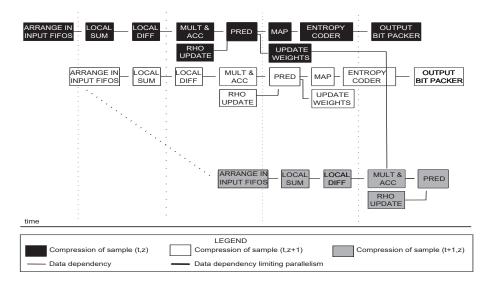

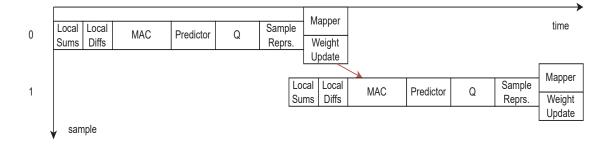

| 3.6  | CCSDS 123.0-B-1 algorithm - BIP schedule                                                          | 61       |

| 3.7  | CCSDS 123.0-B-1 predictor internal structure                                                      | 61       |

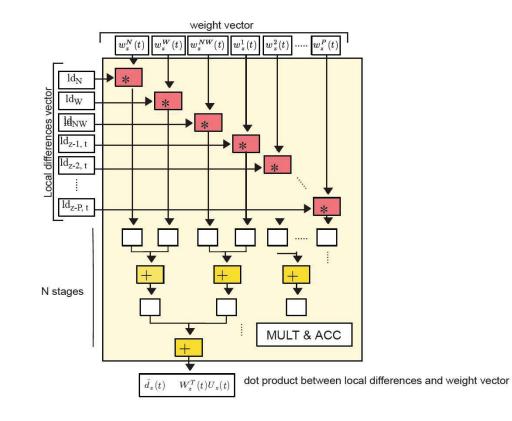

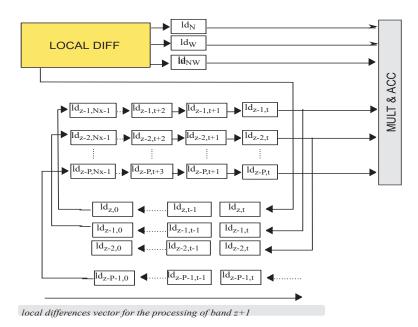

| 3.8  | CCSDS 123.0-B-1 predictor - Multiply-accumulate unit to perform the dot product in BIP            | 63       |

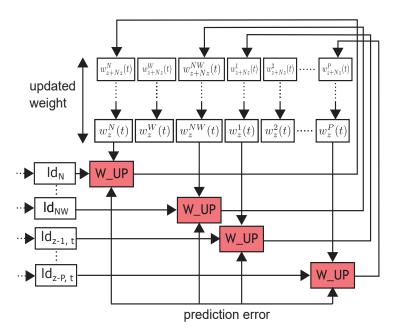

| 3.9  | CCSDS 123.0-B-1 predictor - Weight update in BIP                                                  | 64       |

|      | CCSDS 123.0-B-1 predictor - Vocgit update in BH · · · · · · · · · · · · · · · · · ·               | 04       |

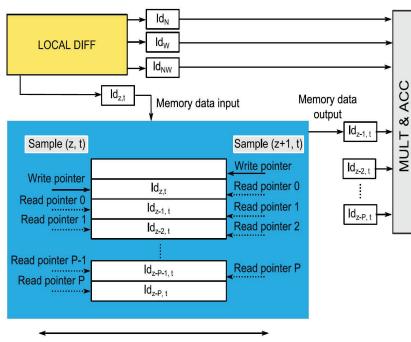

|      | in BSQ                                                                                            | 65       |

| 3.11 | CCSDS 123.0-B-1 predictor - Local differences storage in BIL                                      | 66       |

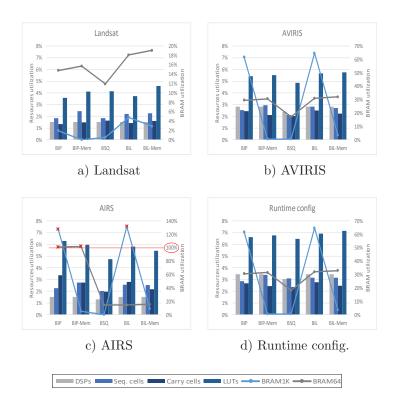

| 3.12 | CCSDS 123.0-B-1 predictor - Resources utilization on Xilinx Kintex Ultra-                         |          |

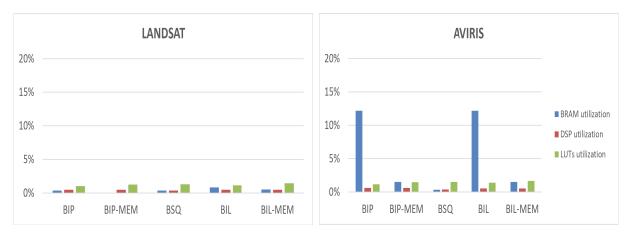

|      | Scale XCKU040                                                                                     | 68       |

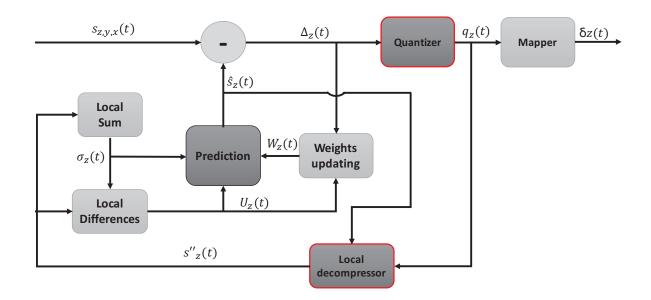

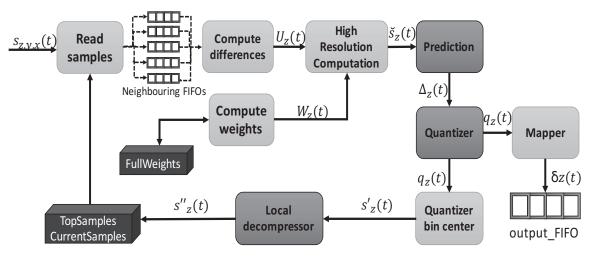

| 3.13 | CCSDS 123.0-B-2 predictor overview                                                                | 70       |

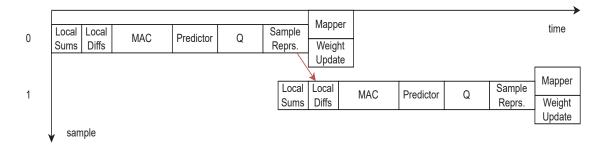

| 3.14 | CCSDS 123.0-B-2 algorithm - BIP schedule                                                          | 74       |

| 3.15 | CCSDS 123.0-B-2 algorithm - BSQ and BIL schedule with reduced prediction<br>and narrow local sums | 74       |

| 3.16 | CCSDS 123.0-B-2 predictor block diagram                                                           | 74<br>76 |

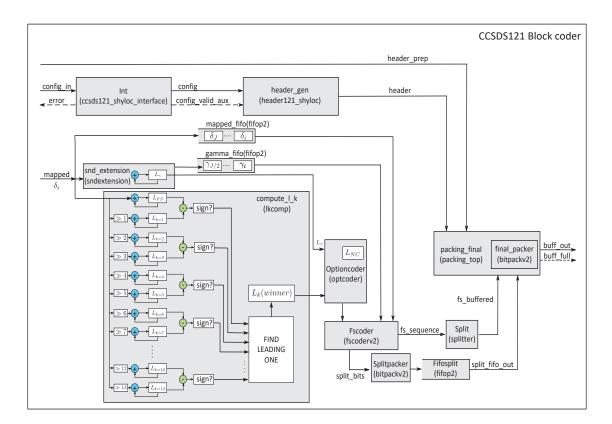

| 4.1  | Block diagram of the CCSDS 121.0-B-3 block-adaptive entropy coder                                 | 87       |

| 4.2  | Block diagram of the CCSDS 123.0-B-1 sample-adaptive entropy coder                                | 93       |

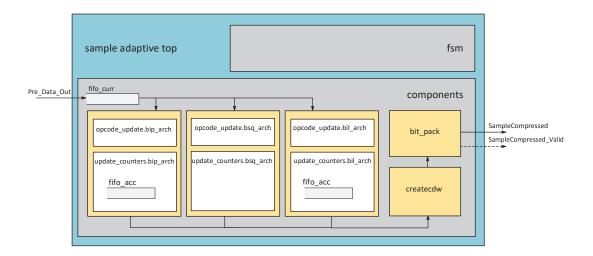

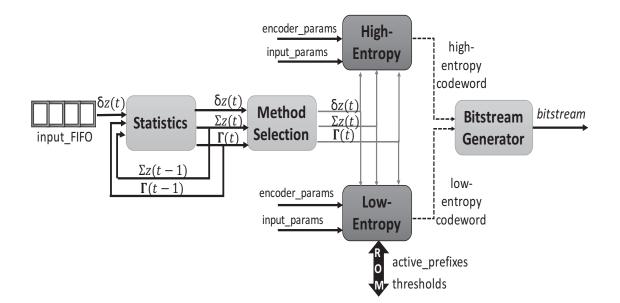

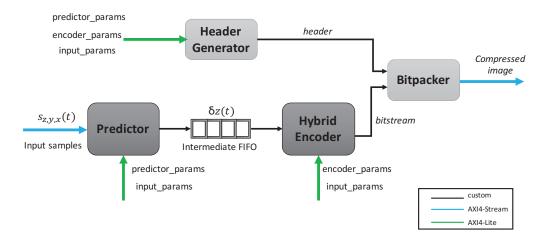

| 4.3  | General overview of the hybrid encoder architecture                                               | 98       |

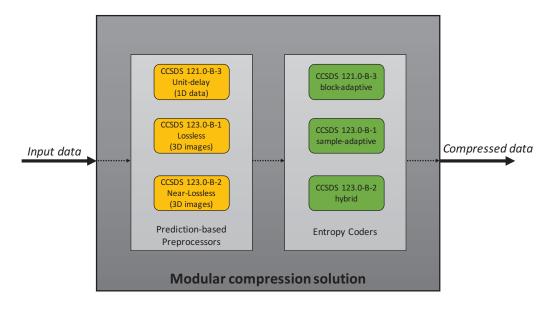

| 5.1  | Concept of modular compression solution                                                           | 105      |

|      |                                                                                                   |          |

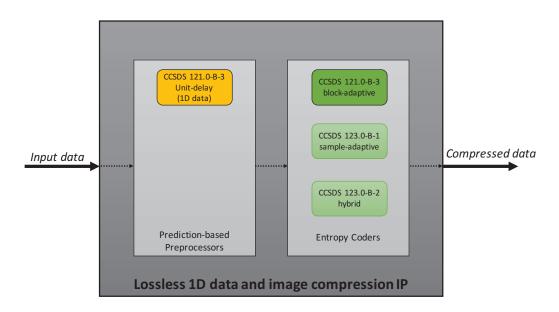

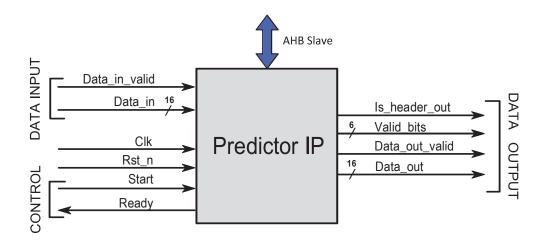

| 5.2         | Block diagram of the lossless 1D data and image compression IP                                                                         | 107 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

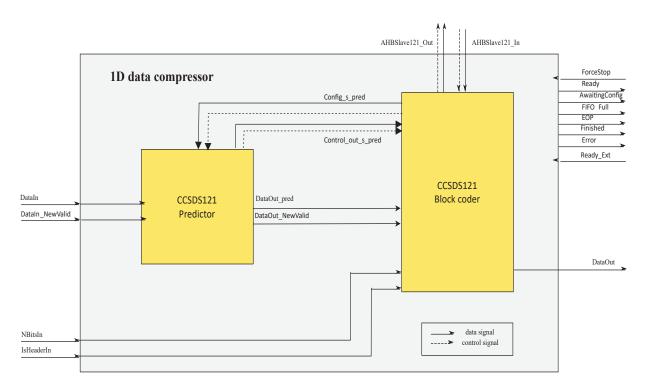

| 5.3         | Schematic of the proposed IP core for lossless compression of one-dimensional                                                          |     |

|             | data                                                                                                                                   | 109 |

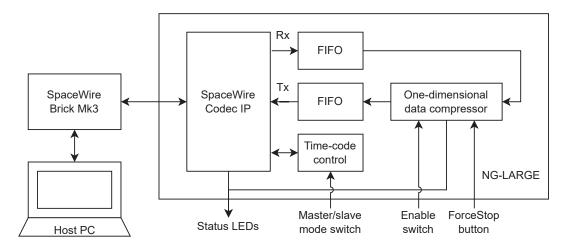

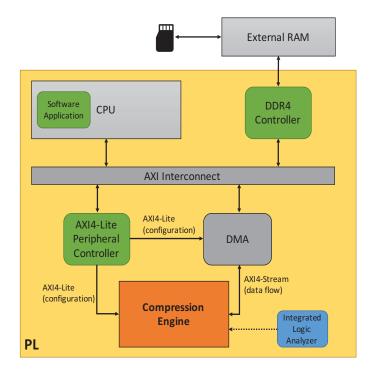

| 5.4         | Block diagram of the hardware design developed for the IP core test set-up                                                             | 113 |

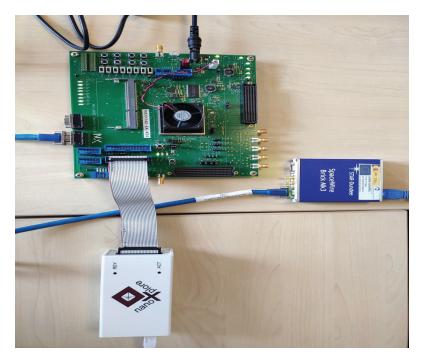

| 5.5         | Overview of the IP test set-up, including the NX1H140TSP development                                                                   |     |

|             | kit and the STAR-Dundee SpaceWire Brick Mk3                                                                                            |     |

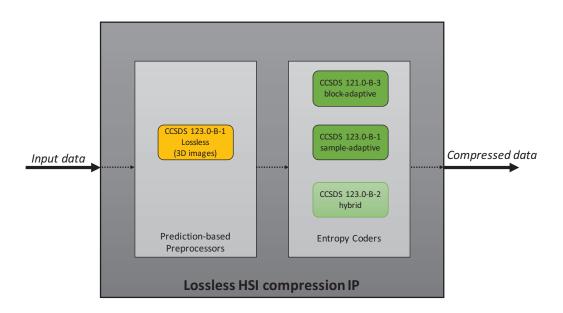

| 5.6         | Block diagram of the lossless hyperspectral image compression IP                                                                       | 115 |

| 5.7         | Internal overview of the proposed IP core for lossless hyperspectral image                                                             |     |

|             | compression and connectivity among functional units                                                                                    | 117 |

| 5.8         | Lossless hyperspectral image compression IP core - Resources utilization on<br>Xilinx Virtex5QR XQR5VFX130 [60]                        | 121 |

| 5.9         | Lossless hyperspectral image compression IP core - Resources utilization on                                                            |     |

|             | Xilinx Kintex UltraScale XCKU040                                                                                                       | 122 |

| 5.10        | Lossless hyperspectral image compression IP core - Resources utilization on                                                            |     |

|             | Microsemi RTG4 150 [60]                                                                                                                | 122 |

| 5.11        | Lossless hyperspectral image compression IP core - Resources utilization on                                                            |     |

|             | NanoXplore NG-LARGE [60]                                                                                                               | 123 |

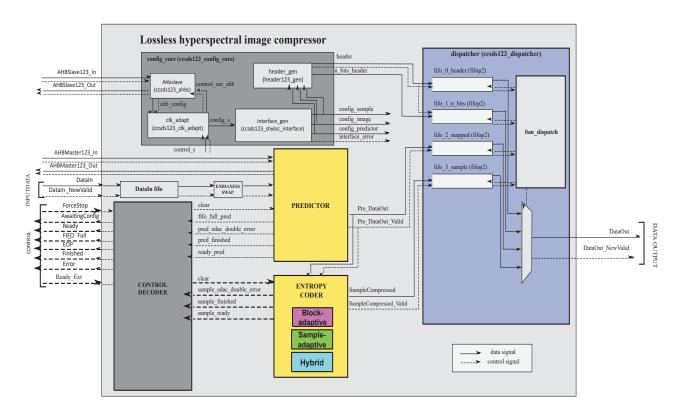

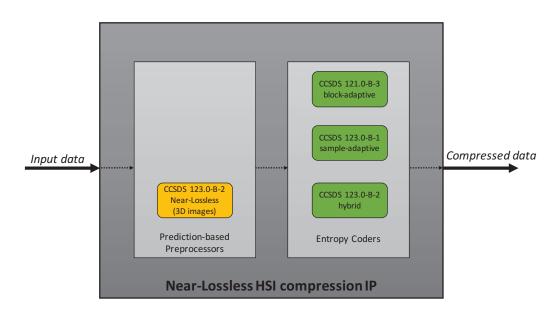

| 5.12        | Block diagram of the near-lossless hyperspectral image compression IP $~$                                                              | 126 |

| 5.13        | Top-level hierarchy of the near-lossless hyperspectral image compression                                                               |     |

|             | solution fully compliant with the CCSDS 123.0-B-2 standard                                                                             | 127 |

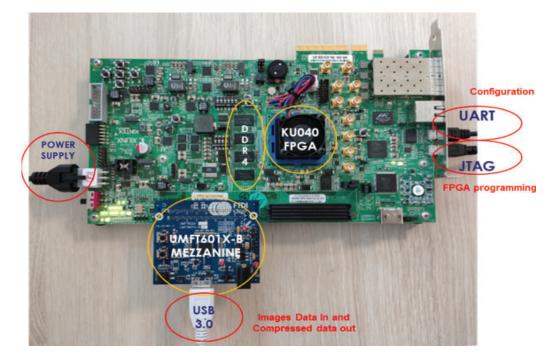

|             | Validation set-up for the CCSDS 123.0-B-2 compliant IP                                                                                 |     |

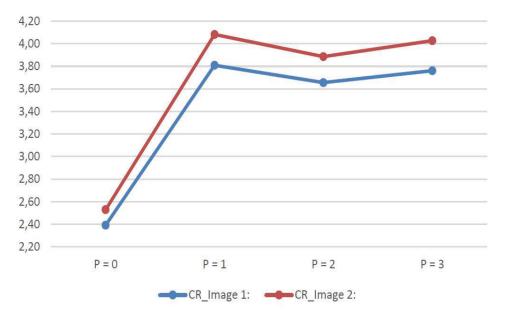

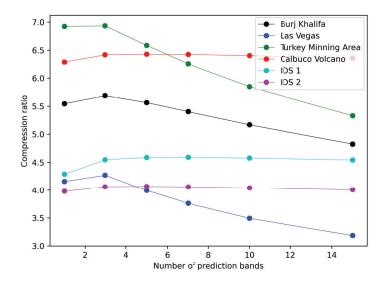

| 5.15        | Compression ratio as a function of the $P$ value $\ldots \ldots \ldots \ldots \ldots \ldots$                                           | 134 |

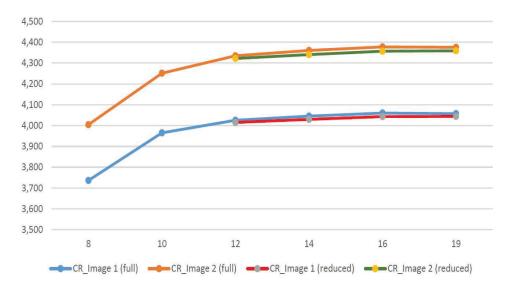

| 5.16        | Compression ratio as a function of the $\Omega$ value $\ldots \ldots \ldots \ldots \ldots \ldots$                                      | 135 |

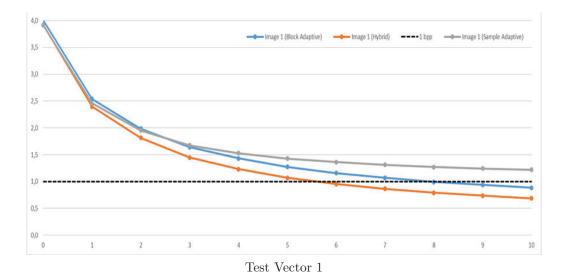

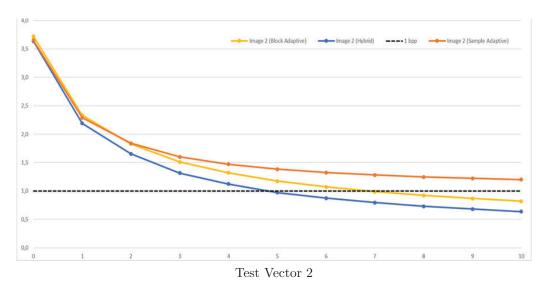

|             | Comparison of the encoder performance for CHIME test vectors                                                                           | 136 |

| 5.18        | Block diagram of the proposed compression approach for CHIME pre-                                                                      |     |

|             | development phase                                                                                                                      |     |

|             | CHIME predictor - Overview                                                                                                             |     |

|             | Validation set-up for CHIME (extracted from [194])                                                                                     |     |

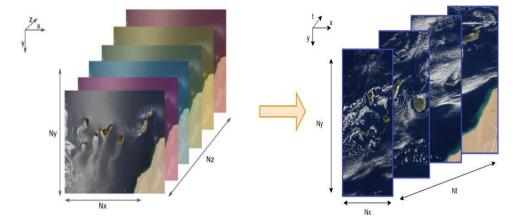

| 5.21        | Conversion from the spectral to the temporal domain $\ldots \ldots \ldots \ldots$                                                      | 143 |

| 5.22        | Panchromatic compression - Influence of $P$ value in the compression ratio                                                             |     |

|             | under lossless mode                                                                                                                    | 145 |

| 5.23        | Panchromatic compression - Relationship between compression ratio and                                                                  |     |

|             | video quality                                                                                                                          | 146 |

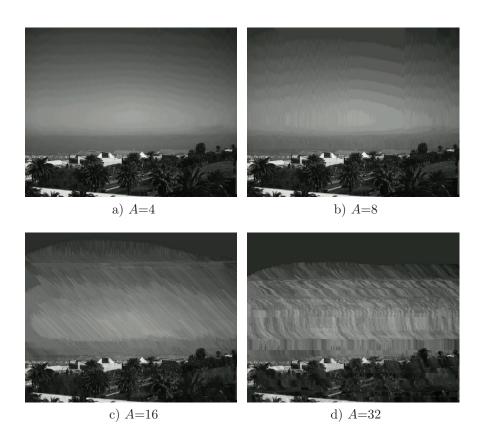

| 5.24        | Visual aspect of the decompressed frames from the <i>IDS 1</i> video sequence                                                          |     |

|             | when compressing it with different maximum errors values                                                                               | 147 |

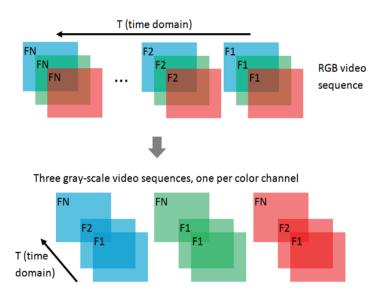

| 5.25        | Compression strategy for RGB video, treating each color channel as inde-                                                               |     |

|             | pendent frames                                                                                                                         |     |

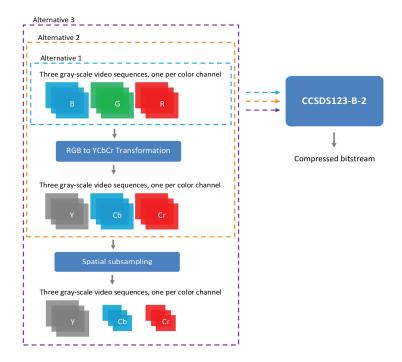

|             | Full processing chain for RGB video compression                                                                                        | 150 |

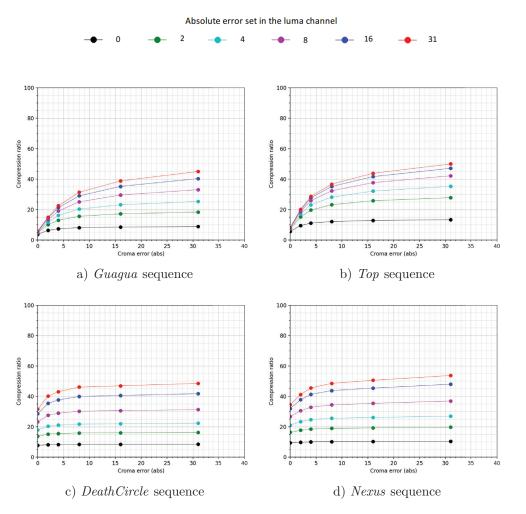

| 5.27        | Relationship of the the chroma and luma errors with the compression ratio                                                              | 150 |

| <b>F</b> 00 | (Alternative 2)                                                                                                                        | 152 |

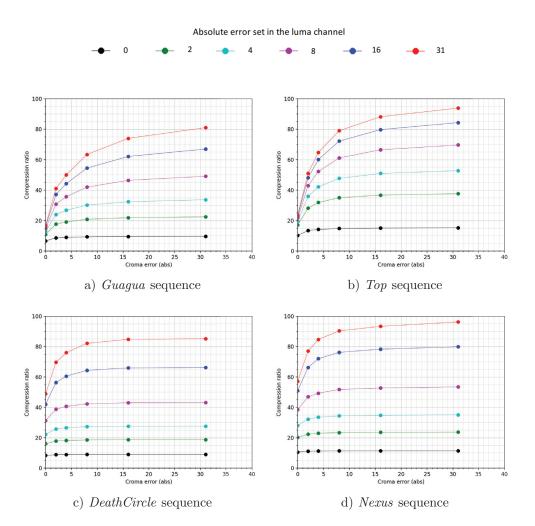

| 5.28        | Relationship of the the chroma and luma errors with the compression ratio                                                              | 150 |

| F 00        | (Alternative 3)                                                                                                                        | 153 |

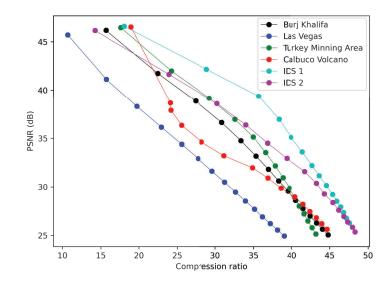

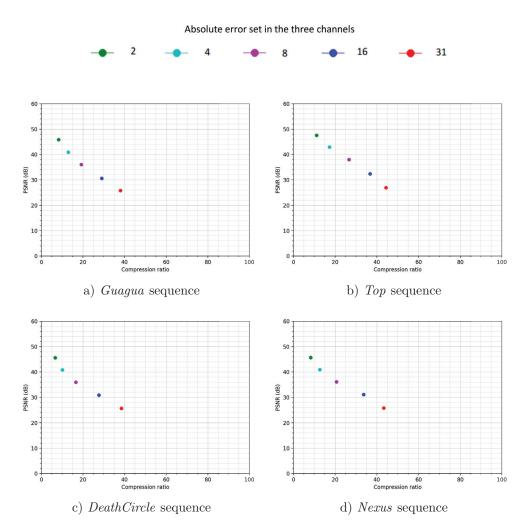

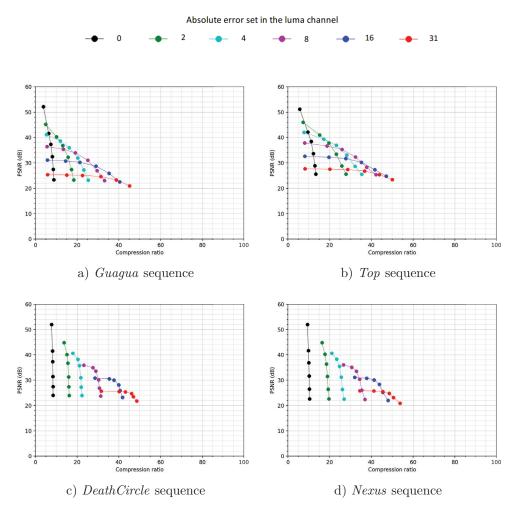

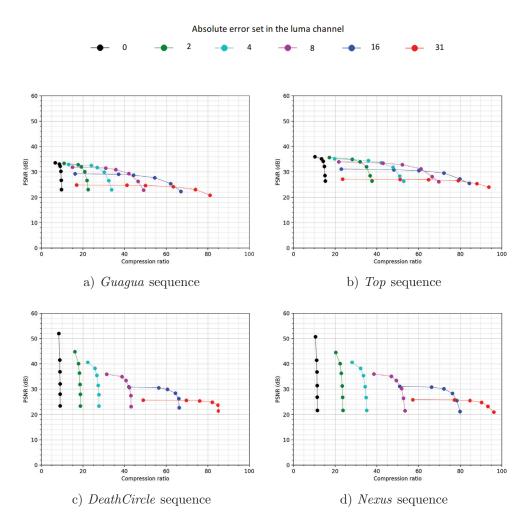

| 5.29        | Relationship between the compression ratio and video quality, measured by<br><u>BSND</u> for ariginal <u>BCD</u> wideo (Alternative 1) | 155 |

|             | PSNR, for original RGB video (Alternative 1)                                                                                           | 199 |

| 5.30 | Relationship between the compression ratio and video quality, measured by          |     |

|------|------------------------------------------------------------------------------------|-----|

|      | PSNR, after applying RGB to YCbCr transformation (Alternative 2) 1                 | 156 |

| 5.31 | Relationship between the compression ratio and video quality, measured by          |     |

|      | PSNR, after applying RGB to YCbCr transformation and chroma subsam-                |     |

|      | pling (Alternative 3)                                                              | 157 |

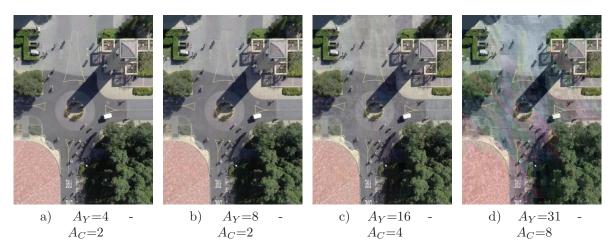

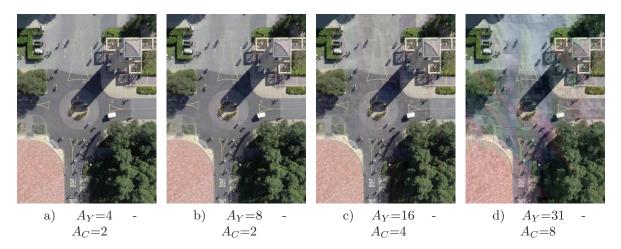

| 5.32 | Decompressed frames from the <i>DeathCircle</i> video with different maximum       |     |

|      | errors values for the Y channel $(A_Y)$ and for the Cb and Cr channels $(A_C)$ . 1 | 158 |

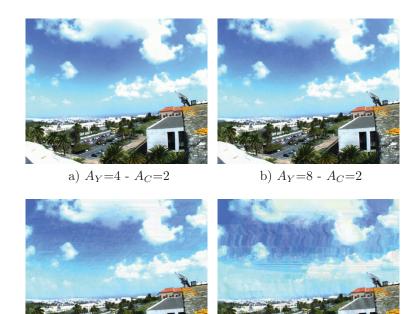

| 5.33 | Decompressed frames from the <i>Guagua</i> video with different maximum errors     |     |

|      | values for the Y channel $(A_Y)$ and for the Cb and Cr channels $(A_C)$ 1          | 158 |

| A.1  | Concepto de solución de compresión modular                                         | 180 |

| A.2  | Compresor de imágenes hiperespectrales sin pérdidas - Utilización de recursos      |     |

|      | en Xilinx Kintex UltraScale XCKU040                                                | 183 |

| A.3  | Relación entre el ratio de compresión y la calidad del vídeo decomprimido,         |     |

|      | medida en términos de PSNR, para la cadena de compresión para vídeo                |     |

|      | RGB completa                                                                       | 186 |

| A.4  | Frames decomprimidos de la secuencia de vídeo Death Circle aplicando difer-        |     |

|      | entes errores a los canales de luma y cromas                                       | 187 |

# List of Tables

| 1.1          | Main features of current and future spacecraft with on-board hyperspectral sensors                                                                     | 4   |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $3.1 \\ 3.2$ | Sets of synthesis configurations for the CCSDS 121.0-B-3 unit-delay predictor CCSDS 121.0-B-3 unit-delay predictor - Synthesis on Xilinx Kintex Ultra- | 54  |

| 3.3          | Scale XCKU040                                                                                                                                          | 55  |

|              | possible input arrangement                                                                                                                             | 62  |

| $3.4 \\ 3.5$ | Baseline synthesis configuration for the CCSDS 123.0-B-1 predictor CCSDS 123.0-B-1 predictor - Maximum frequency on Xilinx Kintex Ultra-               | 67  |

|              | Scale XCKU040                                                                                                                                          | 67  |

| 3.6          | CCSDS 123.0-B-1 predictor - Resources utilization on Xilinx Kintex Ultra-                                                                              |     |

|              | Scale XCKU040 per module in BIP order                                                                                                                  | 68  |

| 3.7          | Baseline synthesis configuration for the CCSDS 123.0-B-2 predictor                                                                                     | 79  |

| 3.8          | CCSDS 123.0-B-2 predictor - Resources utilization on Xilinx Kintex Ul-                                                                                 |     |

|              | traScale XCKU040 depending on the combination of local sum and full prediction                                                                         | 79  |

| 3.9          | CCSDS 123.0-B-2 predictor - Resources utilization on Xilinx Kintex Ultra-                                                                              | 13  |

| 0.0          | Scale XCKU040 depending on the combination of local sum and reduced                                                                                    |     |

|              | prediction                                                                                                                                             | 79  |

| 3.10         | CCSDS 123.0-B-2 predictor - Resources utilization on Xilinx Kintex Ultra-                                                                              |     |

|              | Scale XCKU040 depending on the applied absolute error limit                                                                                            | 80  |

| 3.11         | CCSDS 123.0-B-2 predictor - Resources utilization on Xilinx Kintex Ultra-                                                                              |     |

|              | Scale XCKU040 per submodule                                                                                                                            | 81  |

| 4.1          | Sets of synthesis configurations for the CCSDS 121.0-B-3 block-adaptive                                                                                |     |

|              | encoder                                                                                                                                                | 90  |

| 4.2          | CCSDS 121.0-B-3 block-adaptive encoder - Synthesis on Xilinx Kintex                                                                                    |     |

|              | UltraScale XCKU040                                                                                                                                     | 91  |

| 4.3          | Sets of synthesis configurations for the CCSDS 123.0-B-1 sample-adaptive                                                                               |     |

|              | encoder                                                                                                                                                | 94  |

| 4.4          | CCSDS 123.0-B-1 sample-adaptive encoder - Synthesis on Xilinx Kintex                                                                                   | 05  |

| 4.5          | UltraScale XCKU040                                                                                                                                     | 95  |

| 4.0          | old in the low-entropy mode                                                                                                                            | 97  |

| 4.6          | 10                                                                                                                                                     | 101 |

|              | = 1                                                                                                                                                    | ~ - |

| 4.7          | CCSDS 123.0-B-2 hybrid encoder - Synthesis on Xilinx Kintex UltraScale XCKU040                                             | 102        |

|--------------|----------------------------------------------------------------------------------------------------------------------------|------------|

| 5.1          | Sets of synthesis configurations for the lossless one-dimensional data com-<br>pression IP core                            | 110        |

| 5.2          | Lossless one-dimensional data compression IP core - Synthesis on Xilinx<br>Virtex5QR XQR5VFX130                            | 111        |

| 5.3          | Lossless one-dimensional data compression IP core - Synthesis on Xilinx Kintex UltraScale XCKU040                          | 111        |

| 5.4          | Lossless one-dimensional data compression IP core - Synthesis on Microsemi RTG4 150                                        | 111        |

| 5.5          | Lossless one-dimensional data compression IP core - Synthesis on NanoX-<br>plore NG-LARGE                                  | 112        |

| 5.6          | Sets of synthesis configurations for the lossless hyperspectral image com-<br>pression IP core                             |            |

| $5.7 \\ 5.8$ | Scenarios considered for the IP performance analysis                                                                       | 118        |

| 5.9          | Xilinx Virtex5QR XQR5VFX130 Lossless hyperspectral image compression IP core - Maximum frequency on                        |            |

| 5.10         | Xilinx Kintex UltraScale XCKU040                                                                                           |            |

| 5.11         | Microsemi RTG4 150                                                                                                         | 120        |

| <b>F</b> 10  | NanoXplore NG-LARGE                                                                                                        |            |

|              | Comparison with CCSDS-123 FPGA implementations                                                                             | 124<br>129 |

| 5.14         | Near-lossless hyperspectral image compression IP - Resources utilization on Xilinx Kintex UltraScale XCKU040               | 129        |

|              | Comparison between CCSDS 123 VHDL and HLS implementations $\ . \ . \ .$                                                    |            |

|              | CCSDS123.0-B-2 predictor configuration for CHIME parameter tuning $\ . \ .$                                                | 134        |

| 5.17         | Optimal offset and damping values depending on the absolute error limit $a_z$ , when $\Theta = 4$                          | 135        |

| 5.18         | Parameter values for the block-adaptive encoder to achieve the highest CR $\mathbf{R}$                                     |            |

|              | CHIME predictor - Constant parameters                                                                                      |            |

| 5.20         | CHIME predictor - Runtime configurable parameters                                                                          | 139        |

| 5.21         | CHIME IP - Resources utilization on Xilinx Kintex UltraScale XCKU040 $% \mathcal{A}$ .                                     | 140        |

| 5.22         | Relevant compressor parameters                                                                                             | 144        |

| A.1          | Compresor de datos unidimensionales sin pérdidas - Síntesis en Xilinx Kintex<br>UltraScale XCKU040 con $D = 16$ y $J = 32$ | 182        |

| A.2          | CHIME IP - Utilización de recursos en Xilinx Kintex UltraScale XCKU040                                                     |            |

### Abbreviations

**AAT** Arbitrary Affine Transform

ADC Analog-to-Digital Converter

AHB Advanced High-performance Bus

AIRS Atmospheric Infrared Sounder

AMBA Advanced Microcontroller Bus Architecture

ASI Italian Space Agency

**ASIC** Application Specific Integrated Circuit

AVC Advanced Video Coding

**AVIRIS** Airbone Visible/Infrared Imaging Spectrometer

**AXI** Advanced eXtensible Interface

**BIL** Band Interleaved by Line

**BIP** Band Interleaved by Pixel

**bpp** bits per pixel

${\bf BRAM}\,$  Block RAM

**BRAVE** Big Re-programmable Array for Versatile Environment

**BSQ** Band Sequential

CALIC Context-based, Adaptive, Lossless Image Codec

CAVLC Context-Adaptive Variable Length

**CCSDS** Consultative Committee for Space Data Systems

CHIME Copernicus Hyperspectral Imaging Mission for Environment

**CNES** National Centre for Space Studies

$\mathbf{COTS}$  Commercial off-the-Shell

**CPU** Central Processing Unit

**CR** Compression Ratio

**CTU** Coding Tree Unit

CU Coding Unit

$\mathbf{DCT}$ Discrete Cosine Transform

${\bf DFF}\,$ D-type Flip Flop

**DMR** Double Modular Redundancy

**DPCM** Differential Pulse Code Modulation

**DSP** Digital Signal Processing

${\bf DST}$ Discrete Sine Transform

$\mathbf{DUT}$  Design Under Test

**DWT** Discrete Wavelet Transform

EDA Electronic Design Automation

EDAC Error Detection And Correction

EnMAP Environmental Mapping and Analysis Program

| <b>EO</b> Earth Observation                             |

|---------------------------------------------------------|

| <b>EOP</b> End of Processing                            |

| <b>ESA</b> European Space Agency                        |

| <b>ESTEC</b> European Research and Technology Centre    |

| <b>EZW</b> Embedded Zero-tree Wavelet                   |

| <b>FAPEC</b> Fully Adaptive Prediction Error Coder      |

| $\mathbf{FF}$ Flip-Flop                                 |

| FIFO First-In First-Out                                 |

| <b>FL</b> Fast Lossless                                 |

| <b>FLEX</b> Fast Lossless EXtended                      |

| <b>FPGA</b> Field Programmable Gate Array               |

| <b>FPS</b> Frames Per Second                            |

| $\mathbf{FS}$ Fundamental Sequence                      |

| <b>FSM</b> Finite-State Machine                         |

| <b>GFLOPS</b> Giga-Floating-point Operations per Second |

| GPO2 Golomb-power-of-2                                  |

| <b>GPU</b> Graphics Processing Unit                     |

| HDL Hardware Description Language                       |

| <b>HEVC</b> High Efficiency Video Coding                |

| <b>HISUI</b> Hyperspectral Imager Suite                 |

| <b>HPSC</b> High-Performance Spaceflight Computing      |

| HSI HyperSpectral Imaging                               |

- MPSoC Multi-Processor System-on-Chip

- **MODIS** Moderate Resolution Imaging Spectroradiometer

- **MSB** Most Significant Bit

- **MSE** Mean Squared Error

- **MSI** Multispectral Instrument

- MSS Multispectral Scanner System

- **NASA** National Aeronautics and Space Administration

- NGMP Next Generation Multipurpose Processor

- **NRE** Non-Recurring Engineering

- **PCA** Principal Component Analysis

- PFCU Processing, Formatting and Control Unit

- PLL Phase-Locked Loop

- **POT** Pairwise Orthogonal Transform

- **PRDC** Payload Rice Data Compressor

- **PSNR** Peak-Signal to Noise Ratio

- **RAM** Random Access Memory

- **RHBD** Radiation-Hardened by Design

- **ROI** Region of Interest

- **SAO** Sample Adaptive Offset

- **SEE** Single Event Effect

- **SEFI** Single Event Functional Interrupt

- **SEU** Single Event Upset

#### SHALOM Spaceborne Hyperspectral Applicative Land and Ocean Mission

- SHyLoC Hyperspectral Lossless Compressor for space applications

- **SNR** Signal to Noise Ratio

- $\mathbf{SoC}$  System-on-Chip

- **SPARC** Scalable Processor ARChitecture

- ${\bf SRAM}$  Static RAM

- **TID** Total Ionizing Dose

- **TMR** Triple Modular Redundancy

- $\mathbf{TTM}$  Time-To-Market

- **UAB** Universitat Autònoma de Barcelona

- ULPGC University of Las Palmas de Gran Canaria

- VCL Video Coding Layer

- VHDL VHSIC Hardware Description Language

- WICOM Wavelet Image Compression Module

- WPP Wavefront Parallel Processing

## Chapter 1

## Introduction

This Chapter presents the motivation and objectives of the Thesis, which is focused on providing efficient hardware implementations for on-board data compression. The main goal of the work is to develop different modular solutions to compress generic data, hyperspectral images and video sequences on-board satellites using configurable hardware devices and keeping in mind the main constraints existing on space missions (computational resources, storage capacity and power consumption, among others). This Chapter also provides some hints about the constraints to deal with when designing hardware for space. This information is required to understand the problems involved and the solutions provided.

#### 1.1 Motivation

Remote Sensing applications have become very popular for the space industry during the last decades, since high-resolution sensors allow to obtain useful information for an important number of applications (e.g. environmental studies, climate, surveillance, characterization, monitoring, detection, etc.) [1–7]. These kind of sensors, commonly used in Earth Observation (EO) missions, are also gaining interest for space exploration, and are currently considered by space agencies to study the Moon or the Mars surface [8, 9].

Among all sensors, those with the capability to obtain rich spectral information have been used since the beginning because of their strengths for characterization and monitorization applications. A proof of this is the number of satellites with multi- or hyperspectral sensors on-board. The history starts with Landsat-1, launched by NASA in 1972, which can be considered the first modern satellite for EO [10]. Landsat-1 integrated a Multispectral Scanner System (MSS) that acquires four bands with wavelengths from 0.5 to 1.1  $\mu m$  with a spatial resolution of 80 m. The Landsat program has launched a total of nine satellites and still continues. Landsat-9 has been recently launched on September 2021 and it will join Landsat-8 in orbit. Other important missions by NASA are the Earth-Observing One (EO-1) satellite, which embarked the Hyperion Imaging Spectrometer (decommissioned on March 2017) [11]; and the Hyperspectral Infrared Imager (HyspIRI) mission, aims to provide critical information on natural disasters and vegetation health [12]. HyspIRI was launched in 2020 and includes an imaging spectrometer measuring from the visible to short-wave infrared (i.e. from 380 nm to 2.5  $\mu m$ ) in 10 nm contiguous bands, with a spatial resolution of 60 m.

In Europe, the Copernicus program has the main goal of providing real-time dynamic monitoring of the environment. The space-based observation part of the program is responsibility of the European Space Agency (ESA), which has launched a family of six satellites, known as Sentinel [13]. Sentinel-2 integrates a Multispectral Instrument (MSI) that acquires 13 spectral channels: the first four bands are the three RGB bands and a Near Infrared (NIR) spectral channel, with a spatial resolution of 10 m; six bands, four of them in the Visible and Near Infrared (VNIR) and 2 Short Wavelengths Infrared (SWIR) bands (1.61  $\mu m$  and 2.19  $\mu m$ ), with a spatial resolution of 20 m; and the last three bands for atmospheric correction (443 nm, 945 nm and 1374 nm), with a 60 m spatial resolution.

The Copernicus Hyperspectral Imaging Mission for Environment (CHIME) is introduced by ESA in the future Copernicus 2.0 program to provide routine hyperspectral observations for the monitorization of natural resources, including applications such as sustainable agricultural and biodiversity management, soil properties characterization, sustainable mining practices and environment preservation [14]. CHIME shall provide continuous spectral data in VNIR and SWIR spectral domains, covering approximately 250 spectral channels between 400 nm and 2.5  $\mu m$ . The sensor will be used to acquire hyperspectral images with a bit-depth of 16 bits per sample, what leads to input data rates up to 2 Gbps. This Thesis will provide an ad-hoc solution for compressing information acquired by the CHIME instrument (see Chapter 5).

European space agencies have also launched different EO satellites as part of their national programs. The National Centre for Space Studies (CNES) has launched seven satellites, known as the SPOT family. SPOT-1, launched in 1986, is considered the world's first Remote Sensing satellite. A new French mission, denoted as HypXIM [15], is expected to be launched in the time-frame 2022-2024, collecting a total of 210 spectral bands in the range 400-2500 nm (VNIR and SWIR regions), with a spectral and spatial resolution of 10 nm and 8 m, respectively. PRISMA is a mission fully funded by the Italian Space Agency (ASI) and launched in 2019 [16]. The Spaceborne Hyperspectral Applicative Land and Ocean Mission (SHALOM) is a joint mission by the Israeli and the Italian space agencies to develop a hyperspectral satellite that collects 275 bands with a spectral resolution of 10 nm and a spatial resolution of 10 m [17]. The Environmental Mapping and Analysis Program (EnMAP) is a German hyperspectral satellite mission for Earth monitoring and characterization, embarking a sensor that collects continuous spectral bands of 6-14  $\mu m$  width in the range 420-2450 nm, with a spatial resolution of 30 m [18].

Finally other Agencies (as Japanese and Chinese) has launched a number of similar programs to the aforementioned ones [19–21]. Table 1.1 summarises the main features of the most relevant current and future space missions that embark hyperspectral sensors, including the number of bands collected and both the spatial and the spectral resolution.

Table 1.1 shows that high-resolution sensors are conceived for acquiring as many spectral bands as possible with a high spatial and spectral resolution. This extra information in the spectral domain is intended to obtain a high grade of information about the objective under analysis. A first solution could be to acquire the information on-board and send it to ground in a raw format to be then processed. However, the satellite downlink bandwidth with ground stations usually is limited, as is the memory storage capacity on-board. In this way, data compression emerges as the solution to dodge these constraints, reducing the data volume prior to send it to ground.

| Sensor                | Number<br>of bands | Spectral<br>Range(nm) | Spectral<br>Resolution(nm) | Spatial<br>Resolution(m) | Launch    |

|-----------------------|--------------------|-----------------------|----------------------------|--------------------------|-----------|

| HyspIRI (USA)         | 210                | 380 - 2500            | 10                         | 60                       | 2020      |

| CHIME (Europe)        | 220                | 400-2500              | 10                         | 20-30                    | 2027-2029 |

| PRISMA (Italy)        | 240                | 400-2500              | 10-12                      | 30                       | 2019      |

| SHALOM (Italy/Israel) | 275                | 400-2500              | 10                         | 10                       | 2022      |

| HypXIM (France)       | 210                | 400-2500              | 10                         | 8                        | 2022-2024 |

| EnMAP (Germany)       | 200                | 420-2450              | 6-14                       | 30                       | 2020      |

| HISUI (Japan)         | 185                | 400-2500              | 10-12.5                    | 30                       | 2019      |

| Gaofen-5 (China)      | 330                | 400-2500              | 5-10                       | 30                       | 2018      |

| Zhuhai-1 (China)      | 166                | 450-2500              | 10-20                      | 30                       | 2019      |

TABLE 1.1: Main features of current and future spacecraft with on-board hyperspectral sensors

On the other hand, the demand of video sensors embarked on satellites is also increasing in the last years since they provide extra information in the temporal domain. This interest will grow exponentially in the near-future, mainly for applications such as monitorization, including target detection and tracking, and exploration missions. Nowadays, some commercial satellites provide video products for potential applications on ground. For instance, SkySat is a constellation of 21 high-resolution imaging satellites (SkySat-1 was launched in 2013) at different orbits and altitudes. They are able to collect video using a panchromatic camera, which has a spatial resolution of approximately 1x2.5 km<sup>2</sup> and with a temporal duration between 30 and 120 seconds at 30 FPS [22]. The Jilin-1 Chinese satellite constellation also provides high-definition video imaging, optical and hyperspectral imagery [23]. High-definition RGB video is provided in real-time at 10 FPS, with a duration up to 120 seconds and a spatial resolution around 1 m, covering a scene of 19 km [24]. Academic institutions are also working in CubeSat missions comprised by Commercial Off-The-Shelf (COTS) components and including image and video sensors for EO. As an example, the High-Resolution Image and Video CubeSat (HiREV), currently under development by the Korea Aerospace Research Institute, will integrate a sensor for high-resolution (5 m per pixel) color image and video [25]. Moreover, multi- and hyperspectral video is expected on space missions in a short future, mainly due to the availability of the snapshot cameras.

In conclusion, it is expected that the new-generation imaging sensors boost in the next years both the spatial and the spectral resolution, even collecting temporal information for video applications. Nowadays, there is a huge amount of data being acquired on satellites and this amount will be much higher in the short future. As mentioned before, the limited downlink bandwidth in comparison with the size of the acquired data will constitute a bottleneck for missions that integrate this kind of sensors, preventing the direct transmission of raw data to ground [26]. Therefore, performing on-board compression is becoming mandatory on space missions for Remote Sensing applications.

Data compression is still considered a challenge by the space industry. Very efficient and low-complexity algorithms and processing platforms will be required on-board to compress that huge amount of information in real-time. This has been a hot topic for the scientific community during the last decades, mainly because the computational restrictions present on-board satellites force the compression algorithms to meet certain design criteria. At the same time, it is very important to preserve the quality of the reconstructed data after decompression because it will be impossible to capture the same data twice.

This is the reason why the Consultative Committee for Space Data Systems (CCSDS), an international organization comprised by the main space agencies in the world to define a common procedure for developing space data and information systems, has published different compression standards. The target of these algorithms has different data nature (1D, 2D and 3D data) and compression techniques (i.e., lossless or lossy), but always meet the condition of a reduced algorithmic complexity. These standards pretend to establish a common framework for the development of on-board compression solutions and to have an universal solution for the decompression of the information on ground. Regarding one-dimensional data, image and hyperspectral image compression, the CCSDS has published the following Recommended Standards: a) CCSDS 121.0-B-3 (Lossless Data Compression) [27], b) CCSDS 122.0-B-2 (Image Data Compression) [28], c) CCSDS 122.1-B-1 (Spectral Preprocessing Transform for Multispectral and Hyperspectral Image Compression) [30] and e) CCSDS 123.0-B-2 (Low-Complexity Lossless and Near-Lossless Multispectral and Hyperspectral Image Compression) [30] and e) CCSDS 123.0-B-2 (Low-Complexity Lossless and Near-Lossless Multispectral and Hyperspectral Image Compression) [31].

Although the algorithms proposed in these standards have been selected in order to be feasibly implemented on the hardware available on-board satellites, the development of these solutions is not trivial, and it is still challenging for both academic institutions and space companies. The most common solution nowadays is to include in the system an IP core (soft or hard, depending on the availability and mission requirements) that implements the specific compression technique needed on-board. If there is not an IP available, the solution is to perform the compression as a software application running on a general-purpose microprocessor, though in this case the performance goals are very hard to met. The main goal of this Thesis is to provide efficient compression solutions to be implemented on space missions. The proposed solutions shall be able to manage data from different nature, including one-dimensional data, hyperspectral images and video (panchromatic and RGB). The proposed approaches have to achieve not only an acceptable compression ratio without degrading the quality of the compressed information, but they also have to take into account additional constraints that appear on-board satellites, such as throughput to meet real-time requirements; low area utilization, to fit well on the available hardware resources embarked on space missions; and low power consumption. The designed solutions will be developed following a modular approach, based on the fact that many of these standards have computational similarities. In particular, this Thesis will study the CCSDS 121.0-B-3, the CCSDS 123.0-B-1 and the CCSDS 123.0-B-2 standard, from which computational modules will be created that can be merged together to solve the problem of one-dimensional data compression, multispectral and hyperspectral image compression and video compression on-board satellites.

#### **1.2** Application environment constraints

When dealing with on-board applications, there is a number of constraints to take into account. The spacecraft is considered as a platform and a payload. For EO satellites, the payload usually includes a hyperspectral sensor and/or a panchromatic/RGB camera, together with the electronic circuits needed to acquire, process and store the information. The platform consists in the satellite subsystems that supports the payload [32]. These subsystems (such as electrical power distribution; telemetry, tracking and command; thermal control; propulsion; etc.) are not covered in this Thesis. This Thesis will cover part of the on-board data handling subsystem and, particularly, will be part of the Processing, Formatting and Control Unit (PFCU) of the satellite, dealing with the compression of the information generated by the different sensors that can be embarked on it.

Usually on-board, depending of the mission, there are three different kind of sensors: Panchromatic, VNIR and SWIR. Apart from the optics and focal plane arrays for each sensor, the payload includes a specific processing element for each sensor, which provides the information in a specific formatted stream. This formatted data are stored in a Mass Memory Unit (MMU) or are directly processed on the fly. All the solutions provided in this Thesis are able to process the information on the fly, and make it ready either to be sent to ground through the satellite downlink or to be stored in the MMU. Ancillary data, telemetry information or other type of data could be also necessary to send to ground. For the sake of saving downlink bandwidth, sometimes it is also necessary to compress this kind of one-dimensional information [33, 34].

Electronic circuits used in space applications are typically several generations behind of those used on ground, at least in terms of complexity and performance. However, this has changed in the last years with the availability of very high performance technologies and solutions, such as Field-Programmable Gate Arrays (FPGAs) or parallel processors. This fact is transferring to the design for space applications the problems intrinsically linked to the highly complex solutions of embedded systems with the aggravation of the problems related to radiation and thus the needed robustness. This section deals with all the related constraints that are important to consider in this Thesis. These topics may be technological, methodological or may be related to the applications themselves.

#### **1.2.1** Hardware on-board satellites