### UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS DE TELECOMUNICACIÓN

#### PROYECTO FIN DE CARRERA

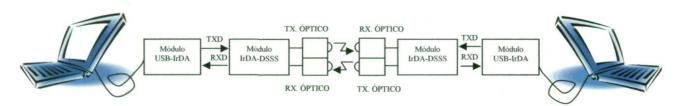

Sistema de comunicación óptica no guiada basado en tecnología IrDA y técnicas DSSS

Autor: D. Adolfo Eduardo García Braun

Tutores: Dr. José Alberto Rabadán Borges

D. Miguel Ángel Bacallado Marrero

Fecha: Julio 2005

# UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS DE TELECOMUNICACIÓN

# PROYECTO FIN DE CARRERA

Sistema de comunicación óptica no guiada basado en tecnología IrDA y técnicas DSSS

**HOJA DE FIRMAS**

Alumng

Fdo.: D. Adolfo Eduardo García Braun

**Tutor**

Fdo.: Dr. José Alberto Rabadán Borges Tutor

Fdo.: D. Miguel Ángel Bacallado Marrero

Fecha: Julio 2005

### UNIVERSIDAD DE LAS PALMAS DE GRAN CANARIA

# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS DE TELECOMUNICACIÓN

#### PROYECTO FIN DE CARRERA

Sistema de comunicación óptica no guiada basado en tecnología IrDA y técnicas DSSS

### **HOJA DE EVALUACIÓN**

Calificación: SOBRESALJENTE SO (M.A.)

**Presidente**

Fdo.: VAROUND BY ARMAS SARA

Vocal

Fdo.: For José Cobrer Angida

Secretarie

Fdo.: FERNAND OF LA PLEAST ARRATT

Fecha: Julio 2005

Las ciencias tienen las raíces amargas, pero muy dulces los frutos...

Aristóteles

## **Dedicatorias**

A mis padres, por hacer que mis sueños se convirtieran en realidad y por estar ahí cuando los necesitaba

A mi novia, Bea, que ha vivido junto a mí día tras día, apoyándome durante estos 6 años en la distancia

A todos y cada uno de los miembros de mi familia, que tanto me han animado cuando me encontraba alicaído

A la memoria de mis abuelos: Adolfo y Guillermo...

# Agradecimientos

¿Qué sería de este proyecto sin la inestimable ayuda y apoyo de mis tutores? Espero haber estado a la altura de sus expectativas. Muchas gracias, José y Miguel Ángel.

#### Gracias también a:

Rafa por guiarme sabiamente hacia el buen camino.

Chago por compartir su sabiduría conmigo.

Iván por echarme un cable en el estudio de los entresijos de las señales.

Los hermanos Navarro, Víctor y Héctor, por ayudarme en los problemas técnicos.

Mi compañero de laboratorio, Arthemy, que ha vivido mis alegrías y tristezas además de auxiliarme en algunos momentos del proyecto.

La mejor y más simpática oficial de laboratorio: Ayaya.

# Índice general

# **MEMORIA**

| I. Introducción                                     | 1                                       |

|-----------------------------------------------------|-----------------------------------------|

| 1. Introducción                                     | 1                                       |

| 2. Objetivos                                        |                                         |

| 3. Descripción del trabajo                          |                                         |

| 4. Medios materiales                                |                                         |

| T. IVIOUIOS IIIIIOITIIIOS                           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|                                                     |                                         |

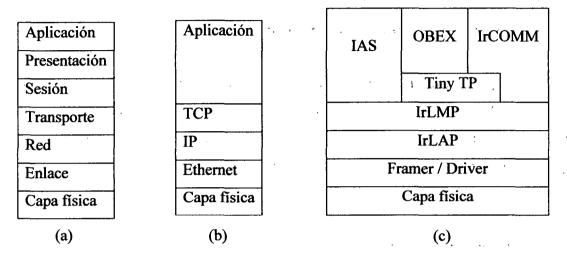

| II. IrDA                                            | 9                                       |

| 1. Historia                                         | 9                                       |

| 2. Conceptos básicos                                |                                         |

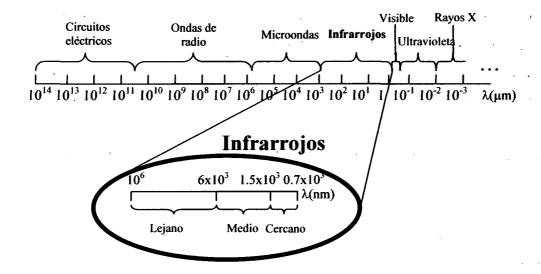

| 2.1 Luz infrarroja                                  |                                         |

| 2.2 Acceso al medio                                 |                                         |

| 2.3 Tasa de datos                                   | 13                                      |

| 2.4 Consumo de potencia                             | 14                                      |

| 2.4 Protocolo                                       | 15                                      |

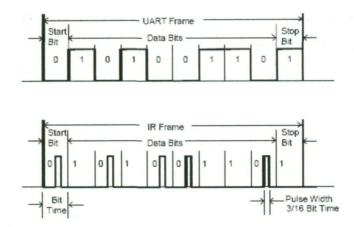

| 3. La capa física                                   | 16                                      |

| 3.1 Características ambientales                     |                                         |

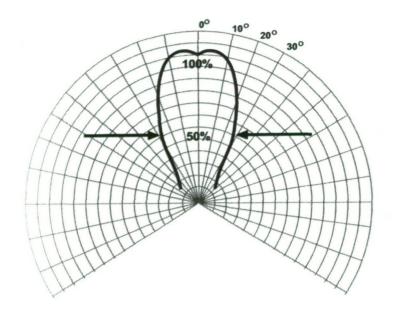

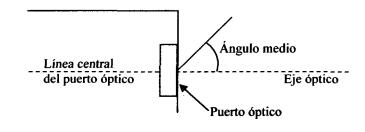

| 3.2 Características del infrarrojo                  |                                         |

| 3.3 Transmitiendo un pulso                          |                                         |

| 3.4 Detectando un pulso                             |                                         |

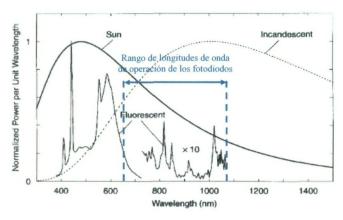

| 3.5 Interferencias de otras fuentes lumínicas       |                                         |

| 3.6 Restricciones del enlace                        |                                         |

| 3.7 Restricciones de los transmisores               |                                         |

| 3.8 Restricciones de los receptores                 |                                         |

| 3.9 Características de los sistemas de codificación | 23                                      |

| 3.10 La ventana plástica                            |                                         |

| 4. Conclusiones                                     | 27                                      |

|                                                     |                                         |

| III. Espectro ensanchado                            | 29                                      |

| 1. Historia                                         |                                         |

| 2. Conceptos básicos                                | 32                                      |

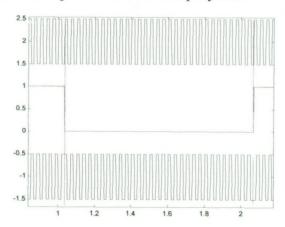

| 3. Señales de código                                |                                         |

|                                                     |                                         |

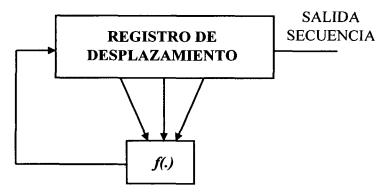

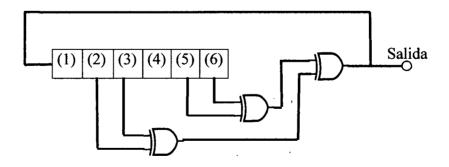

| 3.1. Señales pseudoaleatorias                       |                                         |

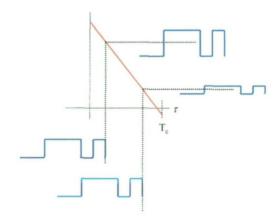

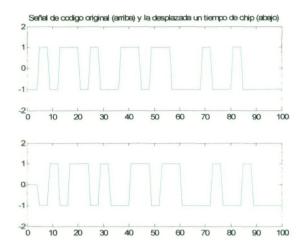

| 3.3. Autocorrelación de secuencias pseudoaleatorias | 37                                      |

|                                                     |                                         |

| 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

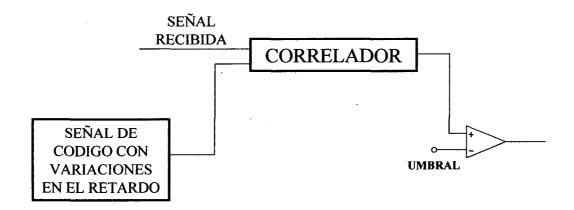

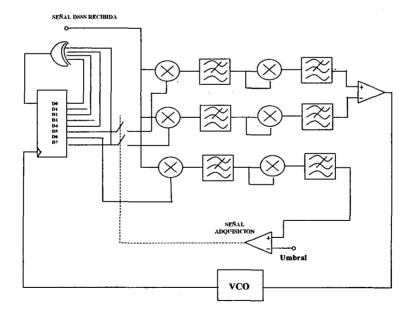

| 4.4. Reducción de la densidad espectral de potencia  5. Tipos de sistemas  6. DSSS  6.1 Generación y demodulación de la señal ensanchada 6.2 Sincronismo  7. Sistema de sincronismo basado en un piloto 8. Conclusiones  1. Introducción 2. Modelado del sistema IrDA 2.1 Esquema 2.2 Sistema sin interferencias 2.3. Sistema con AWGN 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA-DSSS 3.1 Esquema 3.2 Sistema sin interferencias 3.3 Sistema con interferencias 3.5. Sistema con AWGN 3.4. Sistema con AWGN 3.5. Sistema con AWGN 3.6. Sistema con interferencia de banda estrecha 3.7. Sistema con interferencia de banda estrecha 3.8. Sistema con receptor no sincronizado 3.9. Sistema con receptor no sincronizado 3.0. Sistema multicanal 4. Conclusiones  V. Diseño 2. Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39       |

| 4.4. Reducción de la densidad espectral de potencia  5. Tipos de sistemas  6. DSSS  6.1 Generación y demodulación de la señal ensanchada 6.2 Sincronismo  7. Sistema de sincronismo basado en un piloto 8. Conclusiones  1. Introducción 2. Modelado del sistema IrDA 2.1 Esquema 2.2 Sistema sin interferencias 2.3. Sistema con AWGN 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA-DSSS 3.1 Esquema 3.2 Sistema sin interferencias 3.3 Sistema con interferencias 3.5. Sistema con AWGN 3.4. Sistema con AWGN 3.5. Sistema con AWGN 3.6. Sistema con interferencia de banda estrecha 3.7. Sistema con interferencia de banda estrecha 3.8. Sistema con receptor no sincronizado 3.9. Sistema con receptor no sincronizado 3.0. Sistema multicanal 4. Conclusiones  V. Diseño 2. Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40       |

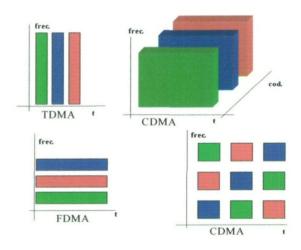

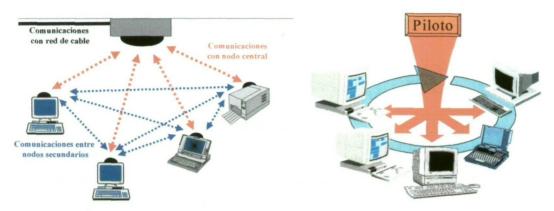

| 5. Tipos de sistemas 6. DSSS 6. I Generación y demodulación de la señal ensanchada 6.2 Sincronismo 7. Sistema de sincronismo basado en un piloto. 8. Conclusiones.  I Introducción 2. Modelado del sistema IrDA 2.1 Esquema 2.2 Sistema sin interferencias 2.3 Sistema con AWGN 2.4 Sistema con interferencia de luz fluorescente 2.6 Sistema IrDA SIR 3. Modelado del sistema IrDA-DSSS 3.1 Esquema 3.2 Sistema con interferencias 3.3 Sistema con AWGN 3.4 Sistema con AWGN 3.5 Sistema con interferencia de banda estrecha 3.5 Sistema con receptor no sincronizado. 3.6 Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquena general 3.2 Transmisor y PLD 3.2 I Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

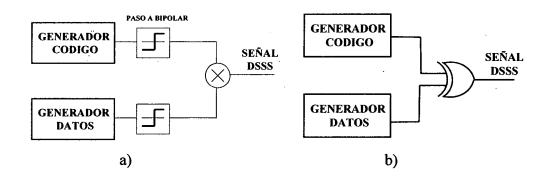

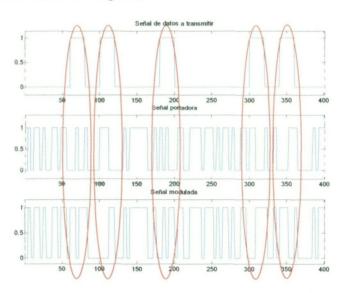

| 6. DSSS 6.1 Generación y demodulación de la señal ensanchada 6.2 Sincronismo 7. Sistema de sincronismo basado en un piloto 8. Conclusiones 1. Introducción 2. Modelado del sistema IrDA 2.1. Esquema 2.2. Sistema sin interferencias 2.3. Sistema con AWGN 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema in interferencia de luz fluorescente 3.1. Esquema 3.2. Sistema in interferencia de luz fluorescente 3.3. Sistema con interferencia de luz fluorescente 3.5. Sistema con receptor no sincronizado 3.6. Sistema con receptor no sincronizado 3.6. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

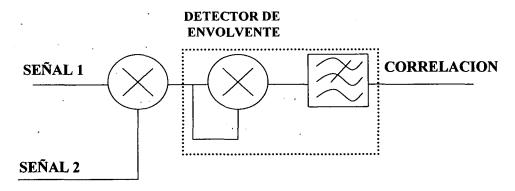

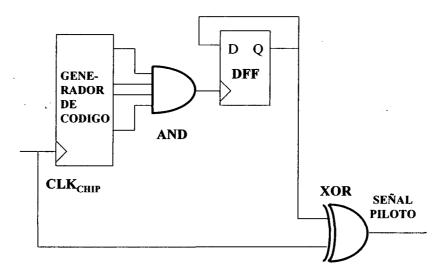

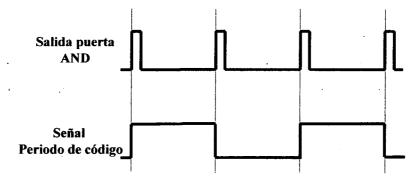

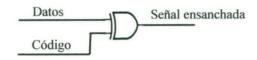

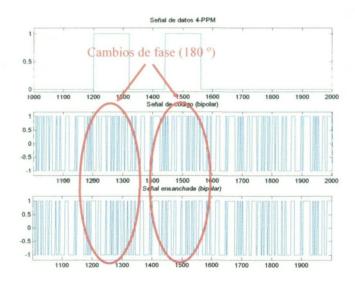

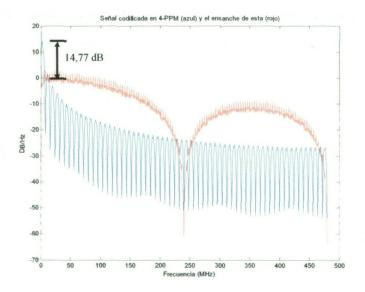

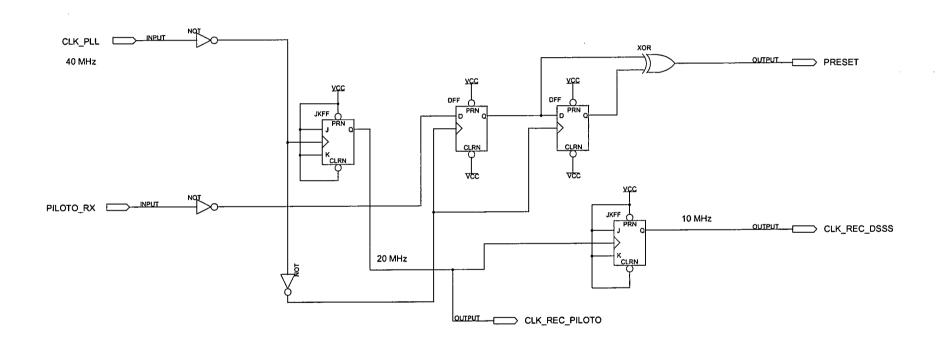

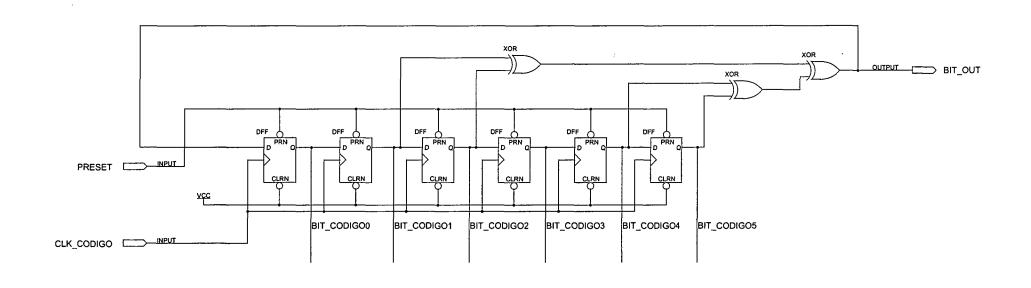

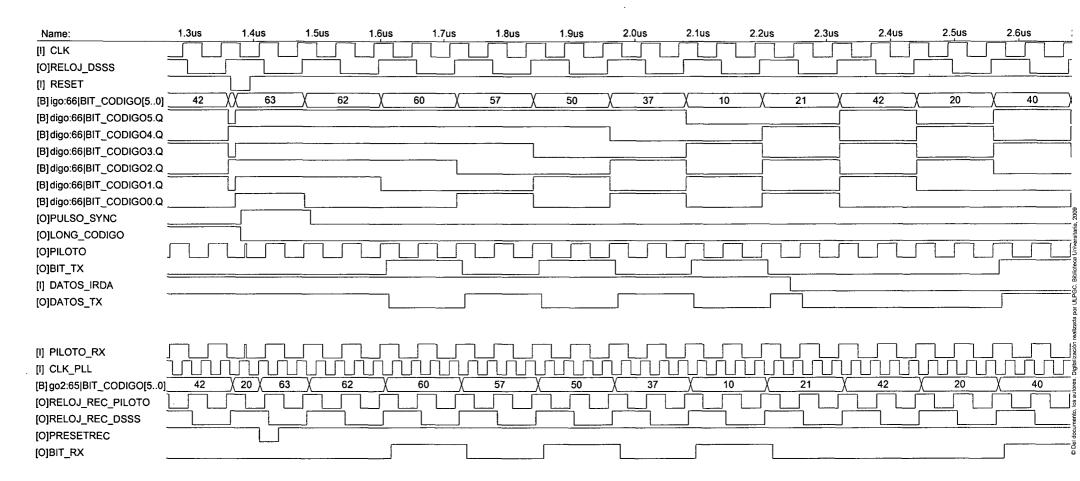

| 6.1 Generación y demodulación de la señal ensanchada 6.2 Sincronismo 7. Sistema de sincronismo basado en un piloto. 8. Conclusiones.  IV. Simulaciones.  1. Introducción. 2. Modelado del sistema IrDA. 2.1 Esquema 2.2 Sistema sin interferencias. 2.3 Sistema con AWGN. 2.4 Sistema con interferencia de luz fluorescente 2.6 Sistema irDA SIR. 3. Modelado del sistema IrDA-DSSS. 3.1 Esquema 3.2 Sistema sin interferencias. 3.3 Sistema con interferencias. 3.4 Sistema con interferencia de banda estrecha. 3.5 Sistema con interferencia de banda estrecha. 3.6 Sistema de banda estrecha. 3.7 Sistema con interferencia de banda estrecha. 3.8 Sistema con interferencia de banda estrecha. 3.9 Sistema con interferencia de banda estrecha. 3.1 Esquema general. 3.2 Transmisor y PLD a 3.2.1 Diseño digital del transmisor. |          |

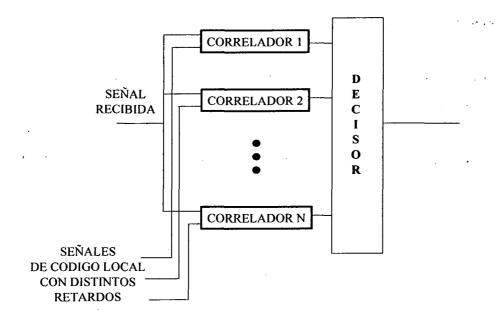

| 6.2 Sincronismo 7. Sistema de sincronismo basado en un piloto 8. Conclusiones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 7. Sistema de sincronismo basado en un piloto 8. Conclusiones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 8. Conclusiones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

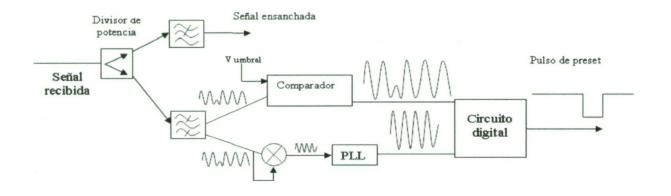

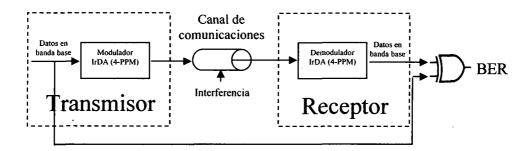

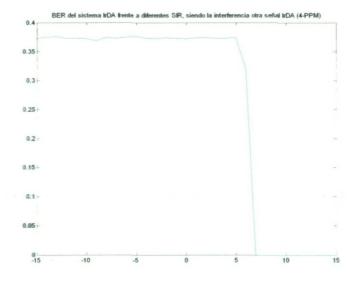

| IV. Simulaciones  1. Introducción  2. Modelado del sistema IrDA  2.1. Esquema  2.2. Sistema sin interferencias  2.3. Sistema con AWGN  2.4. Sistema multicanal  2.5. Sistema con interferencia de luz fluorescente  2.6. Sistema IrDA SIR  3. Modelado del sistema IrDA-DSSS  3.1. Esquema  3.2. Sistema sin interferencias  3.3. Sistema con AWGN  3.4. Sistema con interferencia de banda estrecha  3.5. Sistema con interferencia de banda estrecha  3.6. Sistema con receptor no sincronizado  3.6. Sistema multicanal  4. Conclusiones  V. Diseño  1. Introducción  2. Conversor USB-IrDA  2.1 Diseño  2.2 Aspecto físico  3. Módulo IrDA - DSSS  3.1 Esquema general  3.2 Transmisor y PLD  3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 1. Introducción  2. Modelado del sistema IrDA  2.1. Esquema  2.2. Sistema sin interferencias  2.3. Sistema con AWGN  2.4. Sistema multicanal.  2.5. Sistema con interferencia de luz fluorescente  2.6. Sistema IrDA SIR  3. Modelado del sistema IrDA-DSSS  3.1. Esquema  3.2. Sistema sin interferencias  3.3. Sistema con AWGN  3.4. Sistema con interferencia de banda estrecha  3.5. Sistema con receptor no sincronizado  3.6. Sistema multicanal  4. Conclusiones  V. Diseño  2. Conversor USB-IrDA  2.1 Diseño  2.2 Aspecto físico  3. Módulo IrDA - DSSS  3.1 Esquema general  3.2 Transmisor y PLD  3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34       |

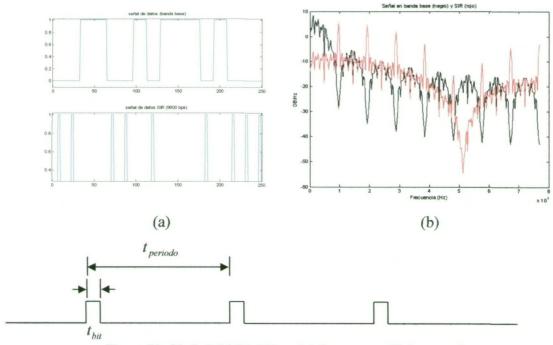

| 2. Modelado del sistema IrDA 2.1. Esquema 2.2. Sistema sin interferencias 2.3. Sistema con AWGN 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR 3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias 3.3. Sistema con AWGN 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con interferencia de banda estrecha 3.6. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .55      |

| 2. Modelado del sistema IrDA 2.1. Esquema 2.2. Sistema sin interferencias 2.3. Sistema con AWGN 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR 3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias 3.3. Sistema con AWGN 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con interferencia de banda estrecha 3.6. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

| 2.1. Esquema 2.2. Sistema sin interferencias 2.3. Sistema con AWGN. 2.4. Sistema multicanal. 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR. 3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias 3.3. Sistema con AWGN. 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal. 4. Conclusiones.  V. Diseño 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 2.2. Sistema sin interferencias 2.3. Sistema con AWGN. 2.4. Sistema multicanal. 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR. 3. Modelado del sistema IrDA-DSSS. 3.1. Esquema 3.2. Sistema sin interferencias. 3.3. Sistema con AWGN. 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal. 4. Conclusiones.  V. Diseño 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

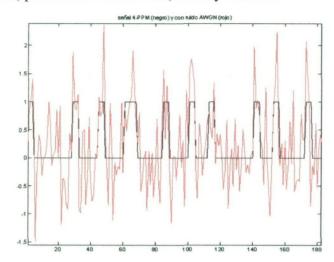

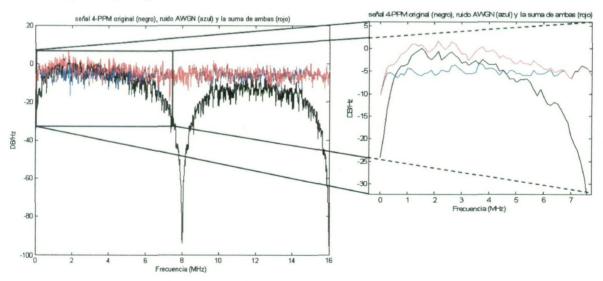

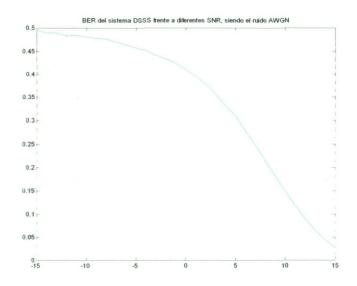

| 2.3. Sistema con AWGN. 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR 3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias 3.3. Sistema con AWGN 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 2.4. Sistema multicanal 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR 3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias 3.3. Sistema con AWGN 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

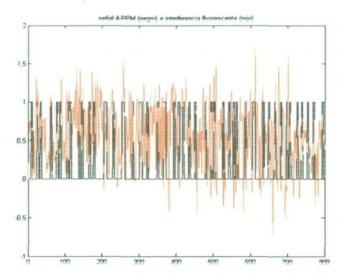

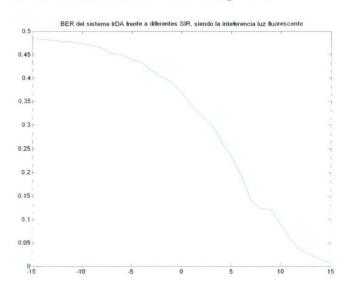

| 2.5. Sistema con interferencia de luz fluorescente 2.6. Sistema IrDA SIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 2.6. Sistema IrDA SIR  3. Modelado del sistema IrDA-DSSS 3.1. Esquema 3.2. Sistema sin interferencias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

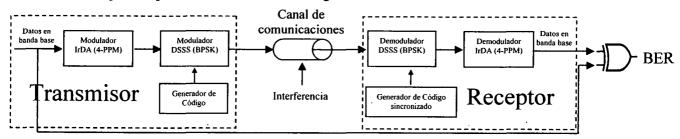

| 3. Modelado del sistema IrDA-DSSS 3.1 Esquema 3.2 Sistema sin interferencias 3.3 Sistema con AWGN 3.4 Sistema con interferencia de banda estrecha 3.5 Sistema con receptor no sincronizado 3.6 Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 3.1. Esquema 3.2. Sistema sin interferencias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

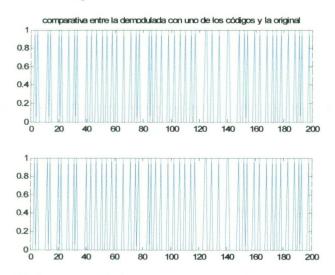

| 3.2. Sistema sin interferencias. 3.3. Sistema con AWGN. 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado. 3.6. Sistema multicanal. 4. Conclusiones.  V. Diseño. 2. Conversor USB-IrDA 2.1 Diseño. 2.2 Aspecto fisico. 3. Módulo IrDA - DSSS 3.1 Esquema general. 3.2 Transmisor y PLD. 3.2.1 Diseño digital del transmisor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

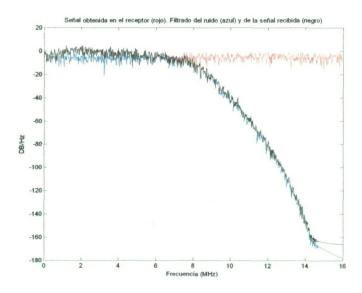

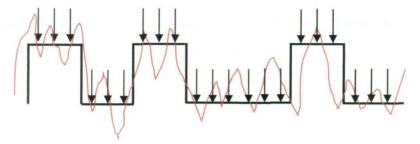

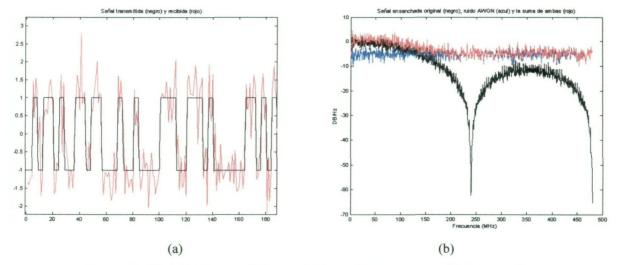

| 3.3. Sistema con AWGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70<br>71 |

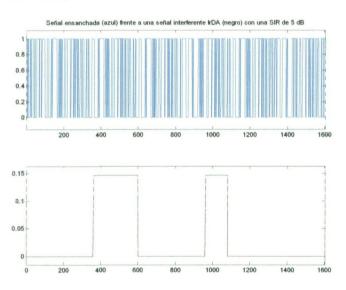

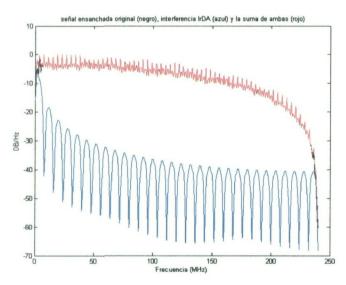

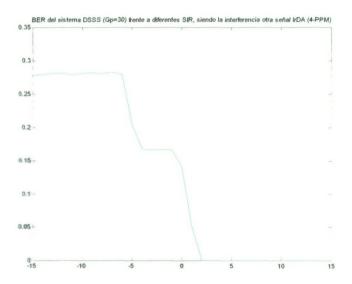

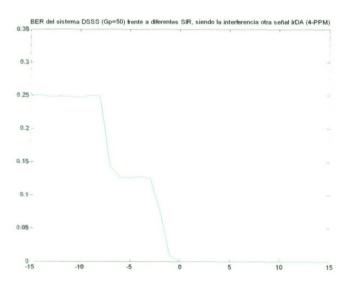

| 3.4. Sistema con interferencia de banda estrecha 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto fisico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 3.5. Sistema con receptor no sincronizado 3.6. Sistema multicanal 4. Conclusiones  V. Diseño 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

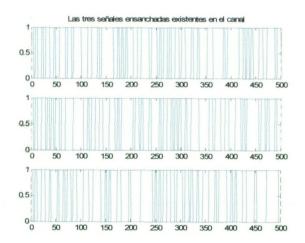

| 3.6. Sistema multicanal. 4. Conclusiones.  V. Diseño  1. Introducción  2. Conversor USB-IrDA  2.1 Diseño  2.2 Aspecto físico  3. Módulo IrDA - DSSS  3.1 Esquema general  3.2 Transmisor y PLD  3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 4. Conclusiones  V. Diseño  1. Introducción  2. Conversor USB-IrDA  2.1 Diseño  2.2 Aspecto físico  3. Módulo IrDA - DSSS  3.1 Esquema general  3.2 Transmisor y PLD  3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| V. Diseño                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 1. Introducción 2. Conversor USB-IrDA 2.1 Diseño 2.2 Aspecto físico 3. Módulo IrDA - DSSS 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 04       |

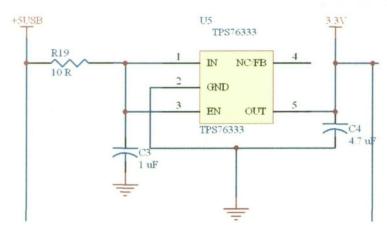

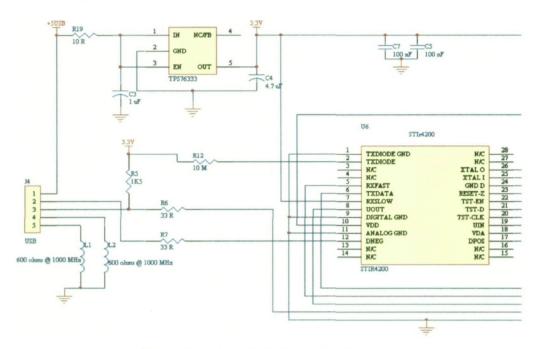

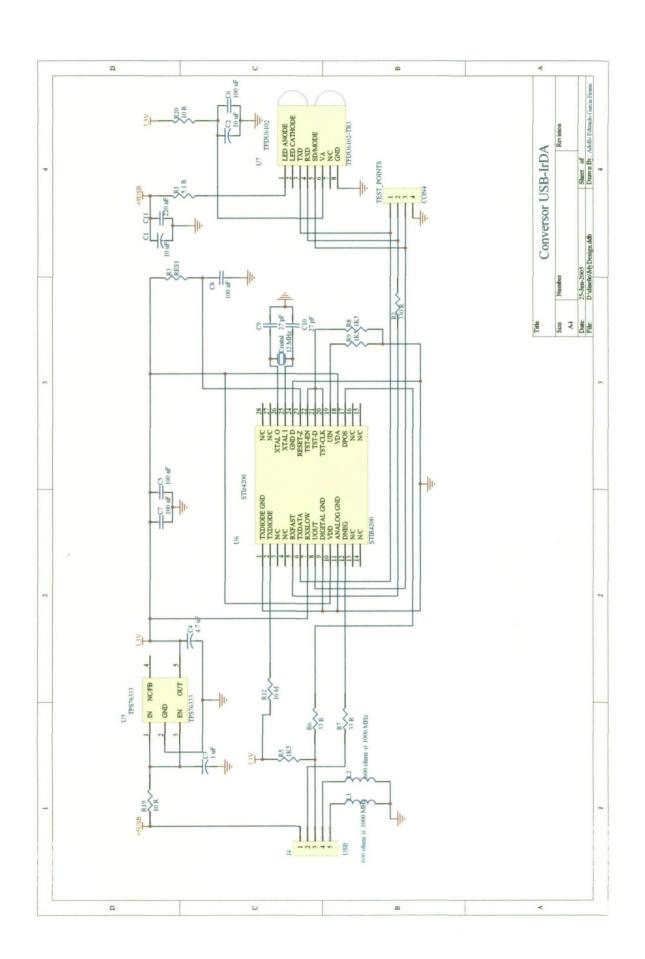

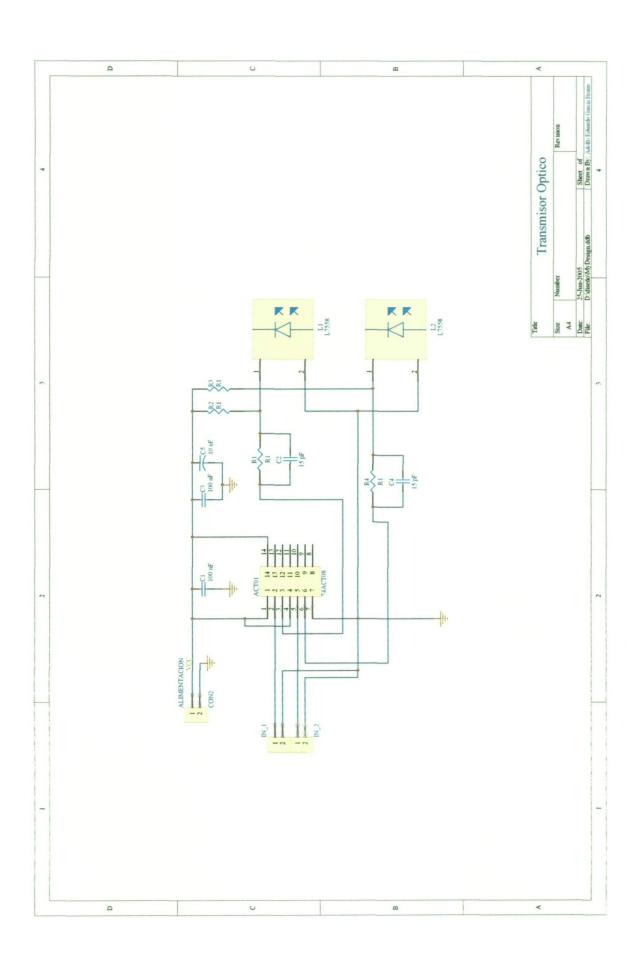

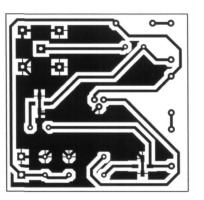

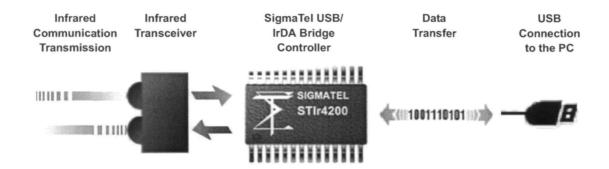

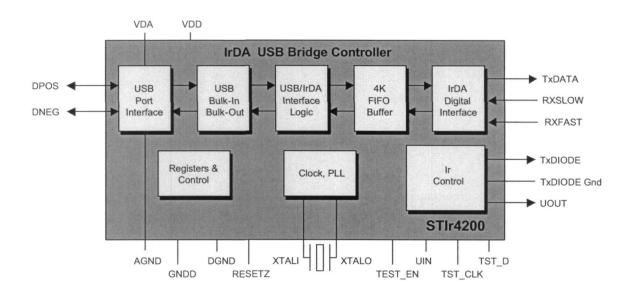

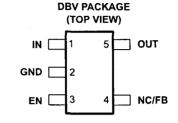

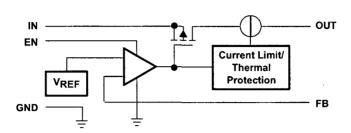

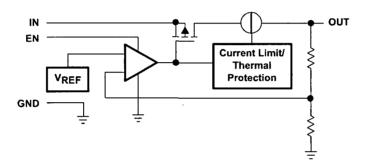

| 2. Conversor USB-IrDA 2.1 Diseño                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

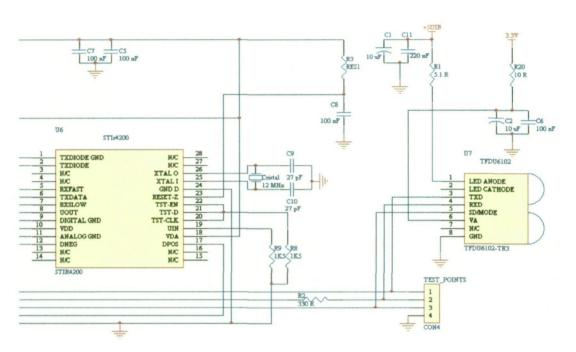

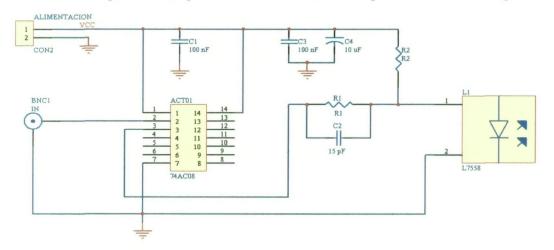

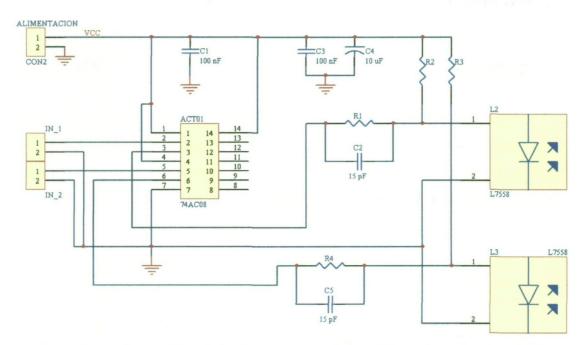

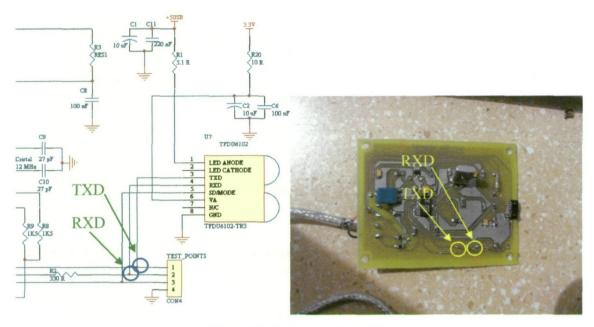

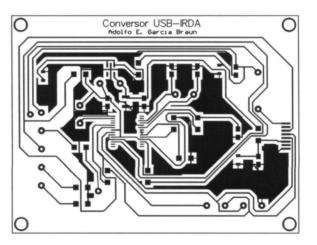

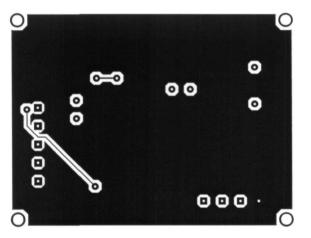

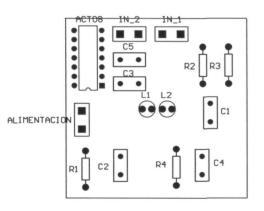

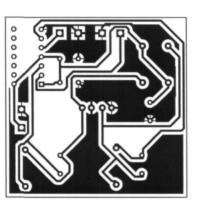

| 2.1 Diseño                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

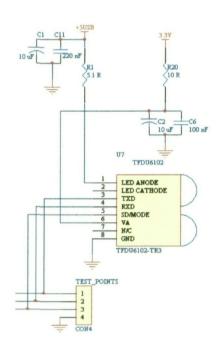

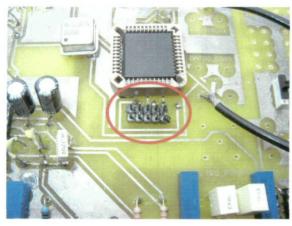

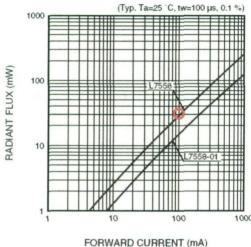

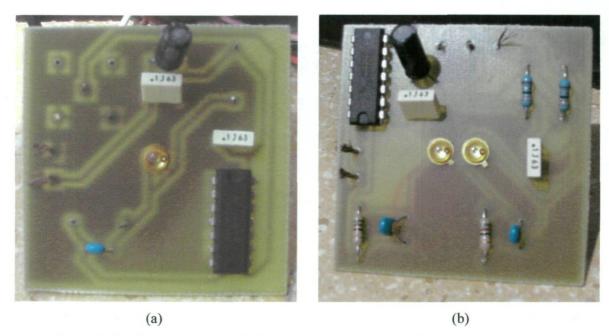

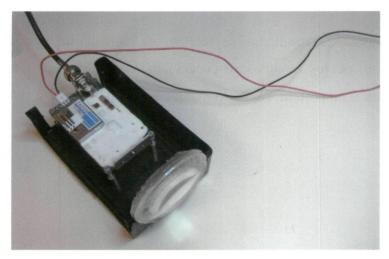

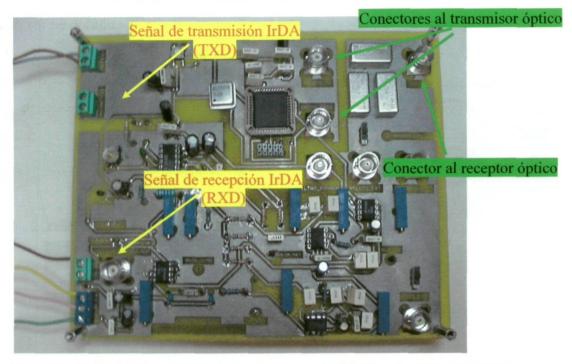

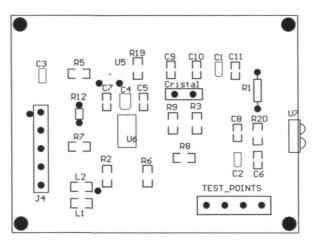

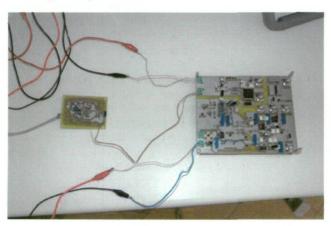

| 2.2 Aspecto físico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85       |

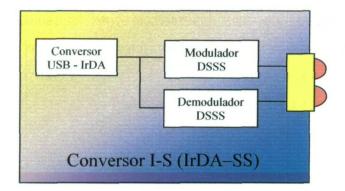

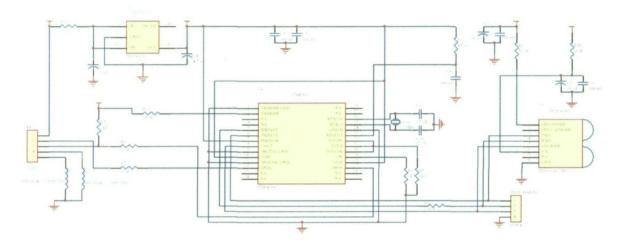

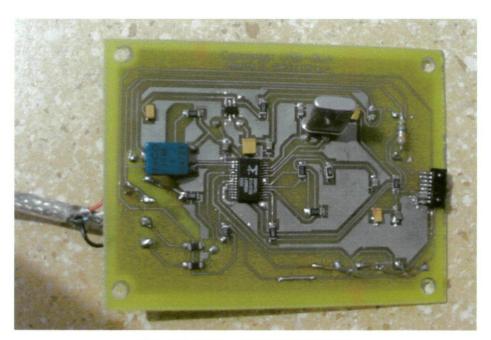

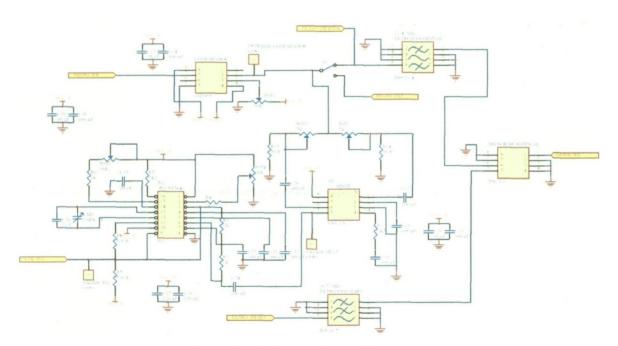

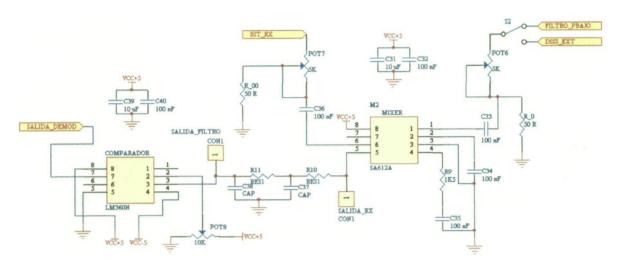

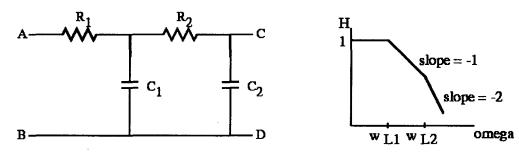

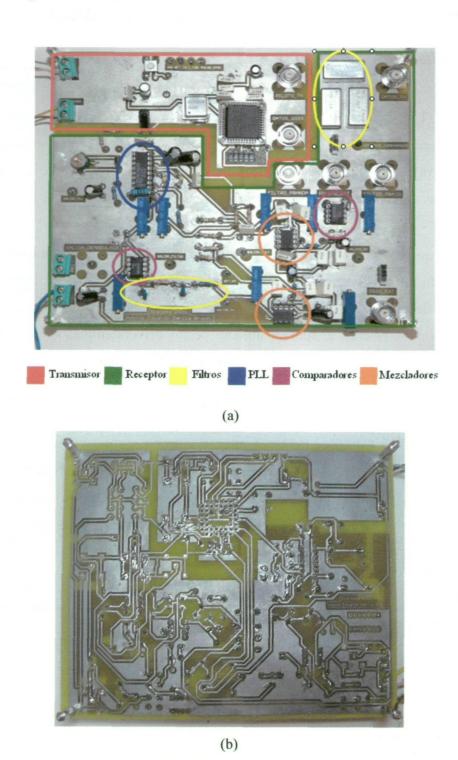

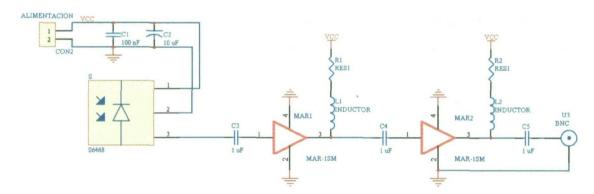

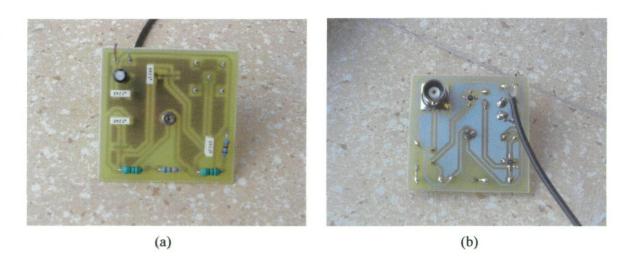

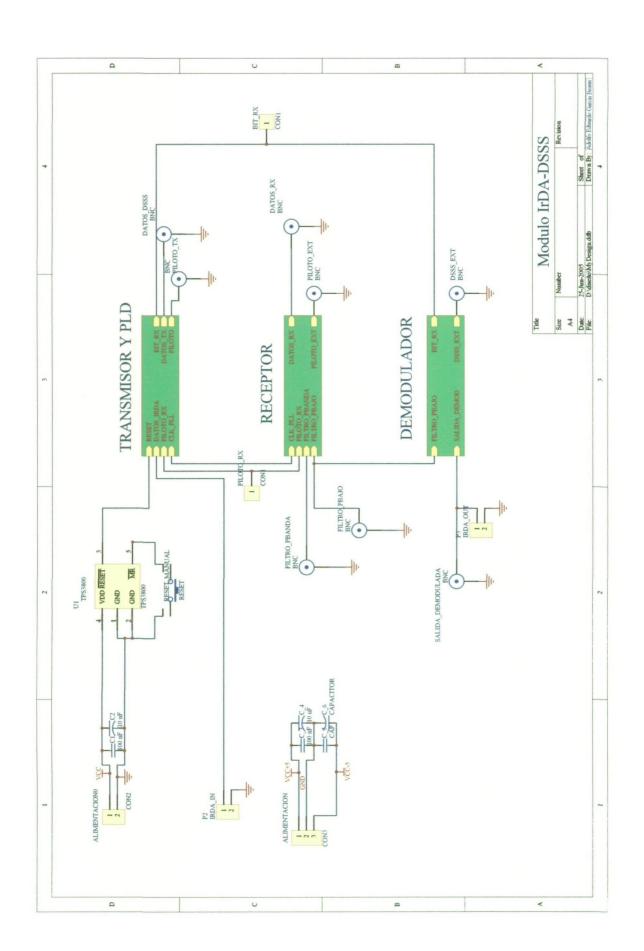

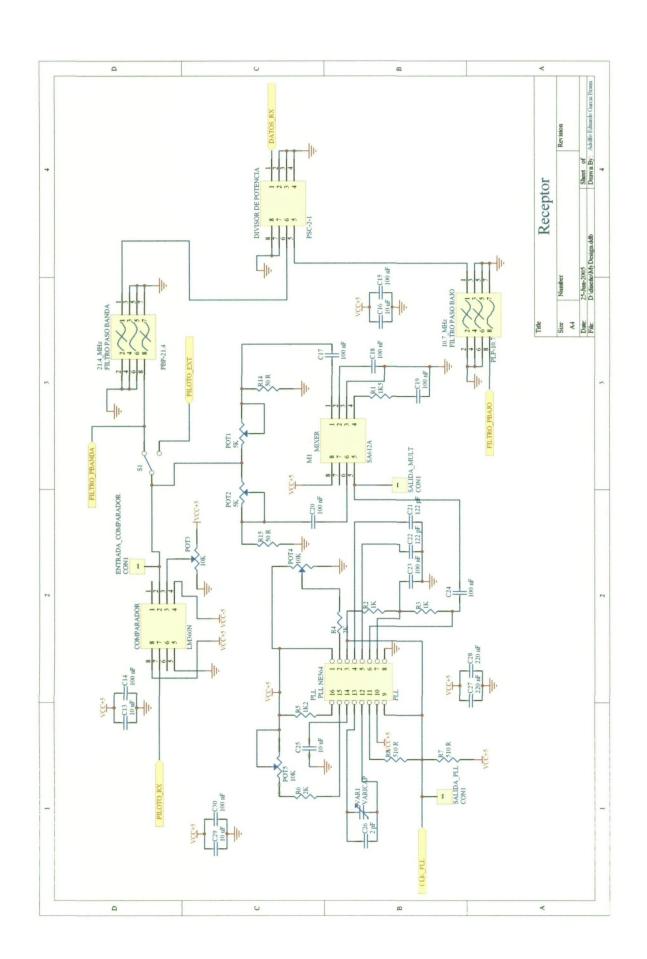

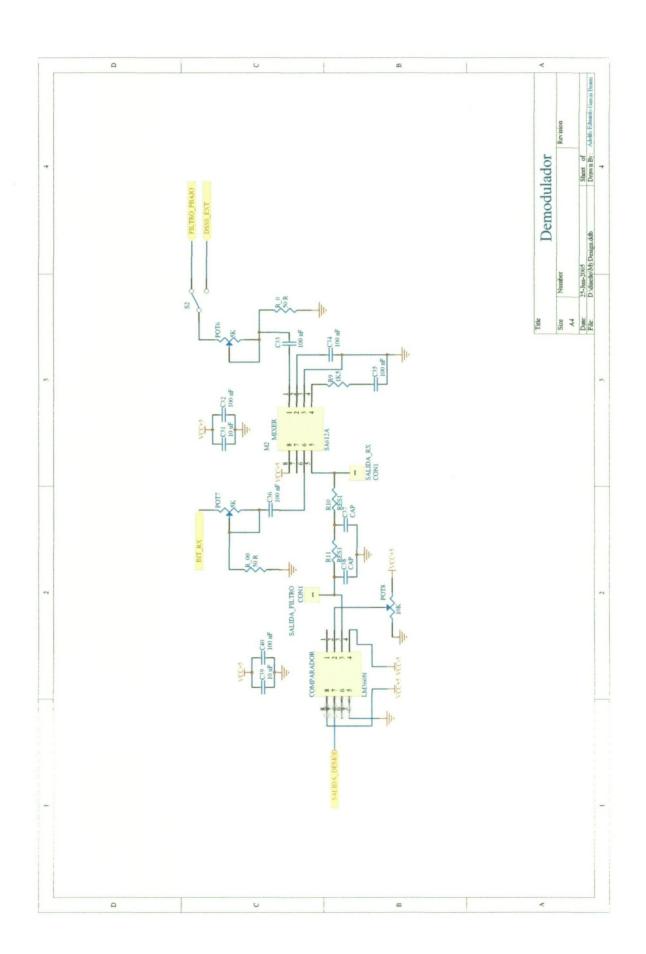

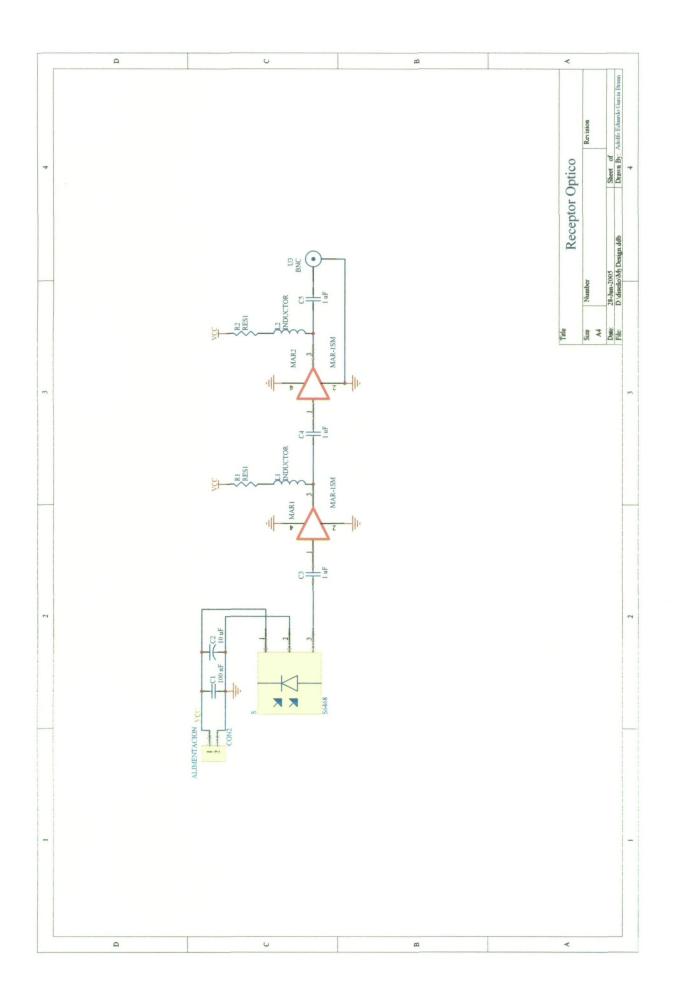

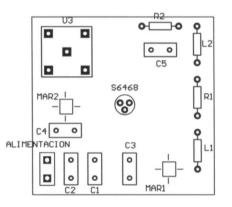

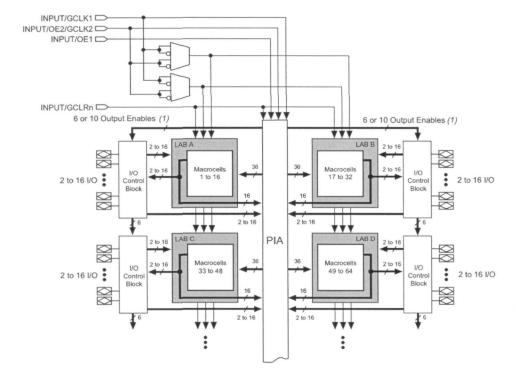

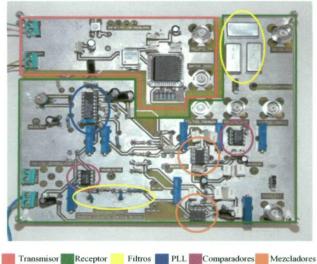

| 3. Módulo IrDA - DSSS  3.1 Esquema general  3.2 Transmisor y PLD  3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85       |

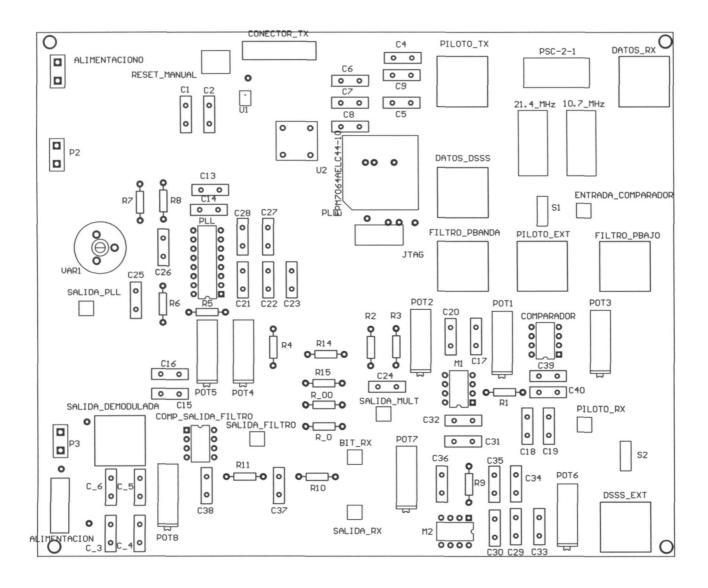

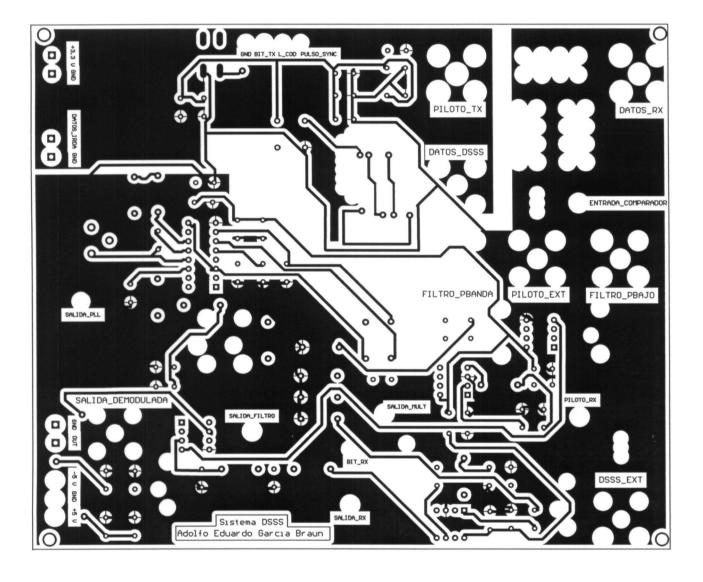

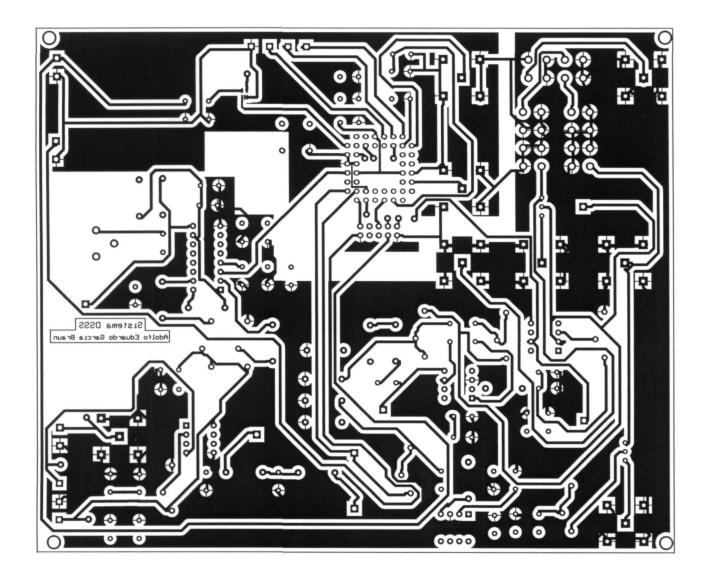

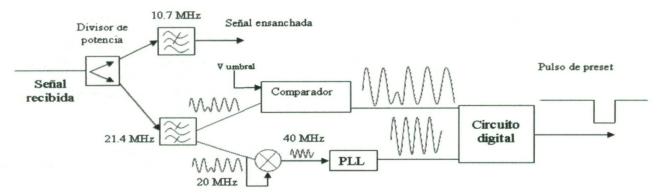

| 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91       |

| 3.1 Esquema general 3.2 Transmisor y PLD 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92       |

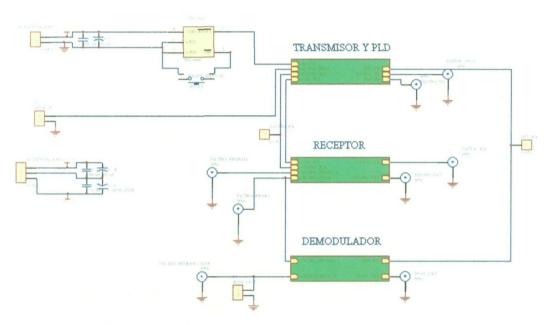

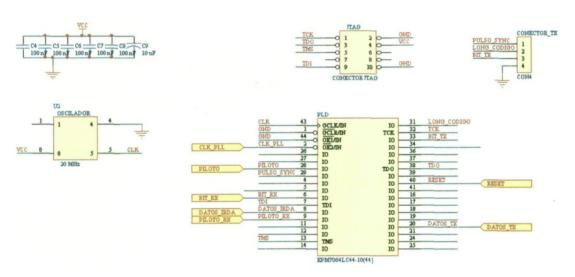

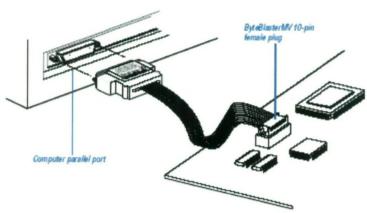

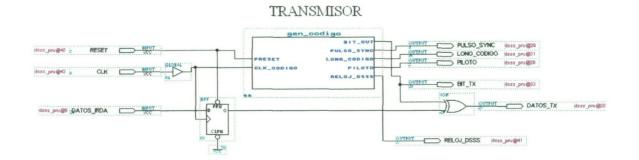

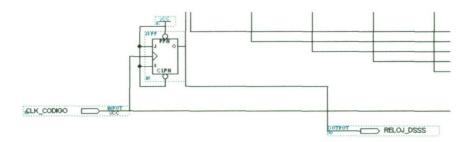

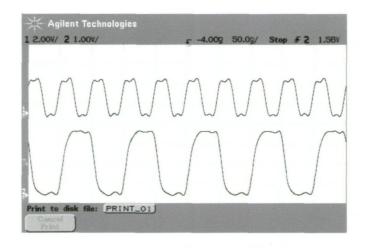

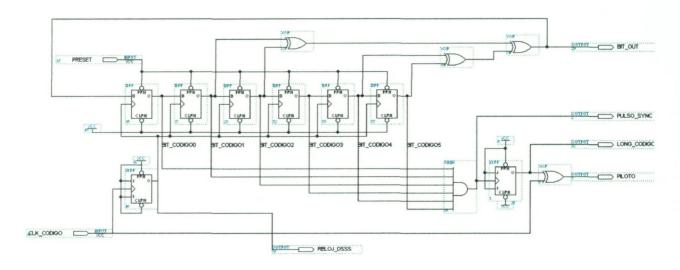

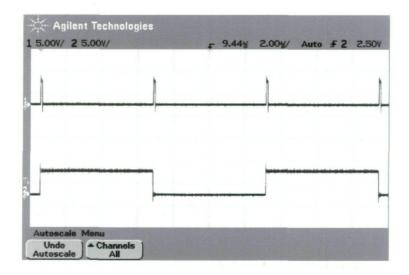

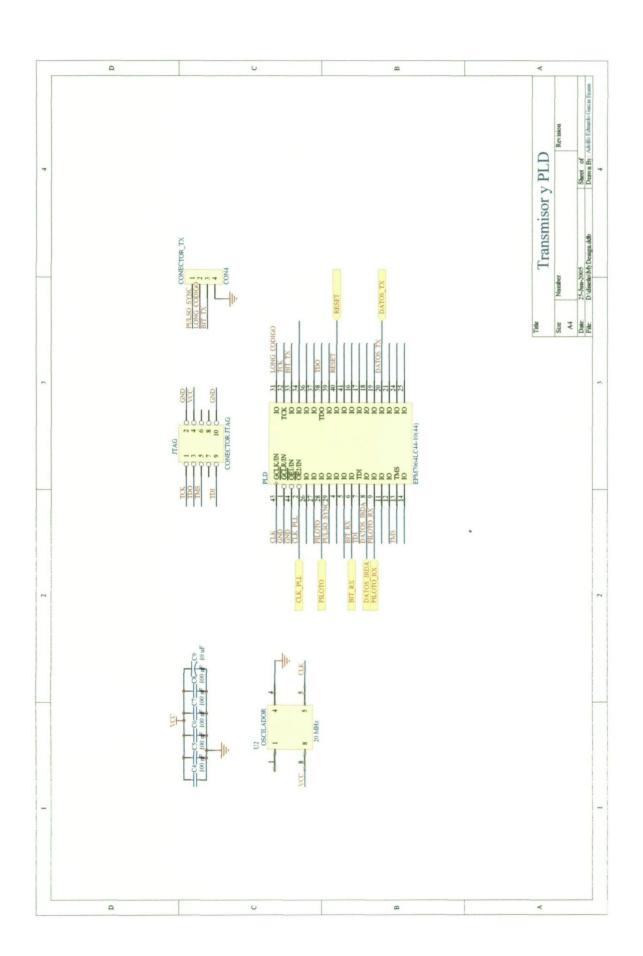

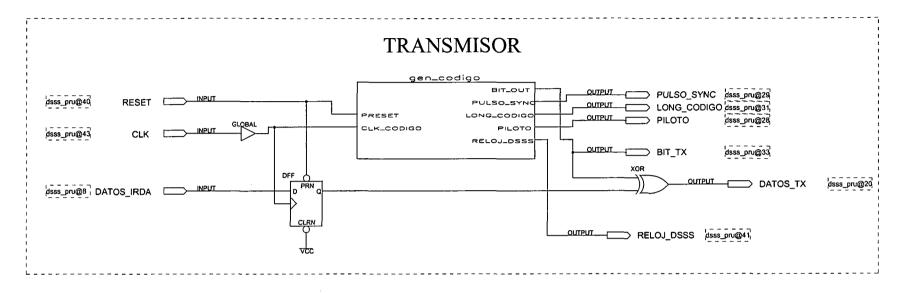

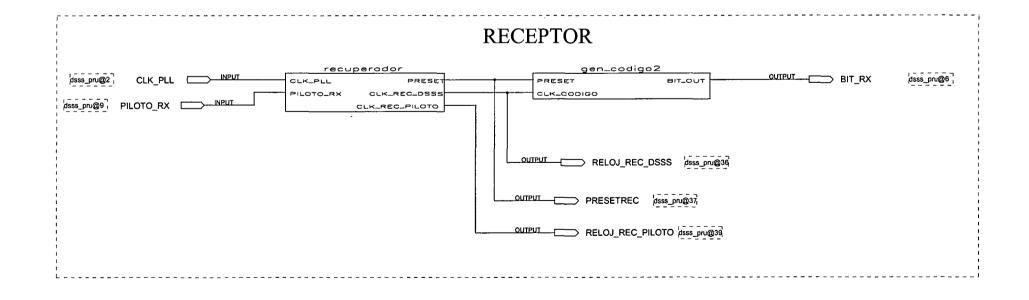

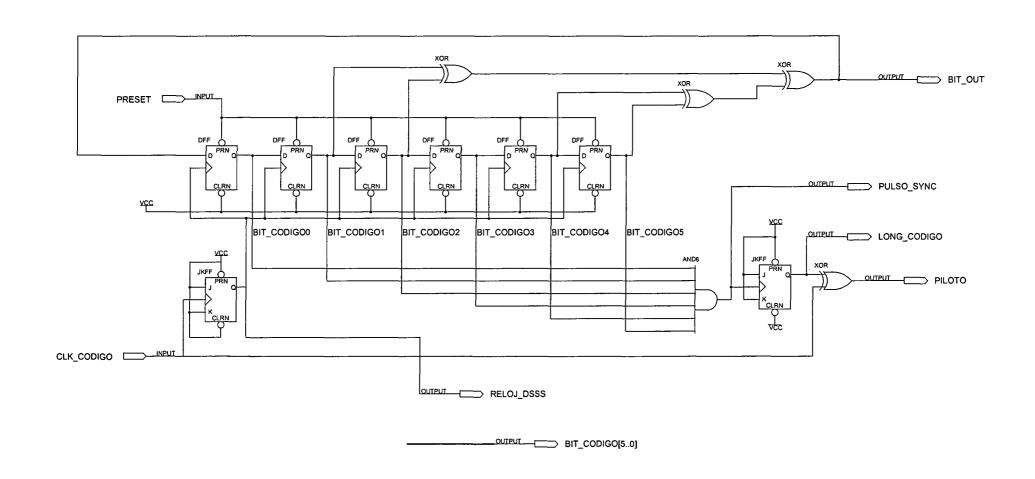

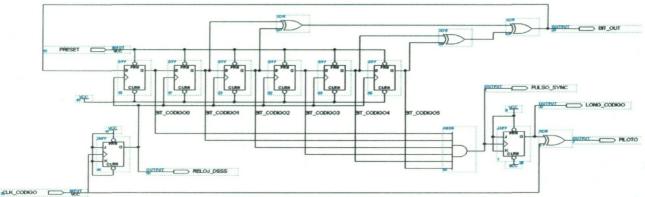

| 3.2 Transmisor y PLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

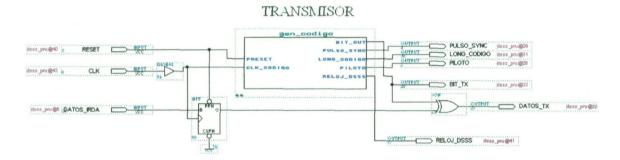

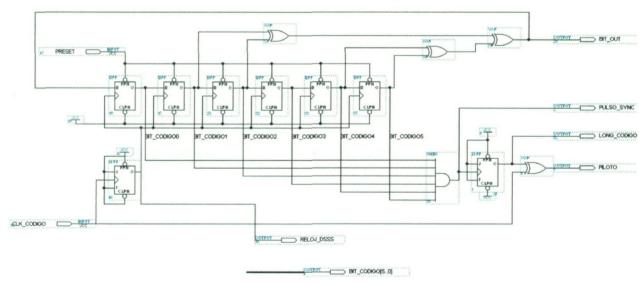

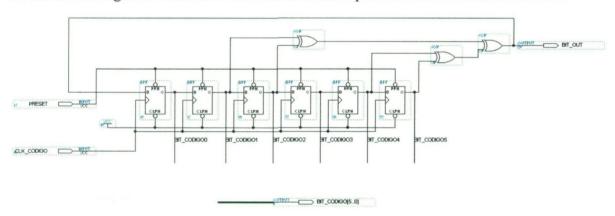

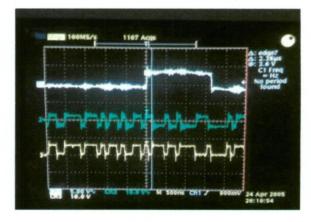

| 3.2.1 Diseño digital del transmisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |