# DISEÑO DE UN TRANSCEPTOR SÍNCRONO DE ESPECTRO ENSANCHADO POR SALTO RÁPIDO EN FRECUENCIA PARA COMUNICACIONES ÓPTICAS NO GUIADAS EN INTERIORES

Santiago T. Pérez

José A. Rabadán

Francisco A. Delgado

José R. Velázquez

Rafael Pérez

Departamento de Señales y Comunicaciones

Universidad de Las Palmas de Gran Canaria

e-mail: sperez@dsc.ulpgc.es

Abstract- In this paper, the design and experimental characterization of a Wireless Optical Fast Frequency Hopping Spread Spectrum (FFHSS) transceiver is presented. It has been designed for indoor applications and supposing a master transmitter emitting a pilot signal to synchronize all the receivers. The FHSS techniques are chosen due to their robustness against narrowband interferences and multipath propagation and because they allow to use Code Division Multiple Access (CDMA). The principal objective of this work is to study a full synchronous system in which each receiver is synchronized by a reference signal emitted by a central station.

#### I. INTRODUCCIÓN

Los sistemas de comunicaciones ópticas tienen la ventaja de no estar sujetos a regulación del espectro como los sistemas de radiofrecuencia. Como inconveniente debe destacarse que solo pueden cubrir areas más pequeñas que las conseguidas con los sistemas de radiofrecuencia. En recintos interiores es habitual que existan fuentes de interferencia óptica. Además existe distorsión por multitrayectoria al rebotar la señal óptica en los objetos del recinto [1]. Los sistemas de espectro ensanchado por secuencia directa (DSSS) y por salto en frecuencia (FHSS) presentan gran robustez a las interferencias y a la multitravectoria [2]. La transmisión de la señal se realiza según el estado de un generador de código pseudoaleatorio. El principal inconveniente de estos sistemas es la sincronización del generador de código en el receptor necesario para desensanchar la señal.

### II. SISTEMA FHSS SÍNCRONO EN EL CANAL ÓPTICO NO GUIADO

La señal de FHSS es una modulación digital pasobanda multifrecuencia, donde se transmite una frecuencia deacuerdo con el valor de la señal moduladora y el estado de un generador de código pseudoaleatorio. Los sistemas FHSS pueden ser de salto lento en frecuencia (SFHSS) o salto rápido en frecuencia (FFHSS) [3]. En la primera de ellas (SFHSS) se mantiene la portadora durante varios bits de datos, esta portadora es modulada en FSK por la señal de datos. En la segunda técnica (FFHSS) la frecuencia transmitida dura una fracción entera del tiempo de bit, a este intervalo se le llama tiempo de chip. El receptor, aunque conoce el código usado, necesita sincronizarlo para poder demodular la señal [4].

Existen costosas configuraciones circuitales de adquisición y seguimiento del sincronismo [5]. Para mejorar y facilitar este proceso se propone el uso de una señal piloto de sincronismo. La señal piloto lleva información de la frecuencia de chip y del comienzo del código del transmisor. Esta señal consiste en una modulación digital de fase (PSK) que tiene como portadora una frecuencia múltiplo de la frecuencia de chip y cambia su fase cada vez que el generador de código pseudoaleatorio inicia una nueva secuencia. Esta solución sólo es viable si se garantiza que no se interfiere la señal de sincronismo, esto es fácil de asegurar en el caso de sistemas de comunicaciones ópticos en interiores.

#### III. SISTEMA DISEÑADO

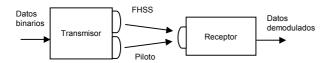

El diagrama de bloques del sistema diseñado se muestra en la figura 1, donde se comprueba que el transmisor emite la señal de FFHSS y de sincronismo por emisores ópticos distintos. La tasa binaria es de 512 kbits por segundo, se envían tres frecuencias por bit, por tanto resulta una tasa de 1,536 Mchips por segundo.

Fig. 1. Esquema del sistema global.

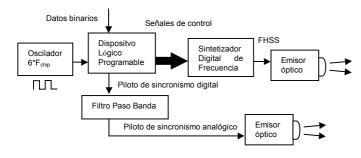

El diagrama de bloques del transmisor se muestra en la figura 2. La lógica digital del transmisor se integra en el dispositivo lógico programable EPM7128S de Altera. La lógica de control digital incluye un generador de código pseudoaleatorio del tipo MLS (*Maximum Lenght Sequence*) de 31 estados, el generador de sincronismo digital y la generación de las señales necesarias para el control del DDS. El DDS usado es el modelo AD9851 de Analog Devices.

Fig. 2. Sistema transmisor.

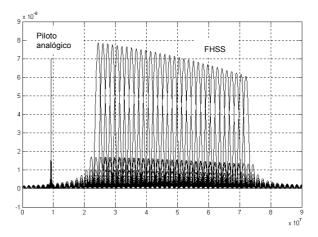

La frecuencia a transmitir de la señal de FHSS se elige de un conjunto de 32 frecuencias uniformementes distribuidas desde 24,384 MHz hasta 72 MHz en pasos de 1,536 MHz. La frecuencia es elegida con un código de 5 bits donde los 4 bits menos significativos se toman del generador de código pseudoaleatorio y como bit más significativo se toma el bit de datos. En la tabla 1 se muestra el código y la frecuencia asignada. Los módulos de los espectros de las 32 frecuencias de la señal de FHSS varían en amplitud según una función *sinc* (figura 3). El ancho de banda de la señal de FHSS vale 50,688 MHz y la ganancia de proceso 15,2 dB.

La señal piloto de sincronismo digital tiene portadora cuadrada. Para obtener la señal de sincronismo con portadora senoidal se usa un filtro paso banda. La señal de FHSS y la señal de sincronismo analógico son conectadas a dos emisores ópticos que usan el LED L7726 de Hamamatsu. La longitud de onda usada es de 650 nanómetros.

| Código | Número de frecuencia | Frecuencia<br>(MHZ) | Código | Número de frecuencia | Frecuencia<br>(MHZ) |

|--------|----------------------|---------------------|--------|----------------------|---------------------|

| 00000  | 0                    | 24,384              | 10000  | 16                   | 48,96               |

| 00001  | 1                    | 25,92               | 10001  | 17                   | 50,496              |

| 00010  | 2                    | 27,456              | 10010  | 18                   | 52,032              |

| 00011  | 3                    | 28,992              | 10011  | 19                   | 53,568              |

| 00100  | 4                    | 30,528              | 10100  | 20                   | 55,104              |

| 00101  | 5                    | 32,064              | 10101  | 21                   | 56,64               |

| 00110  | 6                    | 33,6                | 10110  | 22                   | 58,176              |

| 00111  | 7                    | 35,136              | 10111  | 23                   | 59,712              |

| 01000  | 8                    | 36,672              | 11000  | 24                   | 61,248              |

| 01001  | 9                    | 38,208              | 11001  | 25                   | 62,784              |

| 01010  | 10                   | 39,744              | 11010  | 26                   | 64,32               |

| 01011  | 11                   | 41,28               | 11011  | 27                   | 65,856              |

| 01100  | 12                   | 42,816              | 11100  | 28                   | 67,392              |

| 01101  | 13                   | 44,352              | 11101  | 29                   | 68,928              |

| 01110  | 14                   | 45,888              | 11110  | 30                   | 70,464              |

| 01111  | 15                   | 47,424              | 11111  | 31                   | 72                  |

Tabla 1. Frecuencias generadas para la señal de FHSS.

Fig. 3. Módulos de los espectros de las 32 frecuencias de la señal de FHSS y de la señal de sincronismo.

Como receptor óptico se usó el módulo C5331 de Hamamatsu. En la salida del receptor óptico se conectan los filtros que separan las dos señales recibidas. El recuperador de sincronismo obtiene la portadora de la señal de sincronismo. La portadora recuperada se conecta a la lógica digital, donde se extrae la señal de reloj a la frecuencia de chip necesaria para el generador de código pseudoaleatorio. Seguidamente se demodula síncronamente la señal de sincronismo recibida. La señal demodulada se pasa por un comparador y la salida del comparador se lleva a circuitos temporizadores que se encargan de compensar los retardos de los circuitos. Las salidas de estos temporizadores se combina para conseguir la señal de inicialización necesaria para sincronizar el estado del generador de código del receptor con el del transmisor.

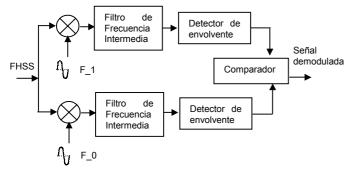

El demodulador es una típica estructura de doble rama como muestra el diagrama de bloques de la figura 4. A cada rama llega la señal de FHSS y un oscilador local. En la salida del detector de envolvente de la rama superior, detectora de unos, se tiene la señal de datos demodulada; y en la de la rama inferior, detectora de ceros, la señal de datos invertida. La salida final del demodulador se consigue comparado las salidas de las dos ramas.

Fig. 4. Demodulador.

Los dos osciladores locales necesarios en el demodulador se diseñaron usando dos DDS's del mismo tipo del transmisor. La lógica digital que controla los DDS's se diseñó usando el mismo dispositivo que en el transmisor. Esta lógica digital, que recibe como señales de entrada las provenientes del recuperador de sincronismo, incluye el generador de código pseudoaleatorio y la generación de las señales de control para los DDS's. El estado del generador de código se usa para sincronizar los dos DDS's. Uno de ellos (F\_0) oscila a la frecuencia de la señal de FHSS si el dato modulador fuese un "0" menos el valor de la frecuencia intermedia. El segundo oscilador (F\_1) oscila a la frecuencia de la señal de FHSS si el dato modulador fuese un "1" menos el valor de la frecuencia intermedia. La frecuencia intermedia del receptor vale 10,7 MHz.

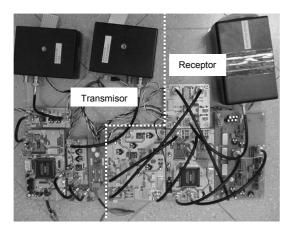

Finalmente el transmisor y el receptor se disponen como muestra la figura 5. Las señales transmitidas se hacen incidir en un espejo y la longitud aproximada del enlace óptico es de unos tres metros.

Fig. 5. Aspecto del equipo transceptor.

#### IV. MEDIDAS Y RESULTADOS

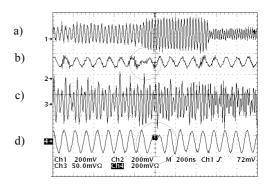

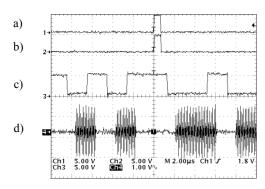

En las simulaciones se comprobó el funcionamiento ante la existencia de interferencia, propagación multitrayectoria y Ruido Blanco Gaussiano Additivo en el canal. En la figura 6 se muestra las señales de FHSS y el piloto de sincronismo analógico en el transmisor (tx) y receptor (rx). En la señal de sincronismo se señala un cambio de fase.

Fig. 6. a) FHSS (corriente en el LED, tx)

- b) Sincronismo (corriente en el LED, tx)

- c) FHSS (salida del filtro paso alto, rx)

- d) Sincronismo (salida del filtro paso banda, rx)

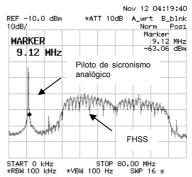

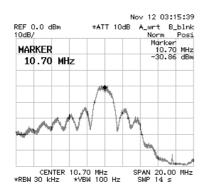

En la figura 7 se observa la Densidad Espectral de Potencia (DEP) obtenida en la salida del receptor óptico donde se comprueba la escasa interferencia mutua entre las señales de FHSS y el piloto de sincronismo debido a su separación frecuencial.

Fig. 7. DEP en la salida del receptor óptico.

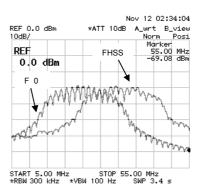

En la figura 8 se muestra la DEP de la señal de FHSS cuando se transmite un "0" y la DEP del oscilador local asociado en el demodulador.

Fig. 8. DEP de la señal de FHSS (tx) cuando se transmite un "0" y del oscilador local asociado (F\_0, rx).

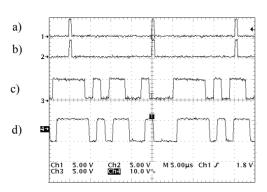

En la figura 9 se observa la señal de salida del filtro de frecuencia intermedia en la rama detectora de ceros del demodulador. Las dos primeras señales indican que transmisor y receptor se encuentran sincronizados. En la figura 10 se visualiza la DEP de salida del filtro de frecuencia intermedia de esta misma rama. En ella se comprueba que el lóbulo principal está centrado en 10,7 MHz y su ancho de

banda (3,072 MHz) se corresponde con el doble de la frecuencia de chip.

Fig. 9. a) Estado todo a "1" en el generador de pseudocódigo (tx).

- b) Estado todo a "1" en el generador de pseudocódigo (rx).

- c) Datos en el transmisor.

- d) Salida del filtro de frecuencia intermedia en la rama detectora de los ceros (rx).

Fig. 10. DEP de la salida del filtro de frecuencia intermedia en la rama detectora de los ceros (rx).

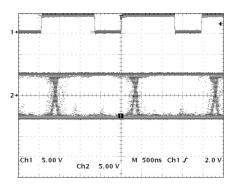

En la figura 11 se muestra la señal de datos binaria en el transmisor y la señal de datos demodulada en el receptor. En la figura 12 se observa el diagrama de ojo de la señal de datos demodulada.

Fig. 11. a) Estado todo a "1" en el generador de pseudocódigo (tx).

- b) Estado todo a "1" en el generador de pseudocódigo (rx).

- c) Datos (tx).

- d) Datos demodulados (rx).

Fig. 12. Diagrama de ojo de la señal de datos demodulada.

#### V. CONCLUSIONES

En este trabajo se presenta la caracterización experimental de un transceptor FFHSS para comunicaciones ópticas no guiadas en interiores. Se ha comprobado su funcionamiento frente a interferencias de banda estrecha, ruido y existencia de multitrayectos en el canal. Se reduce de forma significativa la complejidad en la sincronización del receptor por el uso de un piloto de sincronismo. Reprogramando la lógica digital se puede cambiar las frecuencias de la señal de FHSS y el código pseudoaleatorio usado.

## **AGRADECIMIENTOS**

Este trabajo se ha desarrollado gracias al proyecto de investigación CICYT TIC99-0932-C01 y a la Comunidad Autónoma de Canarias (PI2001-109).

## REFERENCIAS

- [1] F. A. Delgado, R. Pérez, J. A. Rabadán, F. J. López, "Design of fast frequency-hopping spread-spectrum system for wireless infrared communications", Electronics Letters, Vol.36, Nº 17, pp. 1510-1512, agosto de 2000.

- [2] Bernard Sklar, "Digital Communications. Fundamentals and Applications", Prentice-Hall, 1988.

- [3] Robert C. Dixon, "Spread Spectrum Systems", John Wiley & Sons, 1984.

- [4] Kamilo Feher, "Wireless Digital Communications: Modulation and Spread Spectrum Applications", Prentice Hall, 1995.

- [5] Marvin K. Simon, Jim K. Omura, Robert A. Scholtz, Barry K. Levitt, "Spread Spectrum Communications Handbook", McGraw-Hill Professional, abril de 1994.