# Diseño de un acelerador *hardware* FPGA para aplicaciones de *machine learning* usando plataforma virtual

Autor: D. Mario D. Guanche Hernández

Tutores: Dr. Pedro Pérez Carballo<sup>1,2</sup>, Dña. Sonia Raquel León Martín<sup>2</sup>

GITT (Sistemas Electrónicos), Diciembre 2020

<sup>1</sup>EITE (ULPGC) - <sup>2</sup>IUMA (ULPGC)

#### INTRODUCCIÓN

- Machine learning suele requerir de una carga computacional elevada, pero paralelizable, por lo que el uso de aceleradores hardware basados en FPGAs resulta idóneo.

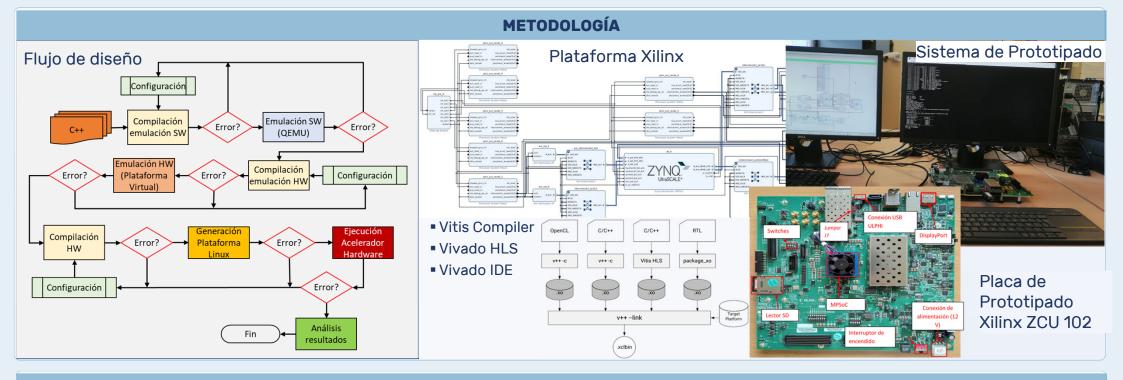

- La complejidad del diseño precisa de metodologías de diseño avanzadas que, desde C/C++, realizan la implementación del acelerador hardware. El uso de plataformas virtuales facilita el desarrollo.

- Se aplica la aceleración hardware a una clasificación mediante kmeans de imágenes hiperespectrales de cáncer de piel utilizando MPSoC Xilinx Zynq UltraScale+.

#### **OBJETIVOS**

- 01. Estudiar la arquitectura del dispositivo MPSoC FPGA

Zynq Ultrascale+ de Xilinx y sus principales bloques.

- 02. Estudiar diferentes alternativas de **clasificación** de *machine learning*.

- 03. Implementar una plataforma virtual para Zynq UltraScale+.

- 04. **Simula**r el sistema de clasificación mediante *machine learning* en la plataforma virtual y estudiar las **prestaciones** de la arquitectura.

- 05. Evaluar el diseño con aplicaciones reales.

## **RESULTADOS**

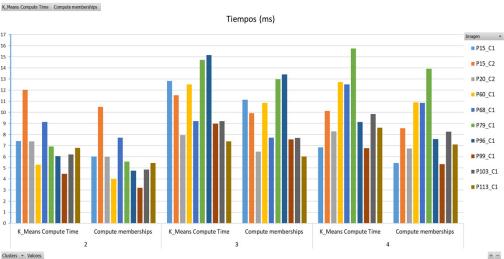

Tiempos de ejecución sobre el acelerador hardware del banco de imágenes de cáncer de piel (ms) para la computación total y la elección de los miembros del kernel.

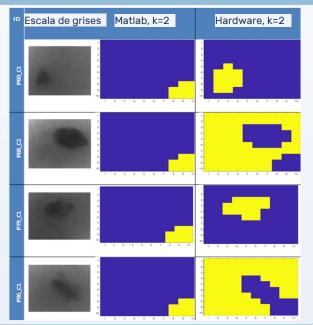

- Comparación de resultados con Matlab usando k=2 para imágenes hiperespectrales de cáncer de piel.

- Mejoras del acelerador Hardware

| Opción                | Compute<br>Membership | K-means<br>Compute<br>Time |

|-----------------------|-----------------------|----------------------------|

| Emulación<br>software | 1 674.28              | 1 765.00                   |

| Hardware              | 7.27                  | 9.35                       |

| Mejora<br>(Hw/Sw)     | x230.30               | x188.77                    |

## CONCLUSIONES

- Se ha realizado el diseño de un acelerador hardware basado en MPSoC FPGA a partir del modelo algorítmico C++ usando técnicas de diseño de alto nivel.

- Se utiliza el entorno Vitis de Xilinx para realizar la compilación del diseño y realizar su prototipado sobre una placa Xilinx ZCU102 que utiliza un dispositivo MPSoC Zyng UltraScale+.

- Se ha aplicado la metodología de diseño y prototipado para la aceleración hardware de un algoritmo kmeans.

- Los resultados aplicados a distintas imágenes hiperespectrales de cáncer de piel demuestran que se consigue un factor de aceleración de x189 para el computo del algoritmo, obteniendo su clasificación en menos de 10 ms.

## REFERENCIAS

- M. Kubat, An Introduction to Machine Learning. Springer International Publishing, 2015

- 2. Xilinx Inc, «ZCU102 Evaluation Board User Guide», 2019

- 3. Xilinx Inc, «Zynq UltraScale+ Device Technical Reference Manual», 2020

- 4. Xilinx Inc, «Vitis Unified Software Platform Documentation Application Acceleration Development», 2020