# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

Diseño de un Acelerador *Hardware* FPGA para Aplicaciones de *Machine Learning* usando Plataforma Virtual

Titulación: Grado en Ingeniería en Tecnologías de la

Telecomunicación

Autor: Mario Daniel Guanche Hernández

Tutores: Dr. Pedro Pérez Carballo

Sonia Raquel León Martín

Fecha: Diciembre de 2020

# ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

### TRABAJO FIN DE GRADO

Diseño de un Acelerador *Hardware* FPGA para Aplicaciones de *Machine Learning* usando Plataforma Virtual

### **HOJA DE EVALUACIÓN**

| Calificación: _      |            |

|----------------------|------------|

| Presidente           |            |

|                      |            |

| Fdo.:                |            |

| Vocal                | Secretario |

|                      |            |

| Fdo.:                | Fdo.:      |

| Fecha: Diciembre 202 | 20         |

### **AGRADECIMIENTOS**

Quisiera agradecer a mis tutores, Pedro Pérez Carballo y Sonia Raquel León Martín, quienes con su asesoramiento, tiempo y esfuerzo han facilitado la finalización de este trabajo. También, quiero agradecer a los encargados de soporte del Instituto Electrónico de Microelectrónica Aplicada la continua ayuda proporcionada para solucionar las diferentes incidencias que han surgido con las herramientas *software* empleadas en el trascurso de este proyecto y en definitiva a todas las personas que me han ayudado a conseguir este importante objetivo personal.

#### Resumen

En este Trabajo Fin de Grado (TFG) se pretende implementar y evaluar una aplicación de machine learning o aprendizaje automático [1]. Este concepto hace referencia a la rama dentro de la Inteligencia Artificial consistente en otorgar a una aplicación la capacidad de efectuar el análisis de los datos con el objetivo de identificar patrones. De esta manera, puede intuirse aspectos futuros relativos a una nueva entrada.

Para ello, se escoge el algoritmo *k-means*, el cual se define como un algoritmo de *machine learning* no supervisado. Los parámetros de entrada de este algoritmo consisten en una serie de elementos, los cuales son definidos por un mismo conjunto de atributos. La diferenciación de cada elemento se establece por medio de los valores que tomen sus atributos. El propósito del algoritmo será subdividir el conjunto de estos elementos en una cantidad fija de agrupaciones o clústeres especificada por el usuario. Estas agrupaciones se deberán realizar de acuerdo a las similitudes relativas de los elementos debido a sus valores de atributos, consiguiendo de manera simultánea la máxima diferenciación posible entre elementos que se encuentren en clústeres distintos.

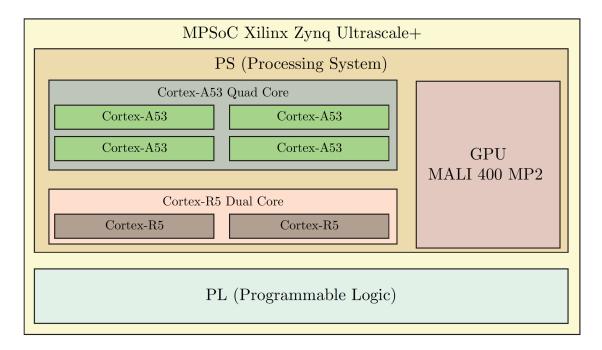

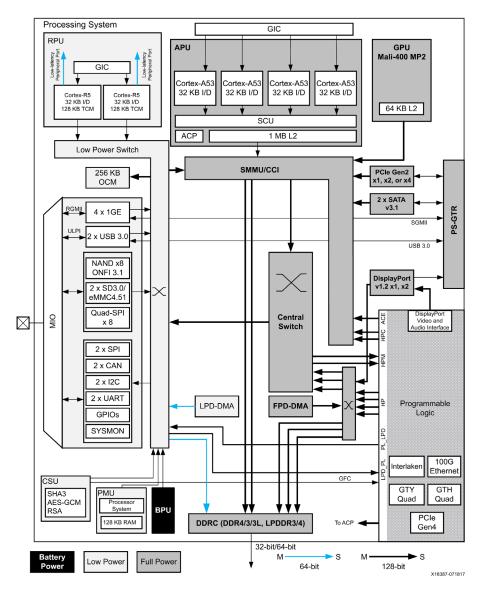

La arquitectura de la aplicación estará conformada por un sistema híbrido que combinará funcionalidad *software* y aceleración *hardware* implementada sobre una placa de prototipado MPSoC Zynq UltraScale+, siendo ZCU102 el modelo concreto. La aceleración *hardware* será llevada a cabo por una serie de unidades de cómputo denominadas *kernels*. La comunicación entre la funcionalidad *software* y el acelerador *hardware* se efectuará por medio de interfaces AXI4 y AXI4-Lite.

Los recursos presentes en la placa de prototipado utilizada se subdividen en el sistema de procesamiento (PS) y la lógica programable (PL). Respecto al PS, este contendrá los microprocesadores que ejecutarán la funcionalidad *software*, así como las interfaces de la placa de prototipado. Por otra parte, la PL contiene los recursos relativos al *hardware* programable, los cuales implementarán la arquitectura *hardware* de los *kernels* del proyecto.

La tarea a realizar consistirá en verificar el funcionamiento del proyecto *k-means* utilizado. Para ello, se dispondrá de varios ficheros, cada uno de los cuales con distintos elementos de entrada al proceso de *clustering*, obteniéndose una serie de resultados de salida que serán posteriormente comparados con los resultados esperados y definidos en otro archivo.

Para la programación del sistema se utilizará el lenguaje C/C++. No obstante, la programación *hardware* se efectuará mediante una descripción de alto nivel realizada de manera indirecta en OpenCL. Para ello, se utilizarán una serie de *wrappers*, los cuales traducirán la

descripción *hardware* especificada mediante una serie de objetos y funciones desarrolladas para C++, en invocaciones de recursos de OpenCL.

La compilación de la aplicación se realizará mediante la ejecución de un archivo *makefile*. Esta compilación vendrá acompañada de un proceso de análisis de las distintas prestaciones temporales y de la ocupación de recursos del diseño, verificando además que se satisfagan las restricciones exigidas. Estos informes serán visualizados por medio de la herramienta Vitis Analyzer.

#### **Abstract**

This work is intended to implement and assess a machine learning application [1]. The machine learning concept refers to the branch within Artificial Intelligence consisting of enabling an application to perform data analysis in a search for patterns. As a result, the application can predict aspects about new entries.

To make this work, the *k-means* algorithm is chosen, which is regarded as an unsupervised machine learning algorithm. Its input parameters are a series of elements defined by the same set of attributes, but whose values differ from one element to the other. This algorithm aims to subdivide the set of elements into a number of clusters specified by the user. The elements in a same cluster must have attribute values as similar as possible. At the same time, the algorithm must achieve the maximum difference between elements belonging to different clusters.

The physical means where application is executed will be the MPSoC Zynq UltraScale+ prototyping board, with ZCU102 being the specific model. The application's architecture consists of a hybrid system which combines software and hardware acceleration functionalities. Hardware acceleration will be carried out by several computing units called kernels. Data transfers between software programming and hardware accelerator will be managed by the AXI4 and AXI4-Lite interfaces.

The board to use contains resources that are subdivided into processing system (PS) and user-programmable logic (PL). Regarding the PS, it contains the microprocessors where software functionality is executed, as well as the interfaces of the prototyping board. On the other hand, the PL contains resources related to programmable hardware, which will implement the hardware architecture of the project's kernels.

The task to be carried out will consist of verifying the operation of the *k-means* project. As input data, there will be several input files available. These files will contain input elements for the clustering process, obtaining a series of output results that will be later compared to the expected results defined in another file.

C/C++ will be used as programming language. However, the architecture for hardware accelerator will be programmed through a high-level description made indirectly in OpenCL. For this purpose, a series of wrappers will be used to translate the hardware description specified by objects and functions developed for C ++ in calls to OpenCL resources.

The application's compilation will be done by running a makefile. This compilation comes together with an analysis of the design about its time performance and its use of PL resources. In this process, the hardware accelerator will be verified to comply with the constraints. These reports will be accessed through the Vitis Analyzer tool.

## ÍNDICE

| Mem     | noria |                                                                               | 1    |

|---------|-------|-------------------------------------------------------------------------------|------|

| Capítul | o 1.  | Introducción                                                                  | 1    |

| 1.1.    | Ant   | ecedentes                                                                     | 1    |

| 1.2.    | Obj   | etivos                                                                        | 2    |

| 1.3.    | Pet   | icionario                                                                     | 3    |

| 1.4.    | Esti  | ructura del documento                                                         | 3    |

| Capítul | o 2.  | Machine Learning                                                              | 5    |

| 2.1.    | Intr  | oducción                                                                      | 5    |

| 2.2.    | Cor   | nsideraciones preliminares                                                    | 6    |

| 2.:     | 2.1.  | Información de entrenamiento                                                  | 6    |

| 2.:     | 2.2.  | Búsqueda automatizada (Hill Climbing)                                         | 7    |

| 2.3.    | Clas  | sificación mediante análisis probabilístico (Bayes)                           | 8    |

| 2.4.    | Cla   | sificación por vecino más cercano                                             | . 12 |

| 2.5.    | Cla   | sificadores lineales y polinómicos                                            | . 14 |

| 2.      | 5.1.  | Clasificadores binarios de ecuación lineal                                    | . 15 |

| 2.      | 5.2.  | Clasificación en más de dos grupos mediante múltiples clasificadores binarios | . 18 |

| 2.      | 5.3.  | Determinación de ecuaciones polinómicas no lineales                           | . 18 |

| 2.6.    | Rec   | les neuronales                                                                | . 21 |

| 2.      | 6.1.  | Multilayer perceptron                                                         | . 22 |

| 2.      | 6.2.  | Radial-basis function network                                                 | . 27 |

| 2.7.    | Apr   | endizaje no supervisado                                                       | . 30 |

| 2.      | 7.1.  | Clustering                                                                    | . 30 |

| 2.8.    | Cor   | nclusiones                                                                    | . 35 |

| Capítul | o 3.  | Zynq UltraScale+ MPSoC                                                        | . 37 |

| 3.1.    | Intr  | oducción                                                                      | . 37 |

| 3.2.    | Sist  | ema de procesamiento                                                          | . 40 |

| 3.:     | 2.1.  | APU basada en ARM Cortex-A53                                                  | . 40 |

|      | 3.2.2  | 2.    | Real-Time Unit ARM Cortex R5             | 42 |

|------|--------|-------|------------------------------------------|----|

|      | 3.2.3  | 3.    | GPU ARM Mali-400                         | 43 |

|      | 3.2.4  | 1.    | Memoria PS                               | 44 |

|      | 3.2.5  | 5.    | Periféricos del PS                       | 45 |

| 3.3  | 3.     | PMU   | J y CSU                                  | 45 |

| 3.4  | 4.     | Ope   | ración de arranque                       | 46 |

| 3.   | 5.     | Lógi  | ca programable                           | 48 |

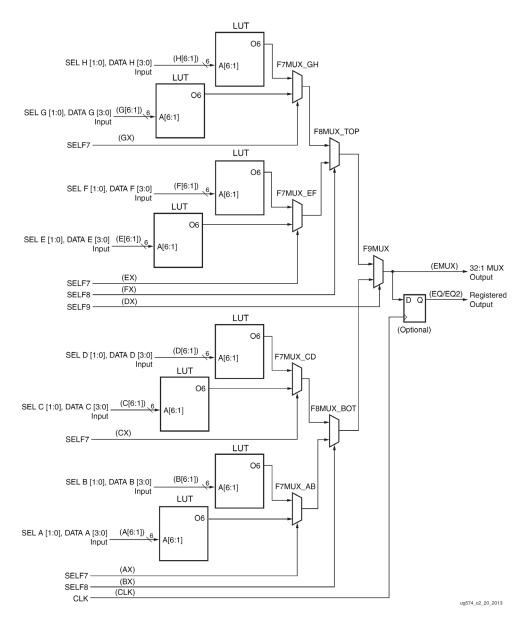

|      | 3.5.1  | L.    | CLBs                                     | 49 |

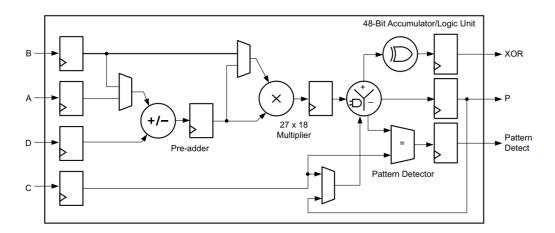

|      | 3.5.2  | 2.    | DSP                                      | 50 |

|      | 3.5.3  | 3.    | Memorias RAM                             | 51 |

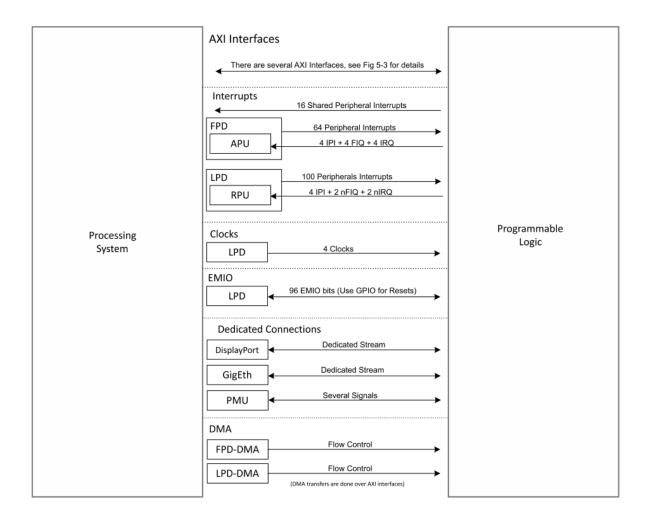

|      | 3.5.4  | 1.    | Intercomunicación PS – PL                | 52 |

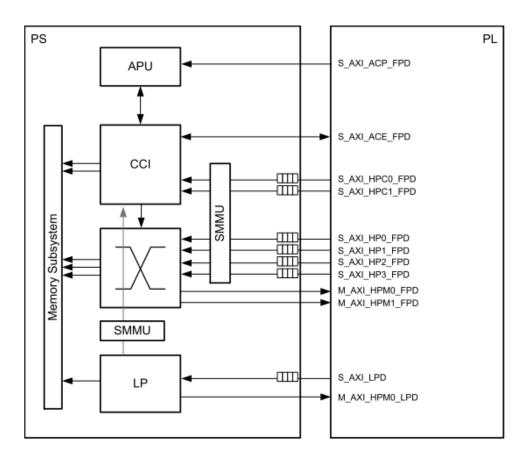

|      | 3.5.5  | 5.    | Interfaz AXI                             | 53 |

|      | 3.5.6  | 5.    | EMIO                                     | 55 |

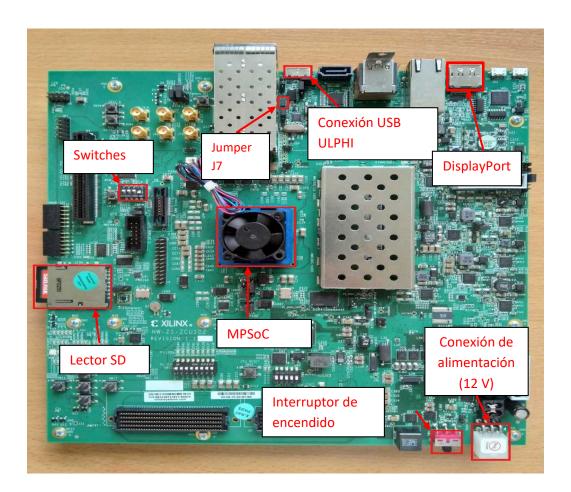

| 3.0  | 6.     | Plac  | a de prototipado                         | 57 |

| 3.   | 7.     | Con   | clusiones                                | 58 |

| Capí | tulo 4 | 4.    | Metodología de diseño                    | 61 |

| 4.   | 1.     | Intro | oducción                                 | 61 |

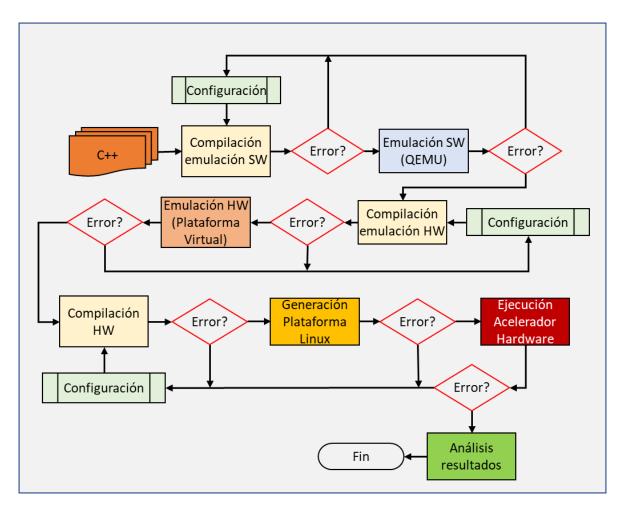

| 4.2  | 2.     | Emu   | llación software                         | 63 |

| 4.3  | 3.     | Emu   | ılación hardware                         | 63 |

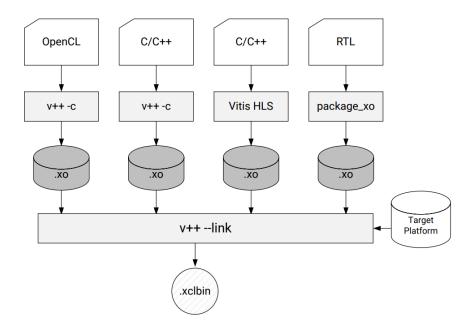

| 4.4  | 4.     | Com   | pilación para ejecución hardware         | 63 |

| 4.   | 5.     | Emp   | paquetado del sistema                    | 65 |

| 4.0  | 6.     | Con   | clusiones                                | 65 |

| Capí | tulo ! | 5.    | Proyecto kmeans                          | 67 |

| 5.:  | 1.     | Intro | oducción                                 | 67 |

| 5.2  | 2.     | Arqı  | uitectura de la aplicación <i>kmeans</i> | 67 |

| 5.3  | 3.     | Fund  | ción main                                | 68 |

| 5.4  | 4.     | fpga  | _kmeans                                  | 75 |

|      | 5.4.2  | l.    | fpga_kmeans_init                         | 75 |

|      | 5.4.2  | 2.    | fpga_kmeans_allocate                     | 77 |

|      | 5.4.3  | 3.    | fpga_kmeans_clustering                   | 79 |

|     | 5.4.4              | 4.         | fpga_kmeans_compute                                   | . 80 |

|-----|--------------------|------------|-------------------------------------------------------|------|

|     | 5.4.5              | 5.         | fpga_kmeans_deallocateMemory                          | . 86 |

|     | 5.4.6              | <b>5</b> . | fpga_kmeans_print_report                              | . 87 |

| 5   | .5.                | kme        | ans_clustering_cmodel.c                               | . 87 |

| 5   | .6.                | krnl       | kmeans                                                | . 91 |

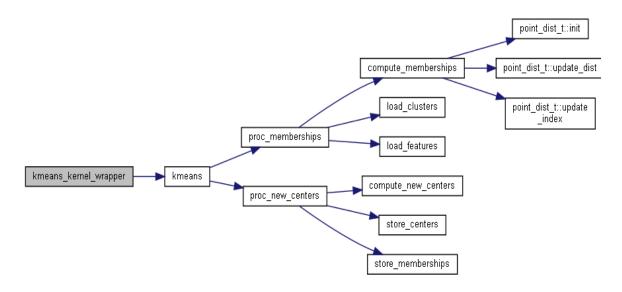

|     | 5.6.1              | 1.         | proc_memberships                                      | . 93 |

|     | 5.6.2              | 2.         | proc_new_centers                                      | . 98 |

| 5   | .7.                | time       | r.h                                                   | 101  |

| 5   | .8.                | krnl_      | _kmeans.ini                                           | 104  |

| 5   | .9.                | Cond       | clusiones                                             | 104  |

| Сар | ítulo (            | 6.         | Implementación del diseño de la plataforma en Vitis   | 105  |

| 6   | .1.                | Intro      | oducción                                              | 105  |

| 6   | .2.                | Com        | pilación del proyecto                                 | 106  |

| 6   | .3.                | Adaı       | otación a la placa ZCU102                             | 107  |

| 6   | .4.                | Cons       | strucción del diseño                                  | 109  |

|     | 6.4.1              | 1.         | Análisis de la emulación software "sw_emu"            | 111  |

|     | 6.4.2              | 2.         | Análisis de la emulación hardware "hw_emu"            | 113  |

|     | 6.4.3              | 3.         | Arquitectura de la plataforma                         | 119  |

|     | 6.4.4              | 4.         | Análisis de la implementación "hw"                    | 125  |

| 6   | .5.                | Cond       | clusiones                                             | 138  |

| Сар | ítulo <sup>·</sup> | 7.         | Resultados                                            | 139  |

| 7   | .1.                | Intro      | oducción                                              | 139  |

| 7   | .2.                | Emu        | laciones software y hardware                          | 139  |

| 7   | .3.                | Ejec       | ución sobre acelerador hardware Xilinx ZCU102         | 141  |

| 7   | .4.                | Clasi      | ficación de imágenes hiperespectrales                 | 144  |

| 7   | .5.                | Com        | parativa ejecución software y con acelerador hardware | 153  |

| 7   | .6.                | Cond       | clusiones                                             | 154  |

| Сар | ítulo (            | 8.         | Conclusiones y líneas futuras                         | 155  |

| 8   | .1.                | Cond       | clusiones                                             | 155  |

| •   | •                  | . ,        |                                                       | 150  |

| Bibliogra | ıfía                     | . 159 |

|-----------|--------------------------|-------|

| Presu     | puesto                   | . 165 |

| 1.1.      | Costes recursos hardware | . 165 |

| 1.2.      | Costes recursos Software | . 166 |

| 1.3.      | Costes recursos humanos  | . 166 |

| 1.4.      | Coste total              | . 166 |

| Pliego    | de Condiciones           | . 171 |

| 1.1.      | Introducción             | . 171 |

| 1.2.      | Recursos Hardware        | . 171 |

| 13        | Recursos Software        | 171   |

### ÍNDICE DE FIGURAS

| Figura 1: Arquitectura del dispositivo MPSoC Zynq UltraScale+ [4]                               | 2   |

|-------------------------------------------------------------------------------------------------|-----|

| Figura 2: Ejemplo estados en el algoritmos de hill-climbing [7]                                 | 8   |

| Figura 3: Clasificación mediante ecuación lineal (izquierda) y otra de grado superior (derecha) |     |

| Figura 4: Estructuración de una red neuronal perceptron multicapa de 2 capas [8]                |     |

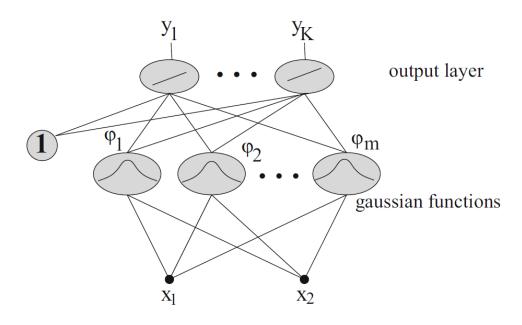

| Figura 5: Red neuronal basada en funciones radiales [8]                                         |     |

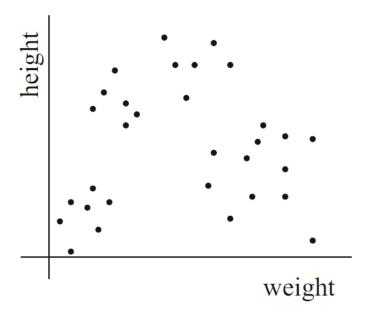

| Figura 6: Distribución de muestras en un espacio bidimensional [8]                              |     |

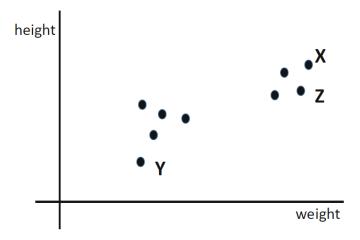

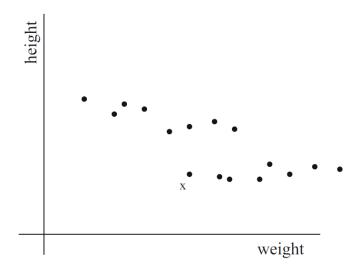

| Figura 7: Ejemplo de distribución de muetras donde k-means no sería eficaz [8]                  |     |

| Figura 8: Diagrama de bloques de la arquitectura Zynq UltraScale+ MPSoC [14]                    |     |

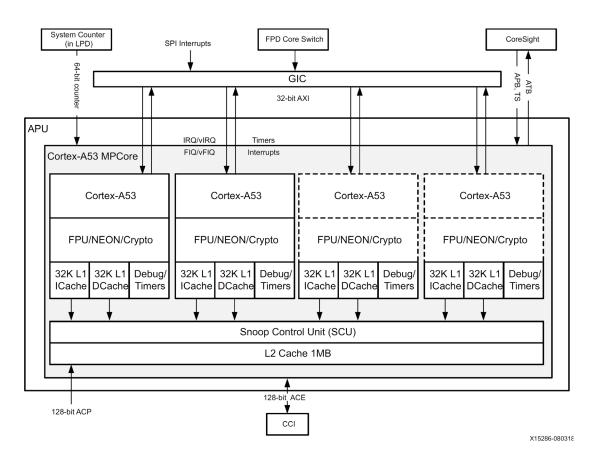

| Figura 9: Diagrama de bloques de la APU [15]                                                    |     |

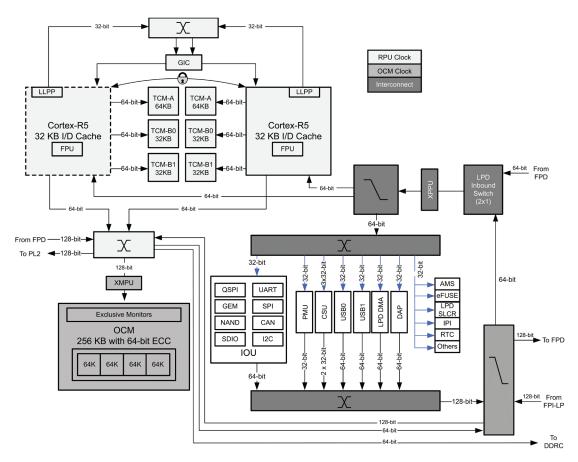

| Figura 10: Vista general de la RPU [15]                                                         |     |

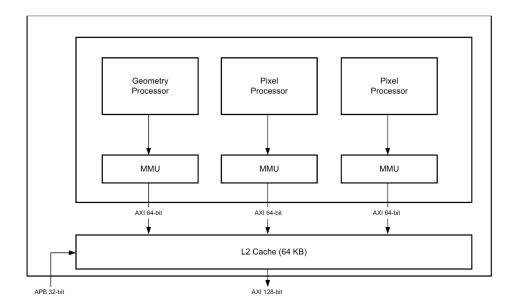

| Figura 11: Diagrama de Bloques de la GPU[20]                                                    |     |

| Figura 12: Conexionado entre las LUTs y los multiplexores de un CLB [25]                        |     |

| Figura 13: Diagrama de bloques del DSP [3]                                                      |     |

| Figura 14: Conexiones entre PS y PL [16]                                                        |     |

| Figura 15: Conexiones AXI PS – PL [16]                                                          | 54  |

| Figura 16: Placa de prototipado ZCU102                                                          | 57  |

| Figura 17: Configuración del switch SW6 para arranque desde la tarjeta SD                       | 58  |

| Figura 18: Flujo de diseño de la aplicación                                                     | 62  |

| Figura 19: Opciones de compilación de hardware programable [27]                                 | 64  |

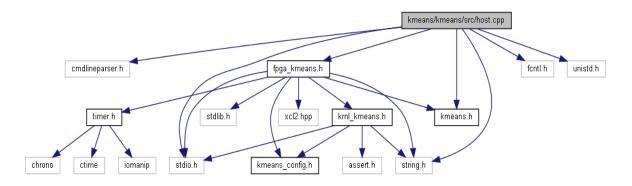

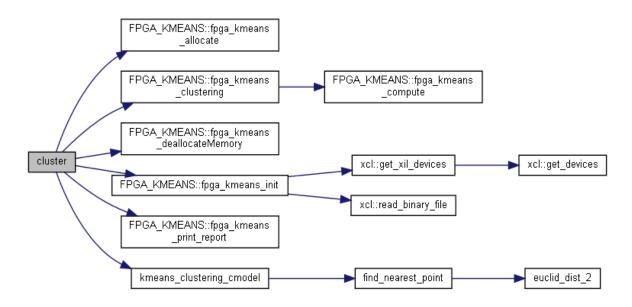

| Figura 20: Dependencias de ficheros de la aplicación                                            | 68  |

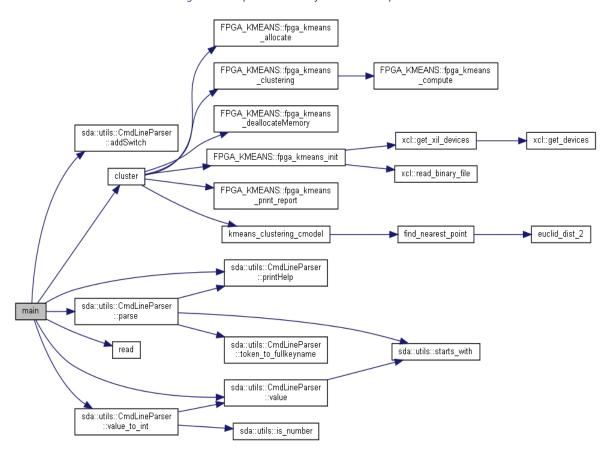

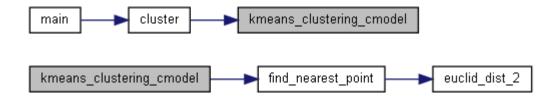

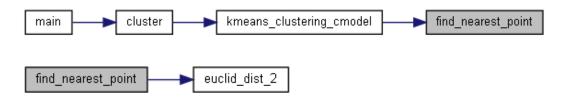

| Figura 21: Grafo de llamadas de la función main                                                 | 68  |

| Figura 22: Grafo de llamadas de la función cluster().                                           | 72  |

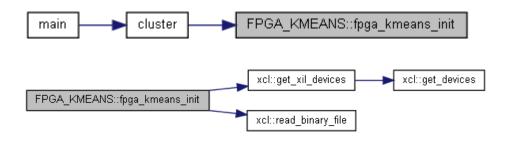

| Figura 23: Grafo de llamadas de la función fpga_kmeans_init                                     | 75  |

| Figura 24: Grafo de llamadas de la función fpga_kmeans_allocate                                 | 77  |

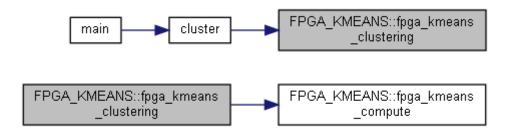

| Figura 25: Grafo de llamadas de la función fpga_kmeans_clustering                               | 79  |

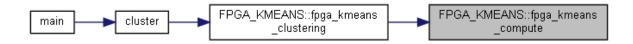

| Figura 26: Grafo de llamadas de la función fpga_kmeans_compute                                  | 81  |

| Figura 27: Grafo de llamadas de la función fpga_kmeans_deallocateMemory                         | 86  |

| Figura 28: Grafo de llamadas de la función fpga_kmeans_print_report                             | 87  |

| Figura 29: Grafo de llamadas de la función kmeans_clustering_cmodel                             | 88  |

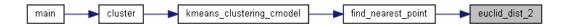

| Figura 30: Grafo de llamadas de la función find_nearest_point                                   | 89  |

| Figura 31: Grafo de llamadas de la función euclid_dist_2                                        | 90  |

| Figura 32: Grafo de llamadas de la función kmeans_kernel_wrapper                                | 91  |

| Figura 33: Grafo de llamadas de la función load_clusters                                        | 94  |

| Figura 34: Grafo de llamadas de la función load_features                                        | 95  |

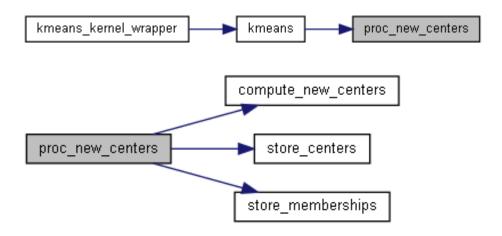

| Figura 35: Grafo de llamadas de la función proc_new_centers                                     | 98  |

| Figura 36: Grafo de llamadas de la función compute_new_centers                                  | 100 |

| Figura 37: Grafo de llamadas de la función store_memberships                                    | 100 |

| Figura 38: Grafo de llamadas de la función store_centers                                        |     |

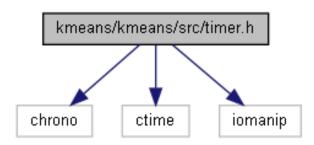

| Figura 39: Dependencias para time.h                                                             |     |

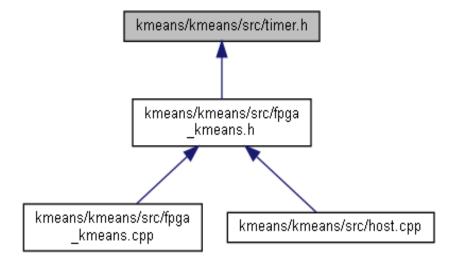

| Figura 40: Archivos que directa o indirectamente incluyen time.h                                | 102 |

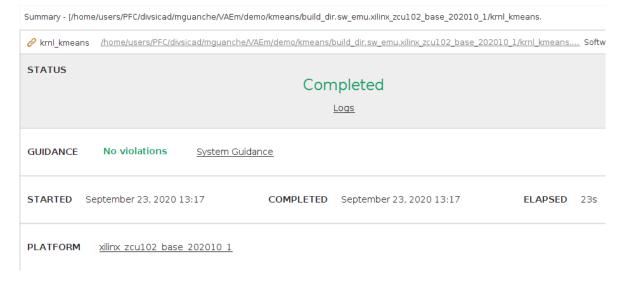

| Figura 41: Informe "Summary" del apartado "krnl_kmeans (Software Emulation)"                    | 111 |

| Figura 42: Informe "Summary" del apartado "krnl_kmeans (Software Emulation)" (II)          | 112    |

|--------------------------------------------------------------------------------------------|--------|

| Figura 43: Informe "Summary" del apartado "kmeans (Software Emulation)"                    | 112    |

| Figura 44: Informe Summary del apartado kmeans (Software Emulation) (II)                   | 112    |

| Figura 45: Confirmación de emulación software realizada sin incidencias                    | 113    |

| Figura 46: Finalización de archivo Logs del subapartado kmeans (Software Emulation)        | 113    |

| Figura 47: Informe "Summary" del apartado "krnl_kmeans (Hardware Emulation)" (I)           | 114    |

| Figura 48: Informe "Summary" del apartado "krnl_kmeans (Hardware Emulation)" (II)          | 114    |

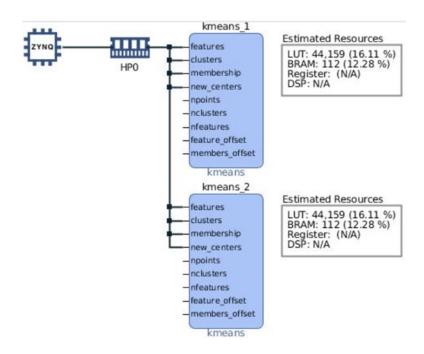

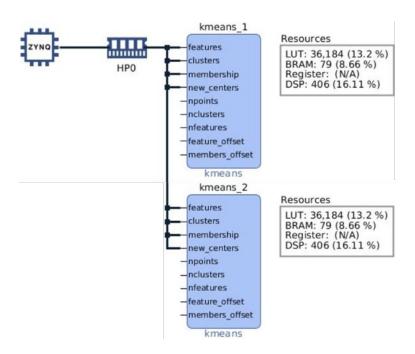

| Figura 49: Diagrama del acelerador hardware elaborado por la opción "hw_emu"               | 115    |

| Figura 50: Frecuencia de reloj y latencia de los módulos según "hw_emu""                   | 115    |

| Figura 51: Recursos PL requeridos según "hw_emu", expuesto en informe "System Estimato     | e" 116 |

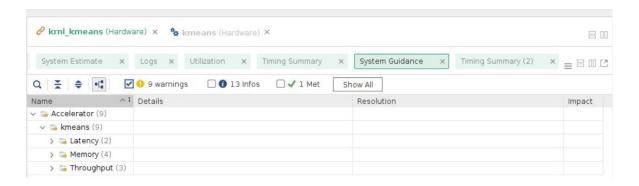

| Figura 52: Informe "System Guidance" obtenido tras la ejecución "hw_emu"                   | 116    |

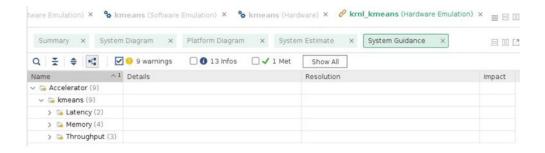

| Figura 53: "Summary" del subapartado "kmeans (Hardware Emulation)"                         | 117    |

| Figura 54: "Summary" del subapartado "kmeans (Hardware Emulation)" (II)                    | 117    |

| Figura 55: Frecuencia de reloj y latencia del kernel según la emulación hardware           | 118    |

| Figura 56: Recursos PL utilizados por un kernel según la estimación de la emulación hardwa |        |

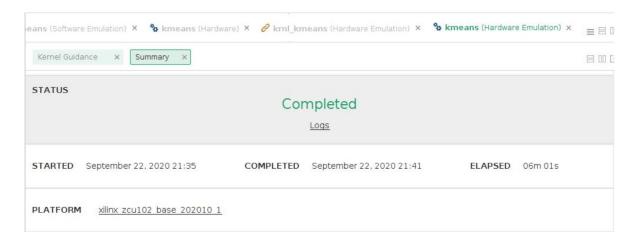

| Figura 57. Arquitectura de la Plataforma                                                   |        |

| Figura 58: Incorporación del host en el diagrama de bloques                                |        |

| Figura 59: Diagrama de bloques dentro de ps_e                                              |        |

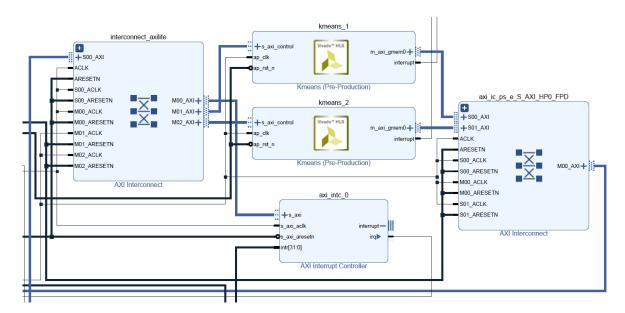

| Figura 60: Introducción de los kernels en la arquitectura de la aplicación                 |        |

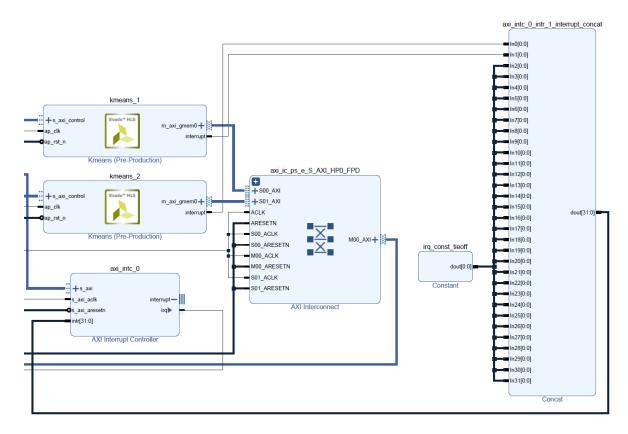

| Figura 61: Gestión de interrupciones de los kernels por el bloque AXI Interrupt Controller | 123    |

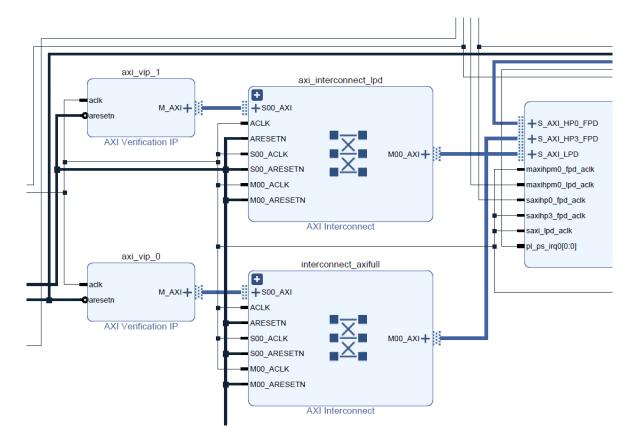

| Figura 62: Implementación de los bloques AXI Verification IP                               | 124    |

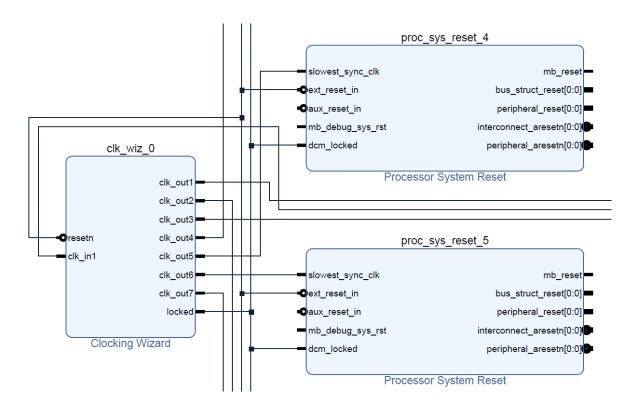

| Figura 63: Clocking Wizard                                                                 |        |

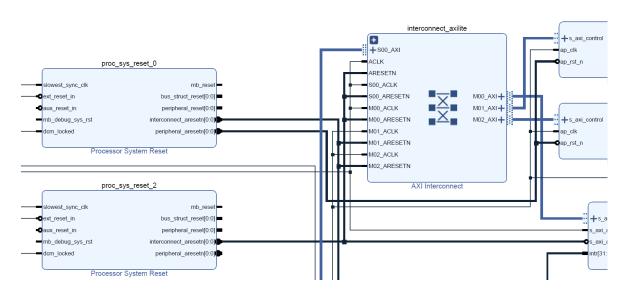

| Figura 64: Bloque Processor System Reset                                                   |        |

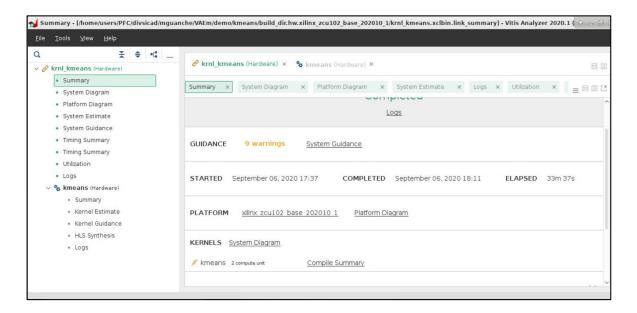

| Figura 65: Informes sobre la ejecución de la opción hw                                     |        |

| Figura 66: Parámetros de la compilación de la opción "hw"                                  |        |

| Figura 67: Diagrama principal del acelerador hardware                                      | 127    |

| Figura 68: Frecuencia de funcionamiento estimada de los distintos módulos                  |        |

| Figura 69: Latencia de los módulos (I)                                                     |        |

| Figura 70: Latencia de los módulos (II)                                                    |        |

| Figura 71: Recursos FPGA requeridos por cada módulo                                        | 128    |

| Figura 72: Errores o incidencias en la implementación de los kernels                       | 129    |

| Figura 73: Contenido del apartado Timing Settings                                          | 129    |

| Figura 74: Aspectos analizados en el apartado Check Timing                                 | 130    |

| Figura 75: "Design Timing Summary" (I)                                                     |        |

| Figura 76: "Design Timing Summary" (II)                                                    | 130    |

| Figura 77: Clock Summary                                                                   | 131    |

| Figura 78: Pulse Width Checks                                                              | 131    |

| Figura 79: Ejemplo de parte inicial de apartado "Max Delay Paths"                          | 132    |

| Figura 80: Informe "Summary" del kernel "kmeans"                                           | 134    |

| Figura 81: Kernel Estimate                                                                 | 135    |

| Figura 82: Informe de potencia generado en la compilación "hw"                             | 136    |

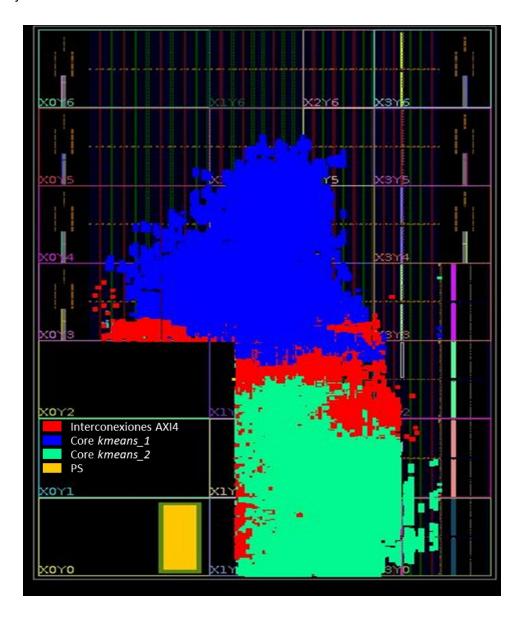

| Figura 83: Distribución de recursos del MPSoC en la implementación de kmeans               |        |

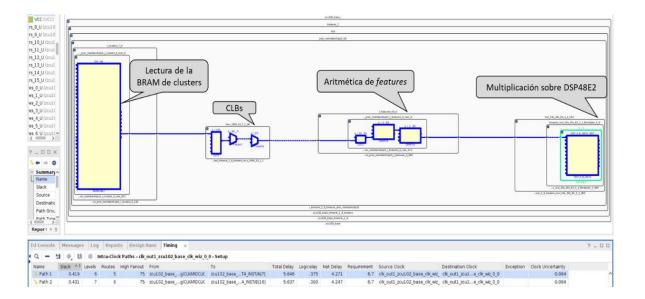

| Figura 84. Determinación de la ruta crítica según Vivado                                   | 138    |

| Figura 85: Configuración del switch SW6 para arranque desde la tarjeta SD                  | 142    |

| Figura 86: Señalización de la placa de finalización del proceso de arrangue                | 142    |

| igura 87: Habilitación de conexión USB para utilización OTG                                | 143 |

|--------------------------------------------------------------------------------------------|-----|

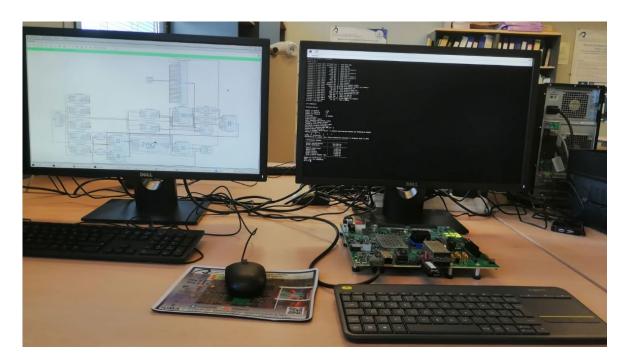

| Figura 88: Sistema implementado                                                            |     |

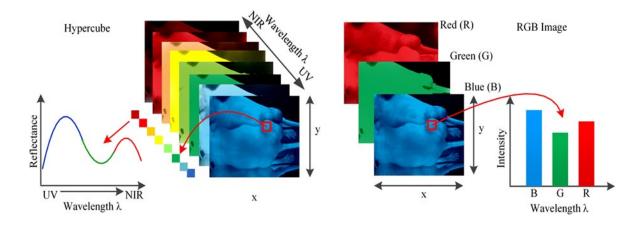

| igura 89: Representación de imagen hiperespectral (izquierda) y de imagen RGB (derecha) [3 |     |

|                                                                                            | -   |

| igura 90: Imágenes RGB de cáncer de piel obtenidas con un dermoscopio digital              |     |

## ÍNDICE DE TABLAS

| Tabla 1: Características de los recursos hardware según la subfamilia (adaptada de [10])          | 38    |

|---------------------------------------------------------------------------------------------------|-------|

| Tabla 2: Componentes hardware en función de la subfamilia (adaptado de [10])                      | 38    |

| Tabla 3: Modos de arranque para la configuración del sistema [10]                                 | 47    |

| Tabla 4: Cantidad de recursos de la parte PL [14][24]                                             | 48    |

| Tabla 5: Periféricos I/O disponibles para MIO y EMIO [20]                                         | 56    |

| Tabla 6: Informe HLS Synthesis generado al ejecutar la opción hw_emu                              | . 118 |

| Tabla 7: Informe "Utilization"                                                                    | . 133 |

| Tabla 8: Informe HLS Synthesis: Latencias                                                         | . 135 |

| Tabla 9. Informe HLS Synthesis: Recursos                                                          | . 135 |

| Tabla 10: Características comunes a todos los casos                                               | . 147 |

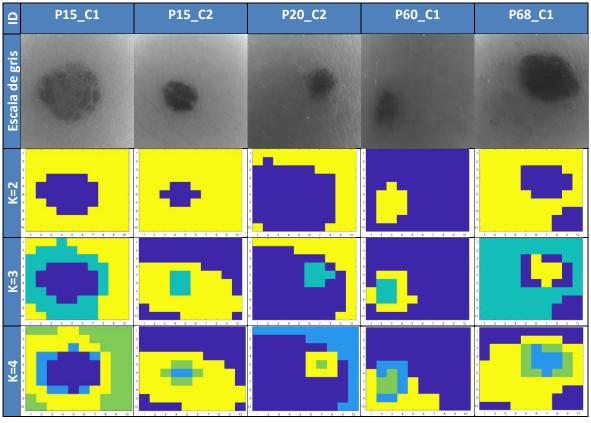

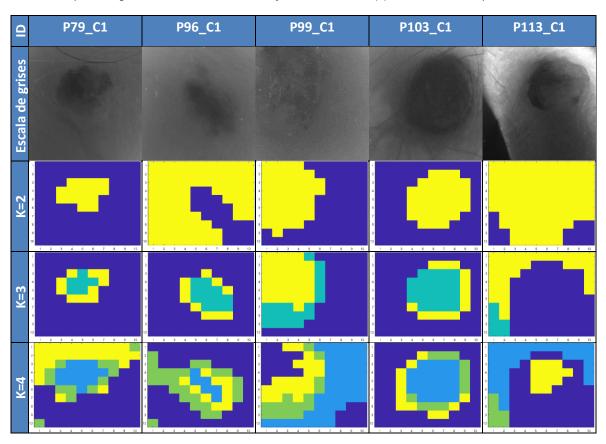

| Tabla 11: Mapas de segmentación obtenidos en cada ejecución de kmeans (I). Los colores del        |       |

| mapa son aleatorios                                                                               | . 149 |

| Tabla 12: Mapas de segmentación obtenidos en cada ejecución de kmeans (II). Los colores del       |       |

| mapa son aleatorios                                                                               | . 149 |

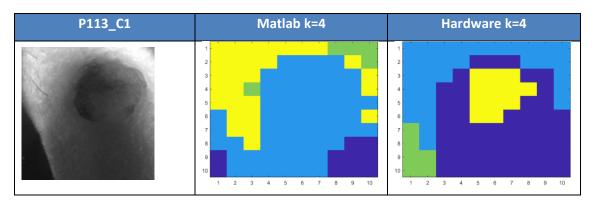

| Tabla 13: Ejecución de la clasificación para 4 clusters en placa y en Matlab para la imagen       |       |

| P113_C1. Los colores del mapa son aleatorios.                                                     | . 151 |

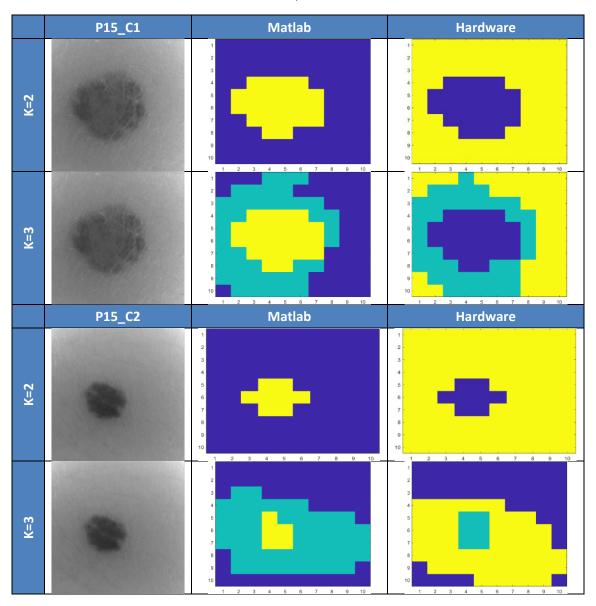

| Tabla 14: Ejecución de la clasificación para 2 y 3 clusters en placa y en Matlab para las imágen  | es    |

| P15_C1 y P15_C2. Los colores del mapa son aleatorios                                              | . 151 |

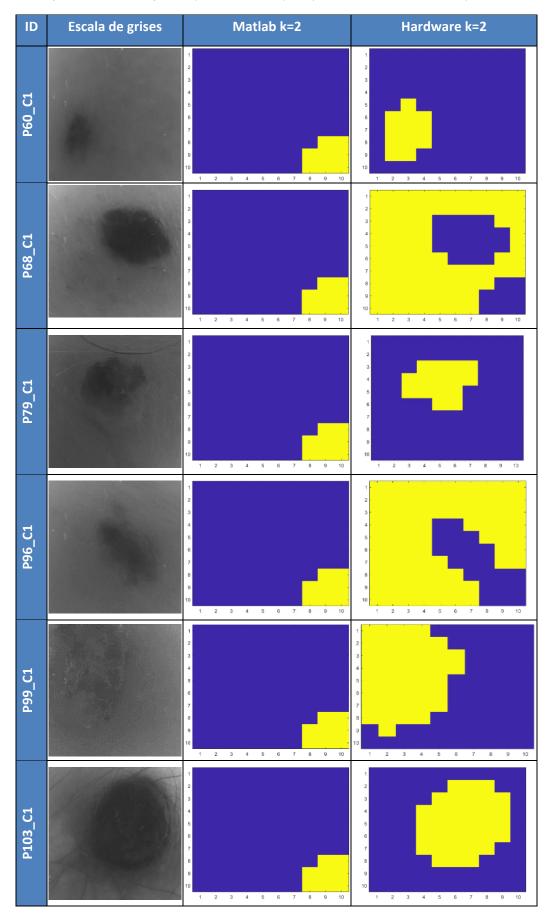

| Tabla 15: Ejecuciones de la clasificación para 2 clusters en placa y en Matlab. Los colores del n | napa  |

| son aleatorios.                                                                                   | . 152 |

| Tabla 16: Comparativa entre la ejecución software y la ejecución con aceleradores hardware .      | . 154 |

| Tabla 17: Presupuesto de los recursos hardware                                                    | . 165 |

| Tabla 18: Presupuesto de los recursos software                                                    | . 166 |

| Tabla 19: Presupuesto de los recursos humanos                                                     | . 166 |

| Tabla 20: Presupuesto total                                                                       | . 167 |

### ÍNDICE DE ECUACIONES

| Ecuación 1: Relación entre la probabilidad condicional y la probabilidad conjunta                    | 9    |

|------------------------------------------------------------------------------------------------------|------|

| Ecuación 2: Fórmula de Bayes                                                                         | 9    |

| Ecuación 3: Relación entre la probabilidad del elemento y la de cada atributo si estos últimos s     | son  |

| independientes                                                                                       | 10   |

| Ecuación 4: Evaluación de la probabilidad de pertenencia del elemento "x" a la clase "c"             | 10   |

| Ecuación 5: Función de probabilidad influenciada por la frecuencia relativa y la presuposición o     | del  |

| programador                                                                                          | 11   |

| Ecuación 6: Ecuación lineal de la frontera entre 2 clases                                            | 14   |

| Ecuación 7: Ecuación del algoritmo Perceptron para la actualización de los parámetros $\mathbf{w}_i$ | 15   |

| Ecuación 8: Ecuación del algoritmo WINNOW para la actualización de los parámetros $\mathbf{w}_i$     | 17   |

| Ecuación 9: Ecuación polinómica de la frontera entre 2 clases                                        | 19   |

| Ecuación 10: Relación entre la cantidad de parámetros w y las otras características de la ecuac      | ción |

| polinómica                                                                                           | 19   |

| Ecuación 11: Error cuadrático medio                                                                  | 22   |

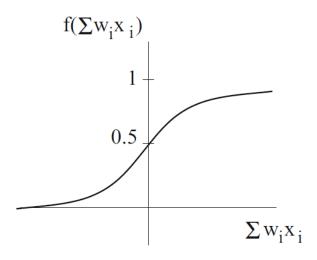

| Ecuación 12: Función sigmoidea                                                                       | 23   |

| Ecuación 13: Influencia de una neurona de salida en la equivocación del clasificador                 | 25   |

| Ecuación 14: Influencia en la equivocación del clasificador de una neurona que precede a las d       | le   |

| salida                                                                                               | 25   |

| Ecuación 15: Ecuación de modificación de los parámetros "w"                                          | 25   |

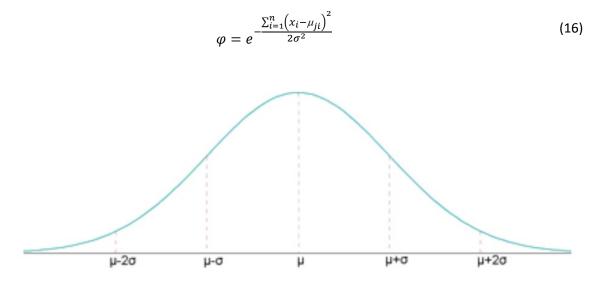

| Ecuación 16: Función de distribución gaussiana de dimensión "n" [8]                                  | 28   |

### ÍNDICE DE CÓDIGOS

| Código 1: Variables locales de la función main                                                 | 69   |

|------------------------------------------------------------------------------------------------|------|

| Código 2: Establecimiento de los argumentos a especificar mediante el terminal de comandos     | 69   |

| Código 3: Extracción de los parámetros indicados mediante la ejecución por línea de comando    | s 69 |

| Código 4: Notificación de los clusters obtenidos y liberación de recursos                      | 71   |

| Código 5: Inicio de la función cluster                                                         | 71   |

| Código 6: Ejecución del proceso de clustering mediante funciones de fpga_kmeans                | 72   |

| Código 7: Verificación mediante modelo software desarrollado en C                              | 72   |

| Código 8: Evaluación de la discordancia entre los resultados del modelo hardware-software y o  | let  |

| modelo software del k-means                                                                    | 73   |

| Código 9: Almacenamiento de los resultados de las agrupaciones de los elementos determinados   | las  |

| por el modelo en C de k-means                                                                  | 73   |

| Código 10: Almacenamiento de los resultados de las agrupaciones de los elementos determina     | ıdas |

| por el modelo hardware-software de k-means                                                     | 74   |

| Código 11: Comparación entre los resultados de la ejecución de k-means y los resultados        |      |

| esperados                                                                                      | 74   |

| Código 12: Liberación final de los recursos empleados en la función cluster                    | 75   |

| Código 13: Búsqueda de los dispositivos y extracción de archivo binario para la programación . | 76   |

| Código 14: Programación de los dispositivos                                                    |      |

| Código 15: Implementación de los kernels mediante OpenCL                                       | 77   |

| Código 16: Reserva de espacio de memoria para los registros de los kernels                     | 78   |

| Código 17: Creación de los objetos cl::Buffer                                                  | 79   |

| Código 18: Parámetros y variables creadas por la función "fpga_kmeans_clustering"              | 80   |

| Código 19: Introducción del primer elemento de cada cluster en "fpga_kmeans_clustering"        | 80   |

| Código 20: Escalamiento y reorganización de la información de los elementos a evaluar          | 81   |

| Código 21: Función para el cálculo del factor de escalamiento                                  | 81   |

| Código 22: Función para el escalamiento y reubicación del contenido de "feature"               | 82   |

| Código 23: Programación de las señales de entrada a los kernels                                | 82   |

| Código 24: Transmisión host-kernel de la información de los elementos                          | 83   |

| Código 25: Función "scale_cluster"                                                             |      |

| Código 26: Intercambio de información entre host y kernels mediante OpenCL                     | 84   |

| Código 27: Ejecución de la funcionalidad del hardware programable mediante                     |      |

| "kmeans_kernel_wrapper"                                                                        | 85   |

| Código 28: Evaluación de los cambios en la membresía de los elementos                          | 85   |

| Código 29: Actualización de "new_centers_len" y "new_centers"                                  | 85   |

| Código 30: Actualización de los centroides de los clusters y terminación de                    |      |

| "fpga_kmeans_compute"                                                                          | 86   |

| Código 31: Función "fpga_kmeans_deallocateMemory"                                              | 86   |

| Código 32: Función "fpga_kmeans_print_report"                                                  | 87   |

| Código 33: Inicialización de "clusters" y "membership"                                         | 88   |

| Código 34: Proceso de clustering en la función kmeans_clustering_cmodel (I)                    | 88   |

| Código 35: Proceso de clustering en la función kmeans clustering cmodel (II)                   | . 89 |

| Código 36: Función "find_nearest_point"                                                      | 89  |

|----------------------------------------------------------------------------------------------|-----|

| Código 37: Función euclid_dist_2                                                             | 90  |

| Código 38: Finalización de la función kmeans_clustering_cmodel                               | 90  |

| Código 39: Función kmeans_kernel_wrapper                                                     | 91  |

| Código 40:Definición de la interfaz de los kernels                                           | 92  |

| Código 41: División de la estructura del kernel en los submódulos "proc_memberships" y       |     |

| "proc_new_centers"                                                                           | 93  |

| Código 42: Ejecución de "load_cluster" en "proc_memberships"                                 | 93  |

| Código 43: Función "load_clusters"                                                           | 94  |

| Código 44: Carga y determinación de las agrupaciones de los elementos en el módulo           |     |

| "proc_memberships"                                                                           | 95  |

| Código 45: Función "load_feature"                                                            | 95  |

| Código 46: Descripción del tipo de variable "point_dist_t"                                   | 96  |

| Código 47: Inicialización de los elementos del array "pt"                                    | 97  |

| Código 48: Etapa de clasificación de los elementos                                           | 97  |

| Código 49: Transmisión de la clasificación de los elementos a "proc_new_centers"             | 98  |

| Código 50: Creación e inicialización de las variables locales de "proc_new_centers"          | 99  |

| Código 51: Distribución de la carga computacional del módulo "proc_new_centers"              | 99  |

| Código 52: Programación de la función "compute_new_centers"                                  | 100 |

| Código 53: Función "store_membership"                                                        | 101 |

| Código 54: Función "store_centers"                                                           | 101 |

| Código 55: Funciones para medir tiempos de ejecución                                         | 103 |

| Código 56: Definición del tipo de variable "cPerfTimer"                                      | 103 |

| Código 57: Contenido completo del archivo krnl_kmeans.ini                                    | 104 |

| Código 58: Tareas principales del Makefile                                                   | 106 |

| Código 59: Sección del Makefile que restringe cualquier placa cuyo nombre contenga "ZC"      | 108 |

| Código 60: Anulación de la restricción del Makefile sobre las placas cuyo nombre contenga    |     |

|                                                                                              |     |

| Código 62: Modificación de la parametrización de run_emulation.pl                            |     |

| Código 63: Comando para la invocación de la compilación del proyecto                         |     |

| Código 64: Invocación de la aplicación "Vitis Analyzer"                                      |     |

| Código 65: Ejecución de la emulación software                                                |     |

| Código 66: Ejecución de la emulación hardware                                                |     |

| Código 67: Resultados de ejecución de la emulación software                                  |     |

| Código 68: Resultados de ejecución de la emulación hardware                                  |     |

| Código 69: Comando para transferencia de los datos para la ejecución del proyecto a la tarjo |     |

|                                                                                              |     |

| Código 70: Resultado ejecución con los archivos de entrada "100" y "100.gold_c10"            |     |

| Código 71: Escalado espacial de las imágenes en Matlab                                       |     |

| Código 72: Selección de bandas espectrales de la imagen                                      |     |

| Código 73: Redimensionamiento de las imágenes                                                |     |

| Código 74: Generación de GoldenFiles en Matlab                                               |     |

| Código 75: Generación de los mapas de segmentación                                           |     |

### ÍNDICE DE GRÁFICAS

| Gráfica 1: Representación de la ecuación sigmoidea en función del sumatorio [8]                          | 23  |

|----------------------------------------------------------------------------------------------------------|-----|

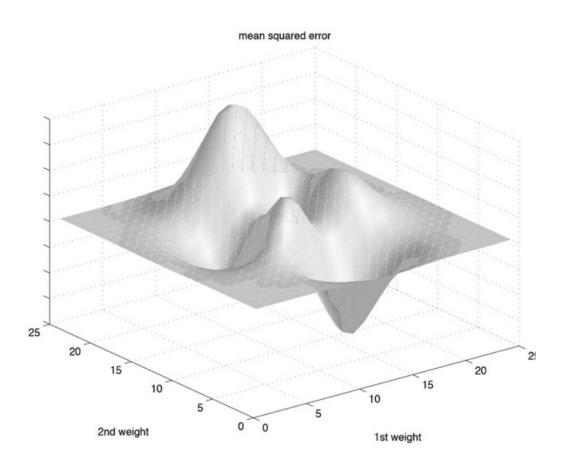

| Gráfica 2: Función con más de un mínimo relativo [8]                                                     | 26  |

| Gráfica 3: Evolución de la función de Gauss con respecto a " $\mu$ " y " $\sigma$ " en una dimensión [9] | 28  |

| Gráfica 4: Ejemplo de detección de clusters [8]                                                          | 30  |

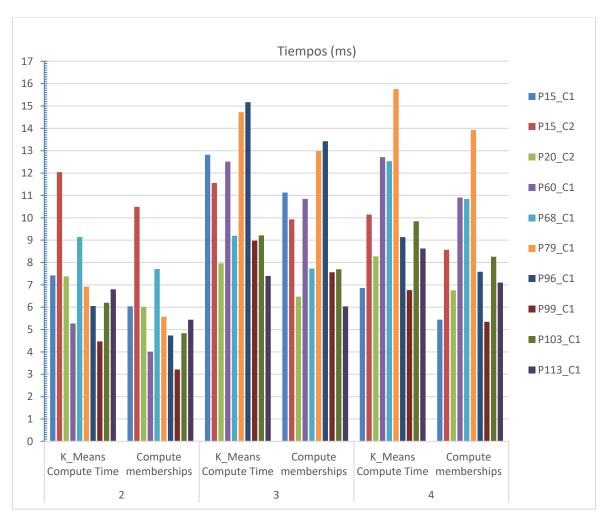

| Gráfica 5: Tiempos para el cálculo de las agrupaciones de las muestras y para la ejecución de la         | ì   |

| aplicación en placa                                                                                      | 147 |

# Memoria

### Capítulo 1. Introducción

#### 1.1. Antecedentes

Machine learning o aprendizaje automático [1] hace referencia a la rama dentro de la Inteligencia Artificial consistente en otorgar a una aplicación la capacidad de efectuar el análisis de los datos con el objetivo de identificar patrones. De esta manera, puede intuirse aspectos futuros relativos a una nueva entrada.

La idea de *machine learning* y de la AI se emplea en la tecnología actual. Ejemplos de ello son las múltiples aplicaciones de asistentes de voz tales como Siri en los terminales de Apple o Alexa desarrollada por Amazon. Por otra parte, el *machine learning* se encuentra en las recomendaciones personalizadas de contenido audiovisual realizadas por plataformas como *Netflix* o *Spotify*, ya que para ello es necesario analizar el historial de reproducciones del usuario [2].

El principal desafío que enfrenta la implementación de funcionalidad de *machine learning* en un sistema electrónico radica en que la fiabilidad de las configuraciones definidas depender de la cantidad de datos extraídos de las situaciones evaluadas y de la variedad de análisis estadísticos efectuados. Esto conlleva una capacidad de computación elevada, pero presenta la ventaja que puede ser paralelizable. Debido a ello, en este trabajo se plantea la implementación de esta funcionalidad utilizando la plataforma MPSoC Zynq UltraScale+ de Xilinx (Figura 1) como acelerador *hardware*. De esta manera, la paralelización puede lograrse utilizando tanto una estrategia *software* mediante procesamiento multiprocesador, como una estrategia basada en el paralelismo implícito de la implementación de una arquitectura *hardware* usando recursos de lógica programable [3].

Al igual que en el diseño de cualquier sistema computacional, una etapa fundamental en el proceso de diseño de una aplicación de *machine learning* es su verificación. Asimismo, una manera de reducir el costo tanto económico como temporal de dicho proceso es el uso de plataformas virtuales. Estos recursos consisten en sistemas que son capaces de desarrollar la funcionalidad de un sistema *hardware* sin necesidad de que este sea físicamente implementado, partiendo de las especificaciones de diseño indicadas por el usuario en un lenguaje de programación de alto nivel.

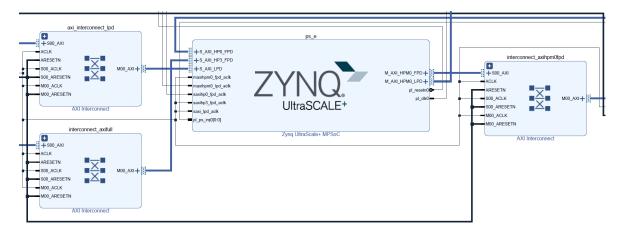

Figura 1: Arquitectura del dispositivo MPSoC Zynq UltraScale+ [4]

De esta manera, los diseñadores *hardware* podrán evaluar diferentes opciones de configuración del sistema, mientras que los programadores de *software* podrán ejecutar y depurar el código de ejecución antes de disponer de sistema físico [5].

Uno de los problemas que requieren un alto coste computacional es el procesado de imágenes hiperespectrales. En este trabajo se evalúa el diseño del acelerador *hardware* procesando un conjunto de 10 imágenes de cáncer de piel con una cantidad de 28 bandas espectrales que cubren el espectro visible e infrarrojo cercano (VNIR) desde 450 a 950 nm, con una resolución espacial de 10 x 10 píxeles.

### 1.2. Objetivos

El principal objetivo de este Trabajo Fin de Grado es el diseño de un sistema que combina funcionalidad *software* y arquitectura *hardware* destinado a la clasificación usando técnicas de *machine learning*. Para ello, se utiliza una plataforma virtual del dispositivo FPGA Zynq UltraScale+ de Xilinx basada en QEMU. Esta plataforma virtual permite verificar el funcionamiento del sistema formado por el sistema de procesamiento (PS) de Zynq y un modelo funcional de la aplicación de clasificación por *machine learning*. Finalmente, la implementación del algoritmo se ejecuta sobre la plataforma real para obtener resultados de su ejecución en un sistema hardware/software. Para lograr tal fin, es necesario definir los siguientes objetivos operativos o parciales:

- O1. Estudiar la arquitectura del dispositivo MPSoC FPGA Zynq UltraScale+ de Xilinx y sus principales componentes.

- O2. Estudiar diferentes alternativas de clasificación de machine learning.

- O3. Implementar una plataforma virtual para Zyng UltraScale+.

- O4. Simular el modelado del sistema de clasificación mediante *machine learning* en la plataforma virtual y estudiar las prestaciones de la arquitectura.

- O5. Documentar el trabajo realizado.

#### 1.3. Peticionario

El Trabajo Fin de Grado ha sido ofertada por el Instituto Universitario de Microelectrónica Aplicada (IUMA), concretamente por la división de Sistemas Industriales y CAD (SICAD). Dicho trabajo resulta de gran interés, ya que abarca el concepto de *machine learning*, una temática en auge debido a su relevancia como vía para el desarrollo y perfeccionamiento de la Inteligencia Artificial (AI, *Artificial Intelligence*). Dicho campo, es uno de los grandes retos de la ingeniería en estos momentos por su capacidad de ser aplicada en distintos sectores de actividad.

Igualmente, actúa como peticionario de este Trabajo Fin de Grado la Escuela de Ingeniería de Telecomunicación y Electrónica (EITE) de la Universidad de Las Palmas de Gran Canaria (ULPGC), siendo requisito para la obtención del título de Graduado en Ingeniería en Tecnologías de la Telecomunicación.

#### 1.4. Estructura del documento

La estructura del presente documento es la siguiente. En este primer capítulo se presentan los objetivos de trabajo una vez contextualizado el problema.

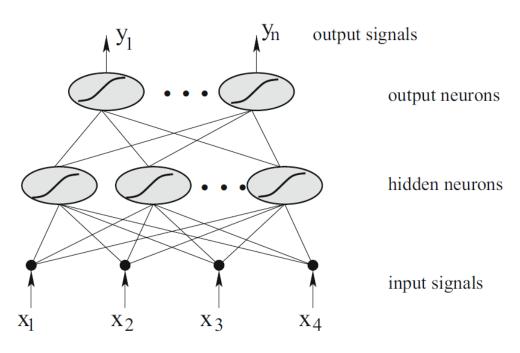

En el capítulo 2 se explican los conceptos necesarios sobre *machine learning*, detallando las principales características que definen los algoritmos de *machine learning*. Se introducen algunas de las estrategias de *machine learning* aplicadas en la ingeniería actual, incluyendo los algoritmos de aprendizaje supervisado. Finalmente se introducen los conceptos de algoritmos de *clustering* que se utilizarán en el sistema para la clasificación.

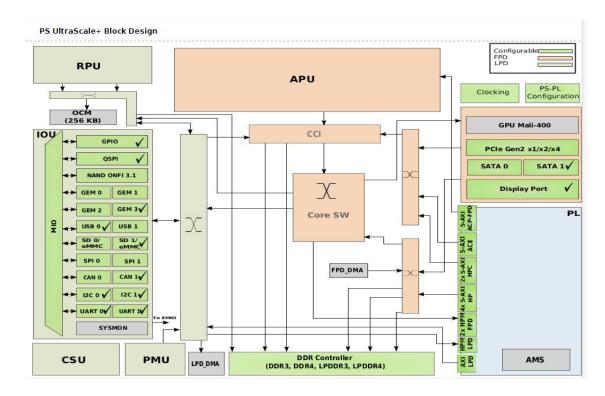

En el capítulo 3 se explica en detalle la arquitectura de la placa de prototipado, sus recursos y las opciones de configuración disponibles. Los principales recursos incluyen el sistema de procesamiento compuesto con la unidad de procesamiento de aplicaciones (APU) y de tiempo real (RPU), el bloque PMU (*Platform Management Unit*) y CSU (*Configuration and Security Unit*),

destinados a la gestión del conjunto de recursos del MPsoC. Además, se explicarán los diferentes tipos de recursos de la parte de lógica programable (PL) del dispositivo MPSoC.

En el capítulo 4 se explica el flujo de diseño de referencia utilizado, poniendo énfasis en las tareas de diseño en alto nivel sobre Vitis.

En el capítulo 5 se analiza el código de referencia utilizado para la aplicación de *machine learning*. Como resultado de este análisis, se visualiza la algorítmica de la aplicación, así como algunas características especificadas con respecto a la arquitectura *hardware* diseñada. Este último aspecto se logra mediante directivas que controlan la generación de la arquitectura *hardware* utilizando herramientas de síntesis de alto nivel. Dichas directivas se utilizarán de forma exhaustiva para la compilación del proyecto.

Los aspectos principales de la compilación del diseño se explican en el capítulo 6. Se analiza la parametrización realizada, en función de la implementación objetivo utilizada: software, emulación hardware sobre la plataforma virtualizada o para la plataforma de prototipado hardware final. Todo ello se completa en el capítulo 7 con la ejecución de la aplicación final indicada, analizando los resultados obtenidos en términos de prestaciones, recursos y potencia utilizada. Finalmente se recogen las principales conclusiones del trabajo realizado y se plantean las posibles líneas de desarrollo futuro del trabajo.

### Capítulo 2. Machine Learning

### 2.1. Introducción

Según Arthur Samuel, podemos definir una aplicación de *machine learning* como aquella que es capaz de aprender y mejorar su efectividad a partir de los datos recibidos. Para ello, se basa en el análisis estadístico para la realización de evaluaciones predictivas. Estas aplicaciones pueden ser clasificadas en tres categorías:

- a. Aprendizaje supervisado. Consiste en introducir una serie de muestras de datos que tienen un valor de salida preestablecido, algunos de los cuales se utilizan para entrenar al algoritmo, mientras que otros se emplean para verificar su funcionamiento. El entrenamiento permite al sistema determinar la salida que le correspondería a las entradas posteriores, aunque no se haya especificado dicha correspondencia. Un ejemplo de uso de este servicio se encuentra en la detección de *spam* en los mensajes de correo electrónico. El valor de salida puede ser la pertenencia a una determinada categoría, en el caso de que sea un sistema de clasificación, o un valor cuantitativo, en el caso de un sistema de regresión.

- b. Aprendizaje sin supervisión. Consiste en introducir datos que se encuentran sin clasificar en una aplicación de *machine learning* no entrenada. Asimismo, el algoritmo tiene como objetivo establecer posibles agrupaciones en función de características comunes en diversos elementos de entrada (*clustering*), o bien detectar posibles correlaciones entre las características de dichos elementos (*association*).

- c. Aprendizaje mediante refuerzo. Consiste en que el sistema aprende mediante la interacción con el entorno considerado. La manera de proceder de este algoritmo se puede enfocar desde una dinámica de recompensa y castigo. Cada acción tomada por el sistema origina, dependiendo de sus consecuencias, una valoración de su adecuación que puede ser negativa (castigo) o positiva (recompensa). De esta manera, el objetivo del algoritmo es maximizar siempre la recompensa, por lo que repetirá aquellas acciones que descubrió que reciben una mayor valoración positiva y evitará aquellas que presentaban una valoración negativa [6].

### 2.2. Consideraciones preliminares

A continuación, se van a estudiar distintos aspectos a considerar en función del tipo de entrenamiento y de la búsqueda de información con objeto de aumentar la precisión de las predicciones realizadas.

#### 2.2.1. Información de entrenamiento

En el caso de los sistemas de aprendizaje supervisado, un aspecto decisivo para asegurar la mayor precisión en sus predicciones es la excelencia de los datos de entrenamiento. Sin embargo, pueden existir algunas imperfecciones en la información contenida en ellos. Asimismo, el sistema debe tener cierto grado de tolerancia ante estos errores que, en muchas ocasiones, pueden ser inherentes al proceso de medida.

- a. Atributos irrelevantes. Puede ocurrir que algunas de las características disponibles para los elementos de entrenamiento carezcan de importancia para la clasificación que se pretende establecer. Dicha situación supone un costo de computación adicional que resulta innecesario, pero normalmente ineludible en aquellos algoritmos en los que el proceso de determinación de los atributos se encuentre automatizado. La ausencia de estos atributos se establecerá en aquellos datos de entrenamiento que se elaboren manualmente.

- b. Ausencia de atributos representativos. Este tipo de circunstancia supone el problema inverso al de los atributos irrelevantes. Asimismo, la omisión de un atributo que se sospecha como no decisivo puede causar incongruencias en el criterio de clasificación desarrollado por el sistema si dispone de cierto grado de relevancia oculta.

- c. Atributos redundantes. Ocurre cuando se dispone de varios atributos que son deducibles entre sí. Un claro ejemplo de esta situación se observa cuando, considerando como datos de entrenamiento la información de un grupo de personas, 2 de los atributos considerados son la fecha de nacimiento y la edad. Sin embargo, su importancia con respecto a la funcionalidad del algoritmo es reducida en comparación con los dos casos anteriores.

- d. **Valor desconocido.** Puede ocurrir que el valor de alguno de los elementos para algunos de sus atributos se desconozca.

- e. Valores de atributos erróneos. Existen distintos factores tales como la poca fiabilidad de las fuentes de información, la imprecisión de los instrumentos de medida, la equivocación del usuario o erratas que originan que el valor de algunos de estos atributos pueda presentar cierto grado de error.

- f. **Categorías mal definidas.** Esto puede originar que las características de algunos de los elementos categorizados no se terminen de adecuar correctamente a las consideradas para

el grupo en el que se incluyen. En consecuencia, cualquier leve modificación en los atributos de dicho elemento puede ocasionar que este se clasifique en el grupo incorrecto.

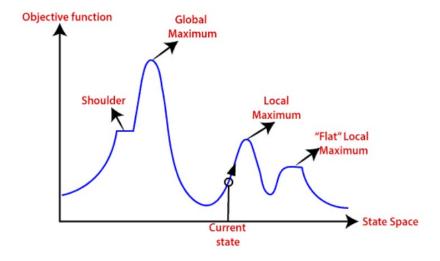

## 2.2.2. Búsqueda automatizada (Hill Climbing)

Las técnicas Hill Climbing conforman una estrategia de búsqueda en la que se basan muchos sistemas de machine learning para realizar procesos de indagación de la solución buscada de manera automatizada. Para ello, la operación de búsqueda se define como un proceso de transición entre estados, partiendo de un estado inicial. Asimismo, el objetivo del algoritmo consiste en lograr que el aspecto tratado evolucione por medio de una serie de estados intermedios hacia un estado final que satisfaga los requisitos solicitados, determinando la secuencia de cambios que permiten esta transformación.

Durante el trascurso de este algoritmo se dispone de dos registros. En uno de ellos se almacenan todos los estados que no han sido evaluados pero que son accesibles desde un estado ya alcanzado con anterioridad. En el otro se almacenan todos los estados que el sistema ha evaluado, a los cuales no se debe regresar como consecuencia de una transición desde un estado futuro.

Las posibles transiciones de un estado actual al siguiente son establecidas por el conjunto de acciones entre las que se puede elegir. En el campo de la inteligencia artificial, dichas acciones se denominan operadores de búsqueda (search operators). Estos estados descubiertos como accesibles se introducen en el registro de estados en los que es posible posicionar el sistema, a excepción de aquellos que el algoritmo haya analizado previamente durante su ejecución. Posteriormente, se utiliza una función de evaluación, cuyo objetivo es determinar el siguiente estado a analizar entre los incluidos en el registro de estados accesibles. Este próximo estado será aquel que, según la función de evaluación, se aproxima en mejor medida al estado final deseado. Asimismo, se repetirá el mismo proceso sobre este nuevo estado actual que se efectuó sobre el estado predecesor, el cual será introducido en el conjunto de estados ya evaluados.

Desde el punto de vista ideal, el proceso de búsqueda automatizada terminaría encontrando un estado final que cumpla con todos los requisitos preestablecidos como criterios de búsqueda. Sin embargo, esto no siempre es posible. Debido a ello, es importante que el algoritmo de *Hill Climbing* implementado pueda sobrellevar la circunstancia de que el estado final ideal resulte inalcanzable. Para ello, se pueden aplicar distintos criterios de terminación del proceso de búsqueda. Por un lado, se tienen criterios relativos al gasto computacional implicado durante la ejecución del algoritmo como, por ejemplo, haberse superado el tiempo de ejecución máximo

otorgado al proceso o el número máximo de transiciones permitidas. Por otra parte, existen otros criterios que tienen en cuenta los resultados obtenidos en la ejecución del algoritmo. Asimismo, entre estos criterios se encuentra la consideración de haber llegado a un estado final que se asemeja suficientemente al deseado, o el hecho de que ya no queden próximos estados accesibles que evaluar.

En términos generales, se observa que, a medida que se suceden las transiciones de estado, el sistema se aproxima a las características deseadas. No obstante, habrá situaciones en las que el nuevo estado establecido se encuentre más alejado de los requisitos a cumplir que el estado predecesor, aunque sea la opción más cercana al estado final deseado desde la perspectiva de la función de evaluación considerando todos los estados accesibles no analizados. Pese a ello, este nuevo estado puede posibilitar que se encuentre un camino a otros estados cuya cercanía al resultado buscado sea mayor a la observada en cualquier estado anterior. Esta situación presenta cierta analogía con el proceso de escalar una montaña, donde a veces es necesario atravesar un valle descendiendo antes de retomar el ascenso a la cima. Este símil es el que le otorga el nombre Hill Climbing al algoritmo aquí estudiado.

Figura 2: Ejemplo estados en el algoritmos de hill-climbing [7]

# 2.3. Clasificación mediante análisis probabilístico (Bayes)

El fundamento en el que se basa este sistema de clasificación consiste en estudiar qué clases contienen una cantidad más elevada de muestras con una serie de atributos de un determinado valor. De esta manera, aquellas muestras que cumplan con el patrón observado tendrán más posibilidades de pertenecer a esa clase en particular que a cualquier otra, siendo catalogados como tal.

Para entender este procedimiento, es necesario introducir los conceptos probabilidad condicional y la probabilidad conjunta. Ambos términos implican considerar una cantidad mínima de 2 características cualesquiera de los elementos estudiados como, por ejemplo, la pertenencia a una clase concreta o el valor de alguno de sus atributos. Asimismo, la probabilidad de que un elemento tenga una característica "x" condicionada con que posea la característica "x<sub>cond</sub>", sería equivalente a, dentro del conjunto elementos posibles, considerar que los elementos que cumplen con la característica "x<sub>cond</sub>" son los únicos existentes, y dentro de este subconjunto evaluar la probabilidad de que un elemento aleatorio se adecúe a la característica "x".

Por otra parte, la probabilidad conjunta de "x" y " $x_{cond}$ " se refiere a la posibilidad de que ambas características se cumplan en un elemento aleatorio, considerando el total de elementos posibles. De esta manera, la probabilidad condicional " $P(x|x_{cond})$ " y la probabilidad conjunta " $P(x,x_{cond})$ ", se encuentran interrelacionadas, como se expone en la ecuación (1). A partir de dicha fórmula, se deduce la fórmula de Bayes que se expone en la ecuación (2).

$$P(x , x_{cond}) = P(x \mid x_{cond}) * P(x_{cond})$$

(1)

$$P(x_{cond} \mid x) = \frac{P(x \mid x_{cond}) * P(x_{cond})}{P(x)}$$

(2)

Aplicando esta fórmula al problema de clasificación concreto, "x<sub>cond</sub>" representaría la pertenencia a una determinada clase, mientras que "x" constituiría una o varias características de los elementos evaluados definidas como valores de sus atributos. De esta manera, si solo se tuviese en consideración un único atributo, se podría emplear la ecuación (2) para determinar, para cada clase, la probabilidad de que el elemento estudiado pertenezca a la misma. Con ello, se establece que la clasificación correcta de la muestra sería aquella en la que, dado el valor del atributo considerado, se consigue un valor mayor en el cálculo de la probabilidad.

Aunque en el caso de un único atributo, la ecuación (2) resulta insuficiente, y no es demasiado útil si se considera varios atributos. Esto se debe a que, al exigir un mayor número de coincidencias para el subconjunto de las muestras consideradas en el cálculo de la probabilidad condicional, la cantidad de muestras evaluables se reduce. En consecuencia, se carece de muestras suficientes para establecer correctamente la categoría del elemento introducido. Por lo tanto, sería necesaria una fórmula en la que la influencia ponderativa ejercida por cada característica del elemento de entrada fuese independiente de las demás. Para ello, es posible aplicar la transformación indicada en la ecuación (3), siempre que los atributos sean independientes entre sí.

En dicha ecuación, "x" simboliza el valor del conjunto de atributos que representa al elemento de entrada, mientras que "x<sub>i</sub>" sería el valor de uno de sus atributos de manera específica. Asimismo, "c" simbolizaría la pertenencia a una clase concreta.

$$P(x \mid c) = \prod_{i=1}^{n} P(x_i \mid c)$$

(3)

Esto permite que se pueda medir, de manera comparativa, la probabilidad de pertenencia de un elemento de entrada "x" a cualquier clase presente en la clasificación, utilizando para ello la fórmula de la ecuación (4). De esta manera, la clase establecida para el elemento introducido será aquella en la que la ecuación ofrezca un valor más elevado.

$$P(x,c) = P(c) * \prod_{i=1}^{n} P(x_i \mid c)$$

(4)

El aspecto clave del funcionamiento de este método de clasificación recae en la fiabilidad de las funciones de determinación de la probabilidad. La extracción de los resultados probabilísticos se establece principalmente mediante la frecuencia relativa de las características buscadas dentro del conjunto de muestras de entrenamiento. De esta manera, en las versiones más simples del proceso de deducción de la probabilidad, su valor y el de la frecuencia relativa se consideran idénticos. Esto quiere decir que, si dentro del conjunto o subconjunto de elementos que representan el total para la función de probabilidad existen 100 elementos y solo 20 de ellos cumplen con las características evaluadas, el resultado devuelto en este caso por la función de probabilidad es de 0.2. Sin embargo, existen circunstancias con respecto al banco de entrenamiento del clasificador que afectan a la utilidad de las funciones de probabilidad de manera particular en comparación con otros sistemas de clasificación. Estas son las siguientes:

a. Conjunto de muestras de entrenamiento demasiado escaso. Esta situación ocasiona que exista cierta facilidad en que la frecuencia relativa no plasme el valor de la probabilidad para todas las características a evaluar. Como posible ejemplo de ello se puede citar las probabilidades de cara o cruz en el lanzamiento de una moneda al aire, que pueden considerarse iguales para ambas opciones. Asimismo, si solo se lanza la moneda 4 veces, resulta fácilmente factible que en lugar de obtenerse 2 veces cada una de las opciones, de manera que la frecuencia relativa y la probabilidad coincidiesen, una de las caras aparezca en 3 ocasiones. Este suceso originar, si solo se tuviese en cuenta la frecuencia relativa, que

una cara tuviera una probabilidad, de acuerdo con el análisis estadístico, de 0.75, y la restante un 0.25.

Si no es posible disponer de una mayor cantidad de muestras de entrenamiento y el programador no está de acuerdo con la probabilidad evidenciada por la frecuencia relativa, se le puede dar cierta influencia a las probabilidades presupuestas por este individuo. Además, esta influencia es parametrizable mediante una variable denominada "m" que, a efectos prácticos, simbolizaría a medida que su valor es más elevado, un mayor grado de certeza que el programador confía tener en sus afirmaciones. La combinación del valor de la frecuencia relativa y de la probabilidad supuesta se efectuaría por medio de la ecuación mostrada en la ecuación (5), donde " $N_{\rm all}$ " es la cantidad de elementos considerados, " $N_{\rm x}$ " la cantidad de elementos dentro del conjunto que cumplen con el patrón "x" y " $\pi_{\rm x}$ " el valor de probabilidad estimado por el programador. Como resultado se obtiene la probabilidad  $P_{\rm x}$ .

$$P_{\chi} = \frac{N_{\chi} + m * \pi_{\chi}}{N_{all} + m} \tag{5}$$

b. Interdependencia de los atributos. Como se comentó con anterioridad, este método de clasificación basado en la ecuación de Bayes requiere que los atributos considerados sean independientes. Esta condición suele no cumplirse con cierta frecuencia en los atributos involucrados en un sistema de clasificación cualquiera. En el caso de que la correlación entre 2 o más atributos sea leve, esta sería fácilmente aproximable como nula. En dicha situación, la precisión del cálculo probabilístico quedaría comprometida. Sin embargo, ello no implicaría que el sistema siga resolviendo correctamente el problema de clasificación.

Para el caso de que la correlación sea muy significativa y, por lo tanto, su relevancia no pueda ser ignorada, se pueden transformar los elementos a clasificar. Esto supondría una serie de cambios como la eliminación de los atributos redundantes o la combinación de atributos. Asimismo, un ejemplo de redundancia sería la obtenida si, entre los atributos del elemento, se considera la fecha de nacimiento y la edad de una misma persona, ya que ofrecen la misma información desde perspectivas diferentes. Debido a ello, sería necesario excluir a uno de estos dos atributos con el objetivo de que el sistema opere correctamente. Respecto a la combinación de atributos, esta consiste en que, si se tienen una serie de atributos que aportan diferente información, por lo que no son perfectamente deducibles una con respecto a la otra, pero que aun así presentan cierta correlación, entonces pueden

sustituirse estos atributos por uno nuevo en el que se contenga la información total aportada por ambos.

c. Atributos de naturaleza continua. El problema de esta situación radica en que las funciones de probabilidad vistas hasta ahora se basan fundamentalmente en dividir la cantidad de elementos encontrados que presentan el patrón buscado entre el total de elementos evaluados. Para ello, se requiere que los atributos dispongan de un conjunto finito de valores, aspecto que no caracteriza a una variable continua, ya que siempre dispondrá de infinidad de valores intermedios.

Para lidiar con esta situación, una alternativa consiste en discretizar los valores de los atributos continuos. Este hecho se traduce en segmentar el rango de valores del atributo continuo en una serie de intervalos. De esta manera, si dos elementos ubican el valor del atributo en un mismo intervalo, se considerará, a nivel de cálculo, que sus valores son coincidentes.

Otra estrategia consiste en reemplazar la función de probabilidad por la función de densidad de probabilidad. Para ello, se supone la disponibilidad de una cantidad infinitamente grande de muestras de entrenamiento. A diferencia de las funciones de probabilidad anteriores, los resultados de la función de densidad de probabilidad son de carácter continuo. Además, el resultado otorgado será más elevado cuanto mayor sea el grado de similitud con una mayor cantidad de muestras para el patrón observado.

## 2.4. Clasificación por vecino más cercano

El principio en el que se apoya, en su versión más simple, consiste en la categorización del elemento de entrada en el mismo grupo que el elemento que presente un mayor grado de similitud con él. Dicha similitud quedará establecida en función de los valores de sus atributos, cuyas semejanzas entre sí se podrán valorar con distintas estrategias, dependiendo de si estos son de naturaleza discreta o continua.

Una posible estrategia en el caso de atributos de valor discreto, que consiste en contar la cantidad de atributos entre dos elementos cuyos valores coinciden, aumentando la semejanza considerada entre estos a medida que se encuentran más coincidencias. Por otra parte, para el caso de atributos de valores continuos, la estrategia más acertada consiste en medir la cercanía geométrica, considerando cada atributo como una coordenada distinta dentro de un espacio vectorial en el que se posicionan los elementos. Esta estrategia puede utilizarse también cuando en

el conjunto de atributos a considerar, existen tanto atributos de valor continuo como atributos de valor discreto. Para el caso de los atributos discretos, la pauta a seguir es añadir un sumando de valor más elevado cuanto más significativa sea la falta de similitud entre los valores comparados, lo cual será establecido a criterio del programador. Cabe destacar que el adecuado escalamiento de los atributos es un aspecto muy importante para asegurar que unos pocos atributos no eclipsen la relevancia de otros en el cálculo de la distancia geométrica por cuestiones de magnitud.

La ecuación más comúnmente conocida que puede aplicarse al cálculo del distanciamiento entre dos elementos y, por ende, de su grado de similitud suele ser la distancia de Euclides, es decir, el cálculo del módulo que une los dos puntos en los que se encuentran los elementos a comparar. Sin embargo, existen otras fórmulas que pueden adecuarse mejor al problema de clasificación concreto, ya que representan de manera más precisa la notoriedad que se le quiera dar a la evolución del distanciamiento entre dos elementos en función de las posibles divergencias en valor de sus atributos. Independientemente de la fórmula aplicada, esta deberá cumplir con las siguientes condiciones.

- 1. La distancia nunca puede ser negativa.

- 2. La distancia entre dos vectores idénticos debe valer 0.

- Debe cumplir la propiedad conmutativa, es decir, que la distancia desde un elemento de referencia al otro será equivalente a la calculada si la referencia se considera en sentido inverso.

- 4. Debe cumplir la desigualdad triangular. Esto quiere decir que, sea "x<sub>1</sub>" y "x<sub>2</sub>" los elementos a comparar e "y<sub>1</sub>" un punto de referencia cualquiera, la suma de la distancia de "x<sub>1</sub>" y "x<sub>2</sub>" con respecto a y<sub>1</sub> adquirirá un valor igual o mayor a la distancia existente entre "x<sub>1</sub>" y "x<sub>2</sub>".

Cabe destacar que, debido al cierto margen de error que puede presentarse tanto en el valor de los atributos como en la clasificación de los elementos estudiados, confiar únicamente en el elemento más cercano para categorizar el elemento entrante puede dar resultados relativamente poco fidedignos. Por este motivo, es aconsejable valorar un mayor número de elementos cercanos a la hora de clasificar el objeto de entrada si el margen de error así lo justifica. Sin embargo, la cantidad de elementos vecinos a establecer no debe incrementarse de manera indefinida, ya que, en función de lo significativa que sea con respecto al total de los elementos de referencia tomados, puede resultar contraproducente.

En el caso de la clasificación con una cantidad plural de elementos cercanos, la categoría del elemento de entrada se establece, siguiendo la versión más simple del algoritmo, en aquel grupo en el que se haya detectado una mayor cantidad de elementos identificados como cercanos.

Sin embargo, se puede optimizar la eficacia del algoritmo de *sorting* si la relevancia de los elementos cercanos se parametriza en función del distanciamiento que presente con respecto al elemento entrante, siendo inversamente proporcionales.

La utilidad del sistema de clasificación depende del banco de elementos de entrenamiento usado como referencia. Para ello, es necesario filtrar aquellos elementos considerados perjudiciales, ya que pueden inducir a una clasificación errónea, así como aquellos que sean redundantes, pues simplemente añaden carga computacional de manera bastante innecesaria.

Para el caso de muestras que generan clasificación incorrecta, estas se limitan a aquellas que se encuentran en una región fronteriza y a aquellas que se encuentran rodeadas de muestras de una categoría distinta a la propia. Para la detección de estas, un procedimiento muy utilizado es el de *Tomek Links* [8], el cual las identifica como parejas de muestras que son las más cercanas entre sí y pertenecen a distintas clases. Por otra parte, para eliminar muestras redundantes, la estrategia consiste en desarrollar un subconjunto del banco de muestras de entrenamiento y comprobar si las muestras excluidas son clasificadas correctamente basándose en dicho subconjunto. En los casos afirmativos, se constata que la muestra es redundante. En los casos contrarios, constituye una muestra a considerar dentro del subconjunto, por lo que se incorpora y se repite el proceso para el resto de las muestras descartadas.

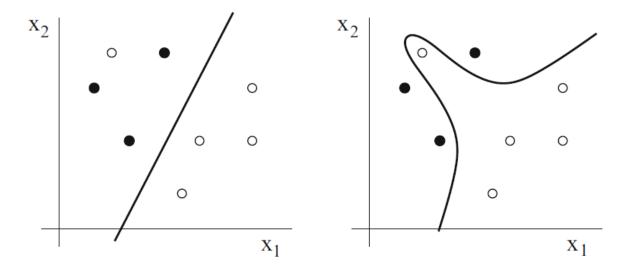

# 2.5. Clasificadores lineales y polinómicos

Al igual que el caso previo, se parte de una serie de muestras de referencia ubicadas dentro de un espacio vectorial. Dichas muestras se utilizan como referencia para delimitar zonas de pertenencia a un tipo concreto de clase, de manera que las muestras entrantes son clasificadas en función de en qué zona del espacio vectorial se encuentran localizadas. Para ello, el aspecto fundamental consiste en establecer correctamente las fronteras entre las regiones, las cuales se definen matemáticamente mediante ecuaciones lineales o polinómicas, cuyo grado será más elevado cuanto más sofisticadas sean las fronteras trazadas. En el caso de la ecuación lineal, esta quedará definida de acuerdo con la ecuación (6), en la que "x<sub>i</sub>" hace referencia a los atributos que definen a las muestras clasificadas y "w<sub>i</sub>" representa la ponderación otorgada a cada una, la cual puede adquirir valores tanto positivos como negativos. Por otra parte, "-w<sub>0</sub>" constituiría el valor umbral [8].

$$w_0 + \sum_{i=1}^n w_i x_i = 0 (6)$$

Asimismo, el objetivo de la aplicación de clasificación será determinar el valor de los parámetros w. De esta manera, dependiendo del valor del conjunto de atributos de la muestra, la ecuación tomará un valor positivo o negativo, perteneciendo a una clase distinta en cada caso. Una situación peculiar que puede ocurrir es la de la muestra cuyos valores de atributos le otorgan un valor nulo, lo que representaría que la muestra se encuentra justo en la frontera entre las dos clases. En dicha circunstancia, la determinación de a cuál de las dos clases pertenece suele establecerse bien aleatoriamente o bien al grupo mayoritario del conjunto de entrenamiento.

#### 2.5.1. Clasificadores binarios de ecuación lineal

En el caso de que la frontera a establecer sea únicamente entre dos clases y pueda expresarse mediante una ecuación lineal, la determinación de la misma resulta relativamente simple. Asimismo, existen principalmente dos procedimientos para ello, los cuales se basan en la modificación recurrente de los parámetros w. Uno de ellos es el procedimiento de *Perceptron*, consistente en sumar o restar una cantidad determinada. Por otra parte, se encuentra el procedimiento *WINNOW* que emplea la multiplicación y la división.

## 2.5.1.1. Método Perceptron

Consiste en que, partiendo de unos valores iniciales de los parámetros de ponderación y del valor umbral relativamente pequeños, se evalúa si la ecuación categoriza correctamente a las muestras en sus respectivas clases y, en caso contrario, se modifican los factores de ponderación de los atributos involucrados y el valor umbral. De esta manera, si el valor obtenido con la ponderación actual de los atributos es negativo para una muestra de entrenamiento, pero se le presupone positivo, entonces se efectuará el incremento de los parámetros w que participasen en el cálculo. En el caso opuesto, si se obtiene un resultado positivo, pero debió ser negativo, se decrementarán dichos parámetros. En ambos casos, el incremento o decremento de cada parámetro "w<sub>i</sub>" será directamente proporcional al valor que posea el atributo "x<sub>i</sub>" al que se le asocia, como se expone en la ecuación (7). Esta ecuación es capaz de operar tanto con atributos que toman valores discretos como continuos. Sin embargo, es conveniente que dichos valores se encuentren normalizados, es decir, que varíen entre 0 y 1.

$$w_i = w_i + \eta[c - h]x_i \tag{7}$$